JP2005294678A - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP2005294678A JP2005294678A JP2004109795A JP2004109795A JP2005294678A JP 2005294678 A JP2005294678 A JP 2005294678A JP 2004109795 A JP2004109795 A JP 2004109795A JP 2004109795 A JP2004109795 A JP 2004109795A JP 2005294678 A JP2005294678 A JP 2005294678A

- Authority

- JP

- Japan

- Prior art keywords

- film

- pad

- semiconductor device

- semiconductor element

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

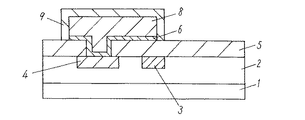

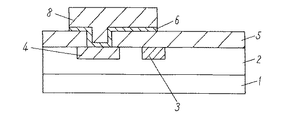

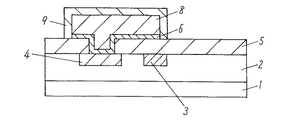

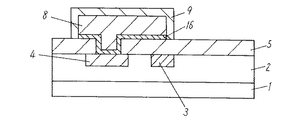

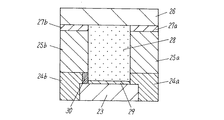

【解決手段】半導体素子1の上に形成された配線電極4が、半導体素子1表面に形成されたパシベーション膜5に対し、開口されており、配線電極4の上にTiW膜6と、さらにその上にNi膜8が形成され、パッド電極を構成する。積層されたTiW膜6とNi膜8の表面および側面を覆うように金膜9を形成する。パッド近傍にイオンや電界が存在してもパッド材料が溶け出すことはなく、信頼性の高い半導体素子が得られる。

【選択図】図1

Description

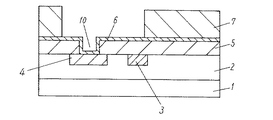

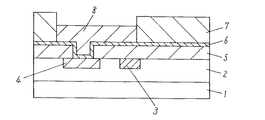

2 層間絶縁膜

3 配線

4 配線電極

5 パシベーション膜

6 TiW膜

7 ホトレジスト膜

8 Ni膜

9 金膜

16 TiN膜

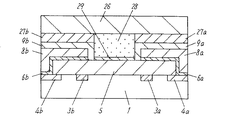

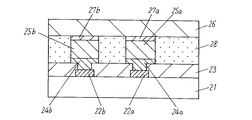

26 インターポーザー

28 樹脂

Claims (6)

- 半導体素子の外部接続用のパッド電極が複数の金属層で積層され、前記パッド電極の表面および側面が導電体薄膜で覆われていることを特徴とする半導体装置。

- 複数の金属層の1つがバンプ層であることを特徴とする請求項1記載の半導体装置。

- 導電体薄膜が金であることを特徴とする請求項1または2記載の半導体装置。

- 複数の金属層は、半導体素子表面側の第1の金属層はTiW膜またはTiN膜であり、その上層の第2の金属層はNi膜であることを特徴とする請求項1または2記載の半導体装置。

- 半導体素子の表面に外部接続用のパッド電極である複数の金属層を形成する工程と、前記パッド電極の表面および側面を覆うように無電界メッキ法で導電体薄膜を形成する工程とを備えたことを特徴とする半導体装置の製造方法。

- 半導体素子表面の所定の領域にパッド電極と接続する配線電極を形成する工程と、前記半導体素子表面に絶縁膜を形成する工程と、前記配線電極上の前記絶縁膜を選択的に除去して、コンタクトホールを形成する工程と、前記配線電極上に第1の金属層を形成する工程と、前記第1の金属層の上に第2の金属層を電界メッキ法で形成する工程と、前記第1の金属層と前記第2の金属層からなる前記パッド電極の表面および側面の上に無電界メッキ法で導電体薄膜を形成する工程とを備えたことを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109795A JP2005294678A (ja) | 2004-04-02 | 2004-04-02 | 半導体装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109795A JP2005294678A (ja) | 2004-04-02 | 2004-04-02 | 半導体装置およびその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294678A true JP2005294678A (ja) | 2005-10-20 |

Family

ID=35327246

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004109795A Withdrawn JP2005294678A (ja) | 2004-04-02 | 2004-04-02 | 半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294678A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012004210A (ja) * | 2010-06-15 | 2012-01-05 | Renesas Electronics Corp | 半導体集積回路装置およびその製造方法 |

| JP2014093318A (ja) * | 2012-10-31 | 2014-05-19 | Dowa Electronics Materials Co Ltd | 半導体素子およびその製造方法 |

| JP2015204393A (ja) * | 2014-04-15 | 2015-11-16 | サンケン電気株式会社 | 半導体装置 |

-

2004

- 2004-04-02 JP JP2004109795A patent/JP2005294678A/ja not_active Withdrawn

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012004210A (ja) * | 2010-06-15 | 2012-01-05 | Renesas Electronics Corp | 半導体集積回路装置およびその製造方法 |

| JP2014093318A (ja) * | 2012-10-31 | 2014-05-19 | Dowa Electronics Materials Co Ltd | 半導体素子およびその製造方法 |

| JP2015204393A (ja) * | 2014-04-15 | 2015-11-16 | サンケン電気株式会社 | 半導体装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100679573B1 (ko) | 반도체 장치의 제조 방법 | |

| KR100290193B1 (ko) | 반도체장치및그제조방법 | |

| US8227341B2 (en) | Semiconductor device and method of manufacturing the same | |

| US8471367B2 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| KR100315030B1 (ko) | 반도체패키지의제조방법 | |

| US20110290545A1 (en) | Through wiring board and method of manufacturing the same | |

| KR100536036B1 (ko) | 반도체 장치 | |

| TWI720233B (zh) | 半導體裝置及其製造方法 | |

| JP2005327984A (ja) | 電子部品及び電子部品実装構造の製造方法 | |

| US8269347B2 (en) | Semiconductor chip, electrode structure therefor and method for forming same | |

| US6683383B2 (en) | Wirebond structure and method to connect to a microelectronic die | |

| JP2003324120A (ja) | 接続端子及びその製造方法並びに半導体装置及びその製造方法 | |

| JP2007317979A (ja) | 半導体装置の製造方法 | |

| JP3918842B2 (ja) | 半導体素子及びそれを備えたワイヤボンディング・チップサイズ・パッケージ | |

| JP4775007B2 (ja) | 半導体装置及びその製造方法 | |

| US20060164110A1 (en) | Semiconductor device and method of fabricating the same | |

| JP2006237151A (ja) | 配線基板および半導体装置 | |

| JP5433849B2 (ja) | 磁気センサ | |

| JP2005294678A (ja) | 半導体装置およびその製造方法 | |

| JP4638614B2 (ja) | 半導体装置の作製方法 | |

| JP5165190B2 (ja) | 半導体装置及びその製造方法 | |

| CN102214616B (zh) | 金属导电结构及其制作方法 | |

| US20060289991A1 (en) | Semiconductor device and manufacturing method of the same | |

| US6617697B2 (en) | Assembly with connecting structure | |

| JP6562161B2 (ja) | 薄膜デバイスおよび薄膜デバイスの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070219 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20070313 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090129 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090210 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20090325 |