JP2005294634A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2005294634A JP2005294634A JP2004109162A JP2004109162A JP2005294634A JP 2005294634 A JP2005294634 A JP 2005294634A JP 2004109162 A JP2004109162 A JP 2004109162A JP 2004109162 A JP2004109162 A JP 2004109162A JP 2005294634 A JP2005294634 A JP 2005294634A

- Authority

- JP

- Japan

- Prior art keywords

- region

- conductive connection

- connection region

- electrode group

- electrodes

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

- H10D89/60—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD]

- H10D89/601—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD] for devices having insulated gate electrodes, e.g. for IGFETs or IGBTs

- H10D89/911—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD] for devices having insulated gate electrodes, e.g. for IGFETs or IGBTs using passive elements as protective elements

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

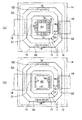

【解決手段】 分離用絶縁膜11で隔てられたN型ウェル10において、さらにN型の不純物が高濃度に導入されたN型領域12,13が形成されている。層間の絶縁膜14が形成され、複数の開孔を介してN型領域12上に複数の電極15を有する電極群G1、N型領域13上に複数の電極16を有する電極群G2が形成されている。N型領域12とN型領域13の関係は、島状の領域とそれを囲む環状の領域になる。島状の領域(12)と環状の領域(13)の間にあるN型ウェル10の環状の領域が抵抗Rとして機能し得る領域である。これにより、ESD等によって過剰に印加された電荷の放電路は、N型領域12の周囲(四方)均等に存在する構成となっている。

【選択図】 図1

Description

また、上記それぞれ本発明に係る半導体装置において、少なくとも前記第1導電接続領域の中心から四方がそれぞれ対称となるようなパターンを伴い前記第1導電接続領域と前記第2導電接続領域の間が抵抗体として機能する。他の素子形成の工程と同時に形成でき、製造効率、コストの面でも有利である。さらに、パターン的に第1電極群から四方がそれぞれ対称な抵抗素子を構成することが可能になる。これにより、第2電極群の接続構成の自由度が広がる。

なお、好ましくは、前記第1電極群における所定の複数電極と接続される第1配線パターン及び前記第2電極群における所定の複数電極と接続される第2配線パターンを形成する工程をさらに含む。

半導体基板上のN型の半導体基体、例えばN型ウェル10に、分離用絶縁膜11が形成されている。分離用絶縁膜11で隔てられたN型ウェル10において、さらにN型の不純物が高濃度に導入されたN型領域12,13が形成されている。すなわち、中央部にN型領域12、その周囲をN型領域13が囲む形態である。層間の絶縁膜14が形成され、複数の開孔を介してN型領域12上に複数の電極15を有する電極群G1、N型領域13上に複数の電極16を有する電極群G2が形成されている。すなわち、N型領域12とN型領域13が互いにN型ウェル10による抵抗領域両端の導電接続領域となる。理想的な構成としては、N型領域12の中心から四方がそれぞれ対称となるようなパターンを伴い、N型領域12とN型領域13の間のN型ウェル10が抵抗体として機能する。

図3において、配線パターン18は、N型領域12上の複数の電極15と接続されている。配線パターン19は、N型領域13上の四方に分かれたうちの一領域に配された複数の電極16と接続されている。配線パターン18,19は、電極15,16と同一工程で形成されてもよい。その際、少なくとも上方に電極群G1と接続される配線パターン18が通る領域に当たる電極16(破線で示す電極群G2)は、形成しない形態となる。また、配線パターン18,19は、必ずしも同一層で構成されていなくてもよい。すなわち、電極群G1と接続される配線パターン18は、電極群G2と接続される配線パターン19より上層の配線パターンとして形成される。すなわち、配線層に合わせて電極群を積み上げることで、異なる配線層のパターンによる構成が可能である。

N型領域12上の電極群G1について、実質的に抵抗素子としての電極として作用するのはN型領域12周囲の電極である。従って、図5(a)では、中央領域A1には電極15を配さず、周囲2列の電極15を配する構成としている。また、図5(b)では、中央領域A2には電極15を配さず、周囲1列の電極15を配する構成としている。

この第2実施形態では、第1実施形態に比べて、N型領域12,13のシリサイド化工程が付加され、所定領域にシリサイド金属層21が設けられている。その他の構成は第1実施形態と同様であるため、説明は省略する。シリサイド金属層21は、N型領域12,13上において、分離用絶縁膜11に隣接した所定領域を除いて配置されている。抵抗として機能し得る領域の端部(縁部)領域においては、電荷の集中を避けるため、シリサイド金属層を除いた領域が形成されている方がよいからである。理想的な構成としては、N型領域12の中心から四方がそれぞれ対称となるようなパターンを伴い、N型領域12とN型領域13の間のN型ウェル10が抵抗体として機能する。

また、各実施形態において、半導体基板上のN型ウェル(10)を基体としたウェル抵抗を示したが、これに限らず、P型ウェルを基体としたウェル抵抗を構成してもよい。また、ウェルが形成される基板はSOI(silicon on insulator)基板であることも考えられる。

Claims (14)

- 第1導電型の半導体基体と、

前記半導体基体に設けられた第1導電型の第1導電接続領域と、

前記半導体基体において前記第1導電接続領域を囲むように設けられた第1導電型の第2導電接続領域と、

前記第1導電接続領域上に設けられた複数の電極を有する第1電極群と、

前記第2導電接続領域上に設けられた複数の電極を有する第2電極群と、

を含む半導体装置。 - 第1導電型の半導体基体と、

前記半導体基体上に設けられた第1絶縁膜と、

前記第1絶縁膜で分離された中央部の第1導電型の第1導電接続領域及びその周囲の第1導電型の第2導電接続領域と、

前記第1導電接続領域及び前記第2導電接続領域上に設けられた第2絶縁膜と、

前記第2絶縁膜の複数の開孔を介して前記第1導電接続領域上に設けられた複数の電極を有する第1電極群と、

前記第2絶縁膜の複数の開孔を介して前記第2導電接続領域上に設けられた複数の電極を有する第2電極群と、

前記第1電極群における所定の複数電極と接続された第1配線パターンと、

前記第2電極群における所定の複数電極と接続された第2配線パターンと、

を含む半導体装置。 - 前記第1導電接続領域及び前記第2導電接続領域は、前記第1絶縁膜に隣接した所定領域を除いてシリサイド金属層が形成されている請求項2記載の半導体装置。

- 前記半導体基体は、半導体基板上に設けられたウェル領域の一つであり、かつ前記第1導電接続領域と前記第2導電接続領域の間が抵抗体として機能する請求項1〜3いずれか一つに記載の半導体装置。

- 前記半導体基体は、半導体基板上に設けられたウェル領域の一つであり、かつ少なくとも前記第1導電接続領域の中心から四方がそれぞれ対称となるようなパターンを伴い前記第1導電接続領域と前記第2導電接続領域の間が抵抗体として機能する請求項1〜3いずれか一つに記載の半導体装置。

- 前記第1電極群に関し、周辺の電極は四方で所定数個ずつ前記第1導電接続領域の縁部に最も近い距離で配列され、前記第2電極群の電極は、前記第1電極群の周辺の電極それぞれと対向するように、四方に所定数配列されている請求項1〜5いずれか一つに記載の半導体装置。

- 前記第1電極群は、前記第1導電接続領域の中央から所定領域全域に分布し、そのうち周辺の電極は四方で所定数個ずつ前記第1導電接続領域の縁部に最も近い距離で配列され、前記第2電極群の電極は、少なくとも前記第1電極群の周辺の所定数個の電極それぞれと対向するように、所定数配列されている請求項1〜5いずれか一つに記載の半導体装置。

- 前記第1導電接続領域は、四角形の四隅部分をなくした少なくとも四辺を有する平面形状を呈し、前記第1電極群は少なくとも前記四辺に沿ってそれぞれ所定数の電極が配列されるように準備され、前記第2電極群の電極は、少なくとも前記第1電極群の所定数個の電極それぞれと対向するように、所定数配列されている請求項1〜5いずれか一つに記載の半導体装置。

- 前記第1導電接続領域と前記第2導電接続領域の間の距離は、前記第1電極群と前記第2電極群が対向する領域が他の領域よりも小さい請求項1〜8いずれか一つに記載の半導体装置。

- 半導体基体上に環状の第1絶縁膜を形成する工程と、

前記第1絶縁膜をマスクに前記半導体基体の中央部に第1導電型の第1導電接続領域及びその周囲に第1導電型の第2導電接続領域を形成する工程と、

前記第1導電接続領域及び前記第2導電接続領域上に第2絶縁膜を形成する工程と、

前記第2絶縁膜の複数の開孔を介して前記第1導電接続領域上及び前記第2導電接続領域上にそれぞれ複数の電極を有する第1電極群及び第2電極群を形成する工程と、

を含む半導体装置の製造方法。 - 前記第1電極群における所定の複数電極と接続される第1配線パターン及び前記第2電極群における所定の複数電極と接続される第2配線パターンを形成する工程をさらに含む請求項10記載の半導体装置の製造方法。

- 前記半導体基体は、半導体基板上に設けられたウェル領域の一つであり、かつ少なくとも前記第1導電接続領域の中心から四方がそれぞれ対称となるような前記第1導電接続領域と前記第2導電接続領域の間の抵抗体を形成する請求項10または11記載の半導体装置の製造方法。

- 前記第1絶縁膜に関し、内周は少なくとも長手の四辺を有する八角形状とし、外周は前記四辺と対向する四辺の領域を形成し少なくとも四隅領域より幅を小さくする請求項10〜12いずれか一つに記載の半導体装置の製造方法。

- 前記第2絶縁膜を形成する工程の前に、少なくとも前記第1絶縁膜に隣接した前記第1導電接続領域及び前記第2導電接続領域の所定領域を覆うシリサイド化防止のための保護層を形成する工程と、前記所定領域を除いて前記第1導電接続領域及び前記第2導電接続領域上にシリサイド金属層を形成する工程と、をさらに含む請求項10〜13いずれか一つに記載の半導体装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109162A JP3760945B2 (ja) | 2004-04-01 | 2004-04-01 | 半導体装置及びその製造方法 |

| US11/095,709 US7394134B2 (en) | 2004-04-01 | 2005-03-31 | Semiconductor device with electrostatic discharge protection |

| US12/126,473 US8076748B2 (en) | 2004-04-01 | 2008-05-23 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109162A JP3760945B2 (ja) | 2004-04-01 | 2004-04-01 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005294634A true JP2005294634A (ja) | 2005-10-20 |

| JP3760945B2 JP3760945B2 (ja) | 2006-03-29 |

Family

ID=35053343

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004109162A Expired - Fee Related JP3760945B2 (ja) | 2004-04-01 | 2004-04-01 | 半導体装置及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7394134B2 (ja) |

| JP (1) | JP3760945B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008098201A (ja) * | 2006-10-05 | 2008-04-24 | Denso Corp | 半導体装置 |

| KR101212267B1 (ko) | 2005-12-29 | 2012-12-14 | 매그나칩 반도체 유한회사 | 고전압 숏키 다이오드 |

| JP2016068650A (ja) * | 2014-09-29 | 2016-05-09 | 日立オートモティブシステムズ株式会社 | 電子制御装置 |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7551414B2 (en) * | 2005-12-15 | 2009-06-23 | Lsi Corporation | Electrostatic discharge series protection |

| KR100672681B1 (ko) * | 2005-12-28 | 2007-01-24 | 동부일렉트로닉스 주식회사 | 바이폴라 트랜지스터의 제조방법 |

| US8217455B2 (en) * | 2008-04-14 | 2012-07-10 | International Business Machines Corporation | Semiconductor-on-insulator device structures with a body-to-substrate connection for enhanced electrostatic discharge protection, and design structures for such semiconductor-on-insulator device structures |

| TWI484197B (zh) * | 2013-02-20 | 2015-05-11 | Au Optronics Corp | 顯示裝置與其檢測方法 |

| JP6705726B2 (ja) * | 2016-09-14 | 2020-06-03 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2022170906A (ja) * | 2021-04-30 | 2022-11-11 | セイコーエプソン株式会社 | 集積回路装置及び発振器 |

| CN114420677B (zh) * | 2021-12-07 | 2025-03-28 | 厦门市三安集成电路有限公司 | GaN器件的防护结构及其制作方法 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07106567A (ja) | 1993-10-05 | 1995-04-21 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP3176806B2 (ja) | 1994-09-09 | 2001-06-18 | 松下電子工業株式会社 | 半導体保護装置 |

| JP4376348B2 (ja) | 1998-05-18 | 2009-12-02 | パナソニック株式会社 | 半導体装置 |

| JP3116916B2 (ja) | 1998-08-17 | 2000-12-11 | 日本電気株式会社 | 回路装置、その製造方法 |

| JP3425574B2 (ja) * | 1999-07-19 | 2003-07-14 | Necエレクトロニクス株式会社 | 半導体集積回路の入出力保護装置 |

| US6476472B1 (en) * | 2000-08-18 | 2002-11-05 | Agere Systems Inc. | Integrated circuit package with improved ESD protection for no-connect pins |

| JP4080682B2 (ja) | 2000-09-28 | 2008-04-23 | 株式会社東芝 | 半導体装置 |

| TW522542B (en) * | 2000-11-09 | 2003-03-01 | United Microelectronics Corp | Electrostatic discharge device structure |

| TW495952B (en) * | 2001-07-09 | 2002-07-21 | Taiwan Semiconductor Mfg | Electrostatic discharge protection device |

| TWI259573B (en) * | 2002-04-22 | 2006-08-01 | Ind Tech Res Inst | High efficiency substrate-triggered ESD protection component |

| TW548824B (en) * | 2002-09-16 | 2003-08-21 | Taiwan Semiconductor Mfg | Electrostatic discharge protection circuit having high substrate triggering efficiency and the related MOS transistor structure thereof |

| US6774417B1 (en) * | 2002-10-23 | 2004-08-10 | Lovoltech, Inc. | Electrostatic discharge protection device for integrated circuits |

| TW569418B (en) * | 2002-11-07 | 2004-01-01 | Taiwan Semiconductor Mfg | Low-capacitance electrostatic discharge protection apparatus and its manufacturing method |

| JP4017573B2 (ja) * | 2003-07-17 | 2007-12-05 | 沖電気工業株式会社 | ダイオード |

| US7067350B1 (en) * | 2005-01-31 | 2006-06-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of manufacturing a semiconductor device using electrical contacts formed in an isolation layer |

-

2004

- 2004-04-01 JP JP2004109162A patent/JP3760945B2/ja not_active Expired - Fee Related

-

2005

- 2005-03-31 US US11/095,709 patent/US7394134B2/en not_active Expired - Lifetime

-

2008

- 2008-05-23 US US12/126,473 patent/US8076748B2/en not_active Expired - Fee Related

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101212267B1 (ko) | 2005-12-29 | 2012-12-14 | 매그나칩 반도체 유한회사 | 고전압 숏키 다이오드 |

| JP2008098201A (ja) * | 2006-10-05 | 2008-04-24 | Denso Corp | 半導体装置 |

| JP2016068650A (ja) * | 2014-09-29 | 2016-05-09 | 日立オートモティブシステムズ株式会社 | 電子制御装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050218454A1 (en) | 2005-10-06 |

| US7394134B2 (en) | 2008-07-01 |

| JP3760945B2 (ja) | 2006-03-29 |

| US20080224219A1 (en) | 2008-09-18 |

| US8076748B2 (en) | 2011-12-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8008723B2 (en) | Semiconductor device including a plurality of diffusion layers and diffusion resistance layer | |

| TWI496245B (zh) | Semiconductor device | |

| JP3237110B2 (ja) | 半導体装置 | |

| US7183612B2 (en) | Semiconductor device having an electrostatic discharge protecting element | |

| US8076748B2 (en) | Semiconductor device | |

| KR100885829B1 (ko) | 반도체 디바이스 및 보호 회로 | |

| CN103022030B (zh) | 半导体装置 | |

| JPWO2017212644A1 (ja) | 半導体装置 | |

| US20040016971A1 (en) | Diode and producing method thereof | |

| JP7043194B2 (ja) | 静電保護素子および半導体装置 | |

| JP2008091687A (ja) | 半導体集積回路装置 | |

| JP2004363136A (ja) | 半導体回路装置 | |

| JP3128334B2 (ja) | 半導体デバイス及びその製造方法 | |

| WO2023167083A1 (ja) | 半導体集積回路装置 | |

| JP3574359B2 (ja) | 半導体装置 | |

| US7595245B2 (en) | Semiconductor device having a gate electrode material feature located adjacent a gate width side of its gate electrode and a method of manufacture therefor | |

| JP4746734B2 (ja) | 半導体装置 | |

| JP4205732B2 (ja) | 半導体集積回路装置 | |

| JP2012028380A (ja) | 半導体装置 | |

| JP2007335463A (ja) | 静電気放電保護素子および半導体装置 | |

| JP2007242899A (ja) | 半導体装置 | |

| KR20050074206A (ko) | 정전기 보호 회로를 갖는 반도체 장치들 및 그 제조 방법들 | |

| JP2008078579A (ja) | 半導体装置およびその製造方法 | |

| JP2005347293A (ja) | 半導体装置およびその製造方法 | |

| JP2003318281A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050902 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20051220 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060102 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 3760945 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100120 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110120 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110120 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120120 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120120 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130120 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130120 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140120 Year of fee payment: 8 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |