JP2005190036A - 記憶制御装置及び記憶制御装置の制御方法 - Google Patents

記憶制御装置及び記憶制御装置の制御方法 Download PDFInfo

- Publication number

- JP2005190036A JP2005190036A JP2003428624A JP2003428624A JP2005190036A JP 2005190036 A JP2005190036 A JP 2005190036A JP 2003428624 A JP2003428624 A JP 2003428624A JP 2003428624 A JP2003428624 A JP 2003428624A JP 2005190036 A JP2005190036 A JP 2005190036A

- Authority

- JP

- Japan

- Prior art keywords

- logical volume

- control device

- storage control

- channel adapter

- written

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0629—Configuration or reconfiguration of storage systems

- G06F3/0634—Configuration or reconfiguration of storage systems by changing the state or mode of one or more devices

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/0625—Power saving in storage systems

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0683—Plurality of storage devices

- G06F3/0689—Disk arrays, e.g. RAID, JBOD

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Human Computer Interaction (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Information Retrieval, Db Structures And Fs Structures Therefor (AREA)

Abstract

相対的にMTBFが短いHDDを使用する記憶制御装置において、MTBFから推定される障害発生までの期間をできるだけ長くすること。

【解決手段】

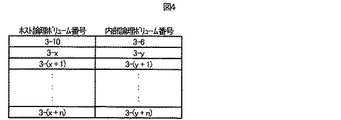

当該HDD上のデータに対して、ホストコンピュータからアクセスが可能なHDDについては、スピンドルモータを回転させ、ホストコンピュータからのアクセスがないと明確に分かっているHDDについてはスピンドルモータを停止させる制御を行う。ホストコンピュータからのアクセスの可/不可については、当該HDDが提供する記憶領域(内部論理ボリューム)が、ホストコンピュータにより認識されてアクセスが可能であるホスト論理ボリュームに対応付けられているかどうかによって判断する。

【選択図】図7

Description

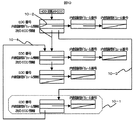

このステップ1は、アプリケーション・プログラム3−12が必要に応じて実施する。例えば、アプリケーション・プログラム3−12の起動時や、アプリケーション・プログラム3−12のオペレータが、記憶制御装置3−1の物理構成または論理構成が変わったことを知ったときに行う明示的な操作契機で、である。

始めに行われる処理は、領域7−23に書き込まれた情報(切り替えの対象とするホスト論理ボリューム番号と新規に対応付ける内部論理ボリュームの番号)の調査である(8−1)。

この図9に例示されるような構造体は、共有メモリ7−16中に構成情報7−17の一つとして保持される。

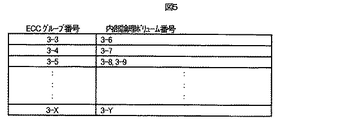

これにより領域7−23で指定されたホスト論理ボリュームに現在対応付けられている内部論理ボリュームを含むECCグループに関する情報が削除され、当該ECC中に回転しているスピンドルモータを停止させたHDDが存在しないという状態になる。

これにより破線で囲まれた部分が、図10に例示するようなのスピンドルモータが回転しているHDDを持つECCグループの番号と、そのECCグループにより提供される内部論理ボリュームの番号を保持する構造体に組み込まれ、以降当該ECCグループ中のHDDのスピンドルモータは回転しているものと見なされる。

1−1・・・記憶制御装置

1−3・・・チャネルアダプタ

1−6・・・ハードディスクドライブ

1−7・・・ディスクアダプタ

1−9・・・接続部

1−10・・・共有メモリ

1−11・・・キャッシュメモリ

Claims (20)

- 上位装置に接続され、前記上位装置に対して第一の論理ボリュームを提供して、前記上位装置から前記第一の論理ボリュームに宛てて送られるデータを受けるチャネルアダプタと、

前記チャネルアダプタに接続され、前記上位装置との間でやり取りされるデータ、前記上位装置との間でやり取りされるデータに関する制御情報、及び自記憶制御装置の構成に関する構成情報が保存されるメモリと、

前記上位装置から前記第一の論理ボリュームに宛てて送られたデータを、前記第一の論理ボリュームに対応しており前記チャネルアダプタとのデータの送受信においてデータの格納領域として用いられる第二の論理ボリュームに対するものとして、前記メモリから読み出し又は前記メモリに対して書き込むように制御するディスクアダプタと、

前記チャネルアダプタ、前記メモリ及び前記ディスクアダプタを接続する接続装置と、

前記ディスクアダプタと接続され、前記ディスクアダプタの制御によって、前記第二の論理ボリュームに対するデータが冗長関係を有するデータ群として書き込まれる複数のディスクドライブとを有し、

前記チャネルアダプタは、前記上位装置から前記メモリ内の前記構成情報が読み出される場合に利用される制御用論理ボリュームを前記上位装置に対して提供するものであり、前記上位装置から前記制御用論理ボリュームに宛てて発行された切り替え指示に応じて、前記第二の論理ボリュームに代えて、他の第二の論理ボリュームを前記第一の論理ボリュームに対応付けて、前記他の第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータを動作させるプロセッサを有するものであることを特徴とする記憶制御装置。 - 請求項1に記載の記憶制御装置において、

前記チャネルアダプタの前記プロセッサは、前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータを停止させるものであることを特徴とする記憶制御装置。 - 請求項1に記載の記憶制御装置において、

前記チャネルアダプタの前記プロセッサは、前記切り替え指示によって指定された前記他の第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータが動作中か否かを判断し、前記動作中であればそのまま動作を継続させ、前記動作中でなければ、前記他の第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータを動作させるものであることを特徴とする記憶制御装置。 - 請求項1に記載の記憶制御装置において、

前記チャネルアダプタの前記プロセッサは、前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのなかに、前記上位装置に対して提供されている他の第一の論理ボリュームに対応する他の第二の論理ボリュームに対応しているものがあれば、前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブの動作を継続させるものである、ことを特徴とする記憶制御装置。 - 請求項1に記載の記憶制御装置において、

前記チャネルアダプタの前記プロセッサは、前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのなかに、前記上位装置に対して提供されている他の第一の論理ボリュームに対応する他の第二の論理ボリュームに対応しているものがなければ、前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブの動作を停止させるものである、ことを特徴とする記憶制御装置。 - 請求項1に記載の記憶制御装置において、

前記チャネルアダプタの前記プロセッサは、前記制御用論理ボリュームに宛てて前記上位装置から送られたコマンドの種類が書き込みコマンドである場合、前記書き込みコマンドの内容を前記制御用論理ボリュームへ書き込み、前記書き込みコマンドの内容が前記切り替え指示であることを判断するものであることを特徴とする記憶制御装置。 - 請求項1に記載の記憶制御装置において、

前記チャネルアダプタの前記プロセッサは、前記制御用論理ボリュームに宛てて前記上位装置から送られたコマンドの種類が読み出しコマンドである場合、前記読み出しコマンドの内容が前記構成情報であることを判断して、前記メモリから前記構成情報を読み出して、前記上位装置に対して送信するものであることを特徴とする記憶制御装置。 - 請求項1に記載の記憶制御装置において、

前記チャネルアダプタの前記プロセッサの指示に応じて、前記第二の論理ボリュームに代えて、前記他の第二の論理ボリュームを前記第一の論理ボリュームに対応付ける対応付け切り替え装置とを有することを特徴とする記憶制御装置。 - 請求項1に記載の記憶制御装置において、

前記チャネルアダプタの前記プロセッサの指示に応じて、前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータを停止させ、前記他の第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータを動作させる電源制御装置とを有することを特徴とする記憶制御装置。 - 請求項1に記載の記憶制御装置において、

前記チャネルアダプタの前記プロセッサは、前記上位装置から送られたコマンドが前記第一の論理ボリューム宛てである場合には、前記上位装置から送られたコマンドをデータの書き込み又は読み出しに関するコマンドであると判断し、前記上位装置から送られたコマンドが前記制御用論理ボリューム宛てである場合には、前記上位装置から送られたコマンドを制御情報に関するコマンドであると判断するものであることを特徴とする記憶制御装置。 - 上位装置に接続され、前記上位装置に対して第一の論理ボリュームを提供して、前記上位装置から前記第一の論理ボリュームに宛てて送られるデータを受けるチャネルアダプタと、

前記チャネルアダプタに接続され、前記上位装置との間でやり取りされるデータ、前記上位装置との間でやり取りされるデータに関する制御情報、及び自記憶制御装置の構成に関する構成情報が保存されるメモリと、

前記上位装置から前記第一の論理ボリュームに宛てて送られたデータを、前記第一の論理ボリュームに対応しており前記チャネルアダプタとのデータの送受信においてデータの格納領域として用いられる第二の論理ボリュームに対するものとして、前記メモリから読み出し又は前記メモリに対して書き込むように制御するディスクアダプタと、

前記チャネルアダプタ、前記メモリ及び前記ディスクアダプタを接続する接続装置と、

前記ディスクアダプタと接続され、前記ディスクアダプタの制御によって、前記第二の論理ボリュームに対するデータが冗長関係を有するデータ群として書き込まれる複数のディスクドライブとを有する記憶制御装置の制御方法において、

前記チャネルアダプタは、

前記上位装置から前記メモリ内の前記構成情報が読み出される場合に利用される制御用論理ボリュームを前記上位装置に対して提供し、

前記上位装置から前記制御用論理ボリュームに宛てて発行された切り替え指示に応じて、前記第二の論理ボリュームに代えて、他の第二の論理ボリュームを前記第一の論理ボリュームに対応付けて、前記他の第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータを動作させる、

ことを特徴とする記憶制御装置の制御方法。 - 請求項11に記載の記憶制御装置の制御方法において、

前記チャネルアダプタは、

前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータを停止させる、

ことを特徴とする記憶制御装置の制御方法。 - 請求項11に記載の記憶制御装置の制御方法において、

前記チャネルアダプタは、

前記切り替え指示によって指定された前記他の第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータが動作中か否かを判断し、

前記動作中であればそのまま動作を継続させ、

前記動作中でなければ、前記他の第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータを動作させる、

ことを特徴とする記憶制御装置の制御方法。 - 請求項11に記載の記憶制御装置の制御方法において、

前記チャネルアダプタは、

前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのなかに、前記上位装置に対して提供されている他の第一の論理ボリュームに対応する他の第二の論理ボリュームに対応しているものがあれば、前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブの動作を継続させる、

ことを特徴とする記憶制御装置の制御方法。 - 請求項11に記載の記憶制御装置の制御方法において、

前記チャネルアダプタは、

前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのなかに、前記上位装置に対して提供されている他の第一の論理ボリュームに対応する他の第二の論理ボリュームに対応しているものがなければ、前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブの動作を停止させる、

ことを特徴とする記憶制御装置の制御方法。 - 請求項11に記載の記憶制御装置の制御方法において、

前記チャネルアダプタは、

前記制御用論理ボリュームに宛てて前記上位装置から送られたコマンドの種類が書き込みコマンドである場合、

前記書き込みコマンドの内容を前記制御用論理ボリュームへ書き込み、

前記書き込みコマンドの内容が前記切り替え指示であることを判断する、

ことを特徴とする記憶制御装置の制御方法。 - 請求項11に記載の記憶制御装置の制御方法において、

前記チャネルアダプタは、

前記制御用論理ボリュームに宛てて前記上位装置から送られたコマンドの種類が読み出しコマンドである場合、

前記読み出しコマンドの内容が前記構成情報であることを判断し、

前記メモリから前記構成情報を読み出し、

前記読み出された前記構成情報を前記上位装置に対して送信する、

ことを特徴とする記憶制御装置の制御方法。 - 請求項11に記載の記憶制御装置の制御方法において、

前記記憶制御装置は、対応付け切替え装置とを有するものであり、

前記対応付け切替え装置は、

前記チャネルアダプタの指示に応じて、前記第二の論理ボリュームに代えて、前記他の第二の論理ボリュームを前記第一の論理ボリュームに対応付ける、

ことを特徴とする記憶制御装置の制御方法。 - 請求項11に記載の記憶制御装置の制御方法において、

前記記憶制御装置は、電源制御装置とを有するものであり、

前記電源制御装置は、

前記チャネルアダプタの前記プロセッサの指示に応じて、

前記切り替え指示に応じて切り替えられる前記第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータを停止させ、

前記他の第二の論理ボリュームに対応しており冗長関係を有するデータ群が書き込まれる複数のディスクドライブのスピンドルモータを動作させる、

ことを特徴とする記憶制御装置の制御方法。 - 請求項11に記載の記憶制御装置の制御方法において、

前記チャネルアダプタは、

前記上位装置から送られたコマンドが前記第一の論理ボリューム宛てである場合には、前記上位装置から送られたコマンドをデータの書き込み又は読み出しに関するコマンドであると判断し、

前記上位装置から送られたコマンドが前記制御用論理ボリューム宛てである場合には、前記上位装置から送られたコマンドを制御情報に関するコマンドであると判断する、

ことを特徴とする記憶制御装置の制御方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003428624A JP2005190036A (ja) | 2003-12-25 | 2003-12-25 | 記憶制御装置及び記憶制御装置の制御方法 |

| US10/803,910 US7360017B2 (en) | 2003-12-25 | 2004-03-19 | Storage control device for longevity of the disk spindles based upon access of hard disk drives |

| US11/311,155 US7669016B2 (en) | 2003-12-25 | 2005-12-20 | Memory control device and method for controlling the same |

| US12/688,564 US7975113B2 (en) | 2003-12-25 | 2010-01-15 | Memory control device and method for controlling the same |

| US13/160,085 US8516204B2 (en) | 2003-12-25 | 2011-06-14 | Memory control device and method for controlling the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003428624A JP2005190036A (ja) | 2003-12-25 | 2003-12-25 | 記憶制御装置及び記憶制御装置の制御方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006335449A Division JP5081441B2 (ja) | 2006-12-13 | 2006-12-13 | 記憶制御装置及び記憶制御装置の制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005190036A true JP2005190036A (ja) | 2005-07-14 |

| JP2005190036A5 JP2005190036A5 (ja) | 2007-02-01 |

Family

ID=34697531

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003428624A Pending JP2005190036A (ja) | 2003-12-25 | 2003-12-25 | 記憶制御装置及び記憶制御装置の制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (4) | US7360017B2 (ja) |

| JP (1) | JP2005190036A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008102667A (ja) * | 2006-10-18 | 2008-05-01 | Hitachi Ltd | 論理区画ごとに電源を管理する計算機システム、ストレージ装置及びそれらの制御方法 |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4463042B2 (ja) | 2003-12-26 | 2010-05-12 | 株式会社日立製作所 | ボリュームの動的割り付け機能を有する記憶装置システム |

| US9264384B1 (en) | 2004-07-22 | 2016-02-16 | Oracle International Corporation | Resource virtualization mechanism including virtual host bus adapters |

| US9813283B2 (en) | 2005-08-09 | 2017-11-07 | Oracle International Corporation | Efficient data transfer between servers and remote peripherals |

| JP4897387B2 (ja) * | 2006-08-10 | 2012-03-14 | 株式会社日立製作所 | ストレージ装置およびこれを用いたデータの管理方法 |

| US8700846B2 (en) * | 2006-12-05 | 2014-04-15 | Netapp, Inc. | Multiple instances of mapping configurations in a storage system or storage appliance |

| US7761642B2 (en) * | 2006-12-22 | 2010-07-20 | Lsi Corporation | Serial advanced technology attachment (SATA) and serial attached small computer system interface (SCSI) (SAS) bridging |

| US8473779B2 (en) * | 2008-02-29 | 2013-06-25 | Assurance Software And Hardware Solutions, Llc | Systems and methods for error correction and detection, isolation, and recovery of faults in a fail-in-place storage array |

| US7882389B2 (en) * | 2008-11-18 | 2011-02-01 | International Business Machines Corporation | Dynamic reassignment of devices attached to redundant controllers |

| US8201001B2 (en) * | 2009-08-04 | 2012-06-12 | Lsi Corporation | Method for optimizing performance and power usage in an archival storage system by utilizing massive array of independent disks (MAID) techniques and controlled replication under scalable hashing (CRUSH) |

| US9973446B2 (en) | 2009-08-20 | 2018-05-15 | Oracle International Corporation | Remote shared server peripherals over an Ethernet network for resource virtualization |

| US9331963B2 (en) | 2010-09-24 | 2016-05-03 | Oracle International Corporation | Wireless host I/O using virtualized I/O controllers |

| US9720606B2 (en) | 2010-10-26 | 2017-08-01 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Methods and structure for online migration of data in storage systems comprising a plurality of storage devices |

| US9083550B2 (en) | 2012-10-29 | 2015-07-14 | Oracle International Corporation | Network virtualization over infiniband |

| US10496531B1 (en) * | 2017-04-27 | 2019-12-03 | EMC IP Holding Company LLC | Optimizing virtual storage groups by determining and optimizing associations between virtual devices and physical devices |

Citations (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03292556A (ja) * | 1990-04-11 | 1991-12-24 | Nec Corp | メモリマツプドデバイス制御方式 |

| JPH08202647A (ja) * | 1995-01-26 | 1996-08-09 | Mutsumi Karauchi | コンピュータ入出力装置の仮想ポートについて |

| JP2000112666A (ja) * | 1998-10-01 | 2000-04-21 | Hitachi Ltd | ディスク制御装置 |

| JP2001075853A (ja) * | 1999-09-03 | 2001-03-23 | Hitachi Ltd | 計算機システム、及び該計算機システムに用いられる計算機並びに記憶装置 |

| JP2001290608A (ja) * | 2000-04-10 | 2001-10-19 | Hitachi Ltd | ディスク制御装置 |

| WO2002002746A2 (en) * | 2000-06-29 | 2002-01-10 | University Of Connecticut | Coiled-coil mediated heterodimerization functional interaction trap |

| JP2002091706A (ja) * | 2000-06-02 | 2002-03-29 | Compaq Information Technologies Group Lp | 仮想記憶システム |

| JP2002099495A (ja) * | 2000-09-26 | 2002-04-05 | Fujitsu Ltd | クライアントサーバシステム、サーバ及びクライアント |

| JP2002163076A (ja) * | 2000-08-04 | 2002-06-07 | Hitachi Ltd | 連続稼動に対する信頼性を高めた情報記憶装置及び記録制御方法 |

| JP2003006137A (ja) * | 2001-06-21 | 2003-01-10 | Fujitsu Ltd | ストレージアクセスシステム |

| WO2003067385A2 (en) * | 2002-02-05 | 2003-08-14 | Asaca Corporation | Data storage system |

| JP2003280823A (ja) * | 2002-02-05 | 2003-10-02 | Quantum Corp | ホストシステムからデータを記憶する記憶システムおよびその方法 |

| JP2003316522A (ja) * | 2002-04-26 | 2003-11-07 | Hitachi Ltd | 計算機システムおよび計算機システムの制御方法 |

| JP2003316616A (ja) * | 2002-04-24 | 2003-11-07 | Hitachi Ltd | 計算機システム |

Family Cites Families (106)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4475194A (en) * | 1982-03-30 | 1984-10-02 | International Business Machines Corporation | Dynamic replacement of defective memory words |

| US4486739A (en) * | 1982-06-30 | 1984-12-04 | International Business Machines Corporation | Byte oriented DC balanced (0,4) 8B/10B partitioned block transmission code |

| US4833605A (en) * | 1984-08-16 | 1989-05-23 | Mitsubishi Denki Kabushiki Kaisha | Cascaded information processing module having operation unit, parallel port, and serial port for concurrent data transfer and data processing |

| US4740916A (en) * | 1985-12-19 | 1988-04-26 | International Business Machines Corporation | Reconfigurable contiguous address space memory system including serially connected variable capacity memory modules and a split address bus |

| US4723120A (en) * | 1986-01-14 | 1988-02-02 | International Business Machines Corporation | Method and apparatus for constructing and operating multipoint communication networks utilizing point-to point hardware and interfaces |

| US5053947A (en) * | 1989-09-29 | 1991-10-01 | Allegro Microsystems, Inc. | Extended multistation bus system and method |

| IL96808A (en) * | 1990-04-18 | 1996-03-31 | Rambus Inc | Introductory / Origin Circuit Agreed Using High-Performance Brokerage |

| US5197055A (en) * | 1990-05-21 | 1993-03-23 | International Business Machines Corporation | Idle demount in an automated storage library |

| US5193184A (en) | 1990-06-18 | 1993-03-09 | Storage Technology Corporation | Deleted data file space release system for a dynamically mapped virtual data storage subsystem |

| US5287531A (en) * | 1990-10-31 | 1994-02-15 | Compaq Computer Corp. | Daisy-chained serial shift register for determining configuration of removable circuit boards in a computer system |

| US5214747A (en) * | 1990-12-24 | 1993-05-25 | Eastman Kodak Company | Segmented neural network with daisy chain control |

| US5745789A (en) | 1992-01-23 | 1998-04-28 | Hitachi, Ltd. | Disc system for holding data in a form of a plurality of data blocks dispersed in a plurality of disc units connected by a common data bus |

| US5387911A (en) * | 1992-02-21 | 1995-02-07 | Gleichert; Marc C. | Method and apparatus for transmitting and receiving both 8B/10B code and 10B/12B code in a switchable 8B/10B transmitter and receiver |

| US5715407A (en) * | 1992-03-06 | 1998-02-03 | Rambus, Inc. | Process and apparatus for collision detection on a parallel bus by monitoring a first line of the bus during even bus cycles for indications of overlapping packets |

| US5394532A (en) | 1992-04-15 | 1995-02-28 | Storage Technology Corporation | Disk drive array memory system having instant format capability |

| JPH064979A (ja) | 1992-06-18 | 1994-01-14 | Ricoh Co Ltd | バッテリにより駆動されるデータ機器のディスク記憶装置の 節電力駆動制御方法 |

| WO1994003901A1 (en) * | 1992-08-10 | 1994-02-17 | Monolithic System Technology, Inc. | Fault-tolerant, high-speed bus system and bus interface for wafer-scale integration |

| US5404485A (en) | 1993-03-08 | 1995-04-04 | M-Systems Flash Disk Pioneers Ltd. | Flash file system |

| US5531135A (en) * | 1993-06-11 | 1996-07-02 | Volkswagon Ag | Pedal arrangement for a motor vehicle |

| US5392244A (en) * | 1993-08-19 | 1995-02-21 | Hewlett-Packard Company | Memory systems with data storage redundancy management |

| JP2858542B2 (ja) * | 1994-06-03 | 1999-02-17 | インターナショナル・ビジネス・マシーンズ・コーポレイション | コンピュータ用ディスク・ドライブの電力消費を節減する方法及び装置 |

| KR0143529B1 (ko) * | 1994-06-22 | 1998-07-15 | 김광호 | 디스크 회전 제어 장치 및 방법 |

| US5611055A (en) * | 1994-09-27 | 1997-03-11 | Novalink Technologies | Method and apparatus for implementing a PCMCIA auxiliary port connector for selectively communicating with peripheral devices |

| US5629685A (en) * | 1995-02-23 | 1997-05-13 | International Business Machines Corporation | Segmentable addressable modular communication network hubs |

| IN188196B (ja) * | 1995-05-15 | 2002-08-31 | Silicon Graphics Inc | |

| US5860137A (en) * | 1995-07-21 | 1999-01-12 | Emc Corporation | Dynamic load balancing |

| JP3202600B2 (ja) | 1996-06-27 | 2001-08-27 | 日本電気株式会社 | 磁気ディスク装置 |

| US5926838A (en) * | 1997-03-19 | 1999-07-20 | Micron Electronics | Interface for high speed memory |

| US6292903B1 (en) * | 1997-07-09 | 2001-09-18 | International Business Machines Corporation | Smart memory interface |

| US6304940B1 (en) * | 1997-08-14 | 2001-10-16 | International Business Machines Corporation | Shared direct access storage system for MVS and FBA processors |

| US6038639A (en) | 1997-09-09 | 2000-03-14 | Storage Technology Corporation | Data file storage management system for snapshot copy operations |

| US6125373A (en) * | 1997-09-19 | 2000-09-26 | Microsoft Corporation | Identifying a driver that is an owner of an active mount point |

| JP3445476B2 (ja) * | 1997-10-02 | 2003-09-08 | 株式会社東芝 | 半導体メモリシステム |

| US5963971A (en) * | 1997-10-09 | 1999-10-05 | International Business Machines Corporation | Method and apparatus for handling audit requests of logical volumes in a virtual media server |

| US6378018B1 (en) * | 1997-10-10 | 2002-04-23 | Intel Corporation | Memory device and system including a low power interface |

| US6105103A (en) * | 1997-12-19 | 2000-08-15 | Lsi Logic Corporation | Method for mapping in dynamically addressed storage subsystems |

| US6725331B1 (en) * | 1998-01-07 | 2004-04-20 | Emc Corporation | Method and apparatus for managing the dynamic assignment resources in a data storage system |

| US6096091A (en) * | 1998-02-24 | 2000-08-01 | Advanced Micro Devices, Inc. | Dynamically reconfigurable logic networks interconnected by fall-through FIFOs for flexible pipeline processing in a system-on-a-chip |

| JPH11353228A (ja) * | 1998-06-10 | 1999-12-24 | Mitsubishi Electric Corp | メモリモジュールシステム |

| US6591356B2 (en) | 1998-07-17 | 2003-07-08 | Roxio, Inc. | Cluster buster |

| US6496540B1 (en) * | 1998-07-22 | 2002-12-17 | International Business Machines Corporation | Transformation of parallel interface into coded format with preservation of baud-rate |

| JP2000112822A (ja) | 1998-10-01 | 2000-04-21 | Hitachi Ltd | アーカイバル機能を有するディスク制御方式 |

| US6167459A (en) * | 1998-10-07 | 2000-12-26 | International Business Machines Corporation | System for reassigning alias addresses to an input/output device |

| US5995405A (en) * | 1998-10-27 | 1999-11-30 | Micron Technology, Inc. | Memory module with flexible serial presence detect configuration |

| US6349940B1 (en) * | 1999-01-25 | 2002-02-26 | Betty Florene Nimry | Collapsible, game card holding means |

| US6356915B1 (en) | 1999-02-22 | 2002-03-12 | Starbase Corp. | Installable file system having virtual file system drive, virtual device driver, and virtual disks |

| JP3837953B2 (ja) | 1999-03-12 | 2006-10-25 | 株式会社日立製作所 | 計算機システム |

| US6176459B1 (en) * | 1999-03-29 | 2001-01-23 | Attwood Corporation | Self-locking angularly-tilting seat support |

| JP4325817B2 (ja) | 1999-04-05 | 2009-09-02 | 株式会社日立製作所 | ディスクアレイ装置 |

| US6754661B1 (en) | 1999-07-13 | 2004-06-22 | Microsoft Corporation | Hierarchical storage systems for holding evidentiary objects and methods of creating and operating upon hierarchical storage systems |

| US6513091B1 (en) * | 1999-11-12 | 2003-01-28 | International Business Machines Corporation | Data routing using status-response signals |

| US6526469B1 (en) * | 1999-11-12 | 2003-02-25 | International Business Machines Corporation | Bus architecture employing varying width uni-directional command bus |

| US6557069B1 (en) * | 1999-11-12 | 2003-04-29 | International Business Machines Corporation | Processor-memory bus architecture for supporting multiple processors |

| US6502161B1 (en) * | 2000-01-05 | 2002-12-31 | Rambus Inc. | Memory system including a point-to-point linked memory subsystem |

| US6839827B1 (en) | 2000-01-18 | 2005-01-04 | International Business Machines Corporation | Method, system, program, and data structures for mapping logical blocks to physical blocks |

| US6834324B1 (en) | 2000-04-10 | 2004-12-21 | Storage Technology Corporation | System and method for virtual tape volumes |

| US6622217B2 (en) * | 2000-06-10 | 2003-09-16 | Hewlett-Packard Development Company, L.P. | Cache coherence protocol engine system and method for processing memory transaction in distinct address subsets during interleaved time periods in a multiprocessor system |

| US6697919B2 (en) * | 2000-06-10 | 2004-02-24 | Hewlett-Packard Development Company, L.P. | System and method for limited fanout daisy chaining of cache invalidation requests in a shared-memory multiprocessor system |

| US6760828B1 (en) | 2000-06-27 | 2004-07-06 | Emc Corporation | Method and apparatus for using logical volume identifiers for tracking or identifying logical volume stored in the storage system |

| US6708265B1 (en) * | 2000-06-27 | 2004-03-16 | Emc Corporation | Method and apparatus for moving accesses to logical entities from one storage element to another storage element in a computer storage system |

| US6622177B1 (en) * | 2000-07-27 | 2003-09-16 | International Business Machines Corporation | Dynamic management of addresses to an input/output (I/O) device |

| EP1178390A3 (en) | 2000-08-04 | 2006-12-27 | Hitachi, Ltd. | Information storage system with increased reliability for continuous operation, and recording control method |

| US6977927B1 (en) * | 2000-09-18 | 2005-12-20 | Hewlett-Packard Development Company, L.P. | Method and system of allocating storage resources in a storage area network |

| US6625687B1 (en) * | 2000-09-18 | 2003-09-23 | Intel Corporation | Memory module employing a junction circuit for point-to-point connection isolation, voltage translation, data synchronization, and multiplexing/demultiplexing |

| US6317352B1 (en) * | 2000-09-18 | 2001-11-13 | Intel Corporation | Apparatus for implementing a buffered daisy chain connection between a memory controller and memory modules |

| US6553450B1 (en) * | 2000-09-18 | 2003-04-22 | Intel Corporation | Buffer to multiply memory interface |

| US6349913B1 (en) * | 2000-10-06 | 2002-02-26 | Collins & Aikman Products Co. | Cup holder having a vertically oriented drawer |

| US7792923B2 (en) * | 2000-10-13 | 2010-09-07 | Zhe Khi Pak | Disk system adapted to be directly attached to network |

| US6510100B2 (en) * | 2000-12-04 | 2003-01-21 | International Business Machines Corporation | Synchronous memory modules and memory systems with selectable clock termination |

| US6880058B2 (en) * | 2000-12-07 | 2005-04-12 | Hitachi, Ltd. | Computer system with storage system having re-configurable logical volumes |

| US6493250B2 (en) * | 2000-12-28 | 2002-12-10 | Intel Corporation | Multi-tier point-to-point buffered memory interface |

| WO2002065275A1 (en) * | 2001-01-11 | 2002-08-22 | Yottayotta, Inc. | Storage virtualization system and methods |

| US7007141B2 (en) * | 2001-01-30 | 2006-02-28 | Data Domain, Inc. | Archival data storage system and method |

| US6606690B2 (en) * | 2001-02-20 | 2003-08-12 | Hewlett-Packard Development Company, L.P. | System and method for accessing a storage area network as network attached storage |

| JP4105398B2 (ja) | 2001-02-28 | 2008-06-25 | 株式会社日立製作所 | 情報処理システム |

| JP2002288108A (ja) | 2001-03-28 | 2002-10-04 | Hitachi Ltd | 外部記憶装置 |

| JP4121255B2 (ja) * | 2001-06-12 | 2008-07-23 | 株式会社日立製作所 | クラスタ構成記憶システム |

| JP4144727B2 (ja) | 2001-07-02 | 2008-09-03 | 株式会社日立製作所 | 情報処理システム、記憶領域提供方法、およびデータ保持管理装置 |

| US6820704B2 (en) * | 2001-08-08 | 2004-11-23 | Smith International, Inc. | Rock bit seal with extrusion prevention member |

| US6519678B1 (en) * | 2001-09-10 | 2003-02-11 | International Business Machines Corporation | Virtualization of data storage drives of an automated data storage library |

| US6902675B2 (en) * | 2001-10-19 | 2005-06-07 | Mississippi State University | Method to control off-flavor in water and aquaculture products |

| JP4087097B2 (ja) | 2001-11-12 | 2008-05-14 | 株式会社日立製作所 | データベース管理システム情報を考慮したデータ再配置方法およびデータ再配置を行う計算機システム |

| US7548975B2 (en) * | 2002-01-09 | 2009-06-16 | Cisco Technology, Inc. | Methods and apparatus for implementing virtualization of storage within a storage area network through a virtual enclosure |

| US7007152B2 (en) * | 2001-12-28 | 2006-02-28 | Storage Technology Corporation | Volume translation apparatus and method |

| JP3993773B2 (ja) | 2002-02-20 | 2007-10-17 | 株式会社日立製作所 | ストレージサブシステム、記憶制御装置及びデータコピー方法 |

| US20030156345A1 (en) * | 2002-02-20 | 2003-08-21 | Fayeulle Serge J. | Data storage device and method for spindle power control |

| JP4032777B2 (ja) | 2002-03-05 | 2008-01-16 | ソニー株式会社 | 撮像装置および撮像装置の制御方法並びに撮像装置の収納装置 |

| US7185169B2 (en) | 2002-04-26 | 2007-02-27 | Voom Technologies, Inc. | Virtual physical drives |

| JP4704659B2 (ja) | 2002-04-26 | 2011-06-15 | 株式会社日立製作所 | 記憶装置システムの制御方法および記憶制御装置 |

| US7035657B2 (en) | 2002-05-08 | 2006-04-25 | Qualcomm Inc. | Method and apparatus for supporting application-layer media multicasting |

| US20030212859A1 (en) | 2002-05-08 | 2003-11-13 | Ellis Robert W. | Arrayed data storage architecture with simultaneous command of multiple storage media |

| JP4100968B2 (ja) * | 2002-06-06 | 2008-06-11 | 株式会社日立製作所 | データマッピング管理装置 |

| DE10235798B4 (de) * | 2002-08-05 | 2004-09-23 | Siemens Ag | Verfahren und eine Vorrichtung zum Anmelden und Verbinden von R-Gesprächen mit intelligenten Netzwerkdiensten (IN-Diensten) |

| US7035972B2 (en) * | 2002-09-03 | 2006-04-25 | Copan Systems, Inc. | Method and apparatus for power-efficient high-capacity scalable storage system |

| JP4124331B2 (ja) | 2002-09-17 | 2008-07-23 | 株式会社日立製作所 | Dbms向け仮想ボリューム作成・管理方法 |

| US6857057B2 (en) * | 2002-10-03 | 2005-02-15 | Hewlett-Packard Development Company, L.P. | Virtual storage systems and virtual storage system operational methods |

| US7152142B1 (en) * | 2002-10-25 | 2006-12-19 | Copan Systems, Inc. | Method for a workload-adaptive high performance storage system with data protection |

| US6957303B2 (en) | 2002-11-26 | 2005-10-18 | Hitachi, Ltd. | System and managing method for cluster-type storage |

| JP2004178337A (ja) | 2002-11-28 | 2004-06-24 | Hitachi Ltd | 記憶装置システム、記憶装置、計算機およびプログラム |

| JP2004302751A (ja) | 2003-03-31 | 2004-10-28 | Hitachi Ltd | 計算機システムの性能管理方法、および、記憶装置の性能を管理する計算機システム |

| US7068455B2 (en) * | 2003-07-21 | 2006-06-27 | Matsushita Electric Industrial Co., Ltd. | Method and system for reducing power consumption in a rotatable media data storage device |

| US20050108375A1 (en) * | 2003-11-13 | 2005-05-19 | Michele Hallak-Stamler | Method and graphical user interface for managing and configuring multiple clusters of virtualization switches |

| US20050108374A1 (en) | 2003-11-14 | 2005-05-19 | Pierzga Wayne F. | Airborne radio relay system |

| US7701909B2 (en) * | 2004-02-17 | 2010-04-20 | Alcatel-Lucent Usa Inc. | Methods and devices for selecting sets of available sub-channels |

| JP2005266933A (ja) | 2004-03-16 | 2005-09-29 | Fujitsu Ltd | ストレージ管理システム及びストレージ管理方法 |

| JP4230410B2 (ja) | 2004-05-11 | 2009-02-25 | 株式会社日立製作所 | 仮想ストレージの通信品質制御装置 |

-

2003

- 2003-12-25 JP JP2003428624A patent/JP2005190036A/ja active Pending

-

2004

- 2004-03-19 US US10/803,910 patent/US7360017B2/en not_active Expired - Fee Related

-

2005

- 2005-12-20 US US11/311,155 patent/US7669016B2/en not_active Expired - Fee Related

-

2010

- 2010-01-15 US US12/688,564 patent/US7975113B2/en not_active Expired - Fee Related

-

2011

- 2011-06-14 US US13/160,085 patent/US8516204B2/en not_active Expired - Fee Related

Patent Citations (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03292556A (ja) * | 1990-04-11 | 1991-12-24 | Nec Corp | メモリマツプドデバイス制御方式 |

| JPH08202647A (ja) * | 1995-01-26 | 1996-08-09 | Mutsumi Karauchi | コンピュータ入出力装置の仮想ポートについて |

| JP2000112666A (ja) * | 1998-10-01 | 2000-04-21 | Hitachi Ltd | ディスク制御装置 |

| JP2001075853A (ja) * | 1999-09-03 | 2001-03-23 | Hitachi Ltd | 計算機システム、及び該計算機システムに用いられる計算機並びに記憶装置 |

| JP2001290608A (ja) * | 2000-04-10 | 2001-10-19 | Hitachi Ltd | ディスク制御装置 |

| JP2002091706A (ja) * | 2000-06-02 | 2002-03-29 | Compaq Information Technologies Group Lp | 仮想記憶システム |

| WO2002002746A2 (en) * | 2000-06-29 | 2002-01-10 | University Of Connecticut | Coiled-coil mediated heterodimerization functional interaction trap |

| JP2002163076A (ja) * | 2000-08-04 | 2002-06-07 | Hitachi Ltd | 連続稼動に対する信頼性を高めた情報記憶装置及び記録制御方法 |

| JP2002099495A (ja) * | 2000-09-26 | 2002-04-05 | Fujitsu Ltd | クライアントサーバシステム、サーバ及びクライアント |

| JP2003006137A (ja) * | 2001-06-21 | 2003-01-10 | Fujitsu Ltd | ストレージアクセスシステム |

| WO2003067385A2 (en) * | 2002-02-05 | 2003-08-14 | Asaca Corporation | Data storage system |

| JP2003280823A (ja) * | 2002-02-05 | 2003-10-02 | Quantum Corp | ホストシステムからデータを記憶する記憶システムおよびその方法 |

| JP2003316616A (ja) * | 2002-04-24 | 2003-11-07 | Hitachi Ltd | 計算機システム |

| JP2003316522A (ja) * | 2002-04-26 | 2003-11-07 | Hitachi Ltd | 計算機システムおよび計算機システムの制御方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008102667A (ja) * | 2006-10-18 | 2008-05-01 | Hitachi Ltd | 論理区画ごとに電源を管理する計算機システム、ストレージ装置及びそれらの制御方法 |

| US8458432B2 (en) | 2006-10-18 | 2013-06-04 | Hitachi, Ltd. | Computer system, storage system and method for controlling power supply based on logical partition |

Also Published As

| Publication number | Publication date |

|---|---|

| US20060101222A1 (en) | 2006-05-11 |

| US20050144383A1 (en) | 2005-06-30 |

| US7975113B2 (en) | 2011-07-05 |

| US20100122029A1 (en) | 2010-05-13 |

| US8516204B2 (en) | 2013-08-20 |

| US7360017B2 (en) | 2008-04-15 |

| US7669016B2 (en) | 2010-02-23 |

| US20110246718A1 (en) | 2011-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7975113B2 (en) | Memory control device and method for controlling the same | |

| JP3431972B2 (ja) | 仮想ディスクシステム | |

| US7707456B2 (en) | Storage system | |

| JP5124103B2 (ja) | 計算機システム | |

| JP4555036B2 (ja) | ストレージ装置及びストレージ装置のデバイス切替制御方法 | |

| US8612644B2 (en) | Storage apparatus and a data management method employing the storage apparatus | |

| US8089487B2 (en) | Storage control device and storage system | |

| EP1643353A2 (en) | Storage controller, storage control system and storage control method | |

| JP2009043030A (ja) | ストレージシステム | |

| JPH0683708A (ja) | データ記憶方法及び装置 | |

| JP2007156597A (ja) | ストレージ装置 | |

| JP2007328408A (ja) | ストレージシステム及び記憶制御装置 | |

| JP2006184949A (ja) | 記憶制御システム | |

| JP2007133821A (ja) | 機器停止を伴う仮想ボリューム制御方法 | |

| US20100115310A1 (en) | Disk array apparatus | |

| JP2002049511A (ja) | アドレスの割付変更方法及びこれを用いた外部記憶サブシステム | |

| CN116483263A (zh) | 一种存储系统的存储设备、存储系统 | |

| JP5594942B2 (ja) | 好適なゾーン・スケジューリング | |

| JP5081441B2 (ja) | 記憶制御装置及び記憶制御装置の制御方法 | |

| CN119728798B (zh) | 一种基于蓝光光盘库的虚拟磁带库网关系统及其管理方法 | |

| CN103780634A (zh) | 数据交互方法及装置 | |

| US8037268B2 (en) | Storage system and operation method thereof | |

| JP4530372B2 (ja) | 広域予備化した分散記憶システム | |

| JP2004078993A (ja) | 複合計算機システムおよび複合i/oシステム | |

| JP2004164657A (ja) | 複合計算機システムおよび複合i/oシステム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060424 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061213 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061213 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20061213 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20070227 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20090216 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100723 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110210 |