JP2004072060A - トランジスタとそれを用いた半導体メモリ、およびトランジスタの駆動方法 - Google Patents

トランジスタとそれを用いた半導体メモリ、およびトランジスタの駆動方法 Download PDFInfo

- Publication number

- JP2004072060A JP2004072060A JP2002322905A JP2002322905A JP2004072060A JP 2004072060 A JP2004072060 A JP 2004072060A JP 2002322905 A JP2002322905 A JP 2002322905A JP 2002322905 A JP2002322905 A JP 2002322905A JP 2004072060 A JP2004072060 A JP 2004072060A

- Authority

- JP

- Japan

- Prior art keywords

- source

- insulating film

- gate

- floating gate

- erasing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

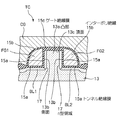

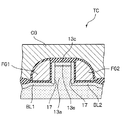

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/68—Floating-gate IGFETs

- H10D30/687—Floating-gate IGFETs having more than two programming levels

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

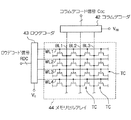

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

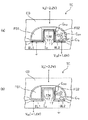

- G11C16/0441—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates

- G11C16/0458—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates comprising two or more independent floating gates which store independent data

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

- H10B41/42—Simultaneous manufacture of periphery and memory cells

- H10B41/43—Simultaneous manufacture of periphery and memory cells comprising only one type of peripheral transistor

- H10B41/48—Simultaneous manufacture of periphery and memory cells comprising only one type of peripheral transistor with a tunnel dielectric layer also being used as part of the peripheral transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0411—Manufacture or treatment of FETs having insulated gates [IGFET] of FETs having floating gates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/031—Manufacture or treatment of data-storage electrodes

- H10D64/035—Manufacture or treatment of data-storage electrodes comprising conductor-insulator-conductor-insulator-semiconductor structures

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0491—Virtual ground arrays

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

- Read Only Memory (AREA)

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002322905A JP2004072060A (ja) | 2001-11-22 | 2002-11-06 | トランジスタとそれを用いた半導体メモリ、およびトランジスタの駆動方法 |

| KR10-2004-7007756A KR20040068147A (ko) | 2001-11-22 | 2002-11-20 | 트랜지스터와 그것을 사용한 반도체 메모리 |

| TW091133883A TW200302569A (en) | 2001-11-22 | 2002-11-20 | Transistor and semiconductor memory using the same |

| PCT/JP2002/012105 WO2003044869A1 (en) | 2001-11-22 | 2002-11-20 | Transistor and semiconductor memory comprising it |

| EP02785942A EP1458032A1 (en) | 2001-11-22 | 2002-11-20 | Transistor and semiconductor memory comprising it |

| CNA028232364A CN1589501A (zh) | 2001-11-22 | 2002-11-20 | 晶体管和使用了晶体管的半导体存储器 |

| US10/831,333 US6944062B2 (en) | 2001-11-22 | 2004-04-26 | Transistor and semiconductor memory using the same |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001358308 | 2001-11-22 | ||

| JP2002169749 | 2002-06-11 | ||

| JP2002322905A JP2004072060A (ja) | 2001-11-22 | 2002-11-06 | トランジスタとそれを用いた半導体メモリ、およびトランジスタの駆動方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004072060A true JP2004072060A (ja) | 2004-03-04 |

| JP2004072060A5 JP2004072060A5 (enExample) | 2005-12-22 |

Family

ID=27347866

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002322905A Pending JP2004072060A (ja) | 2001-11-22 | 2002-11-06 | トランジスタとそれを用いた半導体メモリ、およびトランジスタの駆動方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US6944062B2 (enExample) |

| EP (1) | EP1458032A1 (enExample) |

| JP (1) | JP2004072060A (enExample) |

| KR (1) | KR20040068147A (enExample) |

| CN (1) | CN1589501A (enExample) |

| TW (1) | TW200302569A (enExample) |

| WO (1) | WO2003044869A1 (enExample) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006024309A (ja) * | 2004-07-09 | 2006-01-26 | Renesas Technology Corp | 不揮発性メモリ、データプロセッサ及びicカード用マイクロコンピュータ |

| JP2006040442A (ja) * | 2004-07-28 | 2006-02-09 | Innotech Corp | データ読出し回路 |

| JP2006155701A (ja) * | 2004-11-26 | 2006-06-15 | Innotech Corp | 半導体記憶装置 |

| JP2006294207A (ja) | 2005-04-11 | 2006-10-26 | Hynix Semiconductor Inc | Nand型フラッシュメモリ素子のリカバリ方法 |

| WO2010125695A1 (en) * | 2009-04-30 | 2010-11-04 | Powerchip Corporation | Programming method for nand flash memory device |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004072060A (ja) | 2001-11-22 | 2004-03-04 | Innotech Corp | トランジスタとそれを用いた半導体メモリ、およびトランジスタの駆動方法 |

| JP4472934B2 (ja) * | 2002-03-27 | 2010-06-02 | イノテック株式会社 | 半導体装置および半導体メモリ |

| US6795348B2 (en) * | 2002-05-29 | 2004-09-21 | Micron Technology, Inc. | Method and apparatus for erasing flash memory |

| TWI233691B (en) * | 2004-05-12 | 2005-06-01 | Powerchip Semiconductor Corp | Nonvolatile memory, nonvolatile memory array and manufacturing method thereof |

| US8595459B2 (en) * | 2004-11-29 | 2013-11-26 | Rambus Inc. | Micro-threaded memory |

| CN103094283B (zh) * | 2011-10-27 | 2015-11-25 | 中芯国际集成电路制造(上海)有限公司 | 8-bit半导体存储单元、制作方法及其存储单元阵列 |

| TWI874071B (zh) * | 2023-12-26 | 2025-02-21 | 華邦電子股份有限公司 | 半導體記憶體裝置及其形成方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02122674A (ja) * | 1988-11-01 | 1990-05-10 | Fujitsu Ltd | 不揮発性半導体記憶装置 |

| JPH03249811A (ja) * | 1990-02-27 | 1991-11-07 | Mitsubishi Electric Corp | 受光増幅器 |

| JPH11220044A (ja) * | 1998-01-27 | 1999-08-10 | Masaki Ogura | 低電圧eeprom/nvramトランジスターとその製造方法 |

| JPH11238815A (ja) * | 1997-12-09 | 1999-08-31 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置およびその製造方法 |

| JPH11260944A (ja) * | 1998-01-16 | 1999-09-24 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置およびその製造方法ならびに半導体集積回路装置 |

| JP2001057394A (ja) * | 1999-06-09 | 2001-02-27 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置及びその製造方法 |

| JP2001156188A (ja) * | 1999-03-08 | 2001-06-08 | Toshiba Corp | 半導体記憶装置およびその製造方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5379255A (en) * | 1992-12-14 | 1995-01-03 | Texas Instruments Incorporated | Three dimensional famos memory devices and methods of fabricating |

| US5973356A (en) * | 1997-07-08 | 1999-10-26 | Micron Technology, Inc. | Ultra high density flash memory |

| JP2000082752A (ja) | 1998-09-07 | 2000-03-21 | Matsushita Electronics Industry Corp | 半導体記憶装置の書き込み及び消去方法 |

| US6534816B1 (en) * | 1999-03-24 | 2003-03-18 | John M. Caywood | Method and apparatus for injecting charge onto the floating gate of a nonvolatile memory cell |

| JP4397491B2 (ja) | 1999-11-30 | 2010-01-13 | 財団法人国際科学振興財団 | 111面方位を表面に有するシリコンを用いた半導体装置およびその形成方法 |

| US6538925B2 (en) | 2000-11-09 | 2003-03-25 | Innotech Corporation | Semiconductor memory device, method of manufacturing the same and method of driving the same |

| JP3283872B1 (ja) | 2001-04-12 | 2002-05-20 | イノテック株式会社 | 半導体記憶装置、その製造方法及び半導体記憶装置の駆動方法 |

| JP3249811B1 (ja) | 2000-11-09 | 2002-01-21 | イノテック株式会社 | 半導体記憶装置、その製造方法及び半導体記憶装置の駆動方法 |

| JP3249812B1 (ja) | 2001-05-14 | 2002-01-21 | イノテック株式会社 | 半導体記憶装置及びその製造方法 |

| JP4191975B2 (ja) * | 2001-11-01 | 2008-12-03 | イノテック株式会社 | トランジスタとそれを用いた半導体メモリ、およびトランジスタの製造方法 |

| JP2003224215A (ja) * | 2001-11-22 | 2003-08-08 | Innotech Corp | トランジスタとそれを用いた半導体メモリ、およびトランジスタの駆動方法 |

| JP2004072060A (ja) | 2001-11-22 | 2004-03-04 | Innotech Corp | トランジスタとそれを用いた半導体メモリ、およびトランジスタの駆動方法 |

| US6861315B1 (en) * | 2003-08-14 | 2005-03-01 | Silicon Storage Technology, Inc. | Method of manufacturing an array of bi-directional nonvolatile memory cells |

-

2002

- 2002-11-06 JP JP2002322905A patent/JP2004072060A/ja active Pending

- 2002-11-20 TW TW091133883A patent/TW200302569A/zh unknown

- 2002-11-20 CN CNA028232364A patent/CN1589501A/zh active Pending

- 2002-11-20 KR KR10-2004-7007756A patent/KR20040068147A/ko not_active Withdrawn

- 2002-11-20 EP EP02785942A patent/EP1458032A1/en not_active Withdrawn

- 2002-11-20 WO PCT/JP2002/012105 patent/WO2003044869A1/ja not_active Ceased

-

2004

- 2004-04-26 US US10/831,333 patent/US6944062B2/en not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02122674A (ja) * | 1988-11-01 | 1990-05-10 | Fujitsu Ltd | 不揮発性半導体記憶装置 |

| JPH03249811A (ja) * | 1990-02-27 | 1991-11-07 | Mitsubishi Electric Corp | 受光増幅器 |

| JPH11238815A (ja) * | 1997-12-09 | 1999-08-31 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置およびその製造方法 |

| JPH11260944A (ja) * | 1998-01-16 | 1999-09-24 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置およびその製造方法ならびに半導体集積回路装置 |

| JPH11220044A (ja) * | 1998-01-27 | 1999-08-10 | Masaki Ogura | 低電圧eeprom/nvramトランジスターとその製造方法 |

| JP2001156188A (ja) * | 1999-03-08 | 2001-06-08 | Toshiba Corp | 半導体記憶装置およびその製造方法 |

| JP2001057394A (ja) * | 1999-06-09 | 2001-02-27 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置及びその製造方法 |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006024309A (ja) * | 2004-07-09 | 2006-01-26 | Renesas Technology Corp | 不揮発性メモリ、データプロセッサ及びicカード用マイクロコンピュータ |

| JP2006040442A (ja) * | 2004-07-28 | 2006-02-09 | Innotech Corp | データ読出し回路 |

| JP2006155701A (ja) * | 2004-11-26 | 2006-06-15 | Innotech Corp | 半導体記憶装置 |

| JP2006294207A (ja) | 2005-04-11 | 2006-10-26 | Hynix Semiconductor Inc | Nand型フラッシュメモリ素子のリカバリ方法 |

| WO2010125695A1 (en) * | 2009-04-30 | 2010-11-04 | Powerchip Corporation | Programming method for nand flash memory device |

| JP2011519462A (ja) * | 2009-04-30 | 2011-07-07 | Powerchip株式会社 | Nandフラッシュメモリデバイスのプログラミング方法 |

| US8599614B2 (en) | 2009-04-30 | 2013-12-03 | Powerchip Corporation | Programming method for NAND flash memory device to reduce electrons in channels |

| US9214242B2 (en) | 2009-04-30 | 2015-12-15 | Powerchip Corporation | Programming method for NAND flash memory device to reduce electrons in channels |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200302569A (en) | 2003-08-01 |

| CN1589501A (zh) | 2005-03-02 |

| EP1458032A1 (en) | 2004-09-15 |

| WO2003044869A1 (en) | 2003-05-30 |

| US20040196685A1 (en) | 2004-10-07 |

| US6944062B2 (en) | 2005-09-13 |

| KR20040068147A (ko) | 2004-07-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101039244B1 (ko) | 비휘발성 메모리 및 그 제조방법 | |

| JP4923318B2 (ja) | 不揮発性半導体記憶装置およびその動作方法 | |

| JP4923321B2 (ja) | 不揮発性半導体記憶装置の動作方法 | |

| US6580103B2 (en) | Array of flash memory cells and data program and erase methods of the same | |

| US7042045B2 (en) | Non-volatile memory cell having a silicon-oxide nitride-oxide-silicon gate structure | |

| US5455790A (en) | High density EEPROM cell array which can selectively erase each byte of data in each row of the array | |

| US5940325A (en) | Low voltage one transistor flash EEPROM cell using fowler-nordheim programming and erase | |

| EP1603137B1 (en) | Program/erase method for p-channel charge trapping memory device | |

| JP2002026149A (ja) | 不揮発性半導体記憶装置およびその動作方法 | |

| JPH06314795A (ja) | 不揮発性記憶素子およびこれを利用した不揮発性記憶装置、この記憶装置の駆動方法、ならびにこの記憶素子の製造方法 | |

| JP4191975B2 (ja) | トランジスタとそれを用いた半導体メモリ、およびトランジスタの製造方法 | |

| JP2004072060A (ja) | トランジスタとそれを用いた半導体メモリ、およびトランジスタの駆動方法 | |

| KR20030042422A (ko) | 다중비트를 저장하는 기억소자를 구비한 반도체 메모리 및그것을 구동하는 방법 | |

| US6914819B2 (en) | Non-volatile flash memory | |

| JPH06350098A (ja) | 不揮発性記憶素子およびこれを利用した不揮発性記憶装置ならびにこの記憶装置の駆動方法 | |

| US7652320B2 (en) | Non-volatile memory device having improved band-to-band tunneling induced hot electron injection efficiency and manufacturing method thereof | |

| JP2004047614A (ja) | トランジスタとそれを用いた半導体メモリ、およびトランジスタの製造方法 | |

| JPH06177393A (ja) | 不揮発性記憶装置およびその駆動方法、ならびに製造方法 | |

| JP4654936B2 (ja) | 不揮発性半導体記憶装置および、その動作方法 | |

| US20060226467A1 (en) | P-channel charge trapping memory device with sub-gate | |

| JP3426641B2 (ja) | 不揮発性記憶素子およびこれを利用した不揮発性記憶装置ならびにこの記憶装置の駆動方法 | |

| JP2004319544A (ja) | 半導体メモリ | |

| JPH06125064A (ja) | 不揮発性記憶装置およびその駆動方法 | |

| JPH06314799A (ja) | 不揮発性記憶素子およびこれを利用した不揮発性記憶装置ならびにこの記憶装置の駆動方法 | |

| JPH06125065A (ja) | 不揮発性記憶装置およびその駆動方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051102 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051102 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090728 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090925 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100907 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110111 |