DE112005000512B4 - Verfahren zum Herstellen eines Halbleiterbauelements mit flachen Isolationsgräben und verringerter Ausbildung von Einkerbungen - Google Patents

Verfahren zum Herstellen eines Halbleiterbauelements mit flachen Isolationsgräben und verringerter Ausbildung von Einkerbungen Download PDFInfo

- Publication number

- DE112005000512B4 DE112005000512B4 DE112005000512T DE112005000512T DE112005000512B4 DE 112005000512 B4 DE112005000512 B4 DE 112005000512B4 DE 112005000512 T DE112005000512 T DE 112005000512T DE 112005000512 T DE112005000512 T DE 112005000512T DE 112005000512 B4 DE112005000512 B4 DE 112005000512B4

- Authority

- DE

- Germany

- Prior art keywords

- stop layer

- semiconductor substrate

- forming

- nitride polishing

- polishing stop

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 44

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 21

- 238000007373 indentation Methods 0.000 title description 15

- 238000005498 polishing Methods 0.000 claims abstract description 56

- 150000004767 nitrides Chemical class 0.000 claims abstract description 44

- 239000000758 substrate Substances 0.000 claims abstract description 36

- 238000000034 method Methods 0.000 claims abstract description 24

- 239000011810 insulating material Substances 0.000 claims abstract description 12

- 238000002955 isolation Methods 0.000 claims abstract description 11

- 238000011049 filling Methods 0.000 claims abstract description 8

- 239000002019 doping agent Substances 0.000 claims abstract description 6

- 239000000463 material Substances 0.000 claims abstract description 5

- 150000002500 ions Chemical class 0.000 claims abstract description 4

- 238000005530 etching Methods 0.000 claims description 4

- 239000010410 layer Substances 0.000 description 50

- 229910052581 Si3N4 Inorganic materials 0.000 description 18

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 18

- 230000015572 biosynthetic process Effects 0.000 description 12

- 238000005468 ion implantation Methods 0.000 description 9

- 238000004140 cleaning Methods 0.000 description 7

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 5

- 230000000873 masking effect Effects 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 238000002513 implantation Methods 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 238000000746 purification Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 239000012535 impurity Substances 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 241000293849 Cordylanthus Species 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- QPJSUIGXIBEQAC-UHFFFAOYSA-N n-(2,4-dichloro-5-propan-2-yloxyphenyl)acetamide Chemical compound CC(C)OC1=CC(NC(C)=O)=C(Cl)C=C1Cl QPJSUIGXIBEQAC-UHFFFAOYSA-N 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

Abstract

Description

- Gebiet der Erfindung

- Die vorliegende Erfindung betrifft die Herstellung integrierter Halbleiterschaltungselemente. Die vorliegende Erfindung ist insbesondere auf die Herstellung hochintegrierter Halbleiterschaltungsbauelemente mit flachen Grabenisolationen (STI) mit hoher Qualität, ohne Einkerbungen oder mit einer wesentlich reduzierten Ausbildung von Einkerbungen.

- Hintergrund der Erfindung

- Die Miniaturisierung von Elementen von integrierten Halbleiterschaltungsbauelementen zwingt die Industrie dazu, die Breite und den Abstand eines aktiven Gebiets kleiner zu machen, wodurch die Anwendung üblicher LOCOS(lokale Oxidation von Silizium)-Isolationsverfahren zunehmend problematisch wird. STI wird als eine bessere Isolationstechnik als LOCOS betrachtet, da aufgrund ihrer Natur kaum eine Oxidverbreiterung in Form eines ”Vogelschnabels”, der für LOCOS charakteristisch ist, erzeugt wird, wodurch geringere Konversionsunterschiede erreicht sind.

- Konventionelle STI-Fertigungsverfahren beinhalten das Herstellen eines Pufferoxids auf einer oberen Oberfläche eines Halbleitersubstrats, das Bilden einer Nitridpolierstoppschicht darauf, beispielsweise von Siliziumnitrid, die typischerweise eine Dicke von mehr als 100 nm aufweist, das Bilden einer Öffnung in der Nitridpolierstoppschicht, das anisotrope Ätzen zur Bildung eines Grabens in dem Halbleitersubstrat, das Bilden einer thermischen Oxidschicht in dem Graben und das Füllen des Grabens mit einem isolierenden Material, wie etwa Siliziumoxid, wobei überschüssiges Material auf der Nitridpolierstoppschicht gebildet wird. Es wird dann eine Planarisierung angewendet, beispielsweise durch Ausführen eines chemisch-mechanischen Poliervorganges (CMP). Während der nachfolgenden Bearbeitung wird die Nitridschicht zusammen mit dem Pufferoxid entfernt, woran sich das Bilden von aktiven Bereichen anschließt, was typischerweise Maskierungs-, Ionenimplantations- und Reinigungsschritte umfasst. Während derartiger Reinigungsschritte werden die oberen Kanten des Feldoxids isotrop entfernt, wodurch ein Hohlraum oder eine ”Einsenkung oder Einkerbung” in der Oxidfüllung zurückbleibt.

- In der

US 2003/0 226 127 A1 EP 0 601 950 A2 lehrt ein Verfahren zur Herstellung einer SOI-Schicht durch Wafer-Bonding. DieUS 5 665 633 A lehrt ein Verfahren zur Herstellung eines Halbleiterbauteils mit Feldisolation durch ausgebildete Gräben. DieUS 5 177 028 A lehrt ein Verfahren zur Grabenisolierung und der Ausbildung von FETs auf den Ebenen zwischen den Gräben. DieUS 6 673 695 B1 offenbart ein Verfahren zur Ausbildung von STI-Bereichen in einem Halbleitersubstrat. - In der

US 5 616 513 A wird ein Verfahren zum Herstellen eines Halbleiterbauelements beschrieben, in dem eine Nitridpolierstoppschicht und eine Öffnung in derselben gebildet wird, ein Graben mit isolierendem Material gefüllt wird, eine planare obere Oberfläche des Halbleitersubstrats durch Polieren der oberen Oberfläche des Halbleitersubstrats gebildet wird und Dotierstoffionen durch die Nitridpolierstoppschicht implantiert werden. In derUS 6 566 215 B1 wird das Bilden von Dotiergebieten in einem Halbleitersubstrat durch Durchimplantieren eines Dotierstoffes durch einen Schichtenstapel beschrieben. - Beispielsweise ist eine konventionelle STI-Herstellungstechnik in den

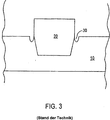

1 bis4 gezeigt, wobei gleiche Merkmale mit den gleichen Bezugszeichen belegt sind. Gemäß1 wird ein Pufferoxid11 auf einer oberen Fläche eines Halbleitersubstrats10 gebildet, und es wird eine Siliziumnitridpolierstoppschicht12 darauf ausgebildet, die typischerweise eine Dicke von über 100 nm aufweist. Eine Fotomaske (nicht gezeigt) wird dann verwendet, um eine Öffnung durch die Nitridpolierstoppschicht12 , das Pufferoxid11 zu bilden, und es wird ein Graben12 in dem Halbleitersubstrat10 hergestellt. - Nachfolgend wird eine thermische Oxidbeschichtung (nicht gezeigt) in dem Graben hergestellt, ein isolierendes Material wird abgeschieden und es wird eine Planarisierung erreicht, durch CMP, wodurch sich die Zwischenstruktur ergibt, die in

2 gezeigt ist, wobei das Bezugszeichen20 die Oxidfüllung bezeichnet. Nachfolgend werden die Nitridpolierstoppschicht12 und die Pufferoxidschicht11 entfernt und es werden dann Reinigungsschritte vor der Herstellung der aktiven Gebiete ausgeführt. Derartige Reinigungsschritte führen zur Ausbildung von Einkerbungen30 , wie in3 gezeigt ist. - Die STI-Einkerbungen sind in vielerlei Hinsicht problematisch. Beispielsweise sind die STI-Einkerbungen verantwortlich für eine hohe Leckage des Feldes an der Kante, insbesondere in flachen Source/Drain-Übergängen, verantwortlich. Wie in

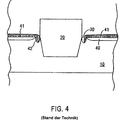

4 gezeigt ist, wachsen Silizidgebiete41 , die in flachen Source/Drain-Gebieten40 ausgebildet sind, steil nach unten, wie dies durch das Bezugszeichen42 dargestellt ist, d. h., diese wachsen bis unter die Tiefe des PN-Übergangs, der in einer späteren Phase hergestellt wird, wodurch sich hohe Leckströme und ein Kurzschluss ergeben können. Die Ansammlung von Dotierstoffen, insbesondere von Bor, an den STI-Feldrändern reduzieren die Tiefe des Übergangs. Folglich verursacht nach der Silizidierung der Übergänge das Silizid42 , das in das Substrat eindringt, Kurzschlusswege und somit können große Leckströme aus den Source/Drain-Übergängen in ein Wannengebiet bzw. Potenzialtopfgebiet oder Substrat auftreten. - Wenn Ferner der STI-Rand freigelegt wird als Folge der Ausbildung von Einkerbungen wird ein parasitärer Transistor mit einer geringen Schwellwertspannung über dem Bereich mit einer geringen Dotierstoffkonzentration ausgebildet, wodurch ein Knick in der charakteristischen Kurve eines Transistors hervorgerufen wird und das Vorhandensein eines Knicks führt zu elektrischen Eigenschaften, die sich von den elektrischen Entwurfseigenschaften unterscheiden, wodurch die Herstellung von Transistoren mit gleichförmigen Eigenschaften verhindert wird.

- Es besteht daher ein Bedarf für eine Verfahrenstechnik, die die Herstellung äußerst hochintegrierter Halbleiterbauelemente mit sehr zuverlässigen STI-Gebieten ohne oder mit deutlich reduzierten Einkerbungen ermöglicht.

- Überblick über die Erfindung

- Ein Vorteil der vorliegenden Erfindung liegt in einem Verfahren zur Herstellung eines Halbleiterbauelements, das sehr zuverlässige STI-Gebiete mit keinen oder wesentlich reduzierten Einkerbungen aufweist.

- Weitere Vorteile und andere Aspekte der vorliegenden Erfindung sind in der nachfolgenden Beschreibung angegeben und werden für den Fachmann zum Teil beim Studium des Folgenden ersichtlich oder können aus dem Praktizieren der vorliegenden Erfindung erkannt werden. Die Vorteile der vorliegenden Erfindung können insbesondere so realisiert und erreicht werden, wie dies in den angefügten Patentansprüchen dargestellt ist.

- Gemäß der vorliegenden Erfindung werden die vorhergehenden und weiteren Vorteile zum Teil durch ein Verfahren des Herstellens eines Halbleiterbauelements erreicht, wobei das Verfahren umfasst: Bilden einer Nitridpolierstoppschicht mit einer Dicke von nicht mehr als 40 nm über einem Halbleitersubstrat; Bilden einer Öffnung in der Nitridpolierstoppschicht und eines Grabens in einer Substratschicht; Füllen der Öffnung mit einem isolierenden Material, wobei ein Überschussmaterial auf der Nitridpolierstoppschicht gebildet wird; und Polieren, um eine obere planare Oberfläche zu bilden, wobei an der Nitridpolierstoppschicht gestoppt wird, wodurch ein flaches Grabenisolationsgebiet gebildet wird.

- Ausführungsformen der vorliegenden Erfindung umfassen: Bilden eines Pufferoxids auf einer oberen Fläche des Halbleiterbauelementsubstrats, Bilden der Nitridpolierstoppschicht, beispielsweise einer Siliziumnitridpolierstoppschicht mit einer Dicke von 5 nm bis 15 nm, beispielsweise 10 nm, auf der Pufferoxidschicht, Füllen der Öffnung mit dielektrischem isolierenden Material, etwa Siliziumoxid, das durch chemische Dampfabscheidung aufgebracht wird, und anschließendes Ausführen eines chemisch-mechanischen Polierens (CMP), um eine Einebnung zu bewirken, wobei an der Nitridpolierstoppschicht angehalten wird, und wobei nicht mehr als 2 nm der oberen Fläche der Nitridpolierstoppschicht abgetragen werden. Ausführungsformen der vorliegenden Erfindung umfassen ferner die Ionenimplantation von Verunreinigungen bzw. Dotierstoffen durch die Nitridpolierstoppschicht, um Dotiergebiete in dem Halbleitersubstrat benachbart zu dem flachen Grabenisolationsgebiet zu schaffen, Ätzen, um einen Teil der oberen Fläche des isolierenden Materials, das den Graben füllt, zu entfernen, so dass die obere Fläche des isolierenden Materials in dem Graben im Wesentlichen bündig zur oberen Fläche des Halbleitersubstrats ist, und anschließendes Entfernen der Nitridpolierstoppschicht. Nachfolgend wird eine Gateoxidschicht auf dem Substrat ausgebildet, und eine Gateelektrodenschicht wird darauf gebildet, wobei konventionelle Verfahren eingesetzt werden.

- Kurze Beschreibung der Zeichnungen

-

1 bis4 zeigen schematisch der Reihe nach Phasen eines konventionellen Verfahrens zur Herstellung von STI-Gebieten. In den1 bis4 sind gleiche Elemente mit gleichen Bezugszeichen belegt. -

5 bis11 zeigen schematisch diverse Stufen eines Verfahrens gemäß einer Ausführungsform der vorliegenden Erfindung. In den5 bis11 sind gleiche Merkmale mit gleichen Bezugszeichen belegt. - Beschreibung der Erfindung

- Die vorliegende Erfindung wendet sich an das Problem, das mit der Einrichtung konventioneller STI-Verfahrensabläufen einhergeht, die zur Ausbildung von Einkerbungen an den Ecken eines STI-Gebiets führen, und löst diese Probleme. Ein derartiger konventioneller Verfahrensablauf umfasst typischerweise das Ausbilden einer relativ dicken Nitridpolierstoppschicht mit einer Dicke von ungefähr größer als 100 nm. Eine derartige dicke Nitridpolierstoppschicht wird typischerweise unmittelbar nach dem STI-Oxidpoliervorgang entfernt, da nachfolgende Schritte eine Ionenimplantation erfordern, um die aktiven Bereiche herzustellen, und dicke Nitridschichten eine derartige Ionenimplantation abblocken. Es werden viele Maskierungs-, Implantations- und Reinigungsschritte angewendet, um die aktiven Gebiete zu bilden, woraus die Ausbildung von Einkerbungen an den Ecken bzw. Kanten des STI-Gebietes resultiert. Konventionelle Lösungen für dieses Problem streben danach, diese Einkerbungen zu minimieren, indem beispielsweise Reinigungen nach der Oxidpolierung und Nitridablösevorgänge vor dem STI-Oxideinfüllen optimiert werden. Jedoch haben solche Lösungen nicht in ausreichender Weise die Problematik der Einkerbung beim STI gelöst.

- Gemäß der vorliegenden Erfindung wird eine äußerst dünne Nitridpolierstoppschicht, beispielsweise ein Siliziumnitrid, bei einer Dicke von nicht mehr als 40 nm abgeschieden, etwa eine Dicke von 1 nm bis 40 nm. Geeignete Dicken für Siliziumnitridpolierätzstoppschichten sind 5 nm bis 15 nm, beispielsweise 10 nm.

- Vorteilhafterweise wird die dünne Nitridpolierstoppschicht nicht unmittelbar nach dem STI-Oxidpolieren entfernt. Vielmehr wird die dünne Nitridpolierstoppschicht während der nachfolgenden Bearbeitung, die Maskierungs-, Ionenimplantations- und Reinigungsschritte umfasst, beibehalten, um die aktiven Gebiete zu bilden. Die Verwendung einer dünnen Nitridpolierstoppschicht ist ausreichend, um die gefüllten Graben zu schützen, wodurch ein isotroper Angriff des Oxids an den STI-Ecken oder Kanten verhindert wird, der ansonsten zur Ausbildung von Einkerbungen führen würde. Da ferner die Nitridpolierstoppschicht dünn ist, wird die Ionenimplantation nicht abgeblockt. Vielmehr liefert die Verwendung einer dünnen Nitridpolierstoppschicht eine konsistentere Oberfläche für die Implantation, da eine relativ unbedeckte Siliziumoberfläche rasch ein nicht konsistentes natürliches Oxid ausbildet, wohingegen die Nitridoberfläche deutlich stabiler ist. Daher wird gemäß den Ausführungsformen gemäß der vorliegenden Erfindung die Nitridpolierstoppschicht bis zur Ausbildung des Gateoxids belassen, wodurch der aktive Siliziumbereich geschützt wird, und wodurch eine wesentlich ebenere Oberfläche bereitgestellt und Einkerbungen vermieden oder wesentlich reduziert werden.

- Ein Verfahren gemäß einer Ausführungsform der vorliegenden Erfindung ist schematisch in den

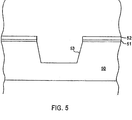

5 bis11 gezeigt, wobei ähnliche Strukturelemente mit ähnlichen Bezugszeichen belegt sind. Gemäß5 wird ein Pufferoxid mit einer Dicke von 5 nm bis 20 nm, beispielsweise 15 nm, über einer oberen Fläche eines Halbleitersubstrats50 gebildet. Gemäß Ausführungsformen der vorliegenden Erfindung wird eine sehr dünne Siliziumnitridpolierstoppschicht52 auf dem Pufferoxid51 gebildet. Die Siliziumnitridpolierstoppschicht52 wird typischerweise mit einer Dicke von 5 nm bis 15 nm, beispielsweise 10 nm, hergestellt. Es wird dann ein Graben53 in dem Substrat50 gebildet, wobei konventionelle Fotolithografie- und Ätzverfahren eingesetzt werden. - Zu diesem Zeitpunkt kann, obwohl dies nicht gezeigt ist, ein dünnes thermisches Oxid zur Auskleidung des Grabens gebildet werden. Nachfolgend wird, wie in

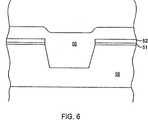

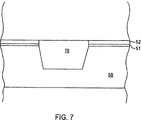

6 gezeigt ist, ein isolierendes Material60 , etwa Siliziumoxid, abgeschieden, um den Graben zu füllen und um ein überschüssiges Material auf der Siliziumnitridpolierstoppschicht52 beispielsweise durch CVD zu bilden. Die Einebnung wird dann beispielsweise durch CMP erreicht, woraus sich die Zwischenstruktur ergibt, die in7 gezeigt ist, wobei das Bezugszeichen70 die STI-Oxidfüllung bezeichnet. Das CMP wird typischerweise so ausgeführt, dass wenn dieses an der Siliziumnitridpolierstoppschicht52 anhält, nicht mehr als 2 nm von der oberen Fläche der Siliziumnitridpolierstoppschicht52 abgetragen werden. - In konventionellen Vorgehensweisen wird die Siliziumnitridpolierstoppschicht nach dem CMP entfernt, woran sich konventionelle Maskierungs-, Ionenimplantations- und Reinigungsschritte anschließen, um die aktiven Gebiete zu bilden, woraus die Erzeugung von Einkerbungen resultiert. Gemäß Ausführungsformen der vorliegenden Erfindung wird jedoch die relativ dünne Siliziumnitridpolierstoppschicht

52 während der nachfolgenden Maskierungs-, Ionenimplantations- und Reinigungsschritte beibehalten, die in konventioneller Weise ausgeführt werden, wodurch sich die Ausbildung von Verunreinigungs- bzw. dotierten Gebieten80 ergibt, wie dies in8 gezeigt ist, die schließlich für Source/Drain-Gebiete von Transistoren verwendet werden können. Da die Siliziumnitridpolierstoppschicht52 relativ dünn ist, gibt es im Wesentlichen keine Blockierung der Ionen während der Implantation. Des Weiteren bildet die Siliziumnitridschicht eine stabile Oberfläche, die eine größere Gleichförmigkeit bei der Herstellung der dotierten Gebiete bietet. - Nachfolgend wird die obere Fläche der STI-Oxidfüllung

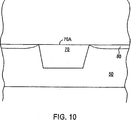

70 entfernt, etwa durch Flusssäure (HF), so dass die obere Fläche70A im Wesentlichen koplanar bzw. bündig ist zu der oberen Fläche des Halbleitersubstrat50 , woraus sich die Zwischenstruktur ergibt, die in9 gezeigt ist. Nachfolgend wird die Siliziumnitridpolierstoppschicht52 beispielsweise durch Anwendung von Flusssäure entfernt, und daraufhin wird die Pufferoxidschicht51 entfernt, woraus sich die in10 gezeigte Struktur ergibt. Nachfolgend wird eine Verarbeitung ausgeführt, um eine Transistorstruktur zu bilden, wie sie in11 gezeigt ist, die eine Gateelektrode100 aufweist, die über dem Halbleitersubstrat50 angeordnet ist, wobei ein Gateoxid101 dazwischen vorgesehen ist, und wobei dielektrischen Seitenwandabstandshalter102 daran ausgebildet sind. In11 bezeichnet das Bezugszeichen103 ein Zwischenschichtdielektrikum und ein Element104 repräsentiert einen elektrischen Kontakt durch die dielektrische Schicht zu einem aktiven Gebiet80 auf dem Substrat50 . - Die vorliegende Erfindung stellen einen Verfahrensablauf bereit, der für die Herstellung von Halbleiterbauelementen mit äußerst zuverlässigen STI-Gebieten ohne die Ausbildung von Einkerbungen oder mit deutlich reduzierten Einkerbungen ermöglicht. Ausführungsformen der vorliegenden Erfindung umfassen das strategische Reduzieren der Dicke einer Siliziumnitridpolierstoppschicht auf unter 40 nm und das Beibehalten der Siliziumnitridpolierstoppschicht unmittelbar nach dem CMP, um die Grabenkanten vor einem isotropen Ätzangriff während konventioneller Reinigungsschritte zu schützen, die ausgeführt werden, wenn aktive Gebiete gebildet werden, wobei die dünne Siliziumnitridpolierstoppschicht während einer Ionenimplantation beibehalten wird, wodurch äußerst gleichförmige implantierte Gebiete erreicht werden.

- Die vorliegende Erfindung ist industriell anwendbar bei der Herstellung hochintegrierter Halbleiterbauelemente, die STI-Gebiete ohne oder mit wesentlich reduzierter Ausbildung von Einkerbungen enthalten. Die vorliegende Erfindung genießt insbesondere eine Anwendbarkeit bei der Herstellung von Halbleiterbauelementen mit Abmessungen im Bereich unter einem Mikrometer.

Claims (6)

- Verfahren zum Herstellen eines Halbleiterbauelements, wobei das Verfahren umfasst: Bilden einer Nitridpolierstoppschicht (

52 ) mit einer Dicke von nicht mehr als 40 nm über einem Halbleitersubstrat (50 ); Bilden einer Öffnung in der Nitridpolierstoppschicht (52 ) und eines Grabens (53 ) in dem Halbleitersubstrat (50 ); Füllen des Grabens (53 ) mit isolierendem Material, wobei Überschussmaterial auf der Nitridpolierstoppschicht (52 ) gebildet wird; und Bilden einer planaren oberen Oberfläche des Halbleitersubstrats (50 ) durch Polieren der oberen Oberfläche des Halbleitersubstrats (50 ), wobei an der Nitridpolierstoppschicht (52 ) angehalten wird, wodurch ein flaches Grabenisolationsgebiet (70 ) gebildet wird; und anschließend Implantieren von Dotierstoffionen durch die Nitridpolierstoppschicht (52 ), wodurch dotierte Gebiete (80 ) in dem Halbleitersubstrat (50 ) benachbart zu dem flachen Grabenisolationsgebiet (70 ) gebildet werden. - Verfahren nach Anspruch 1, welches das Bilden der Nitridpolierschicht (

52 ) mit einer Dicke von 5 nm bis 15 nm umfasst. - Verfahren nach Anspruch 1, bei dem durch das Polieren der oberen Oberfläche des Halbleitersubstrats (

50 ) nicht mehr als 2 nm der Nitridpolierstoppschicht (52 ) abgetragen werden. - Verfahren nach Anspruch 1, welches ferner ein Bilden einer Pufferoxidschicht (

51 ) auf einer oberen Oberfläche des Halbleitersubstrats (50 ) vor dem Bilden der Nitridpolierstoppschicht (52 ) auf der Pufferoxidschicht (51 ) umfasst. - Verfahren nach Anspruch 1, welches ferner umfasst: Entfernen der Nitridpolierstoppschicht (

52 ); Bilden einer Gateoxidschicht (101 ) auf dem Halbleitersubstrat (50 ) nach dem Entfernen der Nitridpolierstoppschicht (52 ); und Bilden einer Gateelektrode (100 ) auf der Gateoxidschicht (101 ). - Verfahren nach Anspruch 5, welches ferner ein Ätzen umfasst, um einen Teil einer oberen Oberfläche (

70A ) des den Graben (53 ) füllenden isolierenden Materials zu entfernen, so dass die obere Oberfläche (70A ) des isolierenden Materials bündig ist zu der oberen Oberfläche des Halbleitersubstrats (50 ) vor dem Entfernen der Nitridpolierstoppschicht (52 ).

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/791,759 | 2004-03-04 | ||

| US10/791,759 US7091106B2 (en) | 2004-03-04 | 2004-03-04 | Method of reducing STI divot formation during semiconductor device fabrication |

| PCT/US2005/006177 WO2005093825A1 (en) | 2004-03-04 | 2005-02-26 | Method of reducing sti divot formation during semiconductor device fabrication |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| DE112005000512T5 DE112005000512T5 (de) | 2007-01-11 |

| DE112005000512B4 true DE112005000512B4 (de) | 2011-09-08 |

Family

ID=34911706

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| DE112005000512T Expired - Fee Related DE112005000512B4 (de) | 2004-03-04 | 2005-02-26 | Verfahren zum Herstellen eines Halbleiterbauelements mit flachen Isolationsgräben und verringerter Ausbildung von Einkerbungen |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US7091106B2 (de) |

| JP (1) | JP2007526652A (de) |

| KR (1) | KR20060129037A (de) |

| CN (1) | CN1926679B (de) |

| DE (1) | DE112005000512B4 (de) |

| GB (1) | GB2426126B (de) |

| TW (1) | TWI355678B (de) |

| WO (1) | WO2005093825A1 (de) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100568259B1 (ko) * | 2004-12-14 | 2006-04-07 | 삼성전자주식회사 | 트렌치 소자 분리형 반도체 장치 및 그 형성 방법 |

| US20080204580A1 (en) * | 2007-02-28 | 2008-08-28 | Micron Technology, Inc. | Method, apparatus and system providing imaging device with color filter array |

| US20090053834A1 (en) * | 2007-08-23 | 2009-02-26 | Vladimir Alexeevich Ukraintsev | Use of scatterometry for in-line detection of poly-si strings left in sti divot after gate etch |

| KR100880227B1 (ko) * | 2007-10-09 | 2009-01-28 | 주식회사 동부하이텍 | 플래시 메모리 소자의 제조방법 |

| US7745320B2 (en) * | 2008-05-21 | 2010-06-29 | Chartered Semiconductor Manufacturing, Ltd. | Method for reducing silicide defects in integrated circuits |

| US8546268B2 (en) | 2009-04-30 | 2013-10-01 | X-Fab Semiconductor Foundries Ag | Manufacturing integrated circuit components having multiple gate oxidations |

| US8274114B2 (en) * | 2010-01-14 | 2012-09-25 | Broadcom Corporation | Semiconductor device having a modified shallow trench isolation (STI) region and a modified well region |

| US8283722B2 (en) | 2010-06-14 | 2012-10-09 | Broadcom Corporation | Semiconductor device having an enhanced well region |

| US9123807B2 (en) | 2010-12-28 | 2015-09-01 | Broadcom Corporation | Reduction of parasitic capacitance in a semiconductor device |

| US20120292735A1 (en) | 2011-05-20 | 2012-11-22 | GLOBALFOUNDRIES Singapore Pte.Ltd. | Corner transistor suppression |

| US9263556B2 (en) * | 2012-06-29 | 2016-02-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | Silicide process using OD spacers |

| US8716102B2 (en) * | 2012-08-14 | 2014-05-06 | Globalfoundries Inc. | Methods of forming isolation structures for semiconductor devices by performing a dry chemical removal process |

| US8603895B1 (en) | 2012-09-11 | 2013-12-10 | Globalfoundries Inc. | Methods of forming isolation structures for semiconductor devices by performing a deposition-etch-deposition sequence |

| US9219059B2 (en) | 2012-09-26 | 2015-12-22 | International Business Machines Corporation | Semiconductor structure with integrated passive structures |

| JP6591347B2 (ja) | 2016-06-03 | 2019-10-16 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP6629159B2 (ja) * | 2016-09-16 | 2020-01-15 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| CN111341724B (zh) * | 2018-12-19 | 2022-11-04 | 上海新微技术研发中心有限公司 | 浅沟槽隔离工艺及浅沟槽隔离结构 |

| KR20200145974A (ko) | 2019-06-21 | 2020-12-31 | 삼성전자주식회사 | 반도체 소자 및 그 제조 방법 |

| CN113611604A (zh) * | 2021-03-19 | 2021-11-05 | 联芯集成电路制造(厦门)有限公司 | 半导体元件的制作方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5177028A (en) * | 1991-10-22 | 1993-01-05 | Micron Technology, Inc. | Trench isolation method having a double polysilicon gate formed on mesas |

| EP0601950A2 (de) * | 1992-12-10 | 1994-06-15 | International Business Machines Corporation | Verfahren zur Herstellung einer dünnen SOI-Schicht |

| US5616513A (en) * | 1995-06-01 | 1997-04-01 | International Business Machines Corporation | Shallow trench isolation with self aligned PSG layer |

| US5665633A (en) * | 1995-04-06 | 1997-09-09 | Motorola, Inc. | Process for forming a semiconductor device having field isolation |

| US6566215B1 (en) * | 2002-06-06 | 2003-05-20 | Chartered Semiconductor Manufacturing Ltd. | Method of fabricating short channel MOS transistors with source/drain extensions |

| US20030226127A1 (en) * | 2002-05-30 | 2003-12-04 | Fujitsu Limited | Designing method and a manufacturing method of an electronic device |

| US6673695B1 (en) * | 2002-02-01 | 2004-01-06 | Chartered Semiconductor Manufacturing Ltd. | STI scheme to prevent fox recess during pre-CMP HF dip |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US98661A (en) * | 1870-01-11 | Ikank l | ||

| JPH098135A (ja) * | 1995-06-26 | 1997-01-10 | Toshiba Corp | 半導体装置の製造方法 |

| JP3125719B2 (ja) * | 1997-07-28 | 2001-01-22 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| JP3053009B2 (ja) * | 1997-09-29 | 2000-06-19 | 日本電気株式会社 | 半導体装置の製造方法 |

| US6555476B1 (en) * | 1997-12-23 | 2003-04-29 | Texas Instruments Incorporated | Silicon carbide as a stop layer in chemical mechanical polishing for isolation dielectric |

| CN1219328C (zh) * | 1998-02-19 | 2005-09-14 | 国际商业机器公司 | 具有改善了注入剂的场效应晶体管及其制造方法 |

| JP3178416B2 (ja) * | 1998-05-22 | 2001-06-18 | 日本電気株式会社 | 半導体装置の製造方法 |

| US6599810B1 (en) * | 1998-11-05 | 2003-07-29 | Advanced Micro Devices, Inc. | Shallow trench isolation formation with ion implantation |

| US6248641B1 (en) * | 1999-02-05 | 2001-06-19 | United Microelectronics Corp. | Method of fabricating shallow trench isolation |

| JP2001185731A (ja) * | 1999-12-24 | 2001-07-06 | Toshiba Corp | 半導体装置及びその製造方法 |

| KR100346842B1 (ko) * | 2000-12-01 | 2002-08-03 | 삼성전자 주식회사 | 얕은 트렌치 아이솔레이션 구조를 갖는 반도체 디바이스및 그 제조방법 |

| US6432797B1 (en) | 2001-01-25 | 2002-08-13 | Chartered Semiconductor Manufacturing Ltd. | Simplified method to reduce or eliminate STI oxide divots |

| US20020142531A1 (en) * | 2001-03-29 | 2002-10-03 | Hsu Sheng Teng | Dual damascene copper gate and interconnect therefore |

-

2004

- 2004-03-04 US US10/791,759 patent/US7091106B2/en active Active

-

2005

- 2005-02-26 JP JP2007501861A patent/JP2007526652A/ja active Pending

- 2005-02-26 GB GB0617207A patent/GB2426126B/en not_active Expired - Fee Related

- 2005-02-26 KR KR1020067017589A patent/KR20060129037A/ko not_active Application Discontinuation

- 2005-02-26 WO PCT/US2005/006177 patent/WO2005093825A1/en active Application Filing

- 2005-02-26 DE DE112005000512T patent/DE112005000512B4/de not_active Expired - Fee Related

- 2005-02-26 CN CN2005800068145A patent/CN1926679B/zh not_active Expired - Fee Related

- 2005-03-02 TW TW094106204A patent/TWI355678B/zh not_active IP Right Cessation

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5177028A (en) * | 1991-10-22 | 1993-01-05 | Micron Technology, Inc. | Trench isolation method having a double polysilicon gate formed on mesas |

| EP0601950A2 (de) * | 1992-12-10 | 1994-06-15 | International Business Machines Corporation | Verfahren zur Herstellung einer dünnen SOI-Schicht |

| US5665633A (en) * | 1995-04-06 | 1997-09-09 | Motorola, Inc. | Process for forming a semiconductor device having field isolation |

| US5616513A (en) * | 1995-06-01 | 1997-04-01 | International Business Machines Corporation | Shallow trench isolation with self aligned PSG layer |

| US6673695B1 (en) * | 2002-02-01 | 2004-01-06 | Chartered Semiconductor Manufacturing Ltd. | STI scheme to prevent fox recess during pre-CMP HF dip |

| US20030226127A1 (en) * | 2002-05-30 | 2003-12-04 | Fujitsu Limited | Designing method and a manufacturing method of an electronic device |

| US6566215B1 (en) * | 2002-06-06 | 2003-05-20 | Chartered Semiconductor Manufacturing Ltd. | Method of fabricating short channel MOS transistors with source/drain extensions |

Also Published As

| Publication number | Publication date |

|---|---|

| US7091106B2 (en) | 2006-08-15 |

| CN1926679A (zh) | 2007-03-07 |

| JP2007526652A (ja) | 2007-09-13 |

| TWI355678B (en) | 2012-01-01 |

| WO2005093825A1 (en) | 2005-10-06 |

| US20050196928A1 (en) | 2005-09-08 |

| TW200535945A (en) | 2005-11-01 |

| GB2426126B (en) | 2008-07-23 |

| GB2426126A (en) | 2006-11-15 |

| GB0617207D0 (en) | 2006-10-11 |

| CN1926679B (zh) | 2010-10-06 |

| DE112005000512T5 (de) | 2007-01-11 |

| KR20060129037A (ko) | 2006-12-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| DE112005000512B4 (de) | Verfahren zum Herstellen eines Halbleiterbauelements mit flachen Isolationsgräben und verringerter Ausbildung von Einkerbungen | |

| DE4235534C2 (de) | Verfahren zum Isolieren von Feldeffekttransistoren | |

| DE10214066B4 (de) | Halbleiterbauelement mit retrogradem Dotierprofil in einem Kanalgebiet und Verfahren zur Herstellung desselben | |

| DE102009031113B4 (de) | Technik zum Freilegen eines Platzhaltermaterials in einem Austausch-Gate-Verfahren durch Modifizieren der Abtragsrate verspannter dielektrischer Deckschichten | |

| DE102009043628B4 (de) | Verbesserte Füllbedingungen in einem Austauschgateverfahren durch Ausführen eines Polierprozesses auf der Grundlage eines Opferfüllmaterials | |

| DE102008054075B4 (de) | Halbleiterbauelement mit Abgesenktem Drain- und Sourcebereich in Verbindung mit einem Verfahren zur komplexen Silizidherstellung in Transistoren | |

| DE102010064288B4 (de) | Halbleiterbauelement mit Kontaktelementen mit silizidierten Seitenwandgebieten | |

| DE102010002450B4 (de) | Transistoren mit Metallgateelektrodenstrukturen mit großem ε und angepassten Kanalhalbleitermaterialien | |

| DE102009039522B4 (de) | Verfahren zur Herstellung eines Halbleiterbauelements mit vergrabener Ätzstoppschicht in Grabenisolationsstrukturen für eine bessere Oberflächenebenheit in dicht gepackten Halbleiterbauelementen | |

| DE102008063403A1 (de) | SOI-Bauelement mit einem vergrabenen isolierenden Material mit erhöhter Ätzwiderstandsfähigkeit | |

| DE10219107A1 (de) | SOI-Transistorelement mit einem verbesserten Rückseitenkontakt und ein Verfahren zur Herstellung desselben | |

| DE102011004922B4 (de) | Verfahren zur Herstellung von Transistoren mit Metallgatestapeln mit erhöhter Integrität | |

| DE102014119641B4 (de) | Verfahren zur herstellung einer halbleitervorrichtung | |

| DE112007002739B4 (de) | Verfahren zur Herstellung eines Halbleiterbauelements mit Isolationsgraben und Kontaktgraben | |

| DE10351006A1 (de) | Technik zur Herstellung eines Transistors mit erhöhten Drain- und Source-Gebieten, wobei eine reduzierte Anzahl von Prozessschritten erforderlich ist | |

| DE102007041206B4 (de) | Halbleiterbauelement und Verfahren zum selbstjustierten Entfernen eines high-k Gatedielektrikums über einem STI-Gebiet | |

| DE112006001520B4 (de) | Prozess für die Herstellung erhabener Source- und Drain-Gebiete mit zu entfernenden Abstandshaltern, wobei "Mausohren" vermieden werden | |

| DE10324433A1 (de) | Verfahren zur Herstellung eines Substratkontakts für ein SOI-Halbleiterbauteil | |

| DE102005022574A1 (de) | Halbleiterspeicherbauelement mit Isolationsgrabenstruktur und zugehöriges Herstellungsverfahren | |

| DE102011080438B3 (de) | Herstellverfahren für einen N-Kanaltransistor mit einer Metallgateelektrodenstruktur mit großem ε und einem reduzierten Reihenwiderstand durch epitaktisch hergestelltes Halbleitermaterial in den Drain- und Sourcebereichen und N-Kanaltransistor | |

| DE102011005641B4 (de) | Verfahren zur Leistungssteigerung in Transistoren durch Reduzierung der Absenkung aktiver Gebiete und durch Entfernen von Abstandshaltern | |

| DE102005014749B4 (de) | Verfahren zur Herstellung eines Transistors mit einem erhöhten Drain- und Sourcegebiet mittels einer Drei-Schicht-Hartmaske für die Gatestrukturierung | |

| DE10233234A1 (de) | Mosfet-Source/Drain-Struktur | |

| DE102011004672B4 (de) | SOI-Halbleiterbauelement mit einer Substratdiode mit reduzierter Metallsilizidleckage | |

| DE102007063230B4 (de) | Halbleiterbauelement mit verspannten Materialschichten und Kontaktelement sowie Herstellungsverfahren hierfür |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| OP8 | Request for examination as to paragraph 44 patent law |

Ref document number: 112005000512 Country of ref document: DE Date of ref document: 20070111 Kind code of ref document: P |

|

| 8181 | Inventor (new situation) |

Inventor name: BONSER, DOUGLAS J., WAPPINGERS FALLS, N.Y., US Inventor name: GROSCHOPF, JOHANNES, FISHKILL, N.Y., US Inventor name: DAKSHINA-MURTHY, SRIKANTESWARA, WAPPINGERS FALLS, Inventor name: PELLERIN, JOHN G., HOPEWELL JUNCTION, N.Y., US Inventor name: CHEEK, JON D., WALLKILL, N.Y., US |

|

| 8127 | New person/name/address of the applicant |

Owner name: GLOBALFOUNDRIES INC., GRAND CAYMAN, KY |

|

| 8128 | New person/name/address of the agent |

Representative=s name: GRUENECKER, KINKELDEY, STOCKMAIR & SCHWANHAEUSSER, |

|

| R018 | Grant decision by examination section/examining division | ||

| R020 | Patent grant now final |

Effective date: 20111209 |

|

| R119 | Application deemed withdrawn, or ip right lapsed, due to non-payment of renewal fee | ||

| R119 | Application deemed withdrawn, or ip right lapsed, due to non-payment of renewal fee |

Effective date: 20140902 |