CN1897285B - 薄膜晶体管阵列面板及制造方法 - Google Patents

薄膜晶体管阵列面板及制造方法 Download PDFInfo

- Publication number

- CN1897285B CN1897285B CN200610098474XA CN200610098474A CN1897285B CN 1897285 B CN1897285 B CN 1897285B CN 200610098474X A CN200610098474X A CN 200610098474XA CN 200610098474 A CN200610098474 A CN 200610098474A CN 1897285 B CN1897285 B CN 1897285B

- Authority

- CN

- China

- Prior art keywords

- conducting film

- ohmic contact

- photoresist pattern

- gas

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000010409 thin film Substances 0.000 title claims abstract description 16

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 10

- 239000010408 film Substances 0.000 claims abstract description 61

- 239000004065 semiconductor Substances 0.000 claims abstract description 44

- 229920002120 photoresistant polymer Polymers 0.000 claims abstract description 31

- 239000000758 substrate Substances 0.000 claims abstract description 22

- 238000005530 etching Methods 0.000 claims abstract description 21

- 239000012212 insulator Substances 0.000 claims description 20

- 238000000034 method Methods 0.000 claims description 20

- 238000001039 wet etching Methods 0.000 claims description 5

- 125000001309 chloro group Chemical group Cl* 0.000 claims description 4

- 229910016027 MoTi Inorganic materials 0.000 claims description 3

- 125000004429 atom Chemical group 0.000 claims description 2

- 230000015572 biosynthetic process Effects 0.000 claims description 2

- 238000003860 storage Methods 0.000 description 31

- 239000007789 gas Substances 0.000 description 26

- 239000000460 chlorine Substances 0.000 description 23

- 239000002184 metal Substances 0.000 description 18

- 229910052751 metal Inorganic materials 0.000 description 18

- 206010047571 Visual impairment Diseases 0.000 description 13

- 229910021417 amorphous silicon Inorganic materials 0.000 description 12

- 229910052801 chlorine Inorganic materials 0.000 description 11

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 10

- 239000004973 liquid crystal related substance Substances 0.000 description 9

- 239000012528 membrane Substances 0.000 description 9

- 238000002161 passivation Methods 0.000 description 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 239000012535 impurity Substances 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 238000002360 preparation method Methods 0.000 description 4

- 235000008733 Citrus aurantifolia Nutrition 0.000 description 3

- 229910001182 Mo alloy Inorganic materials 0.000 description 3

- 235000011941 Tilia x europaea Nutrition 0.000 description 3

- 238000010494 dissociation reaction Methods 0.000 description 3

- 230000005593 dissociations Effects 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 239000004571 lime Substances 0.000 description 3

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- 238000010276 construction Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 238000005984 hydrogenation reaction Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 238000010992 reflux Methods 0.000 description 2

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- 206010034960 Photophobia Diseases 0.000 description 1

- 229910004205 SiNX Inorganic materials 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 125000001153 fluoro group Chemical group F* 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 208000013469 light sensitivity Diseases 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

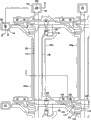

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

- G02F1/13629—Multilayer wirings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

- H01L29/456—Ohmic electrodes on silicon

- H01L29/458—Ohmic electrodes on silicon for thin film silicon, e.g. source or drain electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Nonlinear Science (AREA)

- Chemical & Material Sciences (AREA)

- Optics & Photonics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Mathematical Physics (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Electrodes Of Semiconductors (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

Description

| 流量比(SF<sub>6</sub>∶Cl<sub>2</sub>) | 余像改善 | 蚀刻特性 | 流量比(SF<sub>6</sub>∶HCl) | 余像改善 | 蚀刻特性 |

| 1∶0 | × | ◎ | 1∶0 | × | ◎ |

| 1∶0.3 | × | ◎ | 1∶1.12 | × | ◎ |

| 1∶0.7 | △ | ◎ | 1∶3 | × | ◎ |

| 1∶1 | ○ | ◎ | 1∶3.5 | △ | ◎ |

| 1∶4 | ○ | ◎ | 1∶4 | ○ | ◎ |

| 1∶6 | ◎ | ◎ | 1∶6.5 | ○ | ◎ |

| 1∶8.2 | ◎ | ◎ | 1∶9 | ◎ | ◎ |

| 1∶9.4 | ◎ | ○ | 1∶9.5 | ◎ | ○ |

| 1∶10 | ◎ | ○ | 1∶10 | ◎ | ○ |

| 1∶11.2 | ◎ | △ | 1∶11.2 | ◎ | △ |

| 1∶13 | ◎ | △ | 1∶13 | ◎ | △ |

Claims (14)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050062730 | 2005-07-12 | ||

| KR10-2005-0062730 | 2005-07-12 | ||

| KR1020050062730A KR101189271B1 (ko) | 2005-07-12 | 2005-07-12 | 박막 트랜지스터 표시판 및 그 제조 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1897285A CN1897285A (zh) | 2007-01-17 |

| CN1897285B true CN1897285B (zh) | 2010-05-12 |

Family

ID=37609731

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200610098474XA Expired - Fee Related CN1897285B (zh) | 2005-07-12 | 2006-07-07 | 薄膜晶体管阵列面板及制造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (3) | US7371621B2 (zh) |

| JP (1) | JP5156203B2 (zh) |

| KR (1) | KR101189271B1 (zh) |

| CN (1) | CN1897285B (zh) |

| TW (1) | TWI402988B (zh) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20060097381A (ko) * | 2005-03-09 | 2006-09-14 | 삼성전자주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR101189271B1 (ko) * | 2005-07-12 | 2012-10-09 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

| JP5247070B2 (ja) * | 2007-06-12 | 2013-07-24 | 株式会社ジャパンディスプレイウェスト | 液晶表示パネル及びその製造方法 |

| CN101593756B (zh) * | 2008-05-28 | 2011-05-18 | 群康科技(深圳)有限公司 | 薄膜晶体管基板、薄膜晶体管基板制造方法及显示装置 |

| US8227278B2 (en) * | 2008-09-05 | 2012-07-24 | Semiconductor Energy Laboratory Co., Ltd. | Methods for manufacturing thin film transistor and display device |

| KR101545460B1 (ko) * | 2008-09-12 | 2015-08-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 생산 방법 |

| KR101628254B1 (ko) * | 2009-09-21 | 2016-06-09 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 그의 제조 방법 |

| US8785241B2 (en) | 2010-07-16 | 2014-07-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR101345047B1 (ko) * | 2011-03-30 | 2013-12-26 | 샤프 가부시키가이샤 | 액티브 매트릭스 기판, 표시 장치 및 액티브 매트릭스 기판의 제조 방법 |

| CN102184966B (zh) * | 2011-04-15 | 2013-02-13 | 福州华映视讯有限公司 | 晶体管数组基板 |

| CN102508385A (zh) * | 2011-11-17 | 2012-06-20 | 华映视讯(吴江)有限公司 | 像素结构、阵列基板及其制作方法 |

| WO2014054487A1 (ja) * | 2012-10-02 | 2014-04-10 | シャープ株式会社 | 液晶パネル、及び製造方法 |

| US20140199833A1 (en) * | 2013-01-11 | 2014-07-17 | Applied Materials, Inc. | Methods for performing a via reveal etching process for forming through-silicon vias in a substrate |

| CN103811327A (zh) * | 2014-02-14 | 2014-05-21 | 上海和辉光电有限公司 | 薄膜晶体管的制作方法 |

| CN106653772B (zh) * | 2016-12-30 | 2019-10-01 | 惠科股份有限公司 | 一种显示面板及制程 |

| KR20210052696A (ko) | 2019-10-30 | 2021-05-11 | 삼성디스플레이 주식회사 | 표시 장치, 패턴 형성 방법 및 표시 장치의 제조 방법 |

| KR20220065949A (ko) * | 2020-11-13 | 2022-05-23 | 삼성디스플레이 주식회사 | 표시 장치 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6287899B1 (en) * | 1998-12-31 | 2001-09-11 | Samsung Electronics Co., Ltd. | Thin film transistor array panels for a liquid crystal display and a method for manufacturing the same |

| CN1434428A (zh) * | 2002-01-25 | 2003-08-06 | 三洋电机株式会社 | 显示器 |

| CN1501153A (zh) * | 2002-08-27 | 2004-06-02 | 三星电子株式会社 | 薄膜晶体管阵列面板及其制造方法 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6849872B1 (en) * | 1991-08-26 | 2005-02-01 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor |

| JP2558995B2 (ja) * | 1992-07-14 | 1996-11-27 | 松下電器産業株式会社 | 薄膜トランジスタの製造方法 |

| JPH06267983A (ja) * | 1993-03-16 | 1994-09-22 | Hitachi Ltd | 薄膜トランジスタ及びその製法 |

| US5923050A (en) * | 1995-02-08 | 1999-07-13 | Samsung Electronics Co., Ltd. | Amorphous silicon TFT |

| JPH08264790A (ja) * | 1995-03-22 | 1996-10-11 | Toshiba Corp | 薄膜電解効果トランジスタ及び液晶表示装置 |

| KR100552283B1 (ko) | 1998-01-22 | 2006-06-23 | 삼성전자주식회사 | 몰리브덴및몰리브덴합금을이용한박막트랜지스터기판및그제조방법 |

| JP2000056284A (ja) | 1998-08-10 | 2000-02-25 | Toshiba Corp | 液晶表示装置の製造方法 |

| US6380558B1 (en) * | 1998-12-29 | 2002-04-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of fabricating the same |

| KR100321227B1 (ko) | 2000-03-18 | 2004-09-07 | 테크노세미켐 주식회사 | 액정표시장치의전극용식각액 |

| US7095460B2 (en) * | 2001-02-26 | 2006-08-22 | Samsung Electronics Co., Ltd. | Thin film transistor array substrate using low dielectric insulating layer and method of fabricating the same |

| JP4920140B2 (ja) | 2001-05-18 | 2012-04-18 | ゲットナー・ファンデーション・エルエルシー | 液晶表示装置及びその製造方法 |

| JP2004119923A (ja) | 2002-09-30 | 2004-04-15 | Seiko Epson Corp | 半導体装置およびその製造方法 |

| JP4651929B2 (ja) * | 2002-11-15 | 2011-03-16 | Nec液晶テクノロジー株式会社 | 液晶表示装置の製造方法 |

| KR100904757B1 (ko) | 2002-12-30 | 2009-06-29 | 엘지디스플레이 주식회사 | 액정표시장치 및 그의 제조방법 |

| KR100640211B1 (ko) * | 2003-04-03 | 2006-10-31 | 엘지.필립스 엘시디 주식회사 | 액정표시장치의 제조방법 |

| KR101160823B1 (ko) * | 2004-08-24 | 2012-06-29 | 삼성전자주식회사 | 박막 트랜지스터 표시판과 그 제조 방법 |

| KR101117979B1 (ko) * | 2004-12-24 | 2012-03-06 | 엘지디스플레이 주식회사 | 박막 트랜지스터 기판의 제조 방법 |

| KR101189271B1 (ko) * | 2005-07-12 | 2012-10-09 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

-

2005

- 2005-07-12 KR KR1020050062730A patent/KR101189271B1/ko not_active IP Right Cessation

-

2006

- 2006-06-30 TW TW095124016A patent/TWI402988B/zh not_active IP Right Cessation

- 2006-07-07 CN CN200610098474XA patent/CN1897285B/zh not_active Expired - Fee Related

- 2006-07-12 JP JP2006191725A patent/JP5156203B2/ja not_active Expired - Fee Related

- 2006-07-12 US US11/486,330 patent/US7371621B2/en active Active

-

2008

- 2008-04-08 US US12/099,718 patent/US7888675B2/en active Active

-

2010

- 2010-04-22 US US12/765,698 patent/US8173493B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6287899B1 (en) * | 1998-12-31 | 2001-09-11 | Samsung Electronics Co., Ltd. | Thin film transistor array panels for a liquid crystal display and a method for manufacturing the same |

| CN1434428A (zh) * | 2002-01-25 | 2003-08-06 | 三洋电机株式会社 | 显示器 |

| CN1501153A (zh) * | 2002-08-27 | 2004-06-02 | 三星电子株式会社 | 薄膜晶体管阵列面板及其制造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5156203B2 (ja) | 2013-03-06 |

| US8173493B2 (en) | 2012-05-08 |

| US20070012967A1 (en) | 2007-01-18 |

| TW200715561A (en) | 2007-04-16 |

| US20080203393A1 (en) | 2008-08-28 |

| KR101189271B1 (ko) | 2012-10-09 |

| US7888675B2 (en) | 2011-02-15 |

| TWI402988B (zh) | 2013-07-21 |

| US20100203715A1 (en) | 2010-08-12 |

| US7371621B2 (en) | 2008-05-13 |

| JP2007027735A (ja) | 2007-02-01 |

| CN1897285A (zh) | 2007-01-17 |

| KR20070008868A (ko) | 2007-01-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1897285B (zh) | 薄膜晶体管阵列面板及制造方法 | |

| CN100365478C (zh) | 液晶显示器及其薄膜晶体管阵列面板 | |

| CN102315166B (zh) | 具有低电阻总线结构的薄膜晶体管基板及其制造方法 | |

| CN100465704C (zh) | 触点结构及制造方法,薄膜晶体管阵列面板及制造方法 | |

| US7358124B2 (en) | Thin film transistor array panel and manufacturing method thereof | |

| CN100413077C (zh) | 薄膜晶体管阵列面板 | |

| US8067774B2 (en) | Thin film transistor panel and method of manufacturing the same | |

| US20060175610A1 (en) | Signal line, thin film transistor array panel with the signal line, and method for manufacturing the same | |

| US7932965B2 (en) | Thin film transistor array panel and method for manufacturing the same | |

| KR20070000025A (ko) | 박막 트랜지스터 표시판 및 그 제조 방법 | |

| KR20060135995A (ko) | 박막 트랜지스터 표시판 및 그 제조 방법 | |

| US7371592B2 (en) | Manufacturing method of thin film transistor array panel using an optical mask | |

| CN100419552C (zh) | 薄膜晶体管阵列面板 | |

| KR101909139B1 (ko) | 박막 트랜지스터 표시판 및 그 제조 방법 | |

| US7572658B2 (en) | Method of manufacturing display panel for flexible display device | |

| CN101436569B (zh) | 薄膜晶体管阵列基板的制造方法及显示装置 | |

| US7758760B2 (en) | Thin film transistor array panel and method of manufacturing the same | |

| CN100458533C (zh) | 薄膜晶体管阵列面板及其制造方法 | |

| US7582501B2 (en) | Thin film transistor panel and manufacturing method thereof | |

| CN100543927C (zh) | 薄膜晶体管阵列面板及其制造方法 | |

| US20070080350A1 (en) | Panel for flexible display device and manufacturing method thereof | |

| CN1808266B (zh) | 光掩模和采用该光掩模的薄膜晶体管阵列面板的制造方法 | |

| KR20080030798A (ko) | 박막 트랜지스터 표시판의 제조 방법 | |

| KR20060136215A (ko) | 박막 트랜지스터 기판 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| ASS | Succession or assignment of patent right |

Owner name: SAMSUNG DISPLAY CO., LTD. Free format text: FORMER OWNER: SAMSUNG ELECTRONICS CO., LTD. Effective date: 20121219 |

|

| C41 | Transfer of patent application or patent right or utility model | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20121219 Address after: Gyeonggi Do, South Korea Patentee after: Samsung Display Co., Ltd. Address before: Gyeonggi Do, South Korea Patentee before: Samsung Electronics Co., Ltd. |

|

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20100512 Termination date: 20170707 |

|

| CF01 | Termination of patent right due to non-payment of annual fee |