CN1436331A - 多存储库dimm中实现的每个周期内的多重访问 - Google Patents

多存储库dimm中实现的每个周期内的多重访问 Download PDFInfo

- Publication number

- CN1436331A CN1436331A CN01809630A CN01809630A CN1436331A CN 1436331 A CN1436331 A CN 1436331A CN 01809630 A CN01809630 A CN 01809630A CN 01809630 A CN01809630 A CN 01809630A CN 1436331 A CN1436331 A CN 1436331A

- Authority

- CN

- China

- Prior art keywords

- dimm

- data

- data line

- memory

- switchgear

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4204—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus

- G06F13/4234—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus being a memory bus

- G06F13/4243—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus being a memory bus with synchronous protocol

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/1042—Read-write modes for single port memories, i.e. having either a random port or a serial port using interleaving techniques, i.e. read-write of one part of the memory while preparing another part

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Dram (AREA)

Abstract

本发明公开了一种计算机存储器系统,它能够提供双数据速率(DDR)存储器输出同时只需具有现有技术的DDR存储器芯片频率限制的一半频率的存储器芯片。该系统包括一个含有数据线106的第一存储器库101以及一个含有数据线107的第二存储器库102。一个基本系统时钟利用锁相环140或其它相移器件而产生一个延迟的时钟信号。第一存储器库的数据线与时钟信号104同步地和数据总线116相连,第二存储器库的数据线则与时钟信号105同步地和数据总线114相连。作为结果,数据总线不会同时与两个存储器库的数据线相连接,而是交替地与第一数据存储库和第二数据存储库连接。

Description

本申请要求获得申请日为99年6月22日、申请号为60/141,219以及申请日为99年5月17日、申请号为60/134,511的在先临时申请的优先权。

发明领域

本发明涉及在计算机存储器中提高数据访问速度而不增加存储器的基本时钟频率。

与现有技术有关的说明

术语

本说明书中使用了以下术语:

DIMM=双直列存储器模块

SDRAM=同步动态随机存储器

DDR=双数据速率,数据比特宽度等于时钟频率的二分之一。在基本时钟的一个周期内使用两比特数据,见图1B。

DBR=双总线速率

SDR=单总线速率

DBF=数据比特频率。每条引线每秒的比特数,称为xx比特/秒/引线

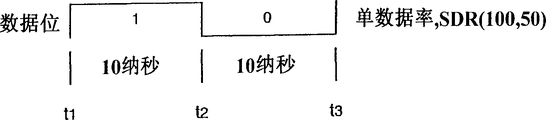

DR=数据速率。数据比特宽度等于一个基本时钟周期,见图1A。

定义:双总线速率(DBR)

为了达到说明的目的,在本文中使用了术语DBRTM(双总线速率)。双总线速率的意思是:进出总线系统的数据速率为与总线连接的各单独芯片在其运行时钟频率上传送数据时的数据速率的两倍。现有技术

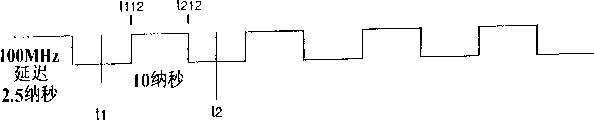

目前,对提高存储器子系统中的吞吐量的期望要求存储器件高速运行。也就是说,按照确定的基本频率运行的单数据速率型SDR存储器芯片将产生一个基本频率周期的数据速率DR。100MHz的DR意味着各个数据比特的宽度等于100MHz频率的一个周期,也就是10纳秒。从DRAM芯片输出的数据比特脉宽为基本时钟的一个周期。因此,如图1A所示,当基本时钟为100MHz时,在1和0之间变化的任何数据比特的实际频率[MPW1]为50MHz。

与当前使用的存储器芯片封装结构有关的是,为了满足一个所需的数据总线(DATA BUS)宽度,多组诸如SDRAM的存储器芯片被在一个印刷电路板上组装在一起。(最小的总线宽度是从一组中只有一个SDRAM芯片传送出的实际比特数)。这些板被以多种形式构成,如SIMM、DIMM、SODIMM、RIMM等。但是,为了简单起见,以下将用术语DIMM来代表其中任意一种或者所有这些不同的类型。

现有的168线DIMM模块(该设计应用于具有任何其它引线数的任何DIMM,或者任何具有其它名称的其它封装)使用了(由JEDEC1协会定义)72数据比特总线、控制线、地址线、电源以及时钟。由JEDEC标准定义的现行模块至多可容纳两库或两行SDRAM芯片。根据系统架构的不同,也可以采用其它的存储库结构。对存储库的选择是由一个选片(CS)线或者由选片线与其它控制线的组合来控制的。DIMM模块或是一个寄存器结构,或是一个非寄存器结构。在寄存器结构中,在所有地址和控制线提供给待被选择进行操作的器件之前被首先锁存入一个寄存器。而在非寄存器[MPW2]结构中,地址和控制线被直接从DIMM的输入连接器连接到其它器件。上述任何一种结构都可含有一个用于时钟同步的锁相环(PLL),或者也可利用系统提供给DIMM的时钟。如图1A所示,在存储器芯片的基本工作频率为100MHz时钟的频率时,所述模块只能产生100MHz的最大DR。如果将时钟频率提高至133MHz,并且使DIMM上的SDRAM器件在133MHz下工作,则最大DR可增加至133MHz。为了达到200MHz的DR,SDRAM芯片必须在200MHz的基本频率下工作。要使SDRAM芯片能在较高频率下工作,就需要开发资金、时间并且还需要提高硅晶速度以及其处理工艺。密度和速度是相互影响的。当密度增加时,速度只会下降,因为需要多级互联以实现电路,所以会给电路路径引入更多的延迟。另外,在硅晶中实现高速和高密度已经越来越难,在某些情况下甚至是不可能的。

在对采用100MHz时钟频率工作的SDRAM器件的DIMM[MPW3]的现有设计中,利用普通印刷电路板(PCB)的物理特性和线宽[MPW3]可以容易地实现设计。因此,利用现有技术很容易设计出一个具有100MHz基本时钟频率的DIMM存储器模块。而当人们试图制造出以200MHz时钟频率工作的器件时,就会出现问题。

现在参考图2,从其中可以看出,两个相同的存储器芯片100、102在其时钟输入端A和时钟输入端B上受到了同一个100MHz时钟的控制。芯片A的单比特输出端与芯片B的相应输出端107相连。在任何给定的时间内只有一个芯片被允许工作,而其它芯片则被输出端106和107上的内部芯片电路的高阻抗隔离起来。芯片A的选片(CS)输入端120允许芯片A访问数据,相应的输入端121则可同样用于芯片B。这种架构是利用现有技术制造DIMM模块的基础。

上述两个芯片都以同样的时钟工作。引线D102、107上的数据比特来自芯片A或者芯片B。现在参考图2B,芯片A的输入引线104和芯片B的输入引线105上出现的时钟具有100MHz的频率。一个典型的时钟周期从具有正向信号的t1开始并且在10纳秒后的t2结束。如图2C所示,典型的数据信号与数据信号同步,因此数据“1”的状态从t1开始并在t2结束,而后面的数据“0”则从t2开始并在t3结束。应该注意的是,可由该系统处理的最高带宽数据信号是一个在1和0之间交替变化的信号。仍然参考图2C,从其中可以看出,虽然以每秒比特数计量的数据速率与时钟频率一致,但这种数据信号的频率为时钟频率的二分之一。

作为结果,采用现有技术的系统中向存储器总线传送的最高数据传送速率DR与存储器芯片A或B的设计数据传送速率是相等的。

JEDEC小组已开发出了一种架构,在这种架构中,一比特数据的有效宽度等于基本时钟频率的二分之一。这个方案被称为DDR(双数据速率)技术。利用这种SDRAM器件设计出的DIMM被称为是DDRDIMM。虽然这种DDR存储器已经存在,但它们需要存储器芯片在两倍的时钟频率下工作。这种高速存储器芯片的制造成本高并且难以制造。

现在参考图1A至1C,其中示出了本文中所述的各种信号的速率。首先参考图1A和图1B,前者示出了一个100MHz时钟的波形,后者则示出了现有技术的DIMM中的一个典型数据总线信号(为了便于说明,图中只示出了一个比特)。各个数据比特与时钟信号的正向沿t1同步开始。这个波形是典型的采用现有技术的SDR结构。

作为对比,现有技术中的DDR数据总线以SDR速率的两倍进行工作。现在参考图1C,DDR数据信号的各个数据比特或者从时钟信号的正向沿t1开始,或者从时钟信号的反向沿t1开始。

目前,所采用的器件包含100MHz基本时钟频率和DDR型100MHz数据比特频率。为了达到说明的目的,这类器件被称为SDRAMDDR器件(100,100)。本发明将揭示出一种能够利用SDRAM芯片(100,100)产生400MHz DR和200MHz数据比特频率的系统。该系统被称为双数据速率/双总线速率(DDR/DBR)系统。

利用本发明所述的技术,可以在采用100MHz时钟频率的数据总线上产生400MHz的DR或200MHz的DBF。作为对比,在采用现有技术的情况下,利用现有SDRAM器件所能够实现的最快速度也只是SDRAM器件自身的速度。但是,通过采用本发明所述的技术,就可使现有的SDRAM(无论是SDR还是DDR)能够在数据总线上产生双倍的器件DR。见图1C至1F。

发明内容

本发明的一般目的是提供一种使用SDR存储器芯片的DDR存储器架构。本发明的另一个目的是组合DDR存储器芯片以产生四倍速的输出。

根据本发明的一个方面,一种具有数据总线的计算机存储器系统包括:含有数据线的第一列存储器库;含有数据线的第二列存储器库;以及含有多个周期的时钟信号,其中每个周期都含有一个起点并且具有一个周期p;另外,所述系统还包括一个第一开关装置,用于在各个所述周期开始时将所述第一存储器库的数据线与数据总线连接起来,并且持续p/2时间;以及一个第二开关装置,用于在各个所述周期开始后的p/2时刻将所述第二存储器库的数据线与数据总线连接起来,并且持续后面的p/2时间;

根据本发明的第二个方面,所述计算机存储器系统还包括一个相对于时钟信号具有180度相差的延迟时钟信号,并且所述第二开关装置与所述延迟时钟信号同步工作。

根据本发明的第三个方面,该系统包括一个主板,用于产生所述延迟时钟信号的装置、第一存储器库、第二存储器库、第一开关装置以及第二开关装置都位于该主板之上。

根据本发明的第四个方面,该系统包括一个或多个DIMM板,并且用于产生所述延迟时钟信号的装置、第一存储器库、第二存储器库、第一开关装置以及第二开关装置都位于该板之上。

根据本发明第五个方面,所述第一开关装置包括第一FET开关,所述第二开关装置包括第二FET开关。

根据本发明第六个方面,所述第一FET开关包括一个控制输入端、与数据总线连接的第一端、以及与所述第一存储器库的数据线连接的第二端。另外,所述第二FET开关包括一个控制输入端、与数据总线连接的第一端、以及与所述第二存储器库的数据线连接的第二端。

根据本发明第七个方面,所述第一开关装置包括在第一存储器芯片上工作的第一数据使能信号,所述第二开关装置包括在第二存储器芯片上工作的第二数据使能信号。

根据本发明第八个方面,该系统还包括一个电路,该电路含有一个输入端和一个输出端,其输入端与时钟信号相连,其输出端与所述延迟时钟信号相连,该电路从由线长延迟电路、非对称输出驱动延迟电路、级联PLL延迟电路、非对称输出PLL延迟电路、外部PLL延迟电路、无源元件延迟电路以及可编程延迟线组成的一组电路中选择出来。

根据本发明第九个方面,一种含有数据总线的计算机存储器系统包括:含有数据线的第一存储器库、含有数据线的第二存储器库、以及含有多个周期的时钟信号,其中每个周期都含有一个起点并且具有一个周期p。另外,所述系统还包括第一开关装置,用于在各个所述周期开始时将所述第一存储器库的数据线与数据总线连接起来,并且持续p/4时间,然后在各个所述周期开始之后的p/2时刻再次启动,并且持续p/4时间。另外,所述系统还包括第二开关装置,用于在各个所述周期开始后的p/4时刻将所述第二存储器库的数据线与数据总线连接起来,并且持续p/4时间,然后在各个所述周期开始之后的3p/4时刻再次启动,并且持续p/4时间。

附图说明

通过以下的文字说明并结合用于描述优选实施例的附图,本发明的上述及其它特征将获得更好的理解。其中

图1A描绘出了一个系统时钟波形;

图1B描绘出了一个典型的SDR数据流;

图1C描绘出了一个典型的DDR数据流;

图1D描绘出了一个与系统时钟呈90度相移的延迟时钟;

图1E描绘出了从本发明所述的存储器库中输出的典型的四倍数据速率数据流;

图1F描绘出了从本发明所述的另一存储器库中输出的典型的四倍数据速率数据流;

图2A描绘出了根据本发明所述的最简单的实施例;

图2B描绘出了一个在SDR存储器系统中使用的典型系统时钟;

图2C描绘出了现有技术中输出至数据总线的SDR;

图3A描绘出了本发明的优选实施例的电路图;

图3B描绘出了本发明优选实施例的DDR数据流;

图3C描绘出了在本发明优选实施例中使用的系统时钟;

图3D描绘出了根据本发明优选实施例所述的存储器库A的输出;

图3E描绘出了在本发明优选实施例中使用的延迟时钟;

图3F描绘出了根据本发明优选实施例所述的存储器库B的输出;

图4A描绘出了本发明的可替换实施例的电路图;

图4B描绘出了在本发明的可替换实施例中使用的系统时钟;

图4C描绘出了在本发明的可替换实施例中使用的延迟时钟;

图4D描绘出了从本发明的可替换实施例所述的存储器库A中输出的数据流;

图4E描绘出了从本发明的可替换实施例所述的存储器库B中输出的数据流;

图5A中描绘了一个在修改DBR的实施例中作为参考的系统时钟;

图5B中描绘了一个DBR输出;

图5C中描绘了在修改DBR的实施例中DBR存储器库A的输出;

图5D中描绘了在修改DBR的实施例中DBR存储器库B的输出;

图5E中描绘了在修改DBR的实施例中所产生的数据总线数据流;

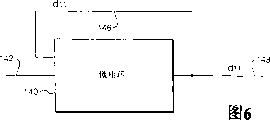

图6描绘出了一个锁相环(PLL);

图7描绘出了一个非对称PLL。

图8中描绘了一个采用现有的DIMM作为存储器库的实施例。

具体实施方式

在理解典型计算机存储器可具有64或72比特的前提下,以下的讨论中对存储器的单比特操作进行了说明。单比特的操作可被推广至构成单个存储器读取或写入的64或72比特。在实际情况中,单个存储器芯片具有8比特或更多,并且需要有8或9个存储器芯片来形成一个单存储器字。但是,为了使以下的说明简单明了,所以在下面的说明中只采用具有单比特输出的单个芯片。

参考图3A,存储器芯片A100和B102被允许操作并且被允许按照它们各自的时钟,时钟A104和时钟B106(它们都工作于100MHz的频率),进行工作。本例中,时钟B相对于另一时钟被移动或延迟了二分之一个周期,如图3C所示。在各个数据比特的输出端上串联插入了一个FET开关。FET开关A110对应于存储器芯片A,FET开关B111对应于存储器芯片B。存储器芯片A的输出端108与FET开关A110的输入端相连。FET开关A受到使能信号A112的控制。类似地,存储器芯片B的输出由FET开关B113进行切换。FET开关A116的输出端与FET开关B114的输出端相连。在本优选实施例中,两个输出都与DIMM的一个连接器相连,该连接器可以是宽数据总线的一部分。

当FET开关被允许操作时,通过该开关的数据路径将对信号带来非常微小的延迟。而当开关被禁止时,数据路径将呈高阻抗以使信号不能通过。在以下的例子中,数据总线上的数据流被显示在图3B中。图3C所示的时钟具有一个周期p,它等于t3-t1。现在参考图3D,其中显示了FET开关A的输出信号,从该图中可以看出,当FET开关A110在t1上被激活并被允许保持激活状态半个周期直到t2为止然后被关闭直到t3为止时,存储器芯片A的输出端只在半个周期内被连接至数据总线114,116。接下来参考图3F,其中显示了FET开关B的输出信号,在从t2开始的下半个周期,当FET开关B被激活并被允许保持激活状态半个周期直到t3然后被关闭半个周期时,存储器芯片B的输出端只在另外半个周期内被连接至数据总线114,116。随着上述过程的持续进行,数据总线将在存储器芯片A和B之间被交替连接,从而在每个时钟周期p中产生两个数据比特。这个结果符合DDR标准,即,总线上的数据速率为SDR系统标准下数据速率的两倍。

虽然现有技术中的器件也能够产生DDR输出,而本发明揭示了一种可利用单数据速率存储器芯片实现的DDR操作的方法。各个存储器芯片持续以SDR速度工作,并在每个时钟周期内产生一个数据比特。但是,通过将存储器芯片数据输出的宽度减少至半个时钟周期,就可以利用另外半个周期输出来自第二存储器芯片的数据。通过将采样时间减少为相应存储器芯片的实际数据时间的一半,FET开关就可产生使存储器芯片自身的带宽加倍的效果。第二优选实施例

如果存储器芯片A和B被设计成按照DDR速度工作,每个芯片都以与基本时钟频率相等的速率产生输出数据,则通过利用一个时钟给芯片B增加1/4周期,并且给用于使数据在数据总线上保持有效的FET开关也增加1/4个时钟周期,就可以实现在一个时钟周期内有四个数据比特传送至数据总线。本实施例中,FET开关的输出信号由图1E和图1F示出。

通过继续参考图3A来说明本发明中所用组件的互联,就可使本实施例得到更好的理解。现在参考图1A,系统时钟具有一个等于t2-t1的周期p,图1D中示出了加载给芯片B的90度相移时钟。图1E描绘了存储器芯片A输出至数据总线114,116的数据。存储器芯片A的输出106与数据总线连接半个周期t12-t1,同时,存储器芯片B的输出107在t12时刻开始与数据总线相连,并且与存储器芯片A的输出一样持续半个周期有效。

如图1E所示,在下面对“四速”信号的说明中,间隔t2-t1将被称为p(波形的周期),并且直接跟随在t1之后的间隔在图中被标为“1”,用于表示信号的TRUE(真值)状态,它被称为δt。间隔t12-t1将被称为p/2。当参考图1F时也使用了这些标记。应该注意,图1F所示的波形与图1E所示的波形相类似,只是延迟了p/4的间隔。

各个数据比特有效宽度只适用于所需的接收数据的器件的建立和保持时间。随着硅技术速度的提高,用于使数据比特有效的建立和保持时间也相应减小。因此,只利用部分数据比特的有效宽度不会影响操作的可靠性,而只会大大提高速度。

上述例子涉及了两个存储器器件。这些器件可被安装在一个模块或者一个主板上。存储器芯片以外的其它器件也可采用本发明的技术,以达到增加数据总线带宽而不增加器件的实际工作频率的目的。如果在一个DIMM板上使用了多个存储器器件,并且采用了图3所示的FET开关连接以用于各个数据比特,则整个总线宽度将以一个宽的带宽数据速率被执行。

在DIMM上使用的整体结构也可被应用到一个主板上以取代DIMM板。诸如RAS(行地址选择)、CAS(列地址选择)、WE(写使能)以及CS(片选)的控制线的组合通常[MPW5]被用于诸如存储器芯片的器件的操作。通常,这些控制线上的信号是利用100MHz时钟的上升沿进入器件中进行时钟控制的。根据本发明的第一个优选实施例所述,各个器件输出端上的数据是与控制该器件的时钟的上升沿有关的。[MPW6]

如果来自一个SDRAM器件的数据比特被允许在10纳秒宽度的一半时间内在数据总线上保持有效,如图1C所示,并且所述时间的另一半被用于来自另一个SDRAM器件的有效数据,则可以产生200MHz的数据速率DR。此举可在以100MHz时钟速率和100MHz数据速率工作的普通SDRAM器件上实现。

作为一个额外的可替换方法,可以利用一个FET来复用两个存储器模块的输出以取代采用两个FET开关的做法。在这种结构中,FET开关具有两个输入端,每个输入端都与一个单独的存储器芯片输出相连,该FET的输出端与数据总线连接。不含有FET开关的可替换实施例

在本发明的另一个可替换实施例中,存储器芯片输出的切换是由存储器芯片自身完成的,而没有使用FET开关。

本实施例中,两个SDRAM存储器芯片自身都具有与DIMM板连接器130相连的数据输出引线,如图4A所示。这种连接既可以在主板上也可以在DIMM上。

如图4(C)所示,芯片B102拥有自己的时钟,它相对于图4B所示的基本时钟移动了二分之一个周期。

在本实施例中,当被相应的输出使能信号124、126允许操作时,各个SDRAM存储器芯片都在其输出引线106、107上使数据比特保持有效,而当不被激活时,它们将转换至高阻抗状态。这类器件被称为是三态器件,其输出可以是逻辑0、逻辑1以及高阻抗状态。

现在参考图4D,从其中可以看出,与存储器芯片A101相对应的数据比特是在各个周期(t1和t3之间)的前半个周期内有效的。另一方面,存储器芯片B102是在各个周期的后半个周期内有效的,即,t2与t3之间。

另外,根据一个附加的控制信号,各个存储器芯片既可在时钟周期前半个周期也可在其后半个周期内被控制为有效。

在存储器芯片是DDR芯片的情况下,两个存储器芯片的输出在宽度上可被减少至四分之一周期,并且可被聚在一起以在图1E和1F所示的前半个或后半个周期内变为有效。这种数据频率的增加可在各个SDRAM芯片的内部实现。SDRAM的输出与数据总线的连接或者由SDRAM内部电路控制,或者由一个外部输出使能(OE)控制线控制。如图4A所示,当两个DDR器件如图4A所示被连接在一起时,芯片将在一个基本时钟周期内产生四个数据比特,如图5E所示。基本时钟自身如图5A所示,它所具有的一个周期等于t3-t1。

上述SDRAM芯片内部结构可以是这样的,即,它可以在内部产生四个数据比特而不是利用外部控制和连接。图5B所示的波形示出了未改进的从一个DDR芯片输出的两个数据比特,其中,第一数据比特位于t1和t2之间,第二数据比特位于t2和t3之间。图5C所示的波形示出了改进后在四分之一个基本时钟周期的宽度内的两个数据比特,其中,第一数据比特出现于t1和t12之间,第二数据比特出现于t12和t2之间。这些数据比特只在所述周期的前半段中有效。图5D所示波形示出了两个改进的DDR数据比特在基本时钟周期的后半段(t2:t3)有效。因此,当芯片被按照如图4A所示连接起来时,并且存储器芯片A101和存储器芯片B102为DDR芯片时,它们产生的最终结果将是在一个基本时钟周期内产生4个数据比特,如图4E所示。此举对输入数据流和输出数据流都是可行的。

各个SDRAM存储器芯片内都有一个控制器,它含有一个数据接收器。当数据被传送入该计数器中时,它一定是与基本系统时钟同步的,如图5A所示。为了实现对进入控制器的接收器的数据计时,可以采用多种办法。如果具有图5E所示波形的数据流被SDRAM产生,则SDRAM内部可以产生具有相同波形的时钟。这个时钟可被各个SDRAM的所述控制器用来将数据锁存入它们各自的寄存器以进行处理。

在分组技术中上述内容还有更好的速度优势。通常,在含有两个上述存储器库的系统中,第一存储器库是由构成第一库的存储器芯片阵列组成的,而第二存储器库则是由构成第二库的存储器芯片阵列组成的。但是,根据本发明所述,以下方法是有益处的,即,在一个衬底内包含两个这种存储器芯片的电路,使其中一个电路用在第一库中,并使另一个电路用在第二库中,同时在两个芯片的输出之间进行切换以形成一个数据总线输出。这种结构比现有技术具有更好的速度优势,因为第一和第二存储器库芯片之间的数据路径的距离被大大缩小。不含有相位延迟时钟的实施例

在本发明的另一个优选实施例中,存储器库A和B都是DDR存储器。相同的时钟信号被用于使存储器库A和存储器库B同步。

在各个周期的起始处,存储器库A产生一个第一内部输出,它在基本时钟周期的p/4宽度内保持有效,并且在所述周期开始后的p/2时刻产生第二内部输出,它持续p/4的宽度。存储器库B在所述周期开始后的p/4时刻开始,产生第三内部输出,它在基本时钟周期的p/4宽度上保持有效,存储器库B还在所述周期开始后的3p/4时刻再产生一个第四内部输出,它也持续p/4的宽度。

在将这些内部输出输出至数据总线之前,第一和第二内部输出被互换,并且第三和第四内部输出也被互换。结果,数据总线上的数据将在时钟周期的前半个周期内含有来自存储器芯片A的数据比特,并且在时钟周期的后半个周期内含有来自存储器芯片B的数据比特。对时钟延迟产生的说明

有多种方法可用于在按照本发明所述内容使用的SDRAM器件或其它器件的内部产生辅助时钟。

像上面指出的那样,根据特定实施例,供给存储器模块的主时钟被相移或延迟了半个周期、180度,或者四分之一周期、90度。

为了进行高速运行,一种产生延迟时钟信号的方法是在具有相同相位的多个输出中使用一个时钟驱动器或者锁相环(PLL),用以在最小容性负载的情况下驱动多个SDRAM芯片。图6中示出了一个简单的PLL140。

该PLL具有一个输入端140和一个输出端148,在PLL的输出与负载(未示出)之间有一个固定的时间延迟dt1。一反馈信号146具有相同的时间延迟dt1。结果,输出将被锁相至负载上得到的信号。

非对称驱动器被定义为具有一个输入端,两个或多个输出端,其每个输出端相对于输入端都具有不同的相角或延迟。

PLL的一个变种是非对称PLL,如图7所示。该非对称PLL含有输入端152以及两个单独的输出端156和158。与具有相同相位的多个输出端的其它各种PLL不同的是,非对称PLL的输出端156和158之间具有相位延迟,它们可被用于驱动本发明所需的多个时钟。

由于PLL的输出与其输入时钟具有相位同步能力,所以任何PLL输出都可被用作产生延迟的时钟或移相的时钟。为了产生一个延迟时钟以用于驱动其输出被用来驱动第二库的SDRAM器件的第二PLL,可以采用两种方法来产生一移相或延迟时钟信号。

PLL的相移或延迟可通过多种方式产生。PLL可以含有一个PLL内部延迟,从而使其输出自动相对于输入产生延迟。或者,也可以在两个PLL电路之间串联插入一个延迟线或电路,从而产生一个级联的PLL延迟电路。

一种建议的方法是利用DIMM所产生的时钟来驱动SDRAM的第一库。如果要在DIMM上实现时钟延迟,可以引入一个印刷线路长度以精确给出所需的延迟,进而产生一个被移相的时钟。然后,这个移相的时钟被用于驱动第二PLL。第二PLL的输出是经过延迟的时钟,它用来驱动两库SDRAM中的第二库。所需的线路长度可通过模拟、理论计算以及试凑法来确定。

如果经延迟的时钟是在一主板上产生,则DIMM也可使用位于该主板上的延迟时钟来驱动位于DIMM之上的PLL。PLL的输出将驱动库中的SDRAM芯片。

产生第二相位延迟时钟的其它方法包括使用延迟线芯片,它也可用于实现延迟时钟所需的预定相移。另外,也可以采用无源和有源电路的组合来实现所需的相移,其中包括目前可以商用的可编程延迟线。由于这些器件和技术在本领域中是公知的,故此不再赘述。使用现有DIMM的系统

上述技术可被用于利用现有DIMM来提高存储器的速度。可以参考图8来了解这种系统。图8中所示的全部组件都安装于主板之上,并且DIMM模块被插入到DIMM连接器166、168、182以及184内。

在最后一个实施例中,DIMM模块自身成为存储器库。DIMM被插入到DIMM连接器166和168中,从而分别形成等价的第一和第二存储器库。连接器116中来自或去向第一DIMM的数据172被FET开关160接通或切断至数据总线。类似地,数据170被同一FET开关60切换至安装在DIMM连接器168中的第二DIMM。锁相环相移倍增器产生时钟信号174和176,它们互相正交,用于首先允许操作第一DIMM,然后再允许操作第二DIMM。

使能信号180由PLL电路164产生,它产生的信号类似于图3A所示的FET EN A 112和FET EN B 113,在本实施例中,这些信号交替地允许操作第一DIMM和第二DIMM。

图8中还示出了第二套DIMM连接器182、184,通过将另外两个DIMM插入到上述连接器中就形成了第三和第四存储器库。这两个额外的DIMM与上述第一和第二DIMM的工作方式完全相同,并且它们具有自己的FET开关178以及正交时钟信号190和192,等等。

当DDR DIMM被采用时,产生一个四速存储器系统,每个DDRDIMM都起到上述实施例中的DDR数据存储库的作用。

本实施例的优点在于它使用了现有形式的DIMM,这样只需通过制造一种主板就可以享受到本发明所提供的速度和访问时间上的优势。在数位分组技术上的其它应用

下面的目录列出了本文所述技术在其它方面的应用。这个目录不是十分完整,也不能排除本发明所述技术在其它方面的应用。

1.计算机存储器子系统。

2.在一模块或主板上的单个计算机存储器芯片的结构。

3.在一模块或主板上的闪存芯片的结构。

4.在一模块或主板上的EEPROM存储器芯片,在一模块或主板上的单个逻辑芯片。

5.从相同或不同的源进行数据传输的数据总线的结构。

6.用于数据和控制线以实现高速交换的微处理器总线的结构。

7.CPU总线复用以在不提高时钟速度的情况下增加带宽。

8.DSP总线复用以在不提高基本时钟频率的情况下增加带宽。

9.在硅晶水平上的单个存储器芯片用于产生高的数据速率而不提高基本时钟速度。

本领域的普通技术人员应该明白,各种在本发明范围之内作出的改进和修改都不会脱离由附带权利要求所定义的本发明的精神。

Claims (49)

1.一种具有数据总线的计算机存储器系统,包括:

(a)含有数据线的第一列存储器库;

(b)含有数据线的第二列存储器库;

(c)含有多个周期的时钟信号,其中每个周期都含有一个起点并且具有一个周期p;

(d)第一开关装置,用于在各个所述周期开始时将所述第一存储器库的数据线与数据总线连接起来,并且随后持续p/2时间;以及

(e)第二开关装置,用于在各个所述周期开始后的p/2处将所述第二存储器库的数据线与数据总线连接起来,并且随后持续p/2时间。

2.根据权利要求1所述的计算机存储器系统,其中还包括一个相对于所述时钟信号具有180度相差的延迟时钟信号,并且所述第二开关装置与所述延迟时钟信号同步工作。

3.根据权利要求2所述的系统,其中还包括一个主板,并且用于产生所述延迟时钟信号的装置、第一存储器库、第二存储器库、第一开关装置以及第二开关装置都位于该主板之上。

4.根据权利要求2所述的系统,其中还包括一个或多个DIMM板,并且用于产生所述延迟时钟信号的装置、第一存储器库、第二存储器库、第一开关装置以及第二开关装置都位于该DIMM板之上。

5.根据权利要求3或4所述的系统,其中所述第一开关装置还包括第一FET开关,并且所述第二开关装置还包括第二FET开关。

6.根据权利要求5所述的系统,其中:

所述第一FET开关还包括一个控制输入端、与数据总线连接的第一端、以及与所述第一存储器库的数据线连接的第二端;所述第二FET开关包括一个控制输入端、与数据总线连接的第一端、以及与所述第二存储器库的数据线连接的第二端。

7.根据权利要求3或4所述的系统,其中所述第一开关装置包括一个在第一存储器库上工作的第一数据使能信号,所述第二开关装置包括一个在一第二存储器库上工作的第二数据使能信号。

8.根据权利要求7所述的系统,其中还包括一个相移电路,该电路含有一个输入端和一个输出端,其输入端与时钟信号相连,其输出端与所述延迟时钟信号相连,该电路从以下一组电路中选出:

线长延迟电路;

非对称输出驱动延迟电路;

级联PLL延迟电路;

非对称输出PLL延迟电路;

外部PLL延迟电路;

无源元件延迟电路;以及

可编程延迟线。

9.一种具有数据总线的计算机存储器系统,包括:

(a)含有数据线的第一DDR存储器库;

(b)含有数据线的第二DDR存储器库;

(c)含有多个周期的时钟信号,其中每个周期都含有一个起点并且具有一个周期p;

(d)第一开关装置,用于在各个所述周期开始时将所述第一存储器库的数据线与数据总线连接起来,并且持续p/4时间,然后在所述各个周期开始后的p/2时刻再次启动,并且随后持续p/4的时间;以及

(e)第二开关装置,用于在各个所述周期开始后的p/4时刻开始将所述第二存储器库的数据线与数据总线连接起来,并且随后持续p/4时间,然后在所述各个周期开始后的3p/4时刻再次启动,并且随后持续p/4的时间。

10.根据权利要求9所述的计算机存储器系统,其中还包括一个相对于所述时钟信号具有90度相差的延迟时钟信号,并且所述第二开关装置与所述延迟时钟信号同步工作。

11.根据权利要求10所述的系统,其中还包括一个主板,并且用于产生所述延迟时钟信号的装置、第一存储器库、第二存储器库、第一开关装置以及第二开关装置都位于该主板之上。

12.根据权利要求10所述的系统,其中还包括一个或多个DIMM板,并且用于产生所述延迟时钟信号的装置、第一存储器库、第二存储器库、第一开关装置以及第二开关装置都位于该DIMM板之上。

13.根据权利要求11或12所述的系统,其中

所述第一开关装置还包括第一FET开关;并且

所述第二开关装置还包括第二FET开关。

14.根据权利要求13所述的系统,其中:

所述第一FET开关还包括一个控制输入端、与数据总线连接的第一端、以及与所述第一存储器库的数据线连接的第二端;所述第二FET开关包括一个控制输入端、与数据总线连接的第一端、以及与所述第二存储器库的数据线连接的第二端。

15.根据权利要求11或12所述的系统,其中所述第一开关装置包括一个在第一存储器库上工作的第一数据使能信号;并且

所述第二开关装置包括一个在一第二存储器库上工作的第二数据使能信号。

16.根据权利要求15所述的系统,其中还包括一个相移电路,该电路含有一个输入端和一个输出端,其输入端与时钟信号相连,其输出端与所述延迟时钟信号相连,该电路从以下一组电路中选出:

线长延迟电路;

非对称输出驱动延迟电路;

级联PLL延迟电路;

非对称输出PLL延迟电路;

外部PLL延迟电路;

无源元件延迟电路;以及

可编程延迟线。

17.一种具有数据总线的计算机存储器系统,包括:

(a)含有数据线的第一列存储器库;

(b)含有数据线的第二列存储器库;

(c)含有多个周期的时钟信号,其中每个周期都含有一个起点并且具有一个周期p;

(d)第一开关装置,用于在各个所述周期开始时将所述第一存储器库的数据线与数据总线连接起来,并且持续δt时间,然后在所述各个周期开始后的p时刻再次启动,并且随后持续δt时间;以及

(e)第二开关装置,用于在各个所述周期开始后的p/2时刻开始将所述第二存储器库的数据线与数据总线连接起来,并且随后持续δt时间,然后在所述各个周期开始后的3p/4时刻再次启动,并且随后持续δt时间。

18.根据权利要求17所述的计算机存储器系统,其中还包括一个第一控制信号,用于使所述第一存储器库或者在各个周期开始时或者在各个周期开始后的p/2时开始输出数据;以及一个第二控制信号,用于使所述第二存储器库或者在各个周期开始时或者在各个周期开始后的p/2时开始输出数据。

19.根据权利要求18所述的系统,其中还包括一个主板,并且所述第一存储器库、第二存储器库、第一开关装置以及第二开关装置都位于该主板之上。

20.根据权利要求18所述的系统,其中还包括一个或多个DIMM板,并且所述第一存储器库、第二存储器库、第一开关装置以及第二开关装置都位于该DIMM板之上。

21.根据权利要求19或20所述的系统,其中

所述第一开关装置还包括一个工作于所述第一存储器库之上的第一数据使能信号,并且

所述第二开关装置还包括一个工作于所述第二存储器库之上的第二数据使能信号。

22.一种具有数据总线的计算机存储器系统,包括:

(a)含有数据线的第一DDR存储器库;

(b)含有数据线的第二DDR存储器库;

(c)含有多个周期的时钟信号,其中每个周期都含有一个起点并且具有一个周期p;

(d)第一开关装置,用于在所述第一存储器库内产生信号s1,该信号包括:间隔i1,始于各个周期的起始处,并且随后持续δt1时间;以及间隔i2,始于各个周期起始后的p/2处,并且随后持续δt1时间;

(e)第二开关装置,用于在所述第二存储器库内产生信号s2,该信号包括:间隔i3,始于各个周期开始后的p/4处,并且随后持续δt1时间;以及间隔i4,始于各个周期起始后的3p/4处,并且随后持续δt1时间;

(f)根据信号s1工作的第三开关装置,用于对间隔i1内的信号与间隔i2内的信号进行交换,并且将信号s1连接至所述第一存储器库的数据线;

(g)根据信号s2工作的第四开关装置,用于对间隔i3内的信号与间隔i4内的信号进行交换,并且将信号s1连接至所述第二存储器库的数据线;

(h)组合装置,用于连接所述第一存储器库的数据线与所述第二存储器库的数据线。

23.根据权利要求22所述的系统,其中所述第一开关装置除了各个周期的间隔i1和i2期间以外都产生一个高阻抗输出,并且所述第二开关装置除了各个周期的间隔i3和i4期间以外都产生一个高阻抗输出

24.根据权利要求23所述的系统,其中所述第一开关装置包括第一FET开关,并且所述第二开关装置包括第二FET开关,各个FET开关都含有一个输入端和一个输出端,第一存储器库的数据线与第一FET开关的输入端相连,第二存储器库的数据线与第二FET开关的输入端相连,并且各FET开关的输出端都与数据总线相连接。

25.根据权利要求24所述的系统,其中还包括一个主板,并且所述第一存储器库、第二存储器库、第一、第二、第三和第四开关装置以及组合装置都位于该主板之上。

26.根据权利要求24所述的系统,其中还包括一个或多个DIMM板,并且所述第一存储器库、第二存储器库、第一、第二、第三和第四开关装置以及组合装置都位于该主板之上。

27.根据权利要求25或26所述的系统,其中所述第一存储器库包括多个第一存储器库子系统,所述第二存储器库包括多个第二存储器库子系统,该系统还包括多个硅晶衬底,各个所述衬底都分别含有一个第一存储器库子系统和一个第二存储器库子系统。

28.一种具有数据总线的计算机存储器系统,包括:

(a)含有数据线的第一DIMM存储器库;

(b)含有数据线的第二DIMM存储器库;

(c)含有多个周期的时钟信号,其中每个周期都含有一个起点并且具有一个周期p;

(d)第一开关装置,用于在各个所述周期开始时将所述第一DIMM的数据线与数据总线连接起来,并且随后持续p/2时间;以及

(e)第二开关装置,用于在各个所述周期开始后的p/2时刻将所述第二DIMM的数据线与数据总线连接起来,并且随后持续p/2时间。

29.根据权利要求28所述的计算机存储器系统,其中还包括一个相对于所述时钟信号具有180度相差的延迟时钟信号,并且所述第二开关装置与所述延迟时钟信号同步工作。

30.根据权利要求29所述的系统,其中还包括一个主板,并且用于产生所述延迟时钟信号的装置、用于所述第一DIMM的连接器、用于所述第二DIMM的连接器、所述第一开关装置以及第二开关装置都位于该主板之上。

31.根据权利要求30所述的系统,其中所述第一开关装置还包括第一FET开关,并且所述第二开关装置还包括第二FET开关。

32.根据权利要求31所述的系统,其中:

所述第一FET开关还包括一个控制输入端、与数据总线连接的第一端、以及与所述第一DIMM的数据线连接的第二端;并且

所述第二FET开关包括一个控制输入端、与数据总线连接的第一端、以及与所述第二DIMM的数据线连接的第二端。

33.根据权利要求30所述的系统,其中所述第一开关装置还包括一个在第一DIMM上工作的第一数据输出使能信号,所述第二开关装置包括一个在第二DIMM上工作的第二数据输出使能信号。

34.根据权利要求33所述的系统,其中还包括一个相移电路,该电路含有一个输入端和一个输出端,其输入端与时钟信号相连,其输出端与所述延迟时钟信号相连,该电路从以下一组电路中选出:

线长延迟电路;

非对称输出驱动延迟电路;

级联PLL延迟电路;

非对称输出PLL延迟电路;

外部PLL延迟电路;

无源元件延迟电路;以及

可编程延迟线。

35.一种具有数据总线的计算机存储器系统,包括:

(a)含有数据线的第一DDR DIMM;

(b)含有数据线的第二DDR DIMM;

(c)含有多个周期的时钟信号,其中每个周期都含有一个起点并且具有一个周期p;

(d)第一开关装置,用于在各个所述周期开始时将所述第一DIMM的数据线与数据总线连接起来,并且随后持续p/4时间,然后在所述各个周期开始后的p/2处再次启动,并且随后持续p/4的时间;以及

(e)第二开关装置,用于在各个所述周期开始后的p/4时刻将所述第二DIMM的数据线与数据总线连接起来,并且随后持续p/4时间,然后在所述各个周期开始后的3p/4时刻再次启动,并且随后持续p/4的时间。

36.根据权利要求35所述的计算机存储器系统,其中还包括一个相对于所述时钟信号具有90度相差的延迟时钟信号,并且所述第二开关装置与所述延迟时钟信号同步工作。

37.根据权利要求36所述的系统,其中还包括一个主板,并且用于产生所述延迟时钟信号的装置、用于安装所述第一DIMM的连接器、用于安装所述第二DIMM的连接器、第一开关装置以及第二开关装置都位于该主板之上。

38.根据权利要求37所述的系统,其中

所述第一开关装置还包括第一FET开关;并且

所述第二开关装置还包括第二FET开关。

39.根据权利要求38所述的系统,其中:

所述第一FET开关还包括一个控制输入端、与数据总线连接的第一端、以及与所述第一DIMM的数据线连接的第二端;并且

所述第二FET开关包括一个控制输入端、与数据总线连接的第一端、以及与所述第二DIMM的数据线连接的第二端。

40.根据权利要求37所述的系统,其中所述第一开关装置包括一个在第一DIMM上工作的第一数据使能信号;并且

所述第二开关装置包括一个在第二DIMM上工作的第二数据使能信号。

41.根据权利要求40所述的系统,其中还包括一个相移电路,该电路含有一个输入端和一个输出端,其输入端与时钟信号相连,其输出端与所述时钟信号相连,该电路从以下一组电路中选出:

线长延迟电路;

非对称输出驱动延迟电路;

级联PLL延迟电路;

非对称输出PLL延迟电路;

外部PLL延迟电路;

无源元件延迟电路;以及

可编程延迟线。

42.一种具有数据总线的计算机存储器系统,包括:

(a)含有数据线的第一DIMM;

(b)含有数据线的第二DIMM;

(c)含有多个周期的时钟信号,其中每个周期都含有一个起点并且具有一个周期p;

(d)第一开关装置,用于在各个所述周期开始时将所述第一DIMM的数据线与数据总线连接起来,并且随后持续δt时间,然后在所述各个周期开始后的p时刻再次启动,并且随后持续δt时间;以及

(e)第二开关装置,用于在各个所述周期开始后的p/2处将所述第二DIMM的数据线与数据总线连接起来,并且随后持续δt时间,然后在所述各个周期开始后的3p/4时刻再次启动,并且随后持续δt时间。

43.根据权利要求42所述的计算机存储器系统,其中还包括一个第一控制信号,用于使所述第一DIMM或者在各个周期开始时或者在各个周期开始后的p/2时开始输出数据;以及一个第二控制信号,用于使所述第二DIMM或者在各个周期开始时或者在各个周期开始后的p/2时开始输出数据。

44.根据权利要求43所述的系统,其中还包括一个主板,并且用于安装所述第一DIMM的连接器、用于安装所述第二DIMM的连接器、第一开关装置以及第二开关装置都位于该主板之上。

45.根据权利要求44所述的系统,其中

所述第一开关装置还包括一个工作于所述第一DIMM之上的第一数据使能信号,并且

所述第二开关装置还包括一个工作于所述第二DIMM之上的第二数据使能信号。

46.一种具有数据总线的计算机存储器系统,包括:

(a)含有数据线的第一DDR DIMM;

(b)含有数据线的第二DDR DIMM;

(c)含有多个周期的时钟信号,其中每个周期都含有一个起点并且具有一个周期p;

(d)第一开关装置,用于在所述第一DIMM内产生信号s1,该信号包括:间隔i1,始于各个周期的起始处,并且随后持续δt1时间;以及间隔i2,始于各个周期起始后的p/2处,并且随后持续δt1时间;

(e)第二开关装置,用于在所述第二DIMM内产生信号s2,该信号包括:间隔i3,始于各个周期开始后的p/4处,并且随后持续δt1时间;以及间隔i4,始于各个周期起始后的3p/4处,并且随后持续δt1时间;

(f)根据信号s1工作的第三开关装置,用于对间隔i1内的信号与间隔i2内的信号进行交换,并且将信号s1连接至所述第一DIMM的数据线;

(g)根据信号s2工作的第四开关装置,用于对间隔i3内的信号与间隔i4内的信号进行交换,并且将信号s1连接至所述第二DIMM的数据线;

(h)组合装置,用于连接所述第一DIMM的数据线与所述第二DIMM的数据线。

47.根据权利要求46所述的系统,其中所述第一开关装置除了各个周期的间隔i1和i2期间以外都产生一个高阻抗输出,并且所述第二开关装置除了各个周期的间隔i3和i4期间以外都产生一个高阻抗输出

48.根据权利要求47所述的系统,其中所述第一开关装置包括第一FET开关并且所述第二开关装置包括第二FET开关,各个FET开关都含有一个输入端和一个输出端,第一DIMM的数据线与第一FET开关的输入端相连,第二DIMM的数据线与第二FET开关的输入端相连,并且各FET开关的输出端都与数据总线相连接。

49.根据权利要求48所述的系统,其中还包括一个主板,并且所述第一DIMM、第二DIMM、第一、第二、第三和第四开关装置以及组合装置都位于该主板之上。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/572,641 US6446158B1 (en) | 1999-05-17 | 2000-05-17 | Memory system using FET switches to select memory banks |

| US09/572,641 | 2000-05-17 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN1436331A true CN1436331A (zh) | 2003-08-13 |

Family

ID=24288730

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN01809630A Pending CN1436331A (zh) | 2000-05-17 | 2001-05-15 | 多存储库dimm中实现的每个周期内的多重访问 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6446158B1 (zh) |

| EP (1) | EP1290561B1 (zh) |

| JP (1) | JP4769953B2 (zh) |

| CN (1) | CN1436331A (zh) |

| AU (1) | AU2001263124A1 (zh) |

| WO (1) | WO2001088714A1 (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110390963A (zh) * | 2018-04-16 | 2019-10-29 | 爱思开海力士有限公司 | 采样电路和使用采样电路的半导体存储器件 |

Families Citing this family (59)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6643752B1 (en) | 1999-12-09 | 2003-11-04 | Rambus Inc. | Transceiver with latency alignment circuitry |

| US7010642B2 (en) * | 2000-01-05 | 2006-03-07 | Rambus Inc. | System featuring a controller device and a memory module that includes an integrated circuit buffer device and a plurality of integrated circuit memory devices |

| US7363422B2 (en) * | 2000-01-05 | 2008-04-22 | Rambus Inc. | Configurable width buffered module |

| US7266634B2 (en) * | 2000-01-05 | 2007-09-04 | Rambus Inc. | Configurable width buffered module having flyby elements |

| US6502161B1 (en) | 2000-01-05 | 2002-12-31 | Rambus Inc. | Memory system including a point-to-point linked memory subsystem |

| US20050010737A1 (en) * | 2000-01-05 | 2005-01-13 | Fred Ware | Configurable width buffered module having splitter elements |

| US7356639B2 (en) * | 2000-01-05 | 2008-04-08 | Rambus Inc. | Configurable width buffered module having a bypass circuit |

| US7404032B2 (en) | 2000-01-05 | 2008-07-22 | Rambus Inc. | Configurable width buffered module having switch elements |

| KR100587052B1 (ko) * | 2000-06-30 | 2006-06-07 | 주식회사 하이닉스반도체 | 고속 인터페이스용 장치 |

| US6839820B1 (en) * | 2000-07-20 | 2005-01-04 | Silicon Graphics, Inc. | Method and system for controlling data access between at least two memory arrangements |

| TW526417B (en) * | 2000-08-03 | 2003-04-01 | Asustek Comp Inc | Control circuit for providing applications of unbuffered dual in-line memory modules (DIMM) on system supporting only registered DIMM chipset |

| US6737891B2 (en) | 2001-02-01 | 2004-05-18 | Chris Karabatsos | Tri-directional, high-speed bus switch |

| DE10106817C1 (de) * | 2001-02-14 | 2002-08-08 | Infineon Technologies Ag | Speicheranordnung |

| US6629225B2 (en) * | 2001-05-31 | 2003-09-30 | Intel Corporation | Method and apparatus for control calibration of multiple memory modules within a memory channel |

| US7656678B2 (en) | 2001-10-26 | 2010-02-02 | Entorian Technologies, Lp | Stacked module systems |

| US6914324B2 (en) * | 2001-10-26 | 2005-07-05 | Staktek Group L.P. | Memory expansion and chip scale stacking system and method |

| US20060255446A1 (en) | 2001-10-26 | 2006-11-16 | Staktek Group, L.P. | Stacked modules and method |

| US6956284B2 (en) * | 2001-10-26 | 2005-10-18 | Staktek Group L.P. | Integrated circuit stacking system and method |

| US20030234443A1 (en) * | 2001-10-26 | 2003-12-25 | Staktek Group, L.P. | Low profile stacking system and method |

| US7003684B2 (en) * | 2002-03-27 | 2006-02-21 | Via Technologies, Inc. | Memory control chip, control method and control circuit |

| TW559809B (en) * | 2002-03-27 | 2003-11-01 | Via Tech Inc | Memory control chip, control method and control circuit |

| US20050050375A1 (en) * | 2003-08-29 | 2005-03-03 | Mark Novak | Memory interface system and method |

| US8250295B2 (en) | 2004-01-05 | 2012-08-21 | Smart Modular Technologies, Inc. | Multi-rank memory module that emulates a memory module having a different number of ranks |

| WO2005083572A1 (ja) * | 2004-03-02 | 2005-09-09 | Sony Corporation | メモリ制御装置、メモリ制御方法、メモリ制御プログラムおよび画像撮像装置 |

| US7532537B2 (en) * | 2004-03-05 | 2009-05-12 | Netlist, Inc. | Memory module with a circuit providing load isolation and memory domain translation |

| US7289386B2 (en) * | 2004-03-05 | 2007-10-30 | Netlist, Inc. | Memory module decoder |

| US7916574B1 (en) | 2004-03-05 | 2011-03-29 | Netlist, Inc. | Circuit providing load isolation and memory domain translation for memory module |

| US7423885B2 (en) | 2004-09-03 | 2008-09-09 | Entorian Technologies, Lp | Die module system |

| US7443023B2 (en) | 2004-09-03 | 2008-10-28 | Entorian Technologies, Lp | High capacity thin module system |

| US7760513B2 (en) | 2004-09-03 | 2010-07-20 | Entorian Technologies Lp | Modified core for circuit module system and method |

| US7280428B2 (en) | 2004-09-30 | 2007-10-09 | Rambus Inc. | Multi-column addressing mode memory system including an integrated circuit memory device |

| US7571296B2 (en) * | 2004-11-11 | 2009-08-04 | Nvidia Corporation | Memory controller-adaptive 1T/2T timing control |

| US8595459B2 (en) | 2004-11-29 | 2013-11-26 | Rambus Inc. | Micro-threaded memory |

| US20060277355A1 (en) * | 2005-06-01 | 2006-12-07 | Mark Ellsberry | Capacity-expanding memory device |

| US7562271B2 (en) | 2005-09-26 | 2009-07-14 | Rambus Inc. | Memory system topologies including a buffer device and an integrated circuit memory device |

| US7464225B2 (en) | 2005-09-26 | 2008-12-09 | Rambus Inc. | Memory module including a plurality of integrated circuit memory devices and a plurality of buffer devices in a matrix topology |

| US11328764B2 (en) | 2005-09-26 | 2022-05-10 | Rambus Inc. | Memory system topologies including a memory die stack |

| US20070260841A1 (en) | 2006-05-02 | 2007-11-08 | Hampel Craig E | Memory module with reduced access granularity |

| US7417310B2 (en) | 2006-11-02 | 2008-08-26 | Entorian Technologies, Lp | Circuit module having force resistant construction |

| US7945740B2 (en) * | 2007-09-24 | 2011-05-17 | International Business Machines Corporation | Structure for a memory switching data processing system |

| US7937537B2 (en) * | 2007-09-24 | 2011-05-03 | International Business Machines Corporation | Memory switching data processing system |

| US8787060B2 (en) | 2010-11-03 | 2014-07-22 | Netlist, Inc. | Method and apparatus for optimizing driver load in a memory package |

| US8417870B2 (en) | 2009-07-16 | 2013-04-09 | Netlist, Inc. | System and method of increasing addressable memory space on a memory board |

| US8154901B1 (en) | 2008-04-14 | 2012-04-10 | Netlist, Inc. | Circuit providing load isolation and noise reduction |

| US8516185B2 (en) | 2009-07-16 | 2013-08-20 | Netlist, Inc. | System and method utilizing distributed byte-wise buffers on a memory module |

| US9128632B2 (en) | 2009-07-16 | 2015-09-08 | Netlist, Inc. | Memory module with distributed data buffers and method of operation |

| US8402208B2 (en) | 2009-10-06 | 2013-03-19 | Dell Products L.P. | Configurable memory controller/memory module communication system |

| KR101796116B1 (ko) | 2010-10-20 | 2017-11-10 | 삼성전자 주식회사 | 반도체 장치, 이를 포함하는 메모리 모듈, 메모리 시스템 및 그 동작방법 |

| US9477597B2 (en) * | 2011-03-25 | 2016-10-25 | Nvidia Corporation | Techniques for different memory depths on different partitions |

| US8701057B2 (en) | 2011-04-11 | 2014-04-15 | Nvidia Corporation | Design, layout, and manufacturing techniques for multivariant integrated circuits |

| US9529712B2 (en) | 2011-07-26 | 2016-12-27 | Nvidia Corporation | Techniques for balancing accesses to memory having different memory types |

| US9268719B2 (en) | 2011-08-05 | 2016-02-23 | Rambus Inc. | Memory signal buffers and modules supporting variable access granularity |

| JP2013061767A (ja) * | 2011-09-13 | 2013-04-04 | Elpida Memory Inc | メモリシステムおよびメモリモジュール |

| WO2015017356A1 (en) | 2013-07-27 | 2015-02-05 | Netlist, Inc. | Memory module with local synchronization |

| KR101707266B1 (ko) * | 2013-08-29 | 2017-02-15 | 엘에스산전 주식회사 | Plc에서의 os의 업데이트 장치 및 방법 |

| US10884958B2 (en) | 2018-06-25 | 2021-01-05 | Intel Corporation | DIMM for a high bandwidth memory channel |

| US10963404B2 (en) | 2018-06-25 | 2021-03-30 | Intel Corporation | High bandwidth DIMM |

| US10635357B2 (en) | 2018-07-03 | 2020-04-28 | Nvidia Corporation | Method for overlapping memory accesses |

| US11699471B2 (en) | 2019-09-25 | 2023-07-11 | Intel Corporation | Synchronous dynamic random access memory (SDRAM) dual in-line memory module (DIMM) having increased per data pin bandwidth |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03113547A (ja) * | 1989-09-28 | 1991-05-14 | Casio Comput Co Ltd | 記憶制御装置 |

| JPH03269662A (ja) * | 1990-03-20 | 1991-12-02 | Fujitsu Ltd | 高速メモリアクセス方式 |

| US5261068A (en) * | 1990-05-25 | 1993-11-09 | Dell Usa L.P. | Dual path memory retrieval system for an interleaved dynamic RAM memory unit |

| JPH06202933A (ja) * | 1992-12-28 | 1994-07-22 | Toshiba Corp | 同期式大規模集積回路記憶装置 |

| JPH07282000A (ja) * | 1994-04-04 | 1995-10-27 | Hitachi Ltd | バスインタフェース回路及びデータ転送システム |

| JP3824689B2 (ja) * | 1995-09-05 | 2006-09-20 | 株式会社ルネサステクノロジ | 同期型半導体記憶装置 |

| US5666322A (en) * | 1995-09-21 | 1997-09-09 | Nec Electronics, Inc. | Phase-locked loop timing controller in an integrated circuit memory |

| US5950223A (en) * | 1997-06-19 | 1999-09-07 | Silicon Magic Corporation | Dual-edge extended data out memory |

| US6233650B1 (en) * | 1998-04-01 | 2001-05-15 | Intel Corporation | Using FET switches for large memory arrays |

| JP4540137B2 (ja) * | 1998-07-24 | 2010-09-08 | ルネサスエレクトロニクス株式会社 | 同期型半導体記憶装置 |

| DE19849909A1 (de) * | 1998-10-29 | 2000-05-04 | Philips Corp Intellectual Pty | Schaltungsanordnung zum Verarbeiten binärer Signale |

-

2000

- 2000-05-17 US US09/572,641 patent/US6446158B1/en not_active Expired - Lifetime

-

2001

- 2001-05-15 JP JP2001585044A patent/JP4769953B2/ja not_active Expired - Fee Related

- 2001-05-15 CN CN01809630A patent/CN1436331A/zh active Pending

- 2001-05-15 AU AU2001263124A patent/AU2001263124A1/en not_active Abandoned

- 2001-05-15 WO PCT/US2001/015592 patent/WO2001088714A1/en active Application Filing

- 2001-05-15 EP EP01937381.0A patent/EP1290561B1/en not_active Expired - Lifetime

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110390963A (zh) * | 2018-04-16 | 2019-10-29 | 爱思开海力士有限公司 | 采样电路和使用采样电路的半导体存储器件 |

Also Published As

| Publication number | Publication date |

|---|---|

| US6446158B1 (en) | 2002-09-03 |

| EP1290561B1 (en) | 2019-10-23 |

| JP2004511026A (ja) | 2004-04-08 |

| WO2001088714A1 (en) | 2001-11-22 |

| JP4769953B2 (ja) | 2011-09-07 |

| EP1290561A4 (en) | 2006-10-11 |

| EP1290561A1 (en) | 2003-03-12 |

| AU2001263124A1 (en) | 2001-11-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1436331A (zh) | 多存储库dimm中实现的每个周期内的多重访问 | |

| US7788608B2 (en) | Microbump function assignment in a buck converter | |

| US20060129712A1 (en) | Buffer chip for a multi-rank dual inline memory module (DIMM) | |

| US7683725B2 (en) | System for generating a multiple phase clock | |

| CN1487669A (zh) | 内部修正占空比的延时锁定环电路及其占空比修正方法 | |

| US6707726B2 (en) | Register without restriction of number of mounted memory devices and memory module having the same | |

| US20110032932A2 (en) | Apparatus and method for producing device identifiers for serially interconnected devices of mixed type | |

| US7383416B2 (en) | Method for setting a second rank address from a first rank address in a memory module | |

| JP2008071468A (ja) | シフトレジスタ及び有機電界発光表示装置 | |

| CN1622462A (zh) | 半导体器件 | |

| JP2007265548A (ja) | 積層メモリ | |

| CA2667904C (en) | Apparatus and method for capturing serial input data | |

| CN1302481C (zh) | 半导体集成电路以及存储系统 | |

| EP3286760A1 (en) | Methods and apparatuses for command shifter reduction | |

| CN1750396A (zh) | 多相位时钟发生器电路 | |

| CN1744228A (zh) | 利用非周期性时钟的存储器模块和单元与集线器及其方法 | |

| JP5197080B2 (ja) | 半導体装置及びデータプロセッサ | |

| CN111834334A (zh) | 三维密排互连线之间的交叉电容和串扰的降低 | |

| CN1577611A (zh) | 延迟锁定回路及使用其闭锁时钟延迟的方法 | |

| CN1225085C (zh) | 从时钟信号生成脉冲信号的电路 | |

| US20020130699A1 (en) | Pump circuits using flyback effect from integrated inductance | |

| CN1538283A (zh) | 同步存储系统及同步存储系统中沟通之方法及协议 | |

| CN1113464C (zh) | 闩锁电路 | |

| CN1104671C (zh) | 内部时钟脉冲发生装置 | |

| CN1860686A (zh) | 延迟控制回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |