CN1225085C - 从时钟信号生成脉冲信号的电路 - Google Patents

从时钟信号生成脉冲信号的电路 Download PDFInfo

- Publication number

- CN1225085C CN1225085C CNB011436093A CN01143609A CN1225085C CN 1225085 C CN1225085 C CN 1225085C CN B011436093 A CNB011436093 A CN B011436093A CN 01143609 A CN01143609 A CN 01143609A CN 1225085 C CN1225085 C CN 1225085C

- Authority

- CN

- China

- Prior art keywords

- delay

- signal

- pulse signal

- clock signal

- mentioned

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015572 biosynthetic process Effects 0.000 title description 2

- 230000000630 rising effect Effects 0.000 claims abstract description 16

- 230000003111 delayed effect Effects 0.000 claims abstract 8

- 238000003708 edge detection Methods 0.000 claims description 10

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 claims description 4

- 238000010586 diagram Methods 0.000 description 21

- 230000001419 dependent effect Effects 0.000 description 3

- 230000001934 delay Effects 0.000 description 2

- 230000008676 import Effects 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- 101100113692 Caenorhabditis elegans clk-2 gene Proteins 0.000 description 1

- 230000033228 biological regulation Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 230000000541 pulsatile effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/131—Digitally controlled

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/135—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals by the use of time reference signals, e.g. clock signals

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Pulse Circuits (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Manipulation Of Pulses (AREA)

Abstract

提供即使考虑延迟元件中的延迟时间的变动,也不过分地降低时钟信号的周期,能够满足关于脉冲信号的特定期间的要求值的技术。生成具有从时钟信号的上升沿延迟了第1延迟时间Td1的边缘的第1延迟信号Q30、Q34。另外,生成具有从时钟信号的下降沿延迟了第2延迟时间Td2的边缘的第2延迟信号Q32、Q36。而且,通过进行这些第1延迟信号Q30、Q34与第2延迟信号Q32、Q36的逻辑运算,生成脉冲信号Sout。

Description

技术领域

本发明涉及从一定周期的时钟信号生成特定的脉冲信号的技术。

背景技术

图13是示出用于从时钟信号CLK生成特定的脉冲信号Q230的传统的脉冲信号生成电路200一例的框图。该电路200具备D触发器210(以下称为「DFF210」),串联连接的2个延迟元件220、222,2个输入端子的一方成为反相输入端子的NAND门230。时钟信号CLK提供到DFF210的时钟输入端子。DFF210的输出Q210输入到第1延元件件220,反相输出#Q210反馈到D输入端子。在第1延迟元件220中延迟了的延迟信号Q220输入到NAND门230的同相输入端子。另外,该延迟信号Q220在由第2延迟元件222进一步延迟了以后输入到NAND门230的反相输入端子。

图14(a)到(e)是示出该脉冲信号生成电路220的动作的流程图。从第1延迟元件220输出的第1延迟信号Q220(图14(c))具有从时钟信号CLK的上升沿延迟了第1延迟时间Td1的边缘。另外,从第2延迟元件222输出的第2延迟信号Q222(图14(d))具有从第1延迟信号Q220的上升沿进一步延迟了第2延迟时间Td2的边缘。从而,第2延迟信号Q222的边缘从时钟信号CLK的上升沿延迟了延迟时间(Td1+Td2)。NAND门230从这2个延迟信号Q220、Q222,生成图14(e)所示的脉冲信号Q230(图14(e))。

该脉冲信号230例如作为RAM的写入控制信号使用。即,脉冲信号230设计为在时钟信号CLK的1个周期Tc内,仅在特定的期间Tw成为L电平的信号。在即将开始该周期Tw之前设定建立时间Ts,另外,在紧接期间Tw之后设定保持时间Th。这些时间Ts、Tw、Th分别设定成设计上的要求值。2个延迟时间Td1、Td2设定为使得这些期间Ts、Tw、Th满足各自的要求值。

但是,在该电路的设计中,一般考虑到延迟元件220、222的制造误差或者温度依赖性等延迟时间的分散性,认为在延迟时间Td1、Td2中存在着相当大的误差。因此,在图13所示以往的电路设计中,难以设定延迟时间Td1、Td2,使得这些期间Ts、Tw、Th满足各自的要求值。这里,假设在3个期间Ts、Tw、Th中设定以下要求值的情况:

条件C1:Ts≥1ns;

条件C2:Tw≥10ns;

条件C3:Th≥3ns。

而由于温度特性等引起的延迟时间Td1、Td2的变动通常取从标准值(典型值)的大约0.6倍到大约1.6倍之间的值。从而,延迟时间Td1、Td2的最大值可以成为最小值的大约2.7倍(=1.6/0.6)左右。如果考虑到这样的误差,则上述条件C1,C3可以改写如下:

条件C1a:Ts=Td1=1ns(min)~2.7ns(max);

条件C2a:Tw=Td2=10ns(min)~27ns(max);

条件C3a:Th≥3ns。

这里,(min)意味着延迟时间Td1、Td2成为最小值的条件,(max)意味着延迟时间Td1、Td2成为最大值的条件。从而,在延迟时间Td1、Td2每一个都成为最大值的条件中,时钟周期Tc成为大约33ns(=2.7+27+3),这相当于大约30MHz。另一方面,从上述条件C1a~C3a所决定的时钟周期Tc的最小值(RAM的循环周期)是14(=1+10+3)ns,这大约相当于71MHz。即,即使使用能够以大约71MHz进行动作的RAM,在图13的电路中生成写入控制信号时,也仅能够使该RAM以大约30MHz(大约42%的速度)进行动作。

这样,在以往的脉冲信号生成电路中,为了满足有关脉冲信号的特定期间的要求值,考虑延迟元件中的延迟时间的变动,存在着必须大大降低时钟信号的周期的问题。

发明内容

本发明是为解决上述以往的课题而产生的,目的在于提供即使考虑到延迟元件中的延迟时间的变动,也能够不过分地降低时钟信号的周期,满足有关脉冲信号的特定期间的要求值的技术。

为了达到上述的目的,本发明提供了用于从具有一定周期的时钟信号生成特定的脉冲信号的电路,其特征在于具备:用于检测上述时钟信号的上升沿和下降沿的边缘检测单元;第1延迟信号生成单元,具有至少1个包含有第1延迟量的第1延迟元件,用于生成至少1个包含有从上述时钟信号的上升沿以上述的第1延迟量延迟了的第1延迟边缘的第1延迟信号;第2延迟信号生成单元,具有至少1个包含有第2延迟量的第2延迟元件,用于生成至少1个包含有从上述时钟信号的下降沿以上述的第2延迟量延迟了的第2延迟边缘的第2延迟信号;可通过进行上述至少1个第1延迟信号与上述至少1个第2延迟信号的逻辑运算来生成上述脉冲信号的逻辑运算单元。

在该脉冲信号生成电路中,从时钟信号的上升沿生成第1延迟信号,从时钟信号的下降沿生成第2延迟信号,通过进行这些延迟信号的逻辑运算生成脉冲信号,因此与以往那样仅从时钟信号的上升沿生成脉冲信号的情况相比较,能够减小延迟量的变动的影响。其结果,即使考虑到延迟元件中的延迟量的变动,也能够不过分地降低时钟信号的周期以满足有关脉冲信号的特定期间的要求值。

另外,上述脉冲信号的1个周期最好设定为与上述时钟信号的1个周期相同。在该结构中,能够把由于延迟量的变动对脉冲信号的影响抑制为很小。

另外,上述第1与第2延迟量最好分别设定为小于上述时钟信号的1个周期的1/2的值。在该结构中,由于延迟量本身小,因此还能够把由于温度特性等引起的延迟量的变动抑制得很小。

进而,上述第1和第2延迟量最好相互相等。在该结构中,即使延迟量变动,由第1延迟量所决定的脉冲信号的边缘与由第2延迟量所决定的脉冲信号的边缘之间的期间能够始终保持为几乎一定。

另外,上述边缘检测单元还可以包括:第1D触发器,它有第1时钟输入端子、第1D输入端子、第1输出端子和第1反相输出端子,在上述时钟信号输入到第1时钟输入端子的同时,来自上述第1反相输出端子的反相输出反馈到上述第1D输入端子;第2触发器,它具有第2时钟输入端子、第2D输入端子、第2输出端子和第2反相输出端子,在上述时钟信号反相后的反相时钟信号输入到上述第2时钟输入端子的同时,来自上述第1D触发器的上述第1输出端子的输出被输入到上述第2D输入端子。这时,在来自上述第1D触发器的上述第1输出端子的输出被输入到上述第1延迟元件的同时,来自上述第2D触发器的上述第2输出端子的输出被输入到上述第2延迟元件。

在该结构中,能够很好地检测时钟信号的上升沿和下降沿。

另外,本发明还能够以种种形态实现,例如,以脉冲信号生成电路或者脉冲信号生成方法等形态实现。

附图说明

图1是示出第1实施例的脉冲信号生成电路100结构的框图。

图2是示出第1实施例的脉冲信号生成电路100的动作的流程图。

图3是相比较地示出在第1延迟时间Td1比第2延迟时间Td2小时,延迟时间取最小值与取最大值的情况的说明图。

图4是相比较地示出在第1与第2延迟时间Td1、Td2相等时,延迟时间取最小值与取最大值的情况的说明图。

图5是相比较地示出在第1延迟时间Td1比第2延迟时间Td2大时,延迟时间取最小值与取最大值的情况的说明图。

图6是示出为了进行外部总线的数据传送使用脉冲信号Q40的例子的说明图。

图7是示出第2实施例的脉冲信号生成电路110的结构框图。

图8是示出第2实施例的脉冲信号生成电路110的动作的流程图。

图9是示出第3实施例的脉冲信号生成电路120的结构的框图。

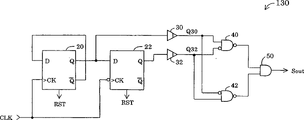

图10是示出第4实施例的脉冲信号生成电路130的结构的框图。

图11是示出第5实施例的脉冲信号生成电路140的结构的框图。

图12是示出第6实施例的脉冲信号生成电路150的结构的框图。

图13是示出以往的脉冲信号生成电路200一例的框图。

图14是示出以往的脉冲信号生成电路200的动作的流程图。

具体实施方式

以下,按照以下的顺序根据实施例说明本发明的实施方式:

A.第1实施例;

B.第2实施例;

C.第3实施例;

D.第4实施例;

E.第5实施例;

F.第6实施例;

G.变形例

A.第1实施例:

图1是示出作为本发明第1实施例的脉冲信号生成电路100的结构的框图。该脉冲信号生成电路100具备2个D触发器20、22,2个延迟元件30、32,2个输入端子的一方成为同相输入端子的NAND门40。另外,以下,把「 D触发器」称为「DFF」。

时钟信号CLK输入到第1DFF20的时钟输入端子的同时,反相后输入到第2DFF22的时钟端子。第1DFF20的反相输出#Q20反馈到第1DFF20的D输入端子。第1DFF20的输出Q20输入到第2DFF22的D输入端子的同时,还输入到第1延迟元件30。第2DFF20的输出Q22输入到第2延迟元件32。由第1延迟元件30延迟了的第1延迟信号Q30输入到NAND门40的同相输入端子。另外,由第2延迟元件32延迟了的第2延迟信号Q32输入到NAND门40的反相输入端子。另外,2个DFF20、22由于在初始状态被复位,因此在初始状态它们的输出Q20、Q22取为L电平。

图2是示出第1实施例的脉冲信号生成电路100的动作的流程图。第1DFF20的输出Q20(图2(b))是在每个时钟信号CLK的上升沿把电平反相的信号。另一方面,第2DFF22的输出Q22(图2(c))是在每个时钟信号CLK的下降沿把电平反相的信号。

第1DFF20的输出Q20由第1延迟元件30延迟第1延迟时间Td1成为第1延迟信号Q30(图2(d))。另一方面,第2DFF22的输出Q22由第2延迟元件32延迟第2延迟时间Td2成为第2延迟信号Q32(图2(e))。即,第1延迟信号Q30是具有从时钟信号CLK的上述沿开始延迟了第1延迟时间Td1的边缘的信号。另外,第2延迟信号Q32是具有从时钟信号CLK的下降沿开始延迟了第2延迟时间Td2的边缘的信号。NAND门40通过把这些延迟信号Q30、Q32进行逻辑运算,生成脉冲信号Q40(图2(f))。

脉冲信号Q40的下降沿从时钟信号CLK的上升沿延迟第1延迟时间Td1。另外,脉冲信号Q40的上升沿从时钟信号CLK的下降沿延迟第2延迟时间Td2。这样,在第1实施例的脉冲信号生成电路100中,脉冲信号Q40的下降沿和上升沿通过相同时钟信号CLK的不同种类的边缘的延迟分别生成,因此具有可以减少由于延迟时间的误差引起的对脉冲信号的影响的优点。其结果,如在以下所说明的那样,与以往相比较能够将时钟信号CLK的周期Tc设计得短一些。

这里,与上述的在以往技术中说明过的例子相同,在来自NAND门40的输出信号Q40(图2(f))的3个期间Ts、Tw、Th中,假设分别设定以下那样的条件C1~C3:

条件C1:Ts≥1ns;

条件C2:Tw≥10ns;

条件C3:Th≥3ns。

如从图2(f)能够理解的那样,这些期间Ts、Tw、Th与时钟信号CLK的周期Tc以及延迟时间Td1、Td2具有以下的(1)~(3)式的关系:

Ts=Td1…(1)

Tw=Td2+Tc/2-Td1…(2)

Th=Tc/2-Td2…(3)。

这时,上述条件C1~C3能够改写为以下的条件C4~C6:

条件C4:Ts=Td1≥1ns;

条件C5:Tw=Td2+Tc/2-Td1≥10ns;

条件C6:Th=Tc/2-Td2≥3ns。

这里,第1延迟时间Td1的最大值Td1max假定是其最小值Td1min的2.7倍,第2延迟时间Td2的最大值Td2max也假定是其最小值Td2min的2.7倍。另外,假定2个延迟时间Td1、Td2中的一方取最小值时另一方也取最小值,一方取最大值时另一方也取最大值。后者的假定是考虑到在延迟时间的最大值或者最小值中,包含着延迟元件30、32温度依赖性的影响的关系。即,如果不考虑一方的延迟元件在温度依赖性的影响下取最大值时,另一方的延迟元件在温度依赖性的影响下取最小值这样的状况,则双方同时取最小值或者同时取最大值的考虑是妥当的。

但是,上述条件C4在第1延迟时间Td1取其最小值Td1min时最严格。另外,上述条件C6在第2延迟时间Td2取其最大值Td2max(=2.7×Td2min)时最严格。从而,条件C4~C6能够改写为以下的条件C4a~C6a:

条件C4a:Ts=Td1min≥1ns;

条件C5a:Tw=Td2+Tc/2-Td1≥10ns;

条件C6a:Th=Tc/2-2.7×Td2min≥3ns。

这里,假设在延迟时间Td1、Td2分别取其最小值Td1min、Td2min时,期间Tw成为10ns。这时,以下的(4)~(6)式成立:

Td1min≥1ns…(4)

Td2min+Tc/2-Td1min=10ns…(5)

Tc/2-2.7×Td2min≥3ns…(6)。

如果把(5)式代入到(4)式中,则可以得到以下的(7)式:

Td2min+Tc/2≥11ns…(7)。

如果把(6)式和(7)式对于Tc求解,则可以得到下述的(8)式:

Tc≥17.7ns…(8)。

这里,如果考虑Td1=1ns,Tc=17.7ns,则从(5)式,Td2min成为2.15ns。在Tc=17.7ns,Td1=Td1min=1ns,Td2=Td2min=2.15ns时,能够容易地确认上述条件C4~C6成立。

另一方面,由于延迟时间Td1、Td2的最大值Td1max、Td2max分别是其最小值Td1min、Td2min的2.7倍,因此分别成为2.7ns和5.8ns。在该最大值条件时,即,Tc=17.7ns,Td1=Td1max=2.7ns,Td2=Td2max=5.8ns时,也能够确认上述条件C4~C6成立。从而,即使考虑延迟时间Td1、Td2的变动、如果把时钟周期Tc设定为17.7ns(56.5MHz),则能够满足脉冲信号Q40的各期间Ts、Tw、Th的要求值。

而从上述条件C1~C3所决定的时钟周期Tc的最小值是14(=1+10+3)ns,这相当于大约71MHz。与此不同,在本实施例中,即使考虑延迟时间的变动,也能够把时钟周期设定为17.7ns(56.5MHz)。例如,在把该脉冲信号Q40使用为RAM的写入控制信号时,能够以RAM的最大可能工作频率(71MHz)的大约80%频率进行工作。另一方面,如在以往技术中所说明过的那样,在图13所示的以往电路中,仅能够以RAM的最大可能工作频率的大约42%的频率(30MHz)进行工作。即,在第1实施例的电路中,与图13所示的以往的电路相比较,能够生成大约1.9倍频率的脉冲信号。

如从以上的说明能够理解的那样,在第1实施例的电路中,即使考虑到延迟元件30、32的延迟时间Td1、Td2的变动,也能够不过分地降低时钟周期Tc,满足有关脉冲信号Q40的各期间的要求值。

其中,延迟时间Td1、Td最好设定为小于时钟周期Tc的1/2的值。其理由如下:例如,在延迟时间Td1是时钟周期Tc的1/2以上时,脉冲信号Q40的下降沿在时钟信号CLK的下降沿以后发生。从而,这时,能够从时钟信号CLK的下降沿生成脉冲信号Q40的下降沿。换言之,在延迟时间Td1是时钟周期Tc的1/2以上时,计算出从延迟时间Td1减去时钟信号CLK的半个周期Tc/2的时间(Td1-Tc/2),能够在从时钟信号CLK的下降沿延迟了该时间(Td1-Tc/2)的时刻,发生脉冲信号Q40的下降沿。而在本方法中,与延迟时间Td1是时钟周期Tc的1/2以上的情况相比较具有减少由于延迟时间的变动产生的影响的优点。从而,在图1的电路中,延迟时间Td1、Td2最好设定为小于时钟周期Tc的1/2的值。

然而,脉冲信号Q40的L电平期间Tw根据延迟时间Td1、Td2的变动而变化,其变化的方式因2个延迟时间Td1、Td2的大小关系而不同。图3是比较地示出第1延迟时间Td1比第2延迟时间Td2小时,延迟时间Td1、Td2分别取最小值时(图3(b))和取最大值时(图3(c))的说明图。能够理解在第1延迟时间Td1比第2延迟时间Td2小时,与延迟时间取最小值时的情况相比较取,最大值时的期间Tw长。

图4是比较地示出第1与第2延迟时间Td1、Td2相等时,延迟时间Td1、Td2分别取最小值时与分别取最大值时的说明图。在2个延迟时间Td1、Td2相等时,即使延迟时间变动,期间Tw的长度也大致保持一定。

图5是比较地示出第1延迟时间Td1比第2延迟时间Td2大时,延迟时间Td1、Td2分别取最小值时与分别取最大值时的说明图。在第1延迟时间Td1比第2延迟时间Td2大时,与延迟时间取最小值的情况相比较,取最大值时的期间Tw短。

这样,延迟时间Td1、Td2的变动对于期间Tw(即,由使时钟信号CLK的上升沿延迟得到的延迟边缘与使下降沿延迟得到的延迟边缘相夹的期间)的长度的影响依赖于延迟时间Td1、Td2的大小关系。从而,最好根据期间Tw的要求值的条件,适当地设定延迟时间Td1、Td2的大小关系。例如,为了始终保证期间Tw的长度大致一定,最好把延迟时间Td1、Td2设定为相等。

脉冲信号Q40不仅能够利用为RAM的写入控制,还能够在其它用途中利用。图6是示出把脉冲信号Q40作为用于数据总线上的数据传送的选通脉冲使用的一例的说明图。图6(b)示出延迟时间Td1、Td2取最小值条件下的脉冲信号Q40,图6(d)示出在该条件下的数据总线上的数据信号的时序。另外,图6(c)示出延迟时间Td1、Td2取最大值条件下的脉冲信号Q40,图6(e)示出在该条件下的数据总线上的数据信号的时序。

如从该例能够理解的那样,当延迟时间Td1、Td2由于温度依赖性等原因而发生变动,而且与此相对应脉冲信号Q40的时序变化时,数据总线上的数据信号的时序也以与此相同的倾向发生变化。即,从数据信号的变化点到脉冲信号Q40的下降沿的期间Tp或者从脉冲信号Q40的上升沿到数据信号的变化点的期间Tq即使受到由于温度产生的影响也保持一定以上的长度。从而,即使数据信号的时序在温度依赖性等的影响下发生变化,如果把脉冲信号Q40用作为选通脉冲,也能够可靠地进行数据传送。另外,如上述那样,如果依据第1实施例的电路100,则由于能够把脉冲信号Q40的频率设定为比以往大的值,因此能够高速地进行数据传送。

B:第2实施例:

图7是示出本发明第2实施例的脉冲信号生成电路110的结构的框图。该脉冲信号生成电路110具有前级电路112和后级电路114以及AND门50。前级电路112具有与图1所示的第1实施例的脉冲信号生成电路100相同的结构。后级电路114具有2个DFF24、26,2个延迟元件34、36,2个输入端子的一方成为反相输入端子的NAND门42。后级电路114内的各元件之间的连接状态基本上与前级电路112内的各元件之间的连接状态相同。另外,后级电路114内的延迟元件34、36具有分别与前级电路112内的延迟元件30、32相同的延迟时间Td1、Td2。但是,在后级电路114内的第1DFF24的D输入端子上输入来自前级电路112内的第2DFF22的输出Q22。另外,与前级电路112的第1DFF20不同,后级电路114的第1DFF24的反相输出没有反馈到DFF24的D输入端子。另外,由于后级电路114内的2个DFF24、26在初始状态被置位,因此在初始状态它们的输出Q24、Q26取H电平。AND门50通过取前级电路112与后级电路114的输出Q40、Q42(即2个NAND门40、42的输出)的逻辑积,生成最终的脉冲信号Sout。

图8是示出第2实施例的脉冲信号生成电路110的动作流程图。图8(a)、(b)、(c)、(d)所示的信号CLK、Q30、Q32、Q40是前级电路112的信号,是分别与在第1实施例中图2(a)、(d)、(e)、(f)所示的对应信号相同的信号。另外,图8(e)、(f)、(g)所示的信号Q34、Q36、Q42是后级电路114的信号,成为从前级电路112中的信号Q30、Q32、Q40分别向后移动了时钟周期Tc的信号。例如,来自前级电路112的输出Q40相当于第奇数个周期Tc中的脉冲信号,来自后级电路114的输出Q42相当于第偶数个周期Tc中的脉冲信号。通过对这些输出Q40、Q42进行逻辑运算,使得在这些输出Q40、Q42的任一个是L电平期间成为L电平那样来生成从AND门50输出的脉冲信号Sout。其结果,该脉冲信号Sout成为在每个时钟周期Tc的成为L电平的期间Tw各出现一次的信号。

如从以上的说明能够理解的那样,第2实施例的脉冲信号生成电路110能够生成在时钟信号CLK的每个期间Tc中,成为L电平的期间Tw各出现一次的脉冲信号Sout。另外,如果把该脉冲信号Sout反相,则能够容易地生成在时钟信号CLK的每个周期Tc中成为H电平的期间Tw各出现一次脉冲信号。从而,在第2实施例的脉冲信号生成电路110中,能够生成在时钟信号CLK的每个周期Tc中,取规定的逻辑电平的期间Tw各出现一次那样的脉冲信号Sout。

上述第1实施例中的RAM工作频率的计算能够正确地适用于图7所示的第2实施例的脉冲生成电路110。但是,第1实施例的脉冲生成电路100在能够生成图13所示的电路的约1.9倍频率的脉冲信号这一点上不变。第2实施例的脉冲生成电路110可以生成具有进而是第1实施例的脉冲信号生成电路100的2倍频率的脉冲信号。

C:第3实施例:

图9是示出本发明第3实施例的脉冲信号生成电路120的结构的框图。该脉冲信号生成电路120具有从图7所示的第2实施例的电路省略了2个DFF24、26的结构。另外,在该电路120中,第2组延迟元件34、36的输入与第2实施例的电路不同。即,在具有第1延迟时间Td1的延迟元件34中,输入第1DFF20的反相输出,在具有第2延迟时间Td2的延迟元件36中输入第2DFF22的反相输出。

该第3实施例的脉冲信号生成电路120也能够生成与第2实施例的脉冲信号生成电路110大致相同的脉冲信号Sout。另外,第3实施例还具有比第2实施例的电路结构简单的优点。

D:第4实施例

图10是示出本发明第4实施例的脉冲信号生成电路130的结构的框图。该脉冲信号生成电路130具有从图9所示的第3实施例的电路省略了2个延迟元件34、36的结构。另外,在该脉冲信号生成电路130中,第1延迟元件30的输出Q30输入到第1NAND门40的同相输入端子与第2NAND门42的反相输入端子。另外,第2延迟元件32的输出Q32输入到第1NAND门40的反相输入端子和第2NAND门42的同相输入端子。

该第4实施例的脉冲信号生成电路130也能够生成与第2实施例或者第3实施例的脉冲信号生成电路几乎相同的脉冲信号Sout。另外,第4实施例还具有比第3实施例的电路结构更简单的优点。

E:第5实施例

图11是示出本发明第5实施例的脉冲信号生成电路140的结构的框图。该脉冲信号生成电路140具有把图10所示的第4实施例的电路的2个NAND门40、48和AND门50替换为1个EXNOR门60的结构。该第5实施例的脉冲信号生成电路140也能够生成与第2至第4实施例的脉冲信号生成电路大致相同的脉冲信号Sout。

F:第6实施例

图12是示出本发明的6实施例的脉冲信号生成电路150的结构的框图。该脉冲信号生成电路150具有在图1所示的第5实施例的电路的第1DFF20的D输入端子的前级,添加了允许控制电路70的结构。允许控制电路70具有2个AND门72、74和OR门76。第1AND门72的2个输入端子中的一方是反相输入端子。

从外部提供的允许信号EN同时输入到第1AND门72的反相输入端子和第2AND门74的1个输入端子。在第1AND门72的另一个输入端子上输入第1DFF20的输出Q20。另外,在第2AND门74的另一个输入端子上,输入第1DFF的反相输出#Q20。2个AND门72、74的输出都输入到OR门76。OR门76的输出供给到第1DFF的D输入端子。

在该第6实施例的脉冲信号输出电路150中,根据允许信号EN的电平控制是否进行动作。即,在允许信号EN是L电平时脉冲信号生成电路150不动作,脉冲信号Sout保持L电平。另一方面,在允许信号EN是H电平时,脉冲信号生成电路150生成上述的图8(h)所示的脉冲信号Sout。

如从该例子能够理解的那样,作为本发明的脉冲信号生成电路能够采用各种电路结构,另外,为了实现生成脉冲信号功能以外的其它功能,还能够设置附加的电路。

G.变形例:

另外,本发明不限定于上述的实施例或实施形态,在不脱离其宗旨范围内,能够在各种形态下实施,例如能够采用以下的变形。

G1:变形例1:

在上述实施例中,作为检测时钟信号的边缘的边缘检测电路使用了多个D触发器,而也能够使用D触发器以外的电路元件构成边缘检测电路。

G2:变形例2:

在上述实施例中,生成在时钟信号CLK的1个周期中仅在一定期间Tw成为L电平那样的脉冲信号,而本发明也能够适用在用于生成除此以外的各种脉冲信号的电路中。

G3:变形例3:

在第2实施例(图7)或者第3实施例(图8)的电路中,生成具有从时钟信号CLK的上升沿延迟了第1延迟量Td1的边缘的2个第1延迟信号Q30、Q34,另外,生成具有从时钟信号CLK的下降沿延迟了第2延迟量Td2的边缘的2个第2延迟信号Q32、Q34。另一方面,在第1实施例(图1)或者第4实施例(图10),第5实施例(图11),第6实施例(图12)的电路中,仅生成各1个第1延迟信号Q30和第2延迟信号Q32。如能够由此理解的那样,在本发明中,生成至少1个具有从时钟信号的上升沿以第1延迟量延迟了的边缘的第1延迟信号的同时,生成至少1个具有从时钟信号的下降沿以第2延迟量延迟了的边缘的第2延迟信号。而且,通过进行这些至少1个第1延迟信号与至少1个第2延迟信号的逻辑运算生成脉冲信号。

Claims (5)

1.一种脉冲信号生成电路,该电路用于从具有一定周期的时钟信号生成特定的脉冲信号,其特征在于具备:

用于检测上述时钟信号的上升沿和下降沿的边缘检测单元;

第1延迟信号生成单元,具有至少1个包含有第1延迟量的第1延迟元件,用于生成至少1个包含有从上述时钟信号的上升沿以上述的第1延迟量延迟了的第1延迟边缘的第1延迟信号;

第2延迟信号生成单元,具有至少1个包含有第2延迟量的第2延迟元件,用于生成至少1个包含有从上述时钟信号的上升沿以上述的第2延迟量延迟了的第2延迟边缘的第2延迟信号,

可通过进行上述至少1个第1延迟信号与上述至少1个第2延迟信号的逻辑运算来生成上述脉冲信号的逻辑运算单元,

上述边缘检测单元,包括:

用于检测上述时钟信号的上升沿的第1边缘检测元件;以及

用于检测上述时钟信号的下降沿的第2边缘检测元件,

上述第1边缘检测元件的输出被输入到上述第1延迟元件的同时,上述第2边缘检测元件的输出被输入到上述第2延迟元件。

2.如权利要求1中所述的脉冲信号生成电路,其特征在于:

上述脉冲信号的1个周期设定为与上述时钟信号的1个周期相同。

3.如权利要求1中所述脉冲信号生成电路,其特征在于;

上述第1和第2延迟量分别设定为小于上述时钟信号的1个周期的二分之一的值。

4.如权利要求1中所述的脉冲信号生成电路,其特征在于:

上述第1与第2延迟量相互相等。

5.如权利要求1至4的任一项中所述的脉冲信号生成电路,其特征在于:

上述第1边缘检测元件是第1D触发器,该第1D触发器具有第1时钟输入端子、第1D输入端子、第1输出端子和第1反相输出端子,在上述时钟信号输入到第1时钟输入端子的同时,来自上述第1反相输出端子的反相输出被反馈到上述第1D输入端子,

上述第1边缘检测元件是第2D触发器,该第2D触发器具有第2时钟输入端子、第2D输入端子、第2输出端子和第2反相输出端子,在上述时钟信号反相后的反相时钟信号输入到上述第2时钟输入端子的同时,来自上述第1D触发器的上述第1输出端子的输出被输入到上述第2D输入端子,

在来自上述第1D触发器的上述第1输出端子的输出被输入到上述第1延迟元件的同时,来自上述第2D触发器的上述第2输出端子的输出被输入到上述第2延迟元件。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000352307A JP3815209B2 (ja) | 2000-11-20 | 2000-11-20 | クロック信号からのパルス信号の生成 |

| JP352307/00 | 2000-11-20 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1360397A CN1360397A (zh) | 2002-07-24 |

| CN1225085C true CN1225085C (zh) | 2005-10-26 |

Family

ID=18825228

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB011436093A Expired - Fee Related CN1225085C (zh) | 2000-11-20 | 2001-11-20 | 从时钟信号生成脉冲信号的电路 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6895523B2 (zh) |

| JP (1) | JP3815209B2 (zh) |

| KR (1) | KR100430609B1 (zh) |

| CN (1) | CN1225085C (zh) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6622160B1 (en) | 1999-07-30 | 2003-09-16 | Microsoft Corporation | Methods for routing items for communications based on a measure of criticality |

| JP4480341B2 (ja) * | 2003-04-10 | 2010-06-16 | 日立プラズマディスプレイ株式会社 | プラズマディスプレイ装置 |

| JP2007306580A (ja) * | 2003-07-14 | 2007-11-22 | Nec Corp | 周波数シンセサイザ |

| JP4149430B2 (ja) * | 2003-12-04 | 2008-09-10 | シャープ株式会社 | パルス出力回路、それを用いた表示装置の駆動回路、表示装置、およびパルス出力方法 |

| US7030676B2 (en) * | 2003-12-31 | 2006-04-18 | Intel Corporation | Timing circuit for separate positive and negative edge placement in a switching DC-DC converter |

| US7421610B2 (en) * | 2005-07-21 | 2008-09-02 | Freescale Semiconductor, Inc. | Clock generation circuit |

| US7366966B2 (en) * | 2005-10-11 | 2008-04-29 | Micron Technology, Inc. | System and method for varying test signal durations and assert times for testing memory devices |

| KR100723537B1 (ko) | 2006-09-12 | 2007-05-30 | 삼성전자주식회사 | 클럭 신호 발생 방법 및 장치와 이를 이용한 클럭 주파수제어 방법 및 장치 |

| CN101577792B (zh) * | 2008-05-06 | 2011-01-19 | 通嘉科技股份有限公司 | 操作模式的判断装置及其判断方法 |

| KR200451836Y1 (ko) * | 2008-10-22 | 2011-01-13 | 이재호 | 야간 식별이 용이한 보안등용 자동 점멸기 |

| CN102571041B (zh) * | 2010-12-22 | 2015-02-04 | 上海华虹宏力半导体制造有限公司 | 检测电路延时和时序的方法及采用该方法校准延时的方法 |

| JP2013165570A (ja) * | 2012-02-10 | 2013-08-22 | Toshiba Corp | 半導体集積回路装置、dc−dcコンバータおよび電圧変換方法 |

| CN106374898B (zh) * | 2016-10-18 | 2019-08-20 | 天津大学 | 多通道输出选通开关时序产生结构 |

| CN111464153A (zh) * | 2020-05-14 | 2020-07-28 | 京东方科技集团股份有限公司 | 脉冲信号生成电路、方法、时钟生成模组和显示装置 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5357196A (en) * | 1991-08-06 | 1994-10-18 | Jeco Company Limited | Circuit for converting a frequency of an input signal so a signal having a digital value corresponding to the frequency |

| JP3338776B2 (ja) * | 1998-03-12 | 2002-10-28 | 日本電気株式会社 | 半導体装置 |

| WO2000042609A1 (fr) * | 1999-01-18 | 2000-07-20 | Fujitsu Limited | Procede et dispositif de commande de signal reproduit |

| JP3358590B2 (ja) * | 1999-06-18 | 2002-12-24 | 日本電気株式会社 | 半導体集積回路 |

| US6526468B1 (en) * | 1999-12-15 | 2003-02-25 | Robotel Electronique Inc. | Peripheral bus extender |

| US6759911B2 (en) * | 2001-11-19 | 2004-07-06 | Mcron Technology, Inc. | Delay-locked loop circuit and method using a ring oscillator and counter-based delay |

| US6727740B2 (en) * | 2002-08-29 | 2004-04-27 | Micron Technology, Inc. | Synchronous mirror delay (SMD) circuit and method including a ring oscillator for timing coarse and fine delay intervals |

-

2000

- 2000-11-20 JP JP2000352307A patent/JP3815209B2/ja not_active Expired - Fee Related

-

2001

- 2001-11-06 US US10/005,471 patent/US6895523B2/en not_active Expired - Lifetime

- 2001-11-19 KR KR10-2001-0071693A patent/KR100430609B1/ko not_active IP Right Cessation

- 2001-11-20 CN CNB011436093A patent/CN1225085C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20020083358A1 (en) | 2002-06-27 |

| US6895523B2 (en) | 2005-05-17 |

| KR20020039245A (ko) | 2002-05-25 |

| JP2002158567A (ja) | 2002-05-31 |

| JP3815209B2 (ja) | 2006-08-30 |

| KR100430609B1 (ko) | 2004-05-10 |

| CN1360397A (zh) | 2002-07-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1225085C (zh) | 从时钟信号生成脉冲信号的电路 | |

| CN1260884C (zh) | 时钟控制电路 | |

| CN1252921C (zh) | 占空比校正电路 | |

| CN1206243A (zh) | 包含噪声防止电路的振荡器电路 | |

| CN1258150C (zh) | 半导体器件 | |

| CN1664956A (zh) | 半导体存储装置中的延迟锁定回路及其时钟锁定方法 | |

| CN1278420C (zh) | 半导体器件内的延迟锁定回路 | |

| CN1048270A (zh) | 含有微处理器重置电路的微机系统 | |

| CN1305266A (zh) | 同步锁相环的方法、锁相环及具有锁相环的半导体器件 | |

| CN1773626A (zh) | 半导体装置的振荡器 | |

| CN1091977C (zh) | 用于非整数倍频系统的时钟同步方法电路 | |

| CN1629980A (zh) | 用于降低地址存取时间的半导体存储设备 | |

| CN1870430A (zh) | 占空比校正器 | |

| CN1209628A (zh) | 时钟移位电路及采用该电路的同步型半导体存储装置 | |

| CN1298134C (zh) | 同步电路 | |

| CN1832351A (zh) | 通用时钟同步器及通用时钟同步方法 | |

| CN101030187A (zh) | 数据接收装置 | |

| CN101047380A (zh) | 共用输入/输出端子控制电路 | |

| CN1241067A (zh) | 脉冲宽度改变器以及其中所用的方法 | |

| CN101039109A (zh) | 频谱扩展时钟控制装置及频谱扩展时钟发生装置 | |

| CN1501580A (zh) | 时钟生成电路 | |

| CN1489037A (zh) | 随机数生成器 | |

| CN100338876C (zh) | 电路装置 | |

| CN1710508A (zh) | 时钟调节装置及其方法 | |

| CN1104671C (zh) | 内部时钟脉冲发生装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20051026 Termination date: 20181120 |

|

| CF01 | Termination of patent right due to non-payment of annual fee |