具体实施方式

在此,说明只写存储电路、存储系统、寻址和读出电路以及生产、实现和使用这些电路和系统的方法。在以下的描述中,为了作解释,举出了具体术语和具体实施细节以便对本发明有透彻的了解。但显然本专业的技术人员都了解,并不一定需要这些具体细节来实现本发明。

在以下的说明中,提到“数据”时应理解,所谓“数据”根据上下文可由各种不同方式来代表。例如,在存储元件中,“数据”可由电压电平,磁状态,或诸如电阻等物理特性来代表,该物理特性代表一种诸如电压和电流电平或转变成读出电路等可测量的效果。另一方面,在总线上或在传输过程中这种“数据”可能是一种电流或电压信号的形式。另外,文中的“数据”在多数情况下基本上具有二进制性质,这样可以方便地以“0”和“1”来代表。但应了解实际上,二进制状态可能由相对不同的电压、电流和电阻等来代表,而且不论某一具体实际表现形式代表着“0”和“1”,一般它是非物质的。

本发明的优选实施例包括寻址电路,其形成方法,以及在上述共同未决的美国专利中描述的存储系统中使用的那类寻址交叉点二极管存储阵列的方法。为了提供对本发明的透彻理解,以下就以这一种存储系统为内容进行详细说明,虽然本专业的技术人员会明白本发明不限于仅应用于所述结构。

只写存储系统

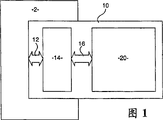

在诸如数码相机和便携式数码音响电器等应用中作数据存储特别有用的便携式、价格便宜且稳定的存储系统以示于图1的方框图中的存储卡10来实现。存储系统最好包括在工业标准的便携式接口卡中(例如PCMCIA或CF),这样,它就可在具有这种接口的现有和将来的产品中使用。存储卡10具有I/O接口接插件12,通过它可在卡10和与其连接的装置2之间进行通信。该接口接插件连接到接口和控制电路14,该接口和控制电路14连接到可拆卸的存储模块20。存储模块20提供用于只写数据存储的电路。接口和控制电路14包括对每个可拆卸存储模块20进行控制、对接、检测并对卡中接收到的错误码作纠错编码(ECC)等的电路。存储模块20这样插入存储卡的插口中,使得可以从中取出并用另一存储模块20更换。插入存储卡后,存储模块20通过内部接口16连接到接口和控制电路14。

只写存储是指,数据只能一次有效地写入存储器,然后就保留不变。在多种形式的存储器中,并不绝对都是存储进的数据在最初写入之后就根本不能改变,但一般不能任意改变,本专业的技术人员都了解这一点。例如,大多数只写存储器都制造成每一存储器元件都处于第一个二进制状态(例如代表二进制数据“0”),在写入过程中选中的存储元件改变成第二个二进制状态(例如代表二进制数据“1”)。通常存储器中从第一个二进制状态到第二个二进制状态的改变是不可逆的,这样一旦写入一个数据“1”,它就不能再改变回数据“0”。这就限制了数据写入存储器后对已存储数据所能作的改变,在存储器中任意数据只能写入一次,以后,例如数据“0”只能改变成数据“1”,反过来就不行。

由于存储模块20包含只写存储器,所以它很适用于数据存储后需保持不变的档案库存储器。这有点象照相胶片,一旦图象存储其上,显影的底片就可作为永久记录保存。因此,一旦存储模块20的全部容量充满了数据,再作数据存储就需换另一个。也可简单地更换装置2中的整个存储卡10,但那就意味着接口和控制电路,以及存储卡构件都和存储模块20一起存了档。为了降低数据存储的费用,最好存储系统中可重复使用的比较贵的元件不要永久地连接到实际的存储器上,故此在优选实施例中,存储模块20可从存储卡上取下。这样存储卡10的主体涉及一次性费用,而插入其中的存储模块20却造价低廉,如以下所讨论。

控制/接口电路14通常类似于“AT”型磁盘控制电路,还包括纠错(ECC)和检测管理功能,以及操作存储模块20所需的功能。这些功能包括:

--向存储模块写入包括设定写入电压、设定允许写入线以及控制电源撤消(stripping);

--通过将逻辑地址转换成存取物理存储器位置所需的地址线图案的方法对存储器寻址;

--读出线输出端的数据读出处理,和

--需要的话作并行-串行转换。

控制/接口电路14还可以提供仿效可重写存储卡某些特性的功能,例如逻辑删除数据文件等。控制/接口电路14的这些功能在例如定制集成电路中实现起来都不困难。上述所需功能从以下对存储模块20的结构和操作的说明就可更充分地理解。

为了存储卡10中控制/接口电路14和存储模块20之间的连接,还提供了内部接口16。物理上,内部接口16接纳存储模块并提供控制/接口电路和存储模块之间的电连接。可以采用合适的插头和插座装置,但最恰当的结构主要取决于需作连接的实际数量。存储模块上的连接触点可以在其外表面形成,例如下文所述,以启动边沿连接模式或网格焊台阵列(LGA)连接。本专业的技术人员都知道,多种连接方案都有可能,实现起来不会有太大困难。

只写存储模块

存储模块20可以利用本发明的原理很便宜的制造出来,从而提供数据存储的低单位成本。为了保持存储器的低成本而同时具有高的存储器容量,考虑到了诸如材料和工艺成本等数个因素。存储模块20的这些特性在下面进行讨论,从存储模块20的一般结构开始。

存储模块20的方框图示于图2,存储模块20连接到控制/接口电路14。为了增加给定基底面积的存储模块的存储容量,模块20由层叠的层22的堆栈构成。每一层22都具有阵列25或提供数据存储的存储元件阵列。每一层还包括寻址电路30,它通过存储系统内部接口将各存储阵列连接到控制/接口电路14。每一层的寻址电路启动较少的存储模块的各层之间以及从存储模块到外部电路的互连线,这样就便于制造并可降低成本。

图3是存储模块20的剖面立体图,示出存储模块的电路和层的可能的物理结构。每一层22包括在衬底50上形成的存储阵列25和寻址电路30。存储阵列25包括存储元件26的矩阵。寻址电路30包括位于存储阵列25的各正交边附近的行和列复用电路部分。输入/输出(I/O)引线40也在制造过程中在衬底上形成。在存储模块20中,行I/O引线从行复用电路部分延伸到衬底的第一邻近边,列I/O引线从列复用电路部分延伸到衬底的第二邻近边。每一引线40在相应的接触片42处终止,接触片42的一部分暴露在衬底50的边沿。

多个层22以相同取向层叠在一起。通过导电接触元件55电接触到叠层的接触片42的暴露部分,图3中以部分剖面图的形式示出。接触元件55沿存储模块20的侧面延伸,与各个层22的平面相交。图中所示的每一个接触元件55电连接到堆栈中多层的相应的接触片。接触元件55可用来通过存储系统内部接口16把存储模块20连接到控制/接口电路14。

在存储模块的优选实施例中,每一层22的衬底50由诸如塑料(例如聚酰胺,聚脂)或金属(例如复有介质层的不锈钢膜)等薄的便宜的材料形成。下面将会对在衬底上形成集成电路(例如存储器阵列和复用/去复用电路)以及将各层组合成存储模块的过程做更详细说明。前面对制造过程和材料的讨论是对存储模块电路,特别是存储阵列和元件以及集成复用方案进行说明。

只写存储阵列

在存储模块20的每一层上形成存储元件26的阵列25。存储阵列包括行线和列线的规则矩阵,每个行/列的相交处有存储元件。图4是有列线60和行线62的部分存储阵列25的示意图。每一列线和行线之间接有存储元件26,其细节示于图4的放大部分。在存储阵列的优选实施例中,每一存储元件26包括与二极管元件66串联的熔丝元件64。熔丝元件64提供存储元件的实际存储效果,而二极管元件66便于利用列/行线对存储元件寻址做数据的读出和写入。

存储阵列25的工作如下:制造时,每个存储元件26具有导电的熔丝元件64。熔丝元件64的导通状态代表一个二进制数据状态,比如说,数据“0”。为了向存储阵列写入数据,利用列/行线对需存储数据的每一存储元件寻址,于是其中的熔丝元件“烧断”,使其处于非导通状态。熔丝元件的非导通状态代表另一个二进制数据状态,比如说,数据“1”。在大多数情况下,熔丝烧断是单向过程,这就使存储器成为一次性存储,如上所述。例如通过选定的行线把预定电流加到选定的列线上来进行数据写入操作,该电流足以烧断直接使该行线和列线互连的存储元件的熔丝。利用行线和列线对存储元件寻址并感测哪些存储元件是导通的(数据“0”)和哪些存是不导通的(数据“1”)就可从存储阵列读出数据。更通常的是,存储元件的二进制数据状态由“导通”电阻和“非导通”电阻之比率来区别。

下面将指出,虽然上述说明是指存储阵列的熔丝元件作成低电阻状态而后烧断造成高电阻状态,同样也可以利用以相反方式工作的“抗熔断”元件来制造存储阵列。在这种情况下,存储元件制造成高电阻状态,而后烧断成低电阻状态。每个存储元件的抗熔丝也与二极管串联,理由同上。此时,二极管和抗熔丝是分隔开的,因为在抗熔丝烧断后还需要二极管的功能。

熔丝或抗熔丝的一个必需特性是在某一临界电流阈值它的电阻在高态和低态之间(或相反)发生不可逆的改变。电阻的改变应是显著的:要有几个数量级。熔丝的临界电流应可由器件的面积控制。器件的面积可以简单地用行电极和列电极相交处的面积来确定,或可用光刻法定义。熔丝和二极管元件可由多种薄膜连续淀积在行电极和列电极之间来形成。各个存储元件形成在行电极和列电极相交处。虽然熔丝和二极管层是淀积成覆盖整个区域的连续薄膜,但可用多种方法(激光烧熔,光刻,软光刻)作出它们的图案以减少各器件间的串扰。

阵列的每个存储元件26中的二极管元件66利用列/行线唯一地协助对存储元件进行寻址作数据的读出和写入。如果在列/行交叉点存储元件中没有二极管,就会有电流通路通过给定的行线和列线之间的许多存储元件。但是,在二极管元件形成通过每个存储元件的单向导电通路的情况下,单一的行线和单一的列线就可用来唯一地确定单个存储元件的地址。换句话说,形成从一行线到一列线的电路就使电流可以只通过单个的存储元件。借助通过该电路施加预定的“数据写入”电流,存储元件中的熔丝就被烧断,把数据“0”变成数据“1”。而且,通过检测电路中的电阻,就可确定存储元件的熔丝是断了还是原封未动,从而读出数据“1”或数据“0”。

这样,二极管66在读出和写入操作中消除了存储阵列中存储元件之间的串扰。另外二极管的非线性电流-电压(I-V)特性改善了数据读出的信-噪比(SNR),有助于遥感和码字寻址。存储模块中的数据是以遥控的方式读出的,因为读出电路是处在单独的集成电路包含的接口和控制电路14中。而且,如下面所描述的,置换二极管逻辑也用于利用复用/去复用电路来对存储元件进行寻址,以便减少存储模块20和接口和控制电路14之间所需的连接数目。

在本文中有时称存储阵列为交叉点阵列存储器,这是考虑到其结构的缘故,图5是该优选实施例的存储阵列的一个存储单元的简化平面图。交叉点阵列存储器的基本结构包括两层正交的多个等距平行导线,中间隔有一半导体层。这两组导线形成行电极和列电极,相互叠交的方式是每个行电极仅在正好一处与列电极相交。在每个交叉点,在行电极(图5的62)和列电极(图5的60)之间通过半导体层(图5的75)作电连接,起二极管和串联熔丝的作用。阵列中的所有二极管这样取向、使得如果在所有行电极和所有列电极之间加共用电位,则所有二极管的偏置方向相同。熔丝元件可以作为一个当临界电流流过时会开路的单独的元件,或也可将其组合进二极管的作用中。

虽然通常在本说明书中提到半导体层时都是指的单数,但实际上可采用不同材料的多层。这些层可包括各种结构的诸如金属和介质等非半导体材料。适合于实现所需功能的材料和结构在其它地方做说明。

图6是交叉点只写存储阵列的示意图。该图示出一个8行乘8列的阵列。如果电压如图所示加在行和列电极上(即:所有的列电极都是电压V,只有一个是-V,而所有的行电极都是电压-V,只有一个是V),那么,只有一个二极管被正向偏置。在图6所示的情况下,只有阵列左上角的二极管(90)被正向偏置。最上一行和最左一列的二极管上没有偏压,阵列中其余的二极管都被反向偏置。这就构成了阵列的寻址方案。如果电流在有这些电压的二极管的行和列中间流过,左上角二极管的熔丝保持不变(例如,代表数据“0”)。相反,如果没有电流在该结构中流过,则相应的二极管/熔丝就会烧断(例如,代表数据“1”)。调整加到阵列电极上的电压幅度,就可使更大的电流流过所选二极管。如果该电压引起的电流超过熔丝的阈值电流,则熔丝烧断,从而改变存储元件的状态。这就构成了写入存储器的方法。

烧断存储阵列中熔丝的实际电流(或为得到此电流所需的电压)在制造时应可预计并可控制。由于通过存储元件的电流密度是作用因素,所以元件烧断时所加的电压/电流就可通过改变元件的交叉点面积来调节。例如,如果交叉点电极的相交截面积减小,为达到烧断熔丝的临界电流密度所需施加的电流/电压也就相应减小。这种方案可用在存储电路设计和制造中以确保可以施加只烧断所需的交叉点熔丝的控制电压。

存储阵列寻址电路

为了简化对存储模块的互连,最好使用复用寻址方案来访问存储元件。换句话说,最好是存储阵列的每个存储元件都可通过比阵列行线和列线总数要少的寻址线从外部电路唯一寻址。为此目的,复用和去复用电路(30)也和存储阵列一起被包括在同一衬底上。最好复用和去复用电路由与存储阵列兼容的逻辑族构成,以便维持简单的制造工艺。事实上,如下所述,确有可能用存储阵列中用的同样简单的器件来构成复用和去复用电路。

在该优选实施例中,地址的复用/去复用功能是用以下要描述的称为置换二极管逻辑的逻辑方案进行的。图7示出以熔丝和二极管串联来代表的单个只写存储元件102。存储元件102接在行电极104和列电极106之间。行地址二极管逻辑电路110连接到行电极104,列地址二极管逻辑电路120连接到列电极106。如图所示,行地址电路110包括连接在行电极和工作电压(pull-up voltage)+V之间的电阻元件112。行地址电路110还包含多个行解码二极管114,它们的正极接在行电极上,而负极分别由以X,Y和Z表示的行地址输入电压来控制。列地址二极管逻辑电路120的构成形式类似,有一电阻元件122从列电极106连接到反偏压(pull-down voltage)-V。多个列解码二极管124的负极连接到列电极,正极则由以A,B和C表示的列地址输入电压来控制。

首先考虑行地址电路110,在此电路中逻辑电平+V和-(V+ΔV)作为行地址输入电压(X,Y,Z)。显然,如果电压+V代表逻辑“1”,行地址电路110就象一个“与”门,其二极管负极(X,Y,Z)为输入端,行电极104为输出端。仅当所有三个行地址输入端(X,Y,Z)都为高时,行电极104才为高(+V)。同理,列地址电路120起负逻辑“与”门作用。此时,如果在列地址输入端(A,B,C)上加逻辑电平-V和-(V+ΔV),当所有三个输入都是-V时,列电极106的输出只能是-V。如果行地址输入端(X,Y,Z)都把负极电压+V都加到二极管114上,且列地址输入端(A,B,C)都把正极电压-V都加到二极管124上,则存储元件102被选中。虽然图7只示出三个输入电路,但此寻址方案可扩展到包括任意数量的输入端。

图8示出一个8x8只写存储阵列150,具有如上所述的作寻址存储元件的连接的行和列电极。为便于参考,存储阵列150的列电极标为G

0至G

7,行电极标为H

0至H

7。每一行(X,Y,Z)和每一列(A,B,C)有三个寻址组。每一寻址组有两个互补的寻址节点(例如A

1和A

2),每一节点连接到8个相应的行/列电极中的四个。节点与行/列电极的连接形式各寻址组各不相同。在图8的实例中连接形式如下:

|

A1 |

A2 |

B1 |

B2 |

C1 |

C2 |

|

G0G1G2G3 |

G4G5G6G7 |

G0G2G4G6 |

G1G3G5G7 |

G0G1G4G5 |

G2G3G6G7 |

列电极地址节点连接

|

X1 |

X2 |

Y1 |

Y2 |

Z1 |

Z2 |

|

H0H1H2H3 |

H4H5H6Hx7 |

H0H2H4H6 |

H1H3H5H7 |

H0H1H4H5 |

H2H3H6H7 |

行电极地址节点连接

列电极与列寻址节点之间的连接各包括一个二极管,其连接如152所示,而从行电极到行寻址节点的连接各包括一个二极管,其连接如154所示。大多数这些二极管在图8中未示出,以免过于复杂。虽然此实例的布局显示地址线都连接到阵列中电极的一端,但地址线也可一样方便地连接到电极的任一端或两端(阵列侧面)。

通过在寻址节点上加电压来对存储阵列150寻址。只在每个寻址组的一个节点上施加启动电压。这样就允许以关于图7所述的方式只选择阵列150中的一个存储元件。

多存储模块层寻址

上述用于读出被寻址的存储元件的状态的系统取决于被寻址的二极管存储元件是行和列电极之间唯一的电流通路。但如果在存储模块中使用并行寻址,就有可能在行和列地址线间有不止一条导通通路,这就会使该读出方案的使用很困难。所以,在下面提出一种检测被寻址的存储元件的改进的方法和系统。

如上所述,此处公开的存储模块的优选结构包括多层的堆栈。每一层都包括只写存储阵列,各不同层的阵列共用同样的地址线以减少需与外部电路连接的数量。因此,即使在单个阵列中一个给定地址唯一寻址一个存储元件,在多个并联寻址阵列中,多个存储元件可被寻址,每一层一个。这样作还有另外两个理由。第一,由于能够并行读出m层,所以为获得给定的串行比特率所需的读写速率就被m除。第二,如果存储器的每一层都需要单独的地址线,那么从层到层和从存储器模块到接口和控制电路的连接数量会多得无法管理。

并行寻址困难的一个较好的解决方案涉及到在接有地址二极管的同一节点上包括对每行和/或列电极接上附加的读出二极管。每行读出二极管的另一端连接到共用的行读出线,同理,每列的读出二极管未接至列电极的那一端连接到共用的列读出线。被寻址存储元件的状态可由或者行读出二极管、或者列读出二极管或者二者进行检测。由于较好的阵列结构的对称性,从此处的说明可知行和列电极在功能上实际上是等效的。

被寻址存储位的状态是由通过读出线流到适当选择的偏压点的电流而决定的。为使电流通过任一读出线,必须满足两个条件:(1)必须对所述二极管存储元件寻址,(2)该元件的熔丝必须处于高电阻态。在所有其他情况下,二极管不被寻址,而且,不论熔丝的状态如何,相应的行和/或列读出二极管都不被正向偏置,也不会导通电流。因此,如果单一读出线连接到所有的行(或列)电极且在行和列阵列中寻址一个存储元件,那么该存储元件的状态就可毫不含糊的被确定。

利用行和列读出线既提供了冗余度又不会影响读出过程的速度,从而改善了信号检测的容限。应当指出,对行或列电极增加另外的读出线,和/或在读出线和行和列电极间增加额外的并联二极管,也可增加冗余度。

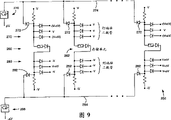

图9示出利用上述技术的寻址和读出电路的示意图。图中示出只写存储阵列的多个存储元件260,它们连接到按上述方法制造来对存储阵列寻址的各自的行和列寻址电路270,280。电路250还包括共用行读出线274和共用列读出线284。共用行读出线274通过各行读出二极管272连接到每一个存储阵列行电极。具体地说,每个二极管272的正极连接到相应的行电极,其负极连接到共用行读出线。同理,列读出二极管282从共用列读出线284连接到存储阵列的各列电极。二极管282的负极连接到各列电极,其正极连接到共用列读出线。

在图示的实例中,中心存储元件(262)被寻址。这是因为存储元件262是与被寻址电路选中的行和列电极都相连接的存储元件。如图所示,存储元件262对应的寻址电路中没有一个行或列地址二极管由于所加电压而导通。如果存储元件262的熔丝烧断,则电流就会流过读出二极管272,282,以及行和列读出线274和284。如果中心存储元件保持不变状态,则不论阵列中任何其它存储元件的熔丝状态如何,行和列读出线中都不会有电流流过。在此情况下,没有电流通过对应于被寻址存储元件的读出二极管,且所有其它存储元件都未选中,因为寻址方案确保只有一个地址二极管会导通,从而保证对应的读出二极管被反向偏置。

对于上述检测方案,利用专用读出二极管时,从检测的观点来看各个数据二极管的漏电并不特别重要,更重要的是在有源读出线上的非活性读出二极管的漏电流。因为,对于有N个元件的阵列而言,每条读出线上只有sqrt(N)个读出二极管,适中数量的电源条(power spply stripe)就可将此问题减少到易于管理的程度,特别是对整流比约为106的二极管。

寻址电路制造

交叉点二极管阵列由衬底材料构成,在所述衬底材料上淀积被构成图案的金属层。这一层是行或列电极层。然后涂敷半导体层。理想的是这一层是由不需构成图案的材料形成,但根据二极管的间距,膜厚,和材料性质,可能也需构成图案。在以下的说明中,假定半导体层不需被构成图案。最后,加上其电极与第一金属层的电极成正交的第二个有图案的金属层。这种结构示于前述图5所示的存储阵列单元。

本发明的优选实施例使上述复用及读出方案能够用交叉点二极管阵列所需的同样工艺进行制造。具体地说,从制造的观点来看,该复用及读出方案的一个重要方面是它们可以利用复用及读出二极管作为通道来实现。传统的两层互连需要有一种介质材料放置在作有图案并加工成有导通通道穿通的两金属层之间。这种工艺需要此二金属层以及介质材料的精确对准。利用复用及读出二极管作为通道,本发明的优选实施方案在制造过程中不再需要用到介质,对准容限也可放宽。

图10是具有上述形式的复用及读出电路的交叉点存储阵列的布局图。该简化图示出了一个二阶寻址的9x9交叉点二极管阵列的行电极、列电极、行读出线、列读出线、行地址线、列地址线。如图所示,列电极502和行电极504相互正交,它们形成在由半导体层隔开的各层上。在电极交叉点形成二极管,构成交叉点二极管存储阵列506。每个交叉点二极管可以从通常的导通态转换成“熔断”高阻或开路态,这就是用来向存储器阵列写入数据的方法。为使二极管从导通态转成开路态,在二极管的正向偏置方向上通过一个超过某一临界电流密度的电流。在该图中,在交叉点未发生变化的二极管元件用“0”表示,熔断的二极管元件用“X”表示。图示的该交叉点存储阵列中没有存储数据,故其中所有的二极管都是原封未动的。

考虑到与对准有关的实际原因,最好是调整行或列电极的宽度,而不是地址线的宽度。如果调整地址线的宽度,则调整必需在行/列线之间间距的范围内进行、使得两相邻二极管不致无意间被熔断。而且,使行/列线从矩阵的对侧伸出可使宽度调整加倍,有助于增加编程过程的裕度。另外,通过选择特定的连接布局,可以保证不会有两条连续的从阵列任一侧伸出的线同时被加宽,进一步增加了编程的裕度。最后,地址和读出线比其他行或列线要宽,因为它们需要传导更大的电流,并在诸如写入时的寻址操作或地址编程操作期间不会失效。他们也可具有更大的间距以减轻对准的容限。

行和列电极从交叉点阵列伸出,终止在上拉/下拉电阻508处(对应于图7的电阻112,122)。与存储阵列和终结电阻之间列电极交叉的是多条列地址线510和至少一条列读出线512。列地址线和列读出线与行电极形成在同一导线层上,这样在它们与列电极交叉处其间就形成二极管结。由列读出线形成的二极管元件对应于图9的二极管282,由列地址线形成的二极管对应于图9的二极管280。通过以下方法形成上述地址线组/节点配置:把选中的列地址线元件熔断,保留所需的二极管连接原封不动(如果是抗-熔丝,形成选择性的连接,保留其他为高阻抗状态)。这种寻址电路的编程可在电路制造后最后完成,如下述。

同样,行电极504也与行地址线514和行读出线516交叉。行地址线和行读出线与列电极形成在同一导线层上,形成行地址二极管(例如图9的270)和行读出二极管(例如图9的272)。

在制造时,在每一列地址线和每一列电极之间以及每一行地址线和每一行电极之间形成二极管结。但是,为了实现上述的组/节点寻址方案,需要在寻址线和阵列电极之间只维持选中的二极管连接。可在电路制造之后通过熔断某些地址二极管而保留选中的二极管连接原封不动,来最终完成选中连接的“编程”。

电极宽度调整的另一方面是所有地址二极管(以及读出二极管)必须能耐受会熔断数据二极管的电流。这种情况发生在二极管正被写入的条(stripe)中未被寻址的行或列电极上的地址二极管。那些二极管分流正用来写入选中二极管的同一电流。相应地,所有地址和读出二极管必须大于数据二极管,但有一些可甚至更大些以便上述编程过程的进行。

所有地址二极管都制造成与行/列电极并联。如果所有二极管都相同,则当在行/列电极和地址线之间施加公共电位时,类似电流会流过每一二极管。但如果二极管有不同的有效面积,虽然它们仍承载着大致相同的电流,但却有不同的电流密度。在这种情况下,就会有电流超过某些二极管的临界电流密度,导致它们熔断,但保留其它二极管原封不动。这种特性被开发,如下述,以使地址网络可被编程。有利的是,本发明的优选实施例不仅提供了在地址二极管、读出二极管、和行与列电极之间建立适当连接的方法,而且也确保了二极管的正极和负极均恰当取向以实现上述的二极管的逻辑功能。

图11示出正交电极交叉点的各种构造,示出为了改变在交叉处形成的二极管的有效面积而改变正交电极宽度的途径。图中未示出分隔垂直和水平电极的半导体层。中间一行的交叉点308,310,312具有标称的交叉面积,即其电极的宽度既不加宽也不变窄。这些电极交叉点在集成电路中形成标称的正常大小的二极管。上面一行电极交叉点302,304,306在交叉点的电极部分变窄。具体地说,交叉点302有变窄的垂直电极部分,交叉点306有变窄的水平电极部分,而交叉点304的垂直和水平电极都变窄。这些电极交叉点形成集成电路中较小的二极管。在较小的二极管中,减小的正极和/或负极面积导致电极间半导体层截面积的减小。这就意味着通过二极管的较小的电流会引起二极管达到其临界电流密度,致使二极管熔断而不导通。另一方面,交叉点314,316,318具有较宽的正极和/或负极面积,意味着这样形成的二极管可承载比正常电流大的电流而不会达到其临界电流密度。有一些面积比其他二极管大的二极管也是很好的,这不仅是为了编程的原因。例如,地址和读出二极管可以更大一些以改善其强度和制造成品率。

一般公认,熔断一个给定的交叉点二极管所需的实际临界电流密度取决于好几个因素,不仅仅是交叉点正极和负极的大小。例如,半导体层用的材料和层厚也会影响需要什么电流密度来熔断一个给定的二极管。但是,假定半导体材料特性和层厚在集成电路面积上都是相对一致的,二极管电极面积的大小可用来控制相对于其它具有不同电极面积的二极管的击穿二极管所需的电流电平。

图12示出两层集成电路导线的结构,示明为什么只改变一个正交电极的宽度来改变二极管的有效面积就特别有利。图的上部是两个行电极和两个列电极的交叉。行电极与一对行地址线交叉,列电极与一对列地址线交叉。图中列电极和行地址线垂直伸出,它们形成在第一导线制造层。行电极和列地址线水平伸出,它们形成在第二导线制造层。图的下部是同样的导线结构,但水平导线相对于垂直电极稍稍倾斜,这种情况制造时可能发生。

行和列电极的间距一般选择为制造光刻工艺等可支持的最小值,以便获得最大的存储器阵列密度。但地址线的间距可相对较大,因为它们数量较少,不会严重影响存储密度。示于图12的结构策略包括以较大间距(相对于行和列间距)隔开的等宽地址线。然后,调整行和列电极在整个长度上的宽度,使之与地址线间距可相比拟,那么在平直移动和旋转时行与列层间所需的对准都可大大减少。如图下部所示,用这种技术形成的器件交叉点部分对于对准几乎不敏感,且地址线对于不对准的敏感度与地址线的间距成反比。

图13是存储模块层600的方框结构布局图,示出各电路元件相对定位的实例。存储阵列602位于中心,在其周边是地址/读出线604,上拉/下拉电阻606和电源调线连接(power supply stripingcoupling)608。在这些电路的外围有接触片610用作外部互连。从上述说明可知,层600的构造特别简单,行/列电极通过地址/读出电路,电阻和调线连接从阵列伸出到互连接触片。地址和读出线的结构类似,所有二极管电路元件都在导线交叉点处自动形成(有一些二极管随后在编程时要熔断,如上所述)。应当知道,描述存储模块层的这些图不是按比例的,虽然寻址读出和条电路(striping circuitry)在图中作了放大,但是这种电路一般只占层面积的约5-10%。

图14更详细的示出存储模块层布局的一部分。此处,示出具有列电极612和行电极613的存储阵列602的一部分。列电极与列读出线614和列地址线616交叉,形成地址/读出电路604。在606,在列电极中形成上拉/下拉电阻。列电极安排成条形,其中电极组连接到各电源终端608a,608b。行电极的结构类似(未示出)。通过一次只把电源加到存储阵列的一部分(子-阵列),从而选中该部分,可以把电源调线连接(power supply striping connection)用作寻址方案的一部分,也可作为减少漏电流的机制。

假定地址线和电源线都通过总线(共用)连接到存储模块的所有各层,对每一层的某一位寻址并在有源子阵列(取决于电源调线)中使电源从读出电平选通到写入电平,就可写入数据。但对不同的层必须能写入不同的数据状态,利用读出线拉低存储元件二极管/熔丝需受保护的那些层上的电压,就可作到这一点。这意味着读出二极管必须能耐受能烧断存储阵列元件的电流。所以,读出二极管就制造成具有较大的截面积,以减小通过其上的电流密度。

集成电路结构

再回到图3,现说明存储模块的物理结构。如上所述,存储模块20的优选形式具有多个堆叠的层22,每一层都有在塑料(聚合物)衬底50上形成的存储阵列。虽然并不是必须用聚合物作衬底材料,之所以选用它们是因为这些材料能够以较低的成本生产和加工。衬底50可用各种商用聚合物材料形成,最好是薄片材的形状。可用作衬底50的典型聚合物材料包括,但不限于:聚酰胺,例如从杜邦公司获得的KaptonTM;聚醚砜(PES);聚丙烯酸脂(PAR);聚醚酰亚胺(PEI),例如通用电气的UltemTM;聚乙烯萘酯(polyethylenenaphthalate)(PEN);聚乙烯对钛酸盐(PET);聚脂对钛酸盐,例如杜邦公司的MylarTM;聚四氟乙烯(PTFE),例如杜邦公司的TeflonTM;聚碳酸脂,例如通用电气的LexanTM;聚氯乙烯(PVC);聚脂薄膜,例如Orica的MelinexTM;以及其它已知的在塑料衬底上形成电路的技术中使用的聚脂膜和聚合物膜。衬底最好较薄,以便能“成卷”加工,例如厚度大约为0.01mm到0.05mm。

存储阵列25和寻址电路30可按照金属-半导体-金属(MSM)工艺在塑料衬底50上形成。MSM工艺产生两层有图案的导电金属电路层,这两层中间有一层或多层半导体材料。在金属层交叉并与半导体层相对的一面接触的位置,在金属层之间就形成了二极管结。MSM二极管集成电路的生产在例如国际专利申请公开No.WO99/39394,题目为“X-Y可寻址电微开关阵列和利用它们的传感器矩阵”中有所说明。该文件的内容作为参考详尽地包括在本文内。

有多种不同的材料可用作存储模块的半导体层,有一些在前述公开中已列出。有机和无机材料都可用作半导体层。无机材料包括例如非晶硅和锗材料,已知在光生伏打电池领域这种材料有类似的应用。但人们喜欢选用有机半导体材料是因为它们能在较低的温度下加工,这就更适合在塑料衬底上成形。在此应用中有机材料的其它可能的有利条件是:1)可以通过改变化学结构而改变的电子性能,2)高度各向异性的体导电率,从而不需将半导体膜构成图案,以避免元件和元件间的串扰,和3)有可能利用半导体作为导电粘结剂来组成交叉点结构。例如,聚酰胺衬底材料可以耐受在高达约300℃温度下加工,但其他可能的诸如PEN和PET等衬底材料限于大约130-150℃的最大加工温度。所以,对既定应用的半导体材料的选择取决于所选的衬底材料。一般来说,能在低于150℃温度下加工(如,淀积和必要的话构成图案)的半导体材料都可与多数适用的衬底相兼容。

在存储模块中可用作半导体层的有机材料实例包括由copperpthalocyanine(CuPc)和PTBCI(3,4,8,10-perylenetetracarbonxilic-bis-benzimidazole)组成的双层。其他可与CuPc结合使用的备选材料是:PTCDA(3,4,9,10-perylenetetracarboxilicdanhydride),和BTQBT[(1,2,5-thiadiazolo)-p-quinobis(1,3-dithiole)]。各层还可以用以下材料形成:TPD(N,N’-diphenyl-N,N’-bis(3-methylphenyl)1-1’biphenyl-4,4’-diamine;α-NPD(4,4’-bis[N-(1-napthyl)-N-phenyl-amino]biphenyl),和四苯(TPP(5,10,15,20-tetraphenyl-21H,23H-porphine))。其他材料也可用于本发明的目的,这对本专业的技术人员显而易见。

图15是存储模块一部分的简化的立体图,示出其一般结构。图上示出形成在第一金属层的衬底50上的一对电极导线70。在第一金属层上形成两层半导体材料72,74。由叠加在半导体层72,74上的第二金属层形成与导线70相交的导线76。在第一和第二金属层的导线70和76之间夹有半导体材料的地方,形成二极管元件。在图15中所示半导体层是连续的,但如果所用半导体材料相对膜厚具有低的体电阻率,使得横向漏电流与拟在电极交叉处通过薄膜的电流相比甚为可观,则需将半导体层做成图案。

在存储阵列中由半导体层形成的二极管最好既作为二极管(如图4的66)又作为存储元件的熔丝(64)。此时,半导体层需完成熔丝的功能,即:在预定条件下,二极管结特性不可逆转地变到高阻抗态。例如,在存储器写入操作时,可用通过二极管的高于某一电流密度阈值的电流密度来击穿二极管,将其导通特性改变到高阻抗。可以这样工作的电极/半导体/电极层状结构的实例是:

(2000埃)Au/(800埃)CuPc/(800埃)PTCB/(200埃)BCP/(3600埃)Ag

式中,CuPc是copper pthalocyanine,PTCB是3,4,9,10-perylnetetracarboxilic-bis-benimidazole,BPC是bathocuproine。

另一种方法是,也可用抗-熔丝元件构造以相反方式工作的存储阵列,其中存储元件制造成高阻抗态,然后被写入导致低阻抗态。例如可用掺(如p+-n-i或n+-p-i)非晶硅层结构作半导体层,需要时它可允许存储元件实际上被擦除或重写。这些结构在例如P.G.Lecomber等的“非晶硅结中的开关机理”(非晶体固体杂志,Journalof Non-Crystalline Solids 77&78(1985)pp1373-1382),和题目为“利用成形电压的非易失性非晶半导体存储器件”的美国专利4,684,972中都有说明,这些文件的内容作为参考明确包括进本文中。

层制造工艺

存储模块中每一层都利用快速而便宜的工艺制造有助于获得成本低廉的产品。例如利用柔性聚合或金属(带介质膜)材料的薄带(thin web)状衬底就可采用较便宜的成卷制造工艺。

以下称为压纹和拆下的技术最初是开发来制造独特的卤化银基的照相胶片PolaroidTM。这种技术可以有利地应用来生产交叉点存储阵列的行和列电极以及地址/读出线,因为它能在经济的成卷加工工艺中在塑料带(plastic web)上生产亚微米大小的部件。微压纹工艺的一个实例在题为“定向能量用于真空微压纹中”的美国专利6,007,888中做了说明,其内容以参考文件包括与本文中。另一方法是,也可用传统的光刻工艺,但在生产环境下目前这种工艺的最小特性尺寸限于大约25微米。

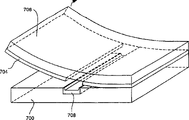

压纹拆下(emboss liff/off)工艺示于以下叙述的图16至22的各步骤。所述工艺以厚度小到10微米的塑料薄带700开始(图16)。第一步是用有微米级特征的图案压制衬底。压制用一辊轴进行,辊轴上有通过类似于为CD-ROM注塑成型工艺生产母片所用的传统高分辨率光刻工艺在其表面上确定的特征。图16示出压制后塑料衬底700的一部分,示出压制的特征槽702。压制在衬底上的图案对应于例如存储阵列的一个导线层和地址/读出线电路。

薄带700用蒸发、溅射、汽相淀积等方法镀复导体(如金属)材料704。镀覆盖层可包括一层薄膜或形成堆栈的数层薄膜。总淀积薄膜厚度小于压制特征(702)的深度。图17示出薄带700在淀积后导体镀覆盖层704覆盖其表面以及压制的特征702中。淀积工艺的性质导致塑料覆盖层的非均匀性,压制特征的侧壁上的覆盖层厚度比与薄带平行的表面上的厚度要薄。这对以后的拆下步骤很重要。

在拆下步骤中,复有压敏粘结剂(未示出)的第二层塑料膜706与第一薄带700相接触。第二层膜粘结到膜704的所有各点,但在压制的特征702中覆盖层凹陷处除外。然后剥离第二薄膜,如图18所示,从第一衬底上移去覆盖层704,但在压制区中的凹陷部分708除外。这个过程取决于两个因素。第一个因素是压敏粘结剂与覆盖层704形成的结合力比覆盖层与在其上淀积的薄膜700的表面形成的结合力要强。第二个因素是要求导体材料覆盖层在压制特征的侧壁足够薄,可使这些区域破裂,而不是从压制凹陷702中把覆盖层部分708拉出去。

此时,有两层可用的有图案的导电薄膜附在塑料衬底上。图19示出拆下后留在压制衬底700上的作有图案的覆盖层708。如果需要有图案的导体708从压制的特征凸出塑料衬底,就需要另一次拆下。这种可选择进行的拆下的第一步是在压制衬底700的表面作一个塑料材料的相似覆盖层710。这一步的结果示于图20。在这一步中,第二种塑料材料710流入图案特征中并粘附在其余有图案导体708的暴露表面。当塑料层710从压制衬底剥离时,如图21所示,它把有图案的导体708和它一起拉开。图22示出具有图案的导体708凸出其上的(倒置的)第二塑料衬底。

上述压制/拆下工艺可用来为每个存储模块层制造两个分离的导体层。然后通过在两个导体层间作一半导体层就完成了存储模块层(22)。例如,如上所述,可以在一个衬底的导体图案上覆盖提供二极管结和熔丝功能的一层或多层材料,然后使另一衬底的导体图案与半导体层的暴露表面物理接触。这种过程示于图23,24和25。

在图23中,示出两个子层802和804,它们可用压制/拆下工艺分别形成。子层802包括在衬底806上形成的第一导体结构808,它形成存储电路的一个导体层。例如,导体结构808可包括列电极、行地址线和行读出线,还有与之相关的接触片和连接点。子层804包括在衬底810上形成的第二导体结构812。第二导体结构可包括行电极、列地址线和列读出线,还有与之相关的接触片和连接点。

为形成二极管结和熔丝功能的一个(或一些)半导体层示于图24,该层淀积在第一子层802的衬底806上的第一导体结构上。这样在第一导体结构和半导体层的一侧形成了电接触。然后第二子层804倒置放在已淀积的半导体层上方,使第二导体图案与半导体层的另一侧接触。第一和第二子层的电极导体彼此相交(例如正交),以形成如上所述的交叉点结。由于电路结构都是从其间的交叉点二极管和互连形成的,所以第一和第二子层间不需要精密的对准容限。这样就形成了图5中在820示出的完成的存储模块层。然后可把多个这种层组装成一个存储模块,如下述。

根据实际选择的半导体材料,子层可以用半导体材料作为粘结剂相互粘结。小分子量的半导体材料已显示能与接触子层结合得相当强。另一种方法是,在使用塑料衬底材料时,塑料子层材料可用加热法粘结在一起。

从以下对存储模块组件的说明可更充分的了解到,最好接触片在横向上相对较宽以使存储模块中各层间易于对准。但是,在上述压制/拆下过程中,对于可制成没有粘附在压制区导体层(708)的拆下薄膜(706)的压制区宽度有一个极限。所以,最好接触片由一系列交叉的导体(在单一导体层上)形成,以避免这种困难。

存储模块制造工艺

制造存储模块涉及到把多层存储器堆叠成一个互连的三维存储模块。根据制造存储器所用的工艺,堆叠可以用在同一衬底上淀积多个交错层的方法实现,也可把各在其自身衬底上制成的完整的层(如上所述)平叠在一起。授予Thomson-CSFDE的美国专利5,640,760提到了这后一种方法。堆叠和互连技术可从Irvine SensorsCorporation of Costa Mesa(california)获得,其工艺的各方面在例如美国专利5,424,920;5,701,233和5,953,588中有说明。堆叠和互连技术也可从法国3D Plus of Buc获得。

图26示出按本发明的实施例从上述多个层22制造存储模块的过程400的通用步骤。过程400从制造好的集成电路层402开始,该电路层具有在塑料衬底406上形成的存储阵列和寻址电路404。它还有互连引线408从电路404的输入和输出接点伸出到各个线性排列的接触片410。层402还包括穿过衬底406形成的对准孔412。层402最好经过测试以确保其上的电路功能正常再送去组装成存储模块。

在过程400的下一步,利用穿过对准孔412伸出的对准杆422把多个层402相互对准并堆叠,形成堆叠层420。堆叠层420可包括多个按同一取向排列的多个相同的层402。用环氧树脂等材料把堆叠层的各层叠加在一起,环氧树脂使各层结牢在其对准位置并形成密封块430。

用高精度锯或其他切割方法通过图中432所示的线从块430上切去端头和侧边。如图中堆叠层420的顶层上所示,块430的切割面通过接触片410的线伸出,这样从切割块侧面的叠层的每一层暴露出接触片410的端面。切割后的块示于440,示明每一层的接触片410的暴露端头。应当理解,在这些简化的图中的特征并不按相对比例示出,某些特征,为了便于图示,例如暴露的接触片部分是夸大的。

切割块440镀复一导电金属覆盖层,例如镍/铝合金,形成镀复块450。金属覆盖层对镀复前暴露在切割块440侧面的接触片410的端头形成电连接。最后,用例如激光刻槽工艺从镀复块450上除去部分金属覆盖层。金属片的保留部分462提供了块中各层的接触片之间的互连。可以用任何所需的方式将金属镀层构成图案,例如在存储模块各层的寻址输入端之间提供共用连接以及连接至I/O线等的单独连接等。460示出一个完整的存储模块,图中保留的金属片部分462的外表面提供了与外部电路、例如图1中的接口和控制电路14的接口的电连接。

一般考虑

本文叙述之存储系统具有数个特性使它特别适用于需要数据存储的便携式电器,例如数码相机(静态相片和/或录象),数码音乐录放机(例如MP3重放机),个人数码助理(PDA),便携式电话等。该存储系统能提供足够这些电器使用的数据存储容量,而且能以相对较低的成本生产。数据可写入存储器然后就永远被保存。这样,就可为便携式电器用的永久档案数据存储提供低成本高容量的存储装置(例如100MB到1GB)。

数据存储是由利用低廉的材料和工艺低成本生产的存储模块提供的。存储模块由许多层形成,每一层都具有交叉点存储阵列。许多层堆叠起来形成单一存储模块(例如即使仅仅在小型闪存(CompactFlash)卡的结构中,也可能有多达60层左右),这样就可使存储模块具有比单层存储数据容量大许多倍的容量。每一层都形成在诸如塑料或介质涂复的金属等价廉的柔性衬底上。这些比传统的单晶硅衬底要便宜得多,而且可以采用比较快速和低廉的制造工艺。每一层上形成的电路,包括交叉点存储阵列和关联的寻址电路,都设计成能用不复杂的工艺制造的简单结构。具体地说,存储阵列和寻址电路都按照置换二极管逻辑规范设计,以使二者可用相同的简单工艺制造。

存储模块的每一层有两组电极导线,分布在各自的层上,中间有半导体层隔开。电极布置成正交矩阵,并且在每对交叉点电极的交叉点上、在半导体材料中形成存储元件。半导体层可以低温加工,以适应于塑料衬底,半导体层可以是非晶硅材料,或由一种或多种有机半导体材料构成。在由半导体层隔开的电极层交叉点处,在两电极导线之间形成整流结。每一整流结可以认为是一个与熔丝串联的二极管,这种结形成存储阵列和置换二极管逻辑寻址电路的基础。寻址/复用电路的构造应是:制造后加电信号时选择的电路互连可以被切断或形成,从而在寻址方案所需的电极和地址线之间形成所选的二极管互连。

存储模块层用简单和低廉的加工工艺生产。通过使用柔性塑料或金属衬底,在所述层上制造电路时就可成卷的加工。寻址电路的二极管逻辑允许在同一衬底上使用制造存储阵列和寻址电路的同样工艺。接触片和导线也在衬底上形成,构成与电路的外部连接。多个层相互堆叠在一起。然后作出外部接点的印制线的图案,使之与存储模块层边沿的接触片形成电连接,于是存储模块就完成了。这些接点的印制线与各层上的电路相连,提供了对外部电路的连接。

存储模块每一层上包含的寻址电路减少了读出或写入每一层的存储元件所需的外部可存取的寻址线的数量。这样对于大存储容量模块而言,存储模块各层之间以及连接到外部电路都只需可管理数量的互连。例如,利用所述二极管逻辑寻址方案,100,000,000比特的存储阵列可用56条外部寻址线来寻址。还采用电源调线,其中,电源每次只加到一部分存储阵列上。这样可形成部分存储阵列寻址方案,在数据读出时也减少了阵列中的漏电流。

接口和控制电路与存储模块分开,例如作成传统的集成电路或电路形式。接口和控制电路包括产生加到存储模块上的寻址信号的寻址电路和读出存储数据的读出电路。读出方案是基于电流电平,而不是基于电荷。这就使读出电路能更容易地从存储模块远程读出数据。而且,数据存储基于存储元件熔丝烧断时的大电阻变化,这种变化提供了较大的感测信号。

存储模块的结构在维持本发明原则的同时可有多种可能的变化。在所述实施例中,每一层上制造一个存储阵列,然后多个层一层一层对准并相互堆叠在一起。每一层也可包含不止一个存储阵列,各层也可用诸如扇-折式等不同方式堆叠。在某些应用中,也可把多个电路层构建在一个衬底上。

在不背离后附的权利要求书定义的本发明的范围内的情况下,对本专业的技术人员,显而易见,利用本发明的原理时同时可对所述电路,结构,布局和加工工艺等作许多其它的改变。