CN1171296C - 不满填充受控折叠芯片连接(c4)集成电路封装的生产流水线 - Google Patents

不满填充受控折叠芯片连接(c4)集成电路封装的生产流水线 Download PDFInfo

- Publication number

- CN1171296C CN1171296C CNB008045658A CN00804565A CN1171296C CN 1171296 C CN1171296 C CN 1171296C CN B008045658 A CNB008045658 A CN B008045658A CN 00804565 A CN00804565 A CN 00804565A CN 1171296 C CN1171296 C CN 1171296C

- Authority

- CN

- China

- Prior art keywords

- substrate

- discontented

- packing material

- integrated circuit

- temperature

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the groups H01L21/18 - H01L21/326 or H10D48/04 - H10D48/07 e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

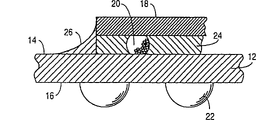

- H01L21/563—Encapsulation of active face of flip-chip device, e.g. underfilling or underencapsulation of flip-chip, encapsulation preform on chip or mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/16—Fillings or auxiliary members in containers or encapsulations, e.g. centering rings

- H01L23/18—Fillings characterised by the material, its physical or chemical properties, or its arrangement within the complete device

- H01L23/24—Fillings characterised by the material, its physical or chemical properties, or its arrangement within the complete device solid or gel at the normal operating temperature of the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/83909—Post-treatment of the layer connector or bonding area

- H01L2224/83951—Forming additional members, e.g. for reinforcing, fillet sealant

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01015—Phosphorus [P]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/156—Material

- H01L2924/15786—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2924/15787—Ceramics, e.g. crystalline carbides, nitrides or oxides

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Dispersion Chemistry (AREA)

- Wire Bonding (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/262,132 US6528345B1 (en) | 1999-03-03 | 1999-03-03 | Process line for underfilling a controlled collapse |

| US09/262,132 | 1999-03-03 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1344424A CN1344424A (zh) | 2002-04-10 |

| CN1171296C true CN1171296C (zh) | 2004-10-13 |

Family

ID=22996282

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB008045658A Expired - Fee Related CN1171296C (zh) | 1999-03-03 | 2000-02-08 | 不满填充受控折叠芯片连接(c4)集成电路封装的生产流水线 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US6528345B1 (enExample) |

| JP (1) | JP2002538624A (enExample) |

| KR (1) | KR100438991B1 (enExample) |

| CN (1) | CN1171296C (enExample) |

| AU (1) | AU2986100A (enExample) |

| MX (1) | MXPA01008581A (enExample) |

| WO (1) | WO2000052751A1 (enExample) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6833629B2 (en) | 2001-12-14 | 2004-12-21 | National Starch And Chemical Investment Holding Corporation | Dual cure B-stageable underfill for wafer level |

| US7238550B2 (en) * | 2002-02-26 | 2007-07-03 | Tandon Group Ltd. | Methods and apparatus for fabricating Chip-on-Board modules |

| US6798806B1 (en) * | 2002-09-03 | 2004-09-28 | Finisar Corporation | Hybrid mirror VCSELs |

| US7242097B2 (en) | 2003-06-30 | 2007-07-10 | Intel Corporation | Electromigration barrier layers for solder joints |

| US7026376B2 (en) * | 2003-06-30 | 2006-04-11 | Intel Corporation | Fluxing agent for underfill materials |

| US20050121310A1 (en) * | 2003-12-03 | 2005-06-09 | Intel Corporation | Method and substrate to control flow of underfill |

| JP5262045B2 (ja) * | 2007-09-27 | 2013-08-14 | 富士通セミコンダクター株式会社 | 電極の形成方法及び半導体装置の製造方法 |

| US7915732B2 (en) * | 2008-06-30 | 2011-03-29 | International Business Mahines Corporation | Production of integrated circuit chip packages prohibiting formation of micro solder balls |

Family Cites Families (43)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4322737A (en) | 1979-11-20 | 1982-03-30 | Intel Corporation | Integrated circuit micropackaging |

| JPS63239827A (ja) | 1987-03-27 | 1988-10-05 | Hitachi Ltd | 半導体装置 |

| EP0340492A3 (en) * | 1988-05-02 | 1990-07-04 | International Business Machines Corporation | Conformal sealing and interplanar encapsulation of electronic device structures |

| JPH0256941A (ja) | 1988-08-20 | 1990-02-26 | Matsushita Electric Works Ltd | 半導体素子の封止方法 |

| JPH0340458A (ja) | 1989-07-07 | 1991-02-21 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| JPH0639563B2 (ja) | 1989-12-15 | 1994-05-25 | 株式会社日立製作所 | 半導体装置の製法 |

| US5371325A (en) | 1992-10-30 | 1994-12-06 | At&T Corp. | Insulation system for magnetic devices |

| US5321583A (en) | 1992-12-02 | 1994-06-14 | Intel Corporation | Electrically conductive interposer and array package concept for interconnecting to a circuit board |

| US5371328A (en) | 1993-08-20 | 1994-12-06 | International Business Machines Corporation | Component rework |

| JP2774436B2 (ja) | 1993-09-07 | 1998-07-09 | リンナイ株式会社 | 多孔質体 |

| US5539153A (en) | 1994-08-08 | 1996-07-23 | Hewlett-Packard Company | Method of bumping substrates by contained paste deposition |

| JP3233535B2 (ja) | 1994-08-15 | 2001-11-26 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JPH08153830A (ja) | 1994-11-29 | 1996-06-11 | Toshiba Corp | 半導体装置およびその製造方法 |

| US5864178A (en) | 1995-01-12 | 1999-01-26 | Kabushiki Kaisha Toshiba | Semiconductor device with improved encapsulating resin |

| US5811317A (en) | 1995-08-25 | 1998-09-22 | Texas Instruments Incorporated | Process for reflow bonding a semiconductor die to a substrate and the product produced by the product |

| EP0778616A3 (en) | 1995-12-05 | 1999-03-31 | Lucent Technologies Inc. | Method of packaging devices with a gel medium confined by a rim member |

| US5766982A (en) | 1996-03-07 | 1998-06-16 | Micron Technology, Inc. | Method and apparatus for underfill of bumped or raised die |

| US5751556A (en) | 1996-03-29 | 1998-05-12 | Intel Corporation | Method and apparatus for reducing warpage of an assembly substrate |

| JP3235454B2 (ja) | 1996-03-29 | 2001-12-04 | 松下電器産業株式会社 | 電子部品の接合方法 |

| US5821456A (en) | 1996-05-01 | 1998-10-13 | Motorola, Inc. | Microelectronic assembly including a decomposable encapsulant, and method for forming and reworking same |

| JP2891184B2 (ja) * | 1996-06-13 | 1999-05-17 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| JPH1055832A (ja) | 1996-08-08 | 1998-02-24 | Yazaki Corp | 圧接端子 |

| US5804771A (en) | 1996-09-26 | 1998-09-08 | Intel Corporation | Organic substrate (PCB) slip plane "stress deflector" for flip chip deivces |

| JP2848357B2 (ja) | 1996-10-02 | 1999-01-20 | 日本電気株式会社 | 半導体装置の実装方法およびその実装構造 |

| US5942805A (en) | 1996-12-20 | 1999-08-24 | Intel Corporation | Fiducial for aligning an integrated circuit die |

| US5891753A (en) | 1997-01-24 | 1999-04-06 | Micron Technology, Inc. | Method and apparatus for packaging flip chip bare die on printed circuit boards |

| US5990552A (en) | 1997-02-07 | 1999-11-23 | Intel Corporation | Apparatus for attaching a heat sink to the back side of a flip chip package |

| US5815372A (en) | 1997-03-25 | 1998-09-29 | Intel Corporation | Packaging multiple dies on a ball grid array substrate |

| US6104093A (en) | 1997-04-24 | 2000-08-15 | International Business Machines Corporation | Thermally enhanced and mechanically balanced flip chip package and method of forming |

| JPH1154884A (ja) | 1997-08-06 | 1999-02-26 | Nec Corp | 半導体装置の実装構造 |

| US5919329A (en) | 1997-10-14 | 1999-07-06 | Gore Enterprise Holdings, Inc. | Method for assembling an integrated circuit chip package having at least one semiconductor device |

| US6049122A (en) | 1997-10-16 | 2000-04-11 | Fujitsu Limited | Flip chip mounting substrate with resin filled between substrate and semiconductor chip |

| US5998242A (en) | 1997-10-27 | 1999-12-07 | Lsi Logic Corporation | Vacuum assisted underfill process and apparatus for semiconductor package fabrication |

| US5917702A (en) | 1997-11-26 | 1999-06-29 | Intel Corporation | Corner heat sink which encloses an integrated circuit of a ball grid array integrated circuit package |

| US6049124A (en) | 1997-12-10 | 2000-04-11 | Intel Corporation | Semiconductor package |

| US5936304A (en) | 1997-12-10 | 1999-08-10 | Intel Corporation | C4 package die backside coating |

| US5965937A (en) | 1997-12-15 | 1999-10-12 | Intel Corporation | Thermal interface attach mechanism for electrical packages |

| US5920120A (en) | 1997-12-19 | 1999-07-06 | Intel Corporation | Assembly for dissipatating heat from a semiconductor chip wherein a stress on the semiconductor chip due to a thermally conductive member is partially relieved |

| US5991161A (en) | 1997-12-19 | 1999-11-23 | Intel Corporation | Multi-chip land grid array carrier |

| US6201301B1 (en) | 1998-01-21 | 2001-03-13 | Lsi Logic Corporation | Low cost thermally enhanced flip chip BGA |

| US5953814A (en) * | 1998-02-27 | 1999-09-21 | Delco Electronics Corp. | Process for producing flip chip circuit board assembly exhibiting enhanced reliability |

| US6057381A (en) * | 1998-07-02 | 2000-05-02 | National Starch And Chemical Investment Holding Corporation | Method of making an electronic component using reworkable underfill encapsulants |

| US6238948B1 (en) | 1999-03-03 | 2001-05-29 | Intel Corporation | Controlled collapse chip connection (C4) integrated circuit package that has a fillet which seals an underfill material |

-

1999

- 1999-03-03 US US09/262,132 patent/US6528345B1/en not_active Expired - Fee Related

-

2000

- 2000-02-08 WO PCT/US2000/003243 patent/WO2000052751A1/en not_active Ceased

- 2000-02-08 JP JP2000603088A patent/JP2002538624A/ja active Pending

- 2000-02-08 CN CNB008045658A patent/CN1171296C/zh not_active Expired - Fee Related

- 2000-02-08 AU AU29861/00A patent/AU2986100A/en not_active Abandoned

- 2000-02-08 KR KR10-2001-7011229A patent/KR100438991B1/ko not_active Expired - Fee Related

- 2000-02-08 MX MXPA01008581A patent/MXPA01008581A/es not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| AU2986100A (en) | 2000-09-21 |

| KR20020005612A (ko) | 2002-01-17 |

| MXPA01008581A (es) | 2002-04-24 |

| JP2002538624A (ja) | 2002-11-12 |

| WO2000052751A1 (en) | 2000-09-08 |

| CN1344424A (zh) | 2002-04-10 |

| US6528345B1 (en) | 2003-03-04 |

| KR100438991B1 (ko) | 2004-07-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6610559B2 (en) | Integrated void-free process for assembling a solder bumped chip | |

| CN1165979C (zh) | 集成电路封装方法 | |

| US7736950B2 (en) | Flip chip interconnection | |

| US20110287582A1 (en) | Method of forming a semiconductor device | |

| JPH08340064A (ja) | 再加工可能な電子デバイス及び形成方法 | |

| CN1191627C (zh) | 具有二种不同的底层填充材料的可控崩塌芯片连接(c4)集成电路封装件 | |

| TW201426928A (zh) | 具有在封裝間之電絕緣材料之層疊封裝(PoP) | |

| CN1157782C (zh) | 利用加热到部分凝胶态的底层填料底层填充控制熔塌芯片连接(c4)集成电路封装的方法 | |

| CN1171296C (zh) | 不满填充受控折叠芯片连接(c4)集成电路封装的生产流水线 | |

| JP2002270642A (ja) | 半導体装置の製造方法 | |

| JP2004282042A (ja) | 半導体デバイスのアセンブリ法 | |

| TWI478257B (zh) | 封裝結構及封裝製程 | |

| JP3309832B2 (ja) | 電子部品の接続構造及び接続方法 | |

| JPH1098077A (ja) | 半導体装置の製造方法 | |

| CN101996974B (zh) | 球栅阵列印刷电路板、其封装结构及其工艺 | |

| CN101989554B (zh) | 封装结构及封装工艺 | |

| KR100498675B1 (ko) | 두 가지 다른 하부 충전 재료를 갖는 붕괴 제어형 칩접속(c4) 집적회로 패키지 | |

| CN104347547A (zh) | 半导体封装件及其的制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20041013 Termination date: 20150208 |

|

| EXPY | Termination of patent right or utility model |