CN1071490C - 形成钨柱塞的方法 - Google Patents

形成钨柱塞的方法 Download PDFInfo

- Publication number

- CN1071490C CN1071490C CN95119463A CN95119463A CN1071490C CN 1071490 C CN1071490 C CN 1071490C CN 95119463 A CN95119463 A CN 95119463A CN 95119463 A CN95119463 A CN 95119463A CN 1071490 C CN1071490 C CN 1071490C

- Authority

- CN

- China

- Prior art keywords

- layer

- hole

- tungsten

- interlayer dielectric

- plunger

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims abstract description 25

- 239000004065 semiconductor Substances 0.000 title description 2

- 239000010410 layer Substances 0.000 claims abstract description 132

- 239000011229 interlayer Substances 0.000 claims abstract description 67

- 229910052721 tungsten Inorganic materials 0.000 claims abstract description 47

- 239000010937 tungsten Substances 0.000 claims abstract description 47

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims abstract description 46

- 229920002120 photoresistant polymer Polymers 0.000 claims abstract description 42

- 239000004020 conductor Substances 0.000 claims abstract description 19

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 55

- 230000012010 growth Effects 0.000 claims description 24

- 230000015572 biosynthetic process Effects 0.000 claims description 23

- 230000007797 corrosion Effects 0.000 claims description 7

- 238000005260 corrosion Methods 0.000 claims description 7

- 238000001259 photo etching Methods 0.000 claims description 6

- 238000009792 diffusion process Methods 0.000 claims description 5

- 239000000758 substrate Substances 0.000 claims description 5

- 150000003657 tungsten Chemical class 0.000 claims 1

- 239000012790 adhesive layer Substances 0.000 abstract 1

- 238000005530 etching Methods 0.000 abstract 1

- 230000000149 penetrating effect Effects 0.000 abstract 1

- 238000005516 engineering process Methods 0.000 description 22

- 239000011148 porous material Substances 0.000 description 14

- 239000010936 titanium Substances 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- 230000008569 process Effects 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 3

- 238000001020 plasma etching Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 229910052801 chlorine Inorganic materials 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- 230000008602 contraction Effects 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 239000000428 dust Substances 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 208000005189 Embolism Diseases 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 229910000765 intermetallic Inorganic materials 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000006386 neutralization reaction Methods 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

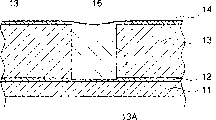

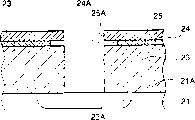

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76853—Barrier, adhesion or liner layers characterized by particular after-treatment steps

- H01L21/76865—Selective removal of parts of the layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76805—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics the opening being a via or contact hole penetrating the underlying conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electrodes Of Semiconductors (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP6316188A JP2758841B2 (ja) | 1994-12-20 | 1994-12-20 | 半導体装置の製造方法 |

| JP316188/1994 | 1994-12-20 | ||

| JP316188/94 | 1994-12-20 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1135094A CN1135094A (zh) | 1996-11-06 |

| CN1071490C true CN1071490C (zh) | 2001-09-19 |

Family

ID=18074282

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN95119463A Expired - Fee Related CN1071490C (zh) | 1994-12-20 | 1995-12-20 | 形成钨柱塞的方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US5893749A (cg-RX-API-DMAC7.html) |

| JP (1) | JP2758841B2 (cg-RX-API-DMAC7.html) |

| KR (1) | KR100228565B1 (cg-RX-API-DMAC7.html) |

| CN (1) | CN1071490C (cg-RX-API-DMAC7.html) |

| TW (1) | TW307021B (cg-RX-API-DMAC7.html) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10172969A (ja) * | 1996-12-06 | 1998-06-26 | Nec Corp | 半導体装置の製造方法 |

| TW398065B (en) * | 1997-07-16 | 2000-07-11 | United Microelectronics Corp | The manufacturing method of the integrated circuit metal wiring |

| TW362261B (en) * | 1997-12-13 | 1999-06-21 | United Microelectronics Corp | Manufacturing method of contact plugs |

| US6319822B1 (en) * | 1998-10-01 | 2001-11-20 | Taiwan Semiconductor Manufacturing Company | Process for forming an integrated contact or via |

| US6146991A (en) * | 1999-09-03 | 2000-11-14 | Taiwan Semiconductor Manufacturing Company | Barrier metal composite layer featuring a thin plasma vapor deposited titanium nitride capping layer |

| EP1612891B1 (en) * | 2003-03-31 | 2011-11-30 | Sumitomo Electric Industries, Ltd. | Anisotropic electrically conductive film and method of producing the same |

| US6989105B2 (en) * | 2003-06-27 | 2006-01-24 | International Business Machines Corporation | Detection of hardmask removal using a selective etch |

| US7091085B2 (en) * | 2003-11-14 | 2006-08-15 | Micron Technology, Inc. | Reduced cell-to-cell shorting for memory arrays |

| CN100395451C (zh) * | 2006-07-27 | 2008-06-18 | 安东石油技术(集团)有限公司 | 抽油泵柱塞的制造方法 |

| CN112992826B (zh) * | 2021-02-01 | 2025-10-03 | 日月光半导体制造股份有限公司 | 半导体结构及其制造方法 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4822753A (en) * | 1988-05-09 | 1989-04-18 | Motorola, Inc. | Method for making a w/tin contact |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4960732A (en) * | 1987-02-19 | 1990-10-02 | Advanced Micro Devices, Inc. | Contact plug and interconnect employing a barrier lining and a backfilled conductor material |

| US5167760A (en) * | 1989-11-14 | 1992-12-01 | Intel Corporation | Etchback process for tungsten contact/via filling |

| US5225372A (en) * | 1990-12-24 | 1993-07-06 | Motorola, Inc. | Method of making a semiconductor device having an improved metallization structure |

| JPH04293233A (ja) * | 1991-03-22 | 1992-10-16 | Sony Corp | メタルプラグの形成方法 |

| JP3116432B2 (ja) * | 1991-06-28 | 2000-12-11 | ソニー株式会社 | 半導体装置の製造方法 |

| JPH0530426A (ja) * | 1991-07-25 | 1993-02-05 | Matsushita Electric Ind Co Ltd | 文字表示装置 |

| JP2655213B2 (ja) * | 1991-10-14 | 1997-09-17 | 三菱電機株式会社 | 半導体装置の配線接続構造およびその製造方法 |

| JPH05166944A (ja) * | 1991-12-19 | 1993-07-02 | Sony Corp | 半導体装置の配線形成方法 |

-

1994

- 1994-12-20 JP JP6316188A patent/JP2758841B2/ja not_active Expired - Lifetime

-

1995

- 1995-12-19 TW TW084113544A patent/TW307021B/zh active

- 1995-12-20 CN CN95119463A patent/CN1071490C/zh not_active Expired - Fee Related

- 1995-12-20 US US08/575,478 patent/US5893749A/en not_active Expired - Fee Related

- 1995-12-20 KR KR1019950052831A patent/KR100228565B1/ko not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4822753A (en) * | 1988-05-09 | 1989-04-18 | Motorola, Inc. | Method for making a w/tin contact |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2758841B2 (ja) | 1998-05-28 |

| JPH08172058A (ja) | 1996-07-02 |

| KR100228565B1 (ko) | 1999-11-01 |

| US5893749A (en) | 1999-04-13 |

| CN1135094A (zh) | 1996-11-06 |

| TW307021B (cg-RX-API-DMAC7.html) | 1997-06-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3925780B2 (ja) | 触媒及び化学気相蒸着法を用いて銅配線及び薄膜を形成する方法 | |

| CN1111908C (zh) | 半导体器件 | |

| KR100337580B1 (ko) | 반도체장치및그제조방법 | |

| KR100238698B1 (ko) | 다층배선의 형성방법 | |

| CN1477695A (zh) | 半导体器件的制造方法 | |

| CN1071490C (zh) | 形成钨柱塞的方法 | |

| CN1596466A (zh) | 通过在多孔材料上的sic∶h沉积提高金属阻挡性能 | |

| CN1599028A (zh) | 金属-绝缘体-金属电容器及互连结构 | |

| EP1064674A2 (en) | A method of manufacturing an electronic device comprising two layers of organic-containing material | |

| JPH04142061A (ja) | タングステンプラグの形成方法 | |

| CN1258097A (zh) | 形成双镶嵌布线的方法 | |

| CN1230020A (zh) | 浅沟槽隔离方法 | |

| US6022800A (en) | Method of forming barrier layer for tungsten plugs in interlayer dielectrics | |

| CN109585363A (zh) | 一种半导体器件的形成方法及半导体器件 | |

| KR950010858B1 (ko) | 반도체 소자의 금속콘택 형성방법 | |

| CN1574284A (zh) | 复合低介电常数的介电结构 | |

| JP2004525504A (ja) | 低誘電率技術における銅のバイア | |

| CN2793918Y (zh) | 半导体装置 | |

| US7189638B2 (en) | Method for manufacturing metal structure using trench | |

| JP2704120B2 (ja) | 半導体装置の製造方法 | |

| JPH07169834A (ja) | 層間接続孔の埋め込み方法 | |

| CN1042473C (zh) | 形成半导体器件接触塞的方法 | |

| CN1897267A (zh) | 半导体装置及其制造方法 | |

| JPH06268077A (ja) | 半導体装置の製造方法 | |

| JPH07111263A (ja) | Wプラグ形成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C19 | Lapse of patent right due to non-payment of the annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |