CN1071490C - 形成钨柱塞的方法 - Google Patents

形成钨柱塞的方法 Download PDFInfo

- Publication number

- CN1071490C CN1071490C CN95119463A CN95119463A CN1071490C CN 1071490 C CN1071490 C CN 1071490C CN 95119463 A CN95119463 A CN 95119463A CN 95119463 A CN95119463 A CN 95119463A CN 1071490 C CN1071490 C CN 1071490C

- Authority

- CN

- China

- Prior art keywords

- layer

- hole

- tungsten

- opening

- interlayer dielectric

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims abstract description 25

- 239000004065 semiconductor Substances 0.000 title description 2

- 239000010410 layer Substances 0.000 claims abstract description 135

- 239000011229 interlayer Substances 0.000 claims abstract description 67

- 229910052721 tungsten Inorganic materials 0.000 claims abstract description 47

- 239000010937 tungsten Substances 0.000 claims abstract description 47

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims abstract description 46

- 229920002120 photoresistant polymer Polymers 0.000 claims abstract description 45

- 239000004020 conductor Substances 0.000 claims abstract description 19

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 55

- 230000012010 growth Effects 0.000 claims description 24

- 230000015572 biosynthetic process Effects 0.000 claims description 23

- 230000007797 corrosion Effects 0.000 claims description 7

- 238000005260 corrosion Methods 0.000 claims description 7

- 238000001259 photo etching Methods 0.000 claims description 6

- 238000009792 diffusion process Methods 0.000 claims description 5

- 239000000758 substrate Substances 0.000 claims description 5

- 150000003657 tungsten Chemical class 0.000 claims 1

- 239000012212 insulator Substances 0.000 abstract 5

- 238000005530 etching Methods 0.000 abstract 1

- 238000005516 engineering process Methods 0.000 description 22

- 239000011148 porous material Substances 0.000 description 14

- 239000010936 titanium Substances 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- 230000008569 process Effects 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 3

- 238000001020 plasma etching Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 229910052801 chlorine Inorganic materials 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- 230000008602 contraction Effects 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 239000000428 dust Substances 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 208000005189 Embolism Diseases 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 229910000765 intermetallic Inorganic materials 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000006386 neutralization reaction Methods 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76853—Barrier, adhesion or liner layers characterized by particular after-treatment steps

- H01L21/76865—Selective removal of parts of the layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76805—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics the opening being a via or contact hole penetrating the underlying conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

在互连被层间绝缘膜所绝缘的上层布线导体和下层布线导体的钨柱塞的形成方法中,在形成于下层布线导体上的层间绝缘膜上形成粘附层。在粘附层上淀积光刻胶层,并在其中形成开口。以其作为掩模,通过各向同性腐蚀,选择性去除缘向外收缩的开口。形成贯通层间绝缘膜的孔,露出下层布线导体,在层间绝缘膜的孔内形成钨层,从而形成填充在层间绝缘膜的孔内的钨。

Description

本发明涉及半导体器件的制造方法,特别是形成孔填充柱塞的方法。

作为填充细小接触孔或通孔的技术,通过覆盖WCVD(钨化学汽相淀积)来形成钨(W)柱塞已经付诸实施了,这种技术在台阶覆盖和降低电阻方面是优异的。这种覆盖WCVD方法是把W层充入形成于层间绝缘膜内的通孔中,从而形成柱塞。

参看图1A~1C,这里的剖面示意图展示了根据传统的覆盖WCVD工艺形成通孔填充W柱塞的工艺。如图1A所示,在形成于下层布线Al导体31之上的第一TiN(氮化钛)膜上形成层间绝缘膜33,通过传统的光刻法和各向异性干式腐蚀,贯通层间绝缘膜33形成通孔33A,以致部分的第一TiN膜32暴露于通孔33A的底部。

接着如图1B所示,通过溅射法淀积第二TiN膜34,从而覆盖包括通孔33A的底部和侧壁在内的整个表面。此外,在通孔33A和层间绝缘膜33的表面淀积W(钨)层36,随着对淀积的W层36深腐蚀,以清除填充在通孔33A内的W层之外的W层36被去除。因而,如图1C所示,在通孔33A中形成由W层36构成的W栓塞。这种由W层36构成的W柱塞用来对被层间绝缘膜33使其相互绝缘的下层布线Al导体31和未示出的上层布线Al导体进行内连接。

在上述传统工艺中,通常通过溅射来形成TiN膜作为粘附层。在此溅射工艺中,在通孔开口边缘处TiN膜34的生成速率高于其它区域的生长速度。结果,已由实验证实,如图1B和1C所示,TiN膜34围绕通孔33A的开口边缘有一个伸出部分34A。如果用来覆盖WCVD工艺在TiN膜34具有伸出部分34A的情况下淀积W层,则淀积的W层36会影响TiN膜34的伸出部分34A的形状,结果在通孔33A内充入的W层36中会产生孔隙39。其原因可考虑如下,由于TiN膜34的伸出部分34A从环绕通孔33A的开口的边缘向内突出,当淀积W层36时,TiN膜34的伸出部分34A成为生长核,因而W层35从通孔33A的开口环绕处开始生长,以致在整个通孔完全被W层36充满之前,通孔33A的开口就被封闭了。

为了避免溅射淀积的TiN膜从通孔33A的开口边缘形成伸出部分,已经考虑通过溅射在层间绝缘膜33上形成第二TiN膜34,如图2所示,然后采用传统的光刻法和各向异性干式腐蚀,贯穿第二TiN膜34和层间绝缘膜33形成通孔33A,之后再实施覆盖WCVD工艺。但是,在此工艺中,由于TiN膜34的内边缘34A沿通孔33A的开口边缘露出,在W层36淀积时,TiN膜34内边缘34B成为生长核。结果,与图1C所示类似地在通孔33A中所填充的W层36中产生气孔39。这也已由实验所证实。

如果在通孔33A内填充的W层36中产生了气孔39,如图1C和2所示,则往往易于产生布线缺陷如断路。为了避免这种问题,必须避免产生气孔。为了避免产生气孔,必须抑制沿通孔33A的开口边缘的W层生长,以使W层从通孔底部均匀地生长直至充满整个通孔。

因此,本发明的目的是提供一种可克服传统方法的上述缺点的孔填充柱塞的形成方法。

本发明的另一目的是提供一种孔填充柱塞的形成方法,能避免在孔填充柱塞中产生气孔,从而使连续缺陷的发生减至最少。

根据本发明,提供一种形成钨柱塞的方法,由该柱塞互连被层间绝缘膜所相互绝缘的上层导体和下层导体区,该方法包括以下步骤:

在下层导体区上形成层间绝缘膜;

在层间绝缘膜上形成粘附层;

在粘附层上形成光刻胶层;

在光刻胶层中形成开口,以便制备将在层间绝缘膜形成孔用的有开口的光刻胶层掩模层;

选择性去除粘附层,形成与光刻胶层中形成的开口对应的开口,而且从环绕形成在光刻胶层中的开口进一步去除形成在生长钨时将会成为生长核的粘附层。

形成贯通层间绝缘膜的孔,以使下层导体区在孔的底部露出以及

把钨层填充入层间绝缘膜的孔内,从而在层间绝缘膜的孔内形成钨填充。

在一个实施例中,通过腐蚀选择性去除粘附层。更具体讲,这种腐蚀是使用其中形成有开口的光刻胶层作为掩模的各向同性腐蚀,以使粘附层中形成的开口从刻胶层中形成的开口边缘向外收缩。

此外,把钨层直接填充入层间绝缘膜的孔内。另外,也可以在把钨填充入层间绝缘膜的孔内之前,在层间绝缘膜的孔的侧壁和底部形成第二粘附层,随后,把钨层填充入层间绝缘膜的孔内。这些粘附层由例如氮化钛膜构成。

由上述可见,在本发明的方法中,从形成于层间绝缘层中的孔边缘,把在生长钨时将会成为生长核的粘附层去除。由此,可使钨层均匀地填充入层间绝缘层的整个孔内。

通过参考附图对本发明优选实施例的以下说明,可清楚地了解本发明的上述目的和其它目的、特征和优点。

图1A~1C是说明按照传统的覆盖WCVD工艺形成通孔填充W柱塞的工艺的剖面示意图。

图2是展示改进的传统覆WCVD工艺的剖面示意图。

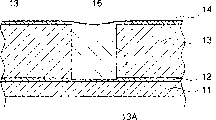

图3A~3D是根据本发明的第一实施例形成通孔填充W柱塞的工艺剖面示意图。

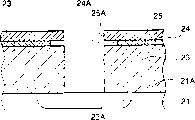

图4A~4C是根据本发明的第二实施例形成接触孔填充W柱塞的工艺剖面示意图。

图5是本发明工艺优点的曲线图。

如上所述,图3A~3D展示了本发明工艺的第一实施例,图4A~4C展示了本发明工艺的第二实施例。

如图3A~3D和图4A~4C所示的本发明工艺包括以下步骤:形成粘附层,形成光刻胶膜,形成掩模,粘附层构图,形成孔和填充钨,其目的在于形成W(钨)柱塞,互连被层间绝缘膜所相互分隔的两层布线区。

在粘附层形成步骤中,在层间绝缘绝层13或24上淀积粘附层14或24。

在光刻胶膜形成步骤中,在粘附层14或24上形成光刻胶层13或23。

在掩模形成步骤中,在光刻胶层13或23中形成开口15A或25A。由此构成用于在层间绝缘层13或24中形成孔的掩模。它由其中形成有开口15A或25A的光刻胶层13或23所构成。

在粘附层构形步骤中,对粘附层14或24选择地去除和构形,以便形成与在光刻胶层形成的开口对应的开口,而且从环绕形成于光刻胶层中的开口边缘(即从在层间绝缘层已有的形成的孔的开口边缘)进一步去除在已有的的孔内生长钨是将以其它方式成为生长核的粘附层。

在孔形成步骤中,使用光刻胶膜15或25作为掩模,形成孔13A或23A使其贯通层间绝缘膜13或23。

在钨填充步骤中,在形成于层间绝缘膜13或23中的孔13A或23A中积W层16或26,其目的在于形成W。

更具体地,在粘附层构形步骤中,以光刻胶膜15或25为掩模,对粘附层14或24选择地去除和构形。尤其是,以其中形成有开口15A和25A的光刻胶层15或25为掩模,通过各向同性腐蚀选择性去除粘附层14或24,以使形成于粘附层14或24中的开口14A或24A从形成于光刻胶层15或25中的开口15A或25A的边缘向外收缩。

在钨填充步骤中,把钨层16或26直接填充入层间绝缘膜13或23的孔13A或23A中。另外,也可以在把钨层16或26填充入层间绝缘膜13或23的孔13A或23A中之前,在层间绝缘膜13或23的孔13A或23A的侧壁和底部形成第二粘附层(Ti膜27,第二TiN膜28,)然后把钨层16或26填充入层间绝缘膜的孔内。

例如粘附层14或24由氮化钛膜构成。

接着,参考附图3A~3D,将详细说明按本发明第一实施例的形式填充W柱塞的工艺。

如图3A所示,在下层布线Al导体11上,形成例如厚500埃的第一粘附TiN层12,在第一粘附TiN层12上再形成层间绝缘膜13。

然后,通过溅射法在层间绝缘膜13上形成例如厚500埃的第二粘附TiN层14(粘附层形成步骤)。

在第二TiN膜14上淀积光刻胶膜15(光刻胶膜形成步骤),实施传统的光刻法在光刻胶膜15形成开口15A,形成用于在层间绝缘膜13中形成孔的掩模,如图3A所示(掩模形成步骤)。

然后,如图3B所示,进行各向同性腐蚀,选择地去除第二TiN膜14,从而形成半径比光刻胶膜15中开口15A半径约大500埃的开口14A(粘附层构形步骤)。在此去除钨填充步骤中在贯通层间绝缘层形成的孔中生长钨时,将会成为W生长核的TiN层14。例如,使用氯气进行各向同性腐蚀用以选择地去除TiN膜14。

接着以光刻胶膜15为掩模,采用各向异性腐蚀例如反应离子腐蚀选择地去除层间绝缘层13直至露出位于下层布线导体11上的第一TiN膜12,如图3C所示。由此,形成贯通层间绝缘层13的通孔13A(孔形成步骤)。在此工艺中,例如使用CHF3作为腐蚀气体。由此形成的通孔13A的直径基本与光刻胶膜15的开口15A的直径相同。

形成通孔13A之后,去除光刻胶膜15。然后,采用覆盖WCVD使W层16在通孔13A及其周围生长(钨填充步骤)。

在位于下层布线导体11上的第一TiN膜12上和位于层间绝缘膜13上的第二TiN膜14上,TiN膜成为W生长核,因此W层16的生长速率高于通孔的侧壁生长速度。此外,在第一实施例中,由于第二TiN膜14的开口14A边缘从通孔13A的开口边缘向外收缩500埃,所以围绕通孔13A的开口不存在成为W生长核的TiN膜14。因此,围绕通孔13A开口的W膜16生长被抑制,以致W层16从通孔13A的底部向整个通孔13A生长。换言之,不可能由于围绕通孔13A开口的W层16快速生长,而导致在通孔整体被W层16完全填充成充满之前的初期使通孔13A的开口被封闭。所以,在填充于通孔13的W层16中不会产生气孔。

W层生长之后,如图3D所示,对W层深腐蚀直至露出TiN膜14,以使W层16仅留在通孔13A中和留在层间绝缘膜13的表面上延续到露出的TiN膜14这种留下的W层16形成了W柱塞。

由于W柱塞中不存在气孔,所以可提高可靠性。如果W柱塞中存在气孔,经常会发生断路,这是因为布线导体塌陷进气孔,或者因为由气孔中残留的气体膨胀而导致W柱塞的上部破裂及消失。此第一实施例能使由于上述原因而造成的断路减至零。

顺便提及,在上述工艺中,TiN层12不仅起粘附层的作用,而且还起阻挡金属的作用,用于防止下层布线Al导体11与W层16之间反应。

接着,参考图4A~4C,将详细说明本发明第二实施例的形成对扩散区和布线导体进行内连接的接触孔填充W柱塞的工艺。

如图4A所示,在其主表面中形成有扩散区21A的硅衬底21上形成层间绝缘膜23。采用溅射法在层间绝缘膜23上形成厚约500埃的第一粘附TiN膜24(粘附层形成步骤)。

然后,在第一TiN膜24上形成光刻胶膜25(光刻胶膜形成步骤),用传统的光刻法,在光刻胶膜25中形成开口25A,以便形成用来在层间绝缘膜23中形成孔的掩模,如图4A所示(掩模形成步骤)。

而且,以光刻胶膜25为掩模进行各向同性腐蚀,选择性去除第二TiN膜以便形成半径比光刻胶膜25的开口25A的半径约大500埃的开口24A。在此去除,钨填充步骤中在贯通层间绝缘层的孔中生长钨时,将会成为W生长核的TiN层24(粘附层造型步骤)。例如,使用氯气通过等离子腐蚀进行各向同性腐蚀选择地去除TiN膜14。

接着还以光刻胶膜25为掩模,通过各向异性腐蚀例如反应离子腐蚀,去除层间绝缘层23,直至衬底21上的扩散区21A露出。由此,贯穿层间绝缘层23形成接触孔23A(孔形成步骤)。如此形成的接触孔23A的直径与光刻膜25的开口25A的直径基本上相同。

在第二实施例中,在层间绝缘膜23的接触孔23A的侧壁和底部设置粘附层,这与第一实施例不同。为此目的,如图4B所示,在仍保留光刻胶膜25的条件下,通过溅射形成Ti(钛)膜27,作为在扩散区21A中与硅衬底21的接触金属,通过溅射形成第二TiN膜28,作为防止硅衬底与钨(W)之间反应的阻挡金属。在此工艺中,在光刻胶膜25和开口25A的侧表面上形成Ti膜27TiN膜28。但是,其中形成有Ti膜27和TiN膜28伸出区域位于光刻胶膜25的开口25A的附近。另一方面,由于TiN膜24的开口边缘在层间绝缘层23的孔23A的开口边缘附近,向外收缩,所以不存在会成为W生长核的TiN膜的伸出部分。例如,在接触孔23A的底部,Ti膜27的厚度为300埃数量级,TiN膜28的厚度为500埃数量级。之后,同时去除光刻胶膜25和位于光刻胶25之上的Ti膜27和TiN膜28。

然后,与第一实施例类似,进行覆盖WCVD工艺,以使W层26在接触孔23A及其周围生长(钨填充步骤)。这里,在接触孔23之内的第二TiN膜28上和层间绝缘膜23之上的第一TiN膜24上,W层的生长处于其它区域。它在第二实施例中,由于第二TiN膜24的开口24A边缘从接触孔23A的开口边缘向外收缩500埃,所以填充在接触孔23A内的W层26不会产生气孔,这与第一实施例相同。

W层生长之后,如图4C所示,对W层深腐蚀直至TiN膜24露出,所使W层26仅留在接触孔23A内并在层间绝缘膜23表面上延续露出的TiN膜24。此留存的W层26形成W柱塞。由于W柱塞中不存在气孔,因而可提高可靠性,比第二实施例可使由气孔造成的断路减至零,这与第一实施例相同。

在此第二实施例,如果在形成于层间绝缘膜中的孔的侧壁和底部上形成粘附和阻挡层,则可以自由地选择填充W层的方法,并可自由地选择由W柱塞所连接的物体。

参看图5,这里展示了从第一和第二实施例中层间绝缘膜13和23中的孔13A和23A的开口边缘TiN膜的收缩量,气孔量和通孔导电性的百分比缺陷之间的关系。从图5可见,如果在柱塞中不产生气孔可以极大地改善布线的可靠性。例如,在通孔直径为0.6μm的情况下,形成在层间绝缘膜上的TiN膜的开口边缘从形成在层间绝缘膜中的孔的开口边缘向外收缩量最好不少于400埃左右。

在上述实施例中,形成了W柱塞。但是,根据本发明的构思,可以形成由除W之外的金属构成的柱塞,或者由选自包括W和其它金属在内的一组金属中的金属化合物的构成。

结合特定实施例已展示和说明了本发明。但是,应该注意,本发明并不限于已说明的结构的细节,而可以做出各种变化和改进但均在权利要求书中要求保护中的范围之内。

Claims (9)

1.一种形成钨柱塞的方法,该钨柱塞互连被层间绝缘膜所相互绝缘的上层导体和下层导电区,包括以下步骤:

在所述下层导电区上形成所述层间绝缘膜;

在所述层间绝缘膜上形成粘附层;

在所述粘附层上形成光刻胶层;

在所述光刻胶层中形成开口,由此用有开口的所述光刻膜层作掩膜层,用于在所述层间绝缘膜中形成孔;

选择性去除所述粘附层,形成与形成在所述光刻胶层中的所述开口对应的开口,而且从形成在所述光刻胶层中的所述开口的边缘周围进一步去除在钨生长时否则将会成为生长核的所述粘附层;

形成贯通所述层间绝缘膜的孔,以使所述下层导电区在所述孔的底部露出;

把钨填充入所述层间绝缘膜的所述孔内,从而形成填充所述层间绝缘膜的所述孔的钨。

2.根据权利要求1所述形成钨柱塞的方法,其特征是通过腐蚀来选择性去除所述粘附层。

3.根据权利要求1所述形成钨柱塞的方法,其特征是以其中形成有所述开口的所述光刻胶层为掩模,通过各向同性腐蚀,选择性去除所述粘附层以使形成于所述粘附层中的所述开口从形成于所述光刻胶层中的所述开口的边缘向外收缩。

4.根据权利要求1所述形成钨柱塞的方法,其特征是所述钨层直接填充所述层间绝缘膜的所述孔内。

5.根据权利要求4所述形成钨柱塞的方法,其特征是所述第一粘附层由氮化钛膜构成。

6.根据权利要求1所述形成钨柱塞的方法,其特征是在所述钨层填充入所述层间绝缘膜的所述孔内之前,在所述层间绝缘膜的所述孔的侧壁和底部上形成第二粘附层,之后把所述钨层填充入所述层间绝级膜的所述孔。

7.根据权利要求6所述形成钨柱塞的方法,其特征是所述第一和第二粘附层由氮化钛膜构成。

8.根据权利要求1所述形成钨柱塞的方法,其特征是所述下层导电区由下层布线导体构成。

9.根据权利要求1所述形成钨柱塞的方法,其特征是所述下层导电区由形成在衬底上的扩散区构成。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP6316188A JP2758841B2 (ja) | 1994-12-20 | 1994-12-20 | 半導体装置の製造方法 |

| JP316188/94 | 1994-12-20 | ||

| JP316188/1994 | 1994-12-20 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1135094A CN1135094A (zh) | 1996-11-06 |

| CN1071490C true CN1071490C (zh) | 2001-09-19 |

Family

ID=18074282

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN95119463A Expired - Fee Related CN1071490C (zh) | 1994-12-20 | 1995-12-20 | 形成钨柱塞的方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US5893749A (zh) |

| JP (1) | JP2758841B2 (zh) |

| KR (1) | KR100228565B1 (zh) |

| CN (1) | CN1071490C (zh) |

| TW (1) | TW307021B (zh) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10172969A (ja) * | 1996-12-06 | 1998-06-26 | Nec Corp | 半導体装置の製造方法 |

| TW398065B (en) * | 1997-07-16 | 2000-07-11 | United Microelectronics Corp | The manufacturing method of the integrated circuit metal wiring |

| TW362261B (en) * | 1997-12-13 | 1999-06-21 | United Microelectronics Corp | Manufacturing method of contact plugs |

| US6319822B1 (en) * | 1998-10-01 | 2001-11-20 | Taiwan Semiconductor Manufacturing Company | Process for forming an integrated contact or via |

| US6146991A (en) * | 1999-09-03 | 2000-11-14 | Taiwan Semiconductor Manufacturing Company | Barrier metal composite layer featuring a thin plasma vapor deposited titanium nitride capping layer |

| US7563487B2 (en) * | 2003-03-31 | 2009-07-21 | Sumitomo Electric Industries, Ltd. | Anisotropic electrically conductive film and method of producing the same |

| US6989105B2 (en) * | 2003-06-27 | 2006-01-24 | International Business Machines Corporation | Detection of hardmask removal using a selective etch |

| US7091085B2 (en) * | 2003-11-14 | 2006-08-15 | Micron Technology, Inc. | Reduced cell-to-cell shorting for memory arrays |

| CN100395451C (zh) * | 2006-07-27 | 2008-06-18 | 安东石油技术(集团)有限公司 | 抽油泵柱塞的制造方法 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4822753A (en) * | 1988-05-09 | 1989-04-18 | Motorola, Inc. | Method for making a w/tin contact |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4960732A (en) * | 1987-02-19 | 1990-10-02 | Advanced Micro Devices, Inc. | Contact plug and interconnect employing a barrier lining and a backfilled conductor material |

| US5167760A (en) * | 1989-11-14 | 1992-12-01 | Intel Corporation | Etchback process for tungsten contact/via filling |

| US5225372A (en) * | 1990-12-24 | 1993-07-06 | Motorola, Inc. | Method of making a semiconductor device having an improved metallization structure |

| JPH04293233A (ja) * | 1991-03-22 | 1992-10-16 | Sony Corp | メタルプラグの形成方法 |

| JP3116432B2 (ja) * | 1991-06-28 | 2000-12-11 | ソニー株式会社 | 半導体装置の製造方法 |

| JPH0530426A (ja) * | 1991-07-25 | 1993-02-05 | Matsushita Electric Ind Co Ltd | 文字表示装置 |

| JP2655213B2 (ja) * | 1991-10-14 | 1997-09-17 | 三菱電機株式会社 | 半導体装置の配線接続構造およびその製造方法 |

| JPH05166944A (ja) * | 1991-12-19 | 1993-07-02 | Sony Corp | 半導体装置の配線形成方法 |

-

1994

- 1994-12-20 JP JP6316188A patent/JP2758841B2/ja not_active Expired - Lifetime

-

1995

- 1995-12-19 TW TW084113544A patent/TW307021B/zh active

- 1995-12-20 US US08/575,478 patent/US5893749A/en not_active Expired - Fee Related

- 1995-12-20 KR KR1019950052831A patent/KR100228565B1/ko not_active IP Right Cessation

- 1995-12-20 CN CN95119463A patent/CN1071490C/zh not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4822753A (en) * | 1988-05-09 | 1989-04-18 | Motorola, Inc. | Method for making a w/tin contact |

Also Published As

| Publication number | Publication date |

|---|---|

| JPH08172058A (ja) | 1996-07-02 |

| TW307021B (zh) | 1997-06-01 |

| KR100228565B1 (ko) | 1999-11-01 |

| US5893749A (en) | 1999-04-13 |

| JP2758841B2 (ja) | 1998-05-28 |

| CN1135094A (zh) | 1996-11-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3925780B2 (ja) | 触媒及び化学気相蒸着法を用いて銅配線及び薄膜を形成する方法 | |

| KR100337580B1 (ko) | 반도체장치및그제조방법 | |

| KR100238698B1 (ko) | 다층배선의 형성방법 | |

| CN1434509A (zh) | 双镶嵌金属内连线结构及其制作方法 | |

| CN1795552A (zh) | 制造一种多层互连结构的方法 | |

| EP1064674A2 (en) | A method of manufacturing an electronic device comprising two layers of organic-containing material | |

| EP1263035A1 (en) | Method for sealing via sidewalls in porous low-k dielectric layers | |

| CN1071490C (zh) | 形成钨柱塞的方法 | |

| CN1293638C (zh) | 半导体存储器件和采用镶嵌位线工艺制造该器件的方法 | |

| CN1216397A (zh) | 一种用于生产具有双重波纹结构的半导体器件的方法 | |

| JPH04142061A (ja) | タングステンプラグの形成方法 | |

| CN1129179C (zh) | 浅沟槽隔离方法 | |

| CN1258097A (zh) | 形成双镶嵌布线的方法 | |

| US6022800A (en) | Method of forming barrier layer for tungsten plugs in interlayer dielectrics | |

| KR950010858B1 (ko) | 반도체 소자의 금속콘택 형성방법 | |

| CN1215227A (zh) | 半导体器件的制造方法 | |

| CN1264172A (zh) | 使用双镶嵌工艺生产半导体器件的方法 | |

| CN1251323C (zh) | 改善双嵌入式层间金属介电层表面平坦度的方法 | |

| CN2793918Y (zh) | 半导体装置 | |

| US5804504A (en) | Method for forming wiring of semiconductor device | |

| KR100292117B1 (ko) | 반도체 장치의 다층배선을 위한 도전체 플러그 형성방법 | |

| JP2704120B2 (ja) | 半導体装置の製造方法 | |

| CN1897267A (zh) | 半导体装置及其制造方法 | |

| JPH07169834A (ja) | 層間接続孔の埋め込み方法 | |

| CN1186819C (zh) | 柱脚型储存节与其接触插塞及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C19 | Lapse of patent right due to non-payment of the annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |