CN101930794A - 具有状态脉冲串输出的同步快闪存储器 - Google Patents

具有状态脉冲串输出的同步快闪存储器 Download PDFInfo

- Publication number

- CN101930794A CN101930794A CN2009102217820A CN200910221782A CN101930794A CN 101930794 A CN101930794 A CN 101930794A CN 2009102217820 A CN2009102217820 A CN 2009102217820A CN 200910221782 A CN200910221782 A CN 200910221782A CN 101930794 A CN101930794 A CN 101930794A

- Authority

- CN

- China

- Prior art keywords

- register

- data

- read

- component part

- storage component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/103—Read-write modes for single port memories, i.e. having either a random port or a serial port using serially addressed read-write data registers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/1018—Serial bit line access mode, e.g. using bit line address shift registers, bit line address counters, bit line burst counters

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1072—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers for memories with random access ports synchronised on clock signal pulse trains, e.g. synchronous memories, self timed memories

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/20—Initialising; Data preset; Chip identification

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/22—Safety or protection circuits preventing unauthorised or accidental access to memory cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

- Read Only Memory (AREA)

Abstract

公开了一种具有状态脉冲串输出的同步快闪存储器,同步快闪存储器包括非易失性存储单元的阵列。存储器阵列被排列成行和列,以及可被进一步排列成可寻址的块。数据通信连接被使用来与外部设备(诸如,处理器或其他存储器控制器)进行双向数据通信。存储器可以在一系列时钟周期期间在数据通信连接上输出来自存储寄存器的数据,以提供寄存器数据的脉冲串。存储器可以按照规定的时钟等待时间值提供寄存器数据。寄存器数据可包括状态数据、操作设置值数据、制造识别、和存储器器件识别。

Description

本申请是申请日为2001年7月27日、申请号为01816420.X、发明名称为“具有状态脉冲串输出的同步快闪存储器”的申请的分案申请。

技术领域

本发明总的涉及非易失性存储器器件,具体地,本发明涉及同步非易失性快闪存储器。

背景技术

存储器器件典型地被提供用作为计算机中的内部存储区域。术语存储器表示具有集成电路芯片形式的数据存储。存储器具有几种不同的类型。一种类型是RAM(随机存取存储器)。这典型地被用作为计算机环境下的主存储器。RAM是指读出和写入存储器,也就是,可以把数据写入到RAM和从RAM读出数据。这是与ROM不同的,ROM只允许读出数据。大多数RAM是易失性的,这意味着它需要稳定的电流来保持它的内容,只要电源被去激活,在RAM中无论什么数据都被丢失。

计算机几乎总是包含小量的只读存储器(ROM),它保存用于激活计算机的指令。与RAM不同,ROM不能被写入。EEPROM(电可擦可编程只读存储器)是一种特殊类型的非易失性ROM,它可以通过把它暴露在电荷中而被擦除。像其他类型的ROM一样,EEPROM传统上没有RAM那样快。EEPROM包括很大数目的、具有电隔离的栅极(浮动栅)的存储单元。数据是以浮动栅上的电荷的形式被存储在存储单元的。通过编程和擦除操作,电荷分别被输送到浮动栅或从浮动栅被去除。

另一种类型的非易失性存储器是快闪存储器。快闪存储器是一种EEPROM,它可以以块的形式,而不是一次一个字节地,被擦除和重新编程。许多现代的PCS具有它们自己的、被存储在快闪存储器芯片上的BIOS,这样,如果必要它可容易地被更新。这样的BIOS有时被称为快速BIOS。快闪存储器在调制解调器中也很通用,因为它使得调制解调器制造商能够支持新的协议(当这些协议成为标准化时)。

典型的快闪存储器包括存储器阵列,它包括很大数目的、以行和列的形式排列的存储单元。每个存储单元包括能够保持电荷的、浮动 栅场效应晶体管。存储单元通常被编组为块。在一个块内的每个单元可以通过对浮动栅进行充电而被随机地电编程。通过块擦除操作,电荷可以从浮动栅上被去除。存储单元中的数据是由浮动栅上的电荷的存在与否而被确定。

同步DRAM(SDRAM)是一种DRAM,它能够以比传统的DRAM存储器高得多的时钟速度运行。SDRAM使它本身与CPU总线同步,以及能够以100MHz速率运行,比传统的FPM(快速页模式)RAM约快三倍,以及约为快速EDO(扩展数据输出)DRAM和BEDO(脉冲串扩展数据输出)DRAM的两倍。可以迅速地访问SDRAM,但它是易失性的。许多计算机系统被设计成使用SDRAM来操作,而从非易失性存储器得到好处。

由于上述的理由,以及由于下面阐述的其他理由,这些理由对于本领域技术人员在阅读和了解本技术说明后将是显而易见的,在本技术中需要一种可以以类似于SDRAM操作的方式操作的、非易失性存储器器件。

发明内容

存储器器件的上述的问题和其他问题由本发明解决,以及可通过阅读和研究以下的技术说明而了解它们。

在一个实施例中,操作同步存储器器件的方法包括确定x个周期的读脉冲串长度以使来自同步存储器器件的数据输出以x个接连的时钟周期被输出,起动寄存器读操作,以便读出被存储在内部寄存器中的数据,以及在x个接连的时钟周期内在外部数据连接上输出被存储在内部寄存器中的数据。

在另一个实施例中,操作同步存储器器件的方法包括接受读寄存器命令,以及响应于读寄存器命令在x个时钟周期内输出来自同步存储器器件的寄存器数据。

在再一个实施例中,操作同步存储器器件的方法包括在存储器器件的阵列上执行写操作,以及在执行写操作期间,把来自处理器的寄存器读命令提供到存储器器件。寄存器读命令在第一时钟周期在存储器器件的输入端处被接受,以及被存储在存储器寄存器中的寄存器数据被读出。寄存器数据在多个时钟周期期间在同步存储器器件的数据通信连接上被输出。寄存器数据的输出在接受到寄存器读命令后、被延时了预定的时钟等待时间间隔。

同步存储器器件包括存储单元阵列、数据寄存器、以及时钟信号输入连接。控制电路响应于寄存器读命令在输出连接处提供来自数据寄存器的数据。控制电路根据编程的读脉冲串长度值在预定数目的时钟周期内输出数据。

附图说明

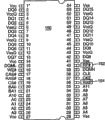

图1A是本发明的同步快闪存储器的方框图;

图1B是本发明的一个实施例的集成电路管脚互联图;

图1C是本发明的一个实施例的集成电路互联凸点网格阵列(bumpgrid array)图;

图2、2A和2B表示本发明的一个实施例的模式寄存器;

图3表示具有一个、两个和三个时钟周期的CAS等待时间的读操作;

图4表示激活在本发明的一个实施例的存储器的一个组中的一个特定的行;

图5表示在工作的命令与读或写命令之间的时序;

图6表示读命令;

图7表示本发明的一个实施例的接连的读脉冲串的时序;

图8表示在本发明的一个实施例的一页内的随机读访问;

图9表示后面跟随写操作的读操作;

图10表示按照本发明的一个实施例的、通过使用脉冲串终结命令终结的读脉冲串操作;

图11表示写命令;

图12表示后面跟随读操作的写操作;

图13表示本发明的一个实施例的电源功率降低操作;

图14表示在脉冲串读出期间时钟中止操作;

图15表示具有两个导引扇区的存储器的一个实施例的存储器地址变换;

图16是按照本发明的一个实施例的、自定时的写序列的流程图;

图17是按照本发明的一个实施例的、完整的写状态检验序列的流程图;

图18是按照本发明的一个实施例的、自定时的块擦除序列的流程图;

图19是按照本发明的一个实施例的、完整的块擦除状态检验序列的流程图;

图20是按照本发明的一个实施例的、块保护序列的流程图;

图21是按照本发明的一个实施例的、完整的块状态检验序列的流程图;

图22是按照本发明的一个实施例的、器件保护序列的流程图;

图23是按照本发明的一个实施例的、块的非保护序列的流程图;

图24表示起动和装载模式寄存器操作的时序;

图25表示时钟中止模式操作的时序;

图26表示脉冲串读操作的时序;

图27表示交替组读出访问的时序;

图28表示全页脉冲串读操作的时序;

图29表示通过使用数据屏蔽信号的脉冲串读操作的时序;

图30表后面跟随对不同组读出的写操作的时序;

图31表示后面跟随对同一个组读出的写操作的时序;

图32表示本发明的存储器系统;以及

图33表示本发明的多处理器系统。

具体实施方式

在本发明的以下的详细的说明中,参考了构成本发明的一部分的附图,以及其中显示了可以实施本发明的特定的实施例。这些实施例充分详细地被描述,以使得本领域技术人员能够实施本发明,以及将会看到,可以利用其他实施例和可以作出逻辑的、机械的和电的改变,而不背离本发明的精神和范围。所以,以下的详细说明并不是在限制的意义上作出的,以及本发明的范围仅仅由权利要求限定。

以下的详细说明分成两个主要的节。第一节是接口功能说明,它详细阐述与SDRAM存储器的兼容性。第二节是功能性说明,它具体说明快闪结构功能性命令。

接口功能说明

参照图1A,描述本发明的一个实施例的方框图。存储器器件100包括非易失性快速存储单元102的阵列。阵列被排列成多个可寻址的组。在一个实施例中,存储器包含四个存储器组104、106、108和110。每个存储器组包含存储单元的可寻址的扇区。被存储在存储器中的数 据可以通过使用由地址寄存器112接受的、外部提供的位置地址被访问。利用行地址复用电路114,对这些地址进行译码。这些地址也可以通过使用组控制逻辑116和行地址锁存与译码电路118被译码。为了访问存储器的适当的列,列地址计数和锁存电路120把接受的地址耦合到列译码电路122。电路124提供输入/输出选通、数据屏蔽逻辑、读数据锁存电路和写驱动器电路。数据通过数据输入寄存器126被输入和通过数据输出寄存器128被输出。命令执行逻辑130被提供来控制存储器器件的基本操作。状态机132也被提供来控制在存储器阵列和单元上执行的特定的操作。状态寄存器134和识别寄存器136也可被提供来输出数据。

图1B表示本发明的一个实施例的互联的管脚分配。存储器封装150具有54个互联管脚。管脚结构基本上类似于已可提供的SDRAM封装。对于本发明特定的两个互联管脚是RP# 152和Vccp 154。虽然本发明可以共享看来与SDRAM的相同的互联标签,但在互联管脚上提供的信号的功能在这里被描述,以及除非这里阐述的,它不应当等同于SDRAM的信号的功能。图1C表示存储器封装160的一个实施例,它具有凸起连接,而不是图1C的管脚连接。所以,本发明并不限于特定的封装结构。

在描述存储器器件的操作特性之前,先给出互联管脚和它们的各个信号的更详细的说明。输入时钟连接被使用来提供时钟信号(CLK)。时钟信号可以被系统时钟驱动,以及所有的同步快闪存储器输入信号在CLK的上升沿处被采样。CLK也给内部脉冲串计数器加增量,以及控制输出寄存器。

输入时钟允许(CKE)连接端被使用来激活(HIGH(高)状态)和去激活(LOW(低)状态)CLK信号输入。去激活时钟输入可提供电源功率降低和等待操作(此处所有的存储器组是空闲的),工作的电源功率降低(在任一个组中存储器行是ACTIVE(工作的)),或时钟中止操作(脉冲串/访问在进行中)。CKE是同步的,除非在器件进入功率降低模式以后,此处CKE成为非同步的,直至退出这个模式以后为止。输入缓冲器,包括CLK,在功率降低模式期间是被禁止的,以便提供低的等待功率。CKE在不需要功率降低模式(不同于RP#深度功率降低)的系统中可以维持在HIGH(高)。

芯片选择(CS#)输入连接端提供一个信号,以便允许(寄存的LOW(低))和禁止(寄存的HIGH(高))在命令执行逻辑中提供的命令译码器。当CS#被寄存为HIGH时所有的命令被屏蔽。另外,CS#在具有多个组的系统上提供外部的组选择,以及CS#可被看作为命令代码的一部分;但不一定是必须的。

用于RAS#、CAS#和WE#(连同CAS#、CS#一起)的输入命令输入连接端规定要被存储器执行的命令,正如下面详细地描述的。输入/输出屏蔽(DQM)连接端被使用来提供用于写访问的输入屏蔽信号,和用于读访问的输出允许信号。当DQM在写周期期间被采样HIGH时,输入数据被屏蔽。当DQM在读周期期间被采样HIGH时,输出缓冲器被置于高阻抗(高-Z)状态(在两个时钟等待时间后)。DQML相应于数据连接DQ0-DQ7,以及DQMH相应于数据连接DQ8-DQ15。DQML和DQMH在表示为DQM时被认为是相同的状态。

地址输入端133主要被使用来提供地址信号。在所表示的实施例中,存储器具有12条线(A0-A11)。其他的信号可以在地址连接处被提供,正如下面描述的。地址输入端在ACTIVE(工作的)命令(行地址A0-A11)和READ/WRITE(读/写)命令(列地址A0-A7)期间被采样,以便选择各个存储器组中的一个位置。地址输入也被使用来在LOADCOMMAND REGISTER(装载命令寄存器)操作期间提供操作代码(OpCode),在下面解释。地址线A0-A11也被使用来在LOAD MODE REGISTER(装载模式寄存器)操作期间输入模式设置值。

输入复位/功率降低(RP#)连接140被使用于复位和功率降低操作。在初始器件功率上升时,在一个实施例中,在发出可执行的命令之前,RP#从低转移到高以后需要100μs延时,以便内部器件初始化。RP#信号清除状态寄存器,把内部状态机(ISM)132设置在阵列读模式,以及当处在LOW(低)时,把器件置于深度功率降低模式。在功率降低模式期间,所有的输入连接,包括CS# 142,都处在“不用管它”,以及所有的输出处在High-Z(高阻)状态。当RP#信号等于VHH电压(5伏)时,在WRITE和ERASE期间,所有的保护模式被忽略。RP#信号也允许器件保护比特被设置为1(保护)以及允许16比特寄存器的块保护比特(在位置0和15)被设置为0(非保护),当被加上VHH时。保护比特将在下面更详细地被描述。在所有其他操作模式期间,RP#被保持为 HIGH。

组地址输入连接,BA0和BA1规定哪个组加上ACTIVE、READ、WRITE、或BLOCK PROTECT命令。DQ0-DQ15连接143是数据总线连接,被使用于双向数据通信。参照图1B,VCCQ连接被使用来提供隔离的功率到DQ连接,以便改善对噪声的抗扰性。在一个实施例中,VCCQ=Vcc或1.8V±0.15V。VSSQ连接被使用来提供隔离的地到DQ连接,以便改善噪声抗状性。VCC连接提供供电电源,诸如3V。通过Vss连接来提供地连接。另一个工作电压被提供到VCCP连接144。VCCP连接在器件初始化、WRITE和ERASE操作期间可以外部地连接到VCC以及源电流。也就是,写入或擦除存储器器件可以通过使用VCCP电压被执行,而所有其他的操作可以用VCC电压来执行。VCCP连接被耦合到高电压开关/泵电路145。

以下的节提供同步快闪存储器的操作的更详细的说明。本发明的一个实施例是非易失性、扇区电可擦的(快闪)、可编程只读存储器,包含被组织为4,194,304字×16比特的67,108,864比特。其他流行的密度也是预期的,但本发明并不限于示例的密度。每个存储器组被组织为四个独立的可擦除的块(总共16个)。为了确保关键的固件被保护免受偶然的擦除或过写入,存储器可包括16个256K字硬件和软件可锁定的块。存储器的四个组的结构支持真正的同时发生的操作。

到任何组的读访问可以与到任何其他的组的背景写入或擦除操作同时发生。同步快闪存储器具有同步的接口(所有的信号在时钟信号CLK的上升沿处被登记)。到存储器的读访问可以是面向脉冲串的。也就是,存储器访问在选择的位置处开始以及在编程的序列中编程的数目的位置上继续。读访问从后面跟随READ命令的ACTIVE命令的登记开始。与ACTIVE命令一致的登记的地址比特被使用来选择要被访问的组和行。与READ命令一致的登记的地址比特被使用来选择脉冲串访问的开始列的位置和组。

同步快闪存储器提供可编程的读脉冲串长度,1、2、4、或8个位置或全页,带有脉冲串终结任选项。另外,同步快闪存储器使用内部管线结构达到高速度操作。

同步快闪存储器可以操作在低功率存储器系统中,诸如工作在3伏的系统。深度功率降低模式可以连同功率节省等待模式一起被提供。 所有的输入和输出是低压晶体管-晶体管逻辑(LVTTL)可兼容的。同步快闪存储器提供快闪工作性能方面重大的优点,包括与自动列地址生成同步地闪现高数据速率的数据的能力以及在脉冲串访问期间在每个时钟周期随机地改变列地址的能力。

通常,同步快闪存储器类似于操作在低压的多组DRAM被配置。以及包括同步接口。每个组被组织为行和列。在正常操作之前,同步快闪存储器被初始化。以下的节提供详细的信息,包括器件初始化,寄存器规定,命令说明和器件操作。

同步快闪存储器被加上电源,以及以预定的方式被初始化。在功率加到VCC,VCCQ和VCCP(同时地)以及时钟信号稳定后,RP# 140从LOW状态转移到HIGH状态。在RP#转移到HIGH后需要一个延时,诸如100μs延时,以便完成内部器件初始化。在延迟的时间过去以后,存储器被置于阵列读模式,以及准备好接受模式寄存器编程或可执行的命令。在非易失性模式寄存器147(NV模式寄存器)的初始编程后,内容在初始化期间被自动装载到易失性模式寄存器148。器件在编程状态下被加上功率,以及不需要在发出工作命令之前重新装载非易失性寄存器147。这将在下面更详细地说明。

模式寄存器148被使用来规定同步快闪存储器的特定的工作模式。这个规定包括选择脉冲串长度、脉冲串类型、CAS等待时间、和工作模式,如图2所示。模式寄存器通过LOAD MODE REGISTER(装载模式寄存器)命令被编程以及保持存储的信息,直至它被重新编程为止。模式寄存器的内容可被复制到NV模式寄存器147。NV模式寄存器设置值在初始化期间自动装载模式寄存器148。关于ERASE NVMODE REGISTER(擦除NV模式寄存器)和WRITE NVMODE REGISTER(写入NV模式寄存器)命令序列的细节在下面被提供。本领域技术人员将会看到,SDRAM要求模式寄存器在每次初始化操作期间必须被外部地装载。本发明允许缺省模式被存储在NV模式寄存器147。NV模式寄存器的内容然后被复制到易失性模式寄存器148,以便在存储器操作期间访问。

模式寄存器比特M0-M2规定脉冲串长度,M3规定脉冲串类型(顺序的或交错的),M4-M6规定CAS等待时间,M7和M8规定工作模式,M9被设置为1,以及M10和M11在本实施例中被保留。因为当前不执行写脉冲串,故M9被设置为逻辑1,以及写访问是单个位置(非脉冲 串)访问。当所有的组是空闲时,模式寄存器必须被装载,以及在初始化以后的操作之前,控制器必须等待规定的时间。

对同步快闪存储器的读访问可以是面向脉冲串的,脉冲串长度是可编程的,如表1所示。脉冲串长度确定对于给定的READ命令可被自动访问的列位置的最大数目。对于顺序的和交错的脉冲串类型都可得到1、2、4、或8个位置的脉冲串长度,以及对于顺序的类型可得到全页的脉冲串长度。全页的脉冲串可以结合BURST TERMINATE(脉冲串终结)命令被使用来生成任意的脉冲串长度,也就是,脉冲串可被选择地终结,以便提供定做的长度的脉冲串。当发出READ命令时,等于脉冲串长度的列的块实际上被选择。对于该脉冲串的所有的访问发生在这个块内,意味着如果到达边界,脉冲串将隐蔽在该块内。当脉冲串长度被设置为2时这个块被A1-A7唯一地选择,当脉冲串长度被设置为4时这个块被A2-A7选择,以及当脉冲串长度被设置为8时这个块被A3-A7选择。其余的(最低有效的)地址比特被使用来选择该块内的开始位置。如果到达边界,则全页的脉冲串隐蔽在该页内。

在给定的脉冲串内的访问可被编程为顺序的或交错的;这被称为脉冲串类型,以及通过比特M3被选择。在一个脉冲串内的访问的次序由脉冲串长度、脉冲串类型和开始的列地址确定,如表1所示。

表1 脉冲串的定义

列地址选通(CAS)等待时间是在READ命令的登记与DQ连接端处的第一片输出数据的可提供性之间的延时(以时钟周期为单位)。等待时间可被设置为一,二,或三个时钟周期。例如,如果READ命令在时钟边沿n处被登记,以及等待时间是m个时钟,则数据将是由时钟边沿n+m可提供的。由于提早一个周期的时钟边沿(n+m-1)的结果,DQ连接将开始驱动数据,以及如果相关的访问时间是满足的话,数据在时钟边沿n+m之前是正确的。例如,假设时钟周期时间是使得所有的相关的访问时间是满足的,如果READ命令在T0时被登记,以及等待 时间被编程为两个时钟,DQ将在T1后开始驱动,以及数据在T2之前是正确的,如图3所示。图3表示示例的工作频率,不同的时钟等待时间设置值可以以这个频率被使用。正常的操作模式通过把M7和M8设置为零而被选择,以及编程的脉冲串长度应用到READ脉冲串。

以下的真值表提供在本发明的存储器的实施例的操作命令方面的更多的细节。这里提供命令的说明,以及接着是真值表2。

真值表1 接口命令和DQM操作

| 名称(功能) | CS# | RAS# | CAS# | WE# | DQM | ADDR | DQs |

| COMMAND INHIBIT(NOP) | H | X | X | X | X | X | X |

| NO OPERATION(NOP) | L | H | H | H | X | X | X |

| ACTIVE(选择组和工作的行) | L | L | H | H | X | 组/行 | X |

| READ(选择组、列和开始READ脉冲串) | L | H | L | H | X | 组/列 | X |

| WRITE(选择组、列和开始WRITE) | L | H | L | L | X | 组/列 | 正确的 |

| BURST TERMINATE | L | H | H | L | X | X | 工作的 |

| ACTIVE TERMINATE | L | L | H | L | X | X | X |

| LOAD COMMAND | L | L | L | H | X | Com | X |

| REGISTER | 代码 | ||||||

| LOAD MODE REGISTER | L | L | L | L | X | 操作码 | X |

| 写允许/输出允许 | - | - | - | - | L | - | 工作的 |

| 写禁止/输出High-Z | - | - | - | - | H | - | 高阻 |

真值表2 快闪存储器命令序列

COMMAND INHIBIT(命令禁止)功能阻止同步快闪存储器执行新的命令,不管CLK信号是否允许。同步快闪存储器实际上被去选择,但已在进行的操作不受影响。

NO OPERATION(NOP)(不操作)命令被使用来对于被选择的同步快闪存储器(CS#为LOW(低))执行NOP。这阻止在空闲或等待状态期间登记不想要的命令,但已在进行的操作不受影响。

模式寄存器数据通过输入端A0-A11被装载。在所有的阵列组是空闲时只能发出LOAD MODE REGISTER(装载模式寄存器)命令,以及在预定的延时(MRD)被满足之前不能发出随后的可执行的命令。在NV模式寄存器147中的数据在上电初始化时被自动装载到模式寄存器148,它是缺省数据,除非它与LOAD MODE REGISTER命令一起被动态地改变。

ACTIVE(工作的)命令被使用来打开(或激活)特定的阵列组中的一行,用于以后的访问。在BA0,BA1输入端上的数值选择那个组,以及在输入端A0-A11上提供的地址选择那一行。这一行保持对于访问是工作的,直至下一个ACTIVE命令、功率降低、或复位为止。

READ(读)命令被使用来起动对工作的行的脉冲串读访问。在BA0,BA1输入端上的数值选择那个组,以及在输入端A0-A7上提供的地址选择开始的列位置。读出的数据出现在DQ上,该DQ受到在两个时钟之前存在的、在数据屏蔽(DQM)输入端上逻辑电平的支配。如果给定的DQM信号被登记为HIGH,则相应的DQ将在两个时钟后是High-Z(高阻);如果DQM信号被登记为LOW,则DQ将提供正确的数据。因此,DQM输入端可被使用来在读操作期间屏蔽输出数据。

WRITE(写)命令被使用来起动对工作的行的单个位置的写访问。WRITE命令前面必须有WRITE SETUP(写建立)命令。在BA0,BA1输入端上的数值选择那个组,以及在输入端A0-A7上提供的地址选择列位置。在DQ上出现的输入数据被写入到存储器阵列,该DQ受到与数据一致的DQM输入逻辑电平的支配。如果给定的DQM信号被登记为LOW,则相应的数据将被写入到存储器;如果DQM信号被登记为HIGH,则相应的数据输入将被忽略,以及对该字/列位置不执行WRITE。具有DQMHIGH的WRITE命令被认为是NOP。

ACTIVE TERMINATE(工作终结)命令对于同步快闪存储器是不需 要的,但它可被提供以类似于SDRAM PRECHARGE命令的方式来终结读操作。ACTIVE TERMINATE命令可被发出来终结正在进行的BURST READ(脉冲串读出),以及可以是或不一定是组特定的。

BURST TERMINATE(脉冲串终结)命令被使用来截断固定长度的脉冲串或全页的脉冲串。在BURST TERMINATE命令之前的最近的READ命令将被截断。BURST TERMINATE不是组特定的。

装载命令寄存器操作被使用来起动对命令执行逻辑(CEL)130的快闪存储器控制命令。CEL接受和解释加到器件的命令。这些命令控制内部状态机132和读路径(即,存储器阵列102、ID寄存器136或状态寄存器134)的操作。

在任何READ或WRITE命令可被发出到同步快闪存储器内的一个组之前,在该组中的一行必须被“打开”。这是通过ACTIVE命令(由CS#,WE#,RAS#,CAS#规定的)完成的,该命令选择要被激活的组和行,见图4。

在打开一行(发出ACTIVE命令)后,READ或WRITE命令可被发出到由时间间隔(tRCD)技术说明规定的行,tRCD(MIN)应当由时钟周期划分,以及舍入到下一个整个数目,确定在ACTIVE命令后的、READ或WRITE命令可被借以进入的、最早的时钟边沿。例如,对于90MHz时钟(11.11ns周期)的30ns的tRCD技术说明导致2.7个时钟,它被舍入为3。这反映在图5上,它覆盖其中2<tRCD(MIN)/tCK<3的任意情形。(相同的程序过程被使用从时间单位到时钟周期来转换其他技术说明极限值)。

以后的、对同一个组的不同的行的ACTIVE命令可被发出,而不必关闭先前工作的行,只要在对同一个组的接连的ACTIVE命令之间的最小时间间隔是由tRC规定的话。

在第一组被访问的同时,以后的、对另一个组的ACTIVE命令可被发出,这导致总计行访问开销的减小。在对不同组的接连的ACTIVE命令之间的最小时间间隔是由时间间隔tRRD规定。

READ脉冲串从READ命令(由CS#,WE#,RAS#,CAS#规定)起动,如图6所示。开始的列和组地址从READ命令提供。在READ脉冲串期间,来自开始列地址的正确的数据读出单元在READ命令后的CAS等待时间后是可以得到的。每个随后的数据读出单元在下一个时钟上升沿之前 是正确的。在完成脉冲串后,假设没有其他命令被起动,DQ将进到High-Z状态。全页的脉冲串将继续,直至终结为止。(在该页的结尾,它将隐蔽到列0,并继续进行。)来自任何READ脉冲串的数据可以用以后的READ命令截断,以及来自固定长度READ脉冲串的数据可以紧接地被来自以后的REAB命令的数据所跟随。在任一种情形下,连续的数据流可被保持。来自新的脉冲串的第一数据单元跟随在完成的脉冲串的最后的单元后面,或跟随在被截断的较长的脉冲串的最后的想要的数据单元后面。新的READ命令应当在最后的想要的数据单元是正确的时钟边沿之前的x周期被发出,其中x等于CAS等待时间减1。这示于图7中对于1,2,和3的CAS等待时间;数据单元n+3或者是4的脉冲串的最后的,或者是较长的脉冲串的最后想要的。同步快闪存储器使用流水线结构,所以,不需要与预取的结构有关的2n法则。READ命令可以在先前的READ命令后的任何时钟周期被起动。可以执行在一页内的全速的随机读访问,如图8所示,或可以执行对不同的组的每个随后的READ。

来自任何READ脉冲串的数据可以用以后的WRITE命令被截断(WRITE命令之前必须有WRITE SETUP),以及来自固定长度READ脉冲串的数据可以紧接地被来自随后的WRITE命令(受到总线换向限制)的数据所跟随。WRITE可以在紧接在来自READ脉冲串的最后的(或最后想要的)数据单元后面的时钟边沿处被起动,只要I/O竞争可被避免。在给定的系统设计中,可以有可能性:驱动输入数据的器件在同步快闪存储器DQ进到High-Z之前进到Low-Z(低阻)。在这种情形下,至少单个周期延时将出现在最后的读数据与WRITE命令之间。

DQM输入被使用来避免I/O竞争,如图9所示。DQM信号必须在WRITE命令之前至少坚持(HIGH)两个时钟(对于输出缓冲器,DQM等待时间是两个时钟)坚持(HIGH),以便抑制来自READ的数据输出。一旦WRITE命令被登记,DQ将进到High-Z(或保持在High-Z),而不管DQM信号的状态。DQM信号必须在WRITE命令之前被去除坚持,(对于输入缓冲器,DQM等待时间是零),以便确保写入的数据不被屏蔽。图9表示其中时钟频率允许不用加上NOP周期而避免总线竞争的情形。

固定长度或全页READ脉冲串可以用ACTIVE TERMINATE命令(可以是或不一定是组特定的)或BURST TERMINATE(不是组特定的)命令 截断。ACTIVE TERMINATE或BURST TERMINATE命令应当在最后的想要的数据单元是正确的时钟边沿之前的x周期被发出,其中x等于CAS等待时间减1。这是在图10上对于每个可能的CAS等待时间所表示的;数据单元n+3或者是四的脉冲串的最后的想要的数据单元,或者是较长的脉冲串的最后想要的数据单元。

单个位置WRITE从WRITE命令(由CS#,WE#,RAS#,CAS#规定)起动,如图11所示。开始的列和组地址从WRITE命令提供。一旦WRITE命令被登记,就可如真值表4和5规定的那样执行READ命令。图12上表示一个例子。在WRITE期间,正确的数据输入与WRITE命令一致地被登记。

不像SDRAM那样,同步快闪存储器不需要PRECHARGE命令来去激活在特定的组中打开的行,或在所有的组中打开的行。ACTIVETERMINATE命令类似于BURST TERMINATE命令;然而,ACTIVE TERMINATE可以是或不一定是组特定的。在ACTIVE TERMINATE命令期间坚持输入A10是HIGH,将终结在任何组中的BURST READ。当A10在ACTIVETERMINATE命令期间是低时,BA0和BA1将确定哪个组将接受终结操作。ACTIVE TERMINATE对于不是由A10、BA0、BA1寻址的组被认为是NOP。

当不是正在进行访问时,如果时钟允许,CKE与NOP或COMMANDINHIBIT(当没有进行访问时)一致地被登记为LOW,则出现功率降低。在内部状态机操作(包括WRITE操作)完成后,进入功率降低使得去激活输入和输出缓冲器(不包括CKE),以便在待机状态时节省功率。

功率降低状态可通过在想要的时钟边沿处(满足tCKS)登记NOP或COMMAND INHIBIT和CKE HIGH而退出。对于示例性功率降低操作,参阅图13。

当列访问/脉冲串正在进行和CKE被登记为LOW时出现时钟中止模式。在时钟中止模式下,内部时钟被去激活,“冻结”同步逻辑。对于CKE借以被采样为LOW的每个时钟上升沿,下一个内部的时钟上升沿被中止。在被中止的内部时钟边沿的时间出现在输入管脚处的任何命令或数据被忽略,出现在DQ管脚处的任何数据将保持被驱动,以及脉冲串计数器不加增量,只要时钟被中止(见图14的例子)。时钟中止模式可通过登记CKE HIGH而退出;内部时钟和相关的操作将在以后的时 钟上升沿时继续进行。

在一个实施例中,脉冲串读/单个写模式是缺省模式。所有的WRITE命令导致单个列位置(长度为一的脉冲串)的访问,而READ命令按照编程的脉冲串长度和序列对列进行访问。以下的真值表3表示使用CKE信号的存储器操作。

真值表3-CKE

| CKEn-1 | CKEn | 当前状态 | COMMANDn(命令) | ACTIONn(动作) |

| L | L | 功率降低 时钟中止 | X X | 保持功率降低 保持时钟中止 |

| L | H | 功率降低 时钟中止 | 命令禁止或NOP X | 退出功率降低 退出时钟中止 |

| H | L | 所有的组空闲 读或写 | 命令禁止或NOP 正确 | 进入功率降低 进入时钟中止 |

| H | H | 见真值表4 |

真值表4-当前状态组n-到组n的命令

| 当前状态 | CS# | RAS# | CAS# | WE# | 命令/动作 |

| 任何 | H L | X H | X H | X H | COMMAND INHIBIT(NOP/继续先前的操作) NO OPERATION(NOP/继续先前的操作) |

| 空闲 | L L L L | L L L L | H L L H | H H L L | ACTIVE(选择和激活一行) LOAD COMMAND REGISTER(装载命令寄存器) LOAD MODE REGISTER(装载模式寄存器) ACTIVE TERMINATE(工作终结) |

| 行工作的 | L L L L | H H L L | L L H L | H L L H | READ(选择列和开始READ脉冲串) WRITE(选择列和开始WRITE) ACTIVE TERMINATE LOAD COMMAND REG ISTER |

| 读 | L L L L L | H H L H L | L L H H L | H L L L H | READ(选择列和开始新的READ脉冲串) WRITE(选择列和开始WRITE) ACTIVE TERMINATE BURST TERMINATE LOAD COMMAND REGISTER |

| 写 | L L | H L | L L | H H | READ(选择列和开始新的READ脉冲串) LOAD COMMAND REGISTER |

真值表5-当前状态组n-对组m的命令

| 当前状态 | CS# | RAS# | CAS# | WE# | 命令/动作 |

| 任何 | H L | X H | X H | X H | COMMAND INHIBIT(NOP/继续先前的操作) NO OPERATION(NOP/继续先前的操作) |

| 空闲 | X | X | X | X | 任何命令,否则允许到组m |

| 行激活的, 工作的,或 工作终结 | L L L L L | L H H L L | H L L H L | H H L L H | ACTIVE(选择和激活行) READ(选择列和开始READ脉冲串) WRITE(选择列和开始WRITE) ACTIVE TERMINATE LOAD COMMAND REGISTER |

| 读 | L L L L L | L H H L L | H L L H L | H H L L H | ACTIVE(选择和激活行) READ(选择列和开始新的READ脉冲串) WRITE(选择列和开始WRITE) ACTIVE TERMINATE LOAD COMMAND REGISTER |

| 写 | L L L L L | L H L H L | H L H H L | H H L L H | ACTIVE(选择和激活行) READ(选择列和开始READ脉冲串) ACTIVE TERMINATE BURST TERMINATE LOAD COMMAND REGISTER |

功能说明

同步快闪存储器引用多个特性,以使得它理想地适用于在SDRAM总线上的代码存储和执行适当的应用。存储器阵列被分段成各个擦除块。每个块可被擦除,而不影响被存储在其他的块中的数据。这些存储器块通过对命令执行逻辑130(CEL)发出命令而被读出、写入和擦除。CEL控制内部状态机132(ISM)的操作,它完全控制所有的ERASENVMODE REGISTER(擦除NV模式寄存器)、WRITE NVMODE REGISTER(写入NV模式寄存器)、WRITE(写入)、BLOCK ERASE(块擦除)、BLOCK PROTECT(块保护)、DEVICE PROTECT(器件保护)、UNPROTECT ALL BLOCK(非保护所有的块)和VERIFY(验证)操作。ISM 132保护每个存储单元 不受到过分擦除,以及使得每个存储单元最佳化,以便最大数据保持。另外,ISM大大地简化在系统中或在外部编程器中为了写入器件所必须的控制。

同步快闪存储器被组织为16个独立的可擦除的存储器块,它们允许擦除存储器的一部分而不影响其余的存储器数据。任何的块可以是硬件保护的,免受不利的擦除或写入。保护的块要求在被修正之前RP#管脚被驱动到VHH(相当高的电压)。在位置0和15处的256K字的块可以具有附加的硬件保护。一旦对于这些块执行了PROTECT BLOCK(保护块)命令,UNPROTECT ALL BLOCKS命令就松开除了在位置0和15处的块以外的所有的块,除非RP#管脚是处在VHH。这在系统内固件更新期间对于关键的代码提供附加的安全性,如果出现不想要的功率扰动或系统复位的话。

功率接通初始化、ERASE、WRITE、和PROTECT的时序可通过使用ISM来控制存储器阵列中所有的编程算法而被简化。ISM确保保护不被过分擦除,以及使得对每个单元的写余量最佳化。在WRITE操作期间,ISM自动加增量以及监视WRITE企图,验证在每个存储单元上写余量以及更新ISM状态寄存器。当BLOCK ERASE操作被执行时,ISM自动地过写整个寻址的块(消除过分擦除),加增量和监视ERASE企图,以及设置在ISM状态寄存器中的比特。

8比特ISM状态寄存器134允许外部处理器200在WRITE、ERASE和PROTECT操作期间监视ISM的状态。8比特状态寄存器(SR7)的一个比特完全被ISM设置和清除。这个比特表示ISM是否忙于ERASE、WRITE或PROTECT任务。附加的错误信息在三个其他比特中(SR3、SR4和SR5)被设置:写入和保护块错误,擦除和非保护所有的块错误,以及器件保护错误。状态寄存器比特SR0,SR1和SR2提供ISM操作进行中的细节。用户可监视器件级或组级ISM操作(包括哪个组处在ISM控制下)是否正在进行中。这六个比特(SR3-SR5)必须被主系统清除。下面参照表2更详细地描述状态寄存器。

CEL 130接受和解释对器件的命令。这些命令控制ISM和读路径(即,存储器阵列,器件配置或状态寄存器)的操作。在ISM是工作的同时,命令可被发出到CEL。

为了允许最大功率保存,同步快闪存储器的特征在于非常低的电 流的、深的功率降低模式。为了进入这个模式,RP#管脚140(复位/功率降低)被取为VSS±0.2V。为了防止有害的RESET,RP#必须在器件进入复位模式之前保持为Vss在100ns内。对于RP#保持在Vss,器件将进入深度功率降低模式。在器件进入深度功率降低模式后,在RP#上从LOW到HIGH的转移,将导致如这里概述的、器件功率接通初始化序列。在进入复位模式后但在进入深度功率降低模式之前RP#从LOW到HIGH的转移需要在发出可执行的命令之前1μs的延时。当器件进入到深度功率降低模式时,不包括RP#缓冲器的所有的缓冲器被禁止,以及电流抽取是低的,例如,在3.3V VCC下50μA的最大值。在深度功率降低期间,加到RP#的输入必须保持在Vss。进入到RESET(复位)模式,清除状态寄存器134,以及把ISM 132设置为阵列读模式。

同步快闪存储器阵列结构被设计成允许扇区被擦除,而不打扰阵列的其余部分。阵列被划分成16个可寻址的“块”,它们是可独立地擦除的。通过擦除块,而不是整个阵列,总的器件耐久性被增强,作为系统灵活性。只有ERASE和BLOCK PROTECT功能是面向块的。16个可寻址的块被相等地划分成四个组104、106、108和110,每个组四个块。四个组具有同时读-写功能。对于任何组的ISM WRITE或ERASE操作可以与对任何其他组的READ操作同时进行。可以对状态寄存器134进行轮询,以确定哪个组处于ISM操作中。同步快闪存储器具有单个基础操作ISM,控制功率接通初始化、ERASE、WRITE、和PROTECT操作。在任何时间只可进行一个ISM操作;然而,某些其他命令,包括READ操作,可以在进行ISM操作的同时被执行。由ISM控制的操作命令被规定为组级操作或器件级操作。WRITE及ERASE为组级ISM操作。在ISM组操作被起动后,对组的任何位置的READ可能输出不正确的数据,而对任何其他组的READ将读出阵列。READ STATUS REGISTER命令将输出状态寄存器134的内容。ISM状态比特将表示,ISM操作何时完成(SR7=1)。当ISM操作完成时,组将自动进入阵列读模式。ERASE NVMODEREGISTER,WRITE NVMODE REGISTER,BLOCK PROTECT,DEVICE PROTECT,和UNPROTECT ALL BLOCK是器件级的ISM操作。一旦ISM器件级操作被起动,对任何组的READ将输出阵列的内容。READ STATUS REGISTER(读状态寄存器)命令可被发出,以确定ISM操作的完成。当SR7=1时,ISM操作将完成以及以后的ISM操作可被起动。任何块可以用硬件 电路保护,不受到不想要的ERASE或WRITE的影响,它要求RP#管脚在WRITE或ERASE开始之前被驱动到VHH,正如下面解释的。

任何块可被硬件保护,以提供对于固件的最敏感部分的额外保护。在WRITE或ERASE硬件保护的块期间,RP#管脚必须保持在VHH上,直至WRITE或ERASE完成为止。在不是RP#=VHH的情形下,对于保护的块的任何WRITE或ERASE企图将被阻止,以及将导致写或擦除错误。在位置0和15处的块可以具有附加的硬件保护,以阻止不利的WRITE或ERASE操作。在本实施例中,这些块不可以通过UNPROTECT ALL BLOCK命令被软件松开的,除非RP#=VHH。任何块的保护状态可以通过用READSTATUS REGISTER命令读出它的块保护比特而被检验。另外,为了保护一个块,必须与块地址一起发出三周期命令序列。

同步快闪存储器的特征在于,具有三种不同类型的READ。取决于模式,READ操作将从存储器阵列、状态寄存器、或器件配置寄存器之一产生数据。对器件配置寄存器或状态寄存器的READ必须在LCR-ACTIVE周期之后,以及输出数据的脉冲串长度将由模式寄存器设置值规定。以后的READ或不在LCR-ACTIVE周期之后的READ就读出阵列。然而,存在几个差别,并将在以下的节中被描述。

对任何组的READ命令输出存储器阵列的内容。在进行WRITE或ERASE ISM操作的同时,在ISM控制下对组中的任何位置的READ可能输出不正确的数据。在退出RESET操作后,器件将自动进入到阵列读模式。

对状态寄存器134进行的READ,要求与在读阵列时相同的输入顺序,除了LCR READ STATUS REGISTER(70H)周期必须在ACTIVE READ周期之前以外。状态寄存器数据输出的脉冲串长度由模式寄存器148规定。状态寄存器内容在经过CAS等待时间的下一个时钟上升沿被更新和锁存。器件将自动进入到阵列读模式,用于以后的READ。

对任何的器件配置寄存器136进行的READ,要求与在读状态寄存器时相同的输入顺序,除了必须发出特定的地址以外。WE#必须是HIGH(高电平),以及DQM和CS#必须是LOW(低电平)。为了读出制造商兼容性ID,地址必须是在000000H,以及为了读出器件ID,地址必须是在000001H。任何的块保护比特在每个擦除块内的第三地址(xx0002H)处被读出,而器件保护比特从位置000003H处被读出。

DQ管脚被使用来输入数据或用来输入阵列。地址管脚被使用来规定地址位置或在LOAD COMMAND REGISTER周期期间对CEL输入命令。命令输入把8比特命令发出到CEL,以便控制器件的工作模式。WRITE被使用来对存储器阵列输入数据。以下的节描述这两种输入类型。

为了执行命令输入,DQM必须是LOW,以及CS#和WE#必须是LOW。地址管脚或DQ管脚被使用来输入命令。不被使用于输入命令的地址管脚是“不用管它”的,以及必须保持为稳定的。8比特命令在DQ0-DQ7或A0-A7处被输入,以及在时钟上升沿处被锁存。

对存储器阵列的WRITE把想要的比特设置为逻辑0,但不能把给定的比特从逻辑0改变到逻辑1。把任何比特设置为逻辑1需要把整个块擦除。为了执行WRITE,DQM必须是LOW,CS#和WE#必须是LOW,以及VCCP必须保持在VCC。对保护的块的写入也要求RP#管脚保持在VHH。A0-A11提供要被写入的地址,而要被写入到阵列的数据在DQ管脚处被输入。数据和地址在时钟的上升沿被锁存。WRITE的前面必须有WRITESETUP命令。

为了简化写入存储器块,同步快闪存储器引用ISM,它在WRITE和ERASE周期内控制所有的内部算法。8比特命令组被使用来控制器件。对于正确的命令的清单,可参阅真值表1和2。

8比特ISM状态寄存器134(见表2)被轮询,以检验ERASE NVMODEREGISTER、WRITE NVMODE REGISTER、WRITE、ERASE、BLOCK PROTECT、DEVICE PROTECT、或UNPROTECT ALL BLOCK的完成或任何相关的错误。ISM操作的完成可以通过发出READ STATUS REGISTER(70H)命令而被监视。状态寄存器的内容被输出到DQ0-DQ7,以及在由模式寄存器设置值规定的、固定脉冲串长度内在下一个时钟上升沿(经过CAS等待时间)处被更新。ISM操作将在SR7=1时完成。所有的规定的比特由ISM设置,但仅仅ISM状态比特被ISM复位。擦除的/非保护的块,写入/保护的块,器件保护必须通过使用CLEAR STATUS REGISTER(50H)命令清除。这允许用户选择何时轮询和清除状态寄存器。例如,主系统可以在检验状态寄存器之前执行多个WRITE操作,而不是在每次单独的WRITE以后检验。坚持RP#信号或将器件功率降低也将清除状态寄存器。

表2 状态寄存器

| 状态比特 | 状态寄存器比特 | 说明 |

| SR7 | ISM状态 1=准备好 0=忙 | 当执行WRITE或BLOCK ERASE时,ISM比特 显示状态机的工作的状态。控制逻辑轮询这 个比特,以确定何时擦除和写入状态比特是 正确的。 |

| SR6 | 保留 | 保留供将来使用。 |

| SR5 | 擦除/非保护块的状态 1=块擦除或块非保护出错 0=成功的块擦除或非保护 | ES在最大数目的ERASE周期由ISM执行(但 不带有成功验证)后被设置为1。如果BLOCK UNPROTECT操作不成功,则这个比特也被设 置为1。ES只由CLEAR STATUS REGISTER命 令或由RESET(复位)清除。 |

| SR4 | 写入/保护块的状态 1=写入或块保护出错 0=成功的写入或块保护 | WS在最大数目的WRITE周期由ISM执行(但 不带有成功验证)后被设置为1。如果BLOCK 或DEVICE PROTECT操作不成功,则这个比 特也被设置为1。WS只由CLEAR STATUS REGISTER命令或由RESET(复位)清除。 |

| SR2 SR1 | 组A1 ISM状态 组A0 ISM状态 | 当SR0=0时,在ISM控制下的组可以从BA0, BA1:[0,0]组0;[0,1]组1;[1,0]组2;[1,1] 组3中译码。 |

| SR3 | 器件保护状态 1=被保护的、企图进行不 正确的操作的器件 0=非保护的或满足 RP#条 件的器件 | 如果试图进行不正确的WRITE,ERASE, PROTECT BLOCK,PROTECT DEVICE 或 UNPROTECT ALL BLOCKS,则DPS被设置为1。 在这些命令之一被发出后,把RP#,块保护比 特和器件保护比特的条件进行比较,以确定 是否允许想要的操作。必须由CLEAR STATUS REGISTER命令或由RESET清除。 |

| SR0 | 器件/组ISM状态 1=器件级ISM操作 0=组级ISM操作 | 如果ISM操作是器件级操作,则DPS被设置 为1。对于阵列的任何的组的正确的READ 可紧接跟随在器件级的ISM WRITE操作后 面。当DBS被设置为0时,ISM操作是组级 操作。在ISM控制下对组的READ可能导致 不正确的数据。SR2和SR3可被译码,以确 定哪个组是在ISM控制下。 |

器件ID、制造商兼容性ID、器件保护状态和块保护状态都可通过发出READ DEVICE CONFIGURATION(90H)命令而被读出。为了读想要的寄存器,必须坚持特定的地址。对于各种器件配置寄存器136的更多的细节,可参阅表3。

表3 器件配置

| 器件配置 | 地址 | 数据 | 条件 |

| 制造商兼容性 | 000000H | 2CH | 读出制造商兼容性 |

| 器件ID | 000001H | D3H | 读出器件ID |

| 块保护比特 | xx0002H xx0002H | DQ0=1 DQ0=0 | 块被保护 块未被保护 |

| 器件保护比特 | 000003H 000003H | DQ0=1 DQ0=0 | 阻止进行块保护修正 允许进行块保护修正 |

可发出命令,以使器件进入不同的操作模式。每个模式具有特定的操作,这些操作可在该模式下被执行。几种模式要求一系列命令在它们到达之前被写入。以下的节描述每个模式的性质,真值表1和2列出对于执行想要的操作所需要的所有的命令序列。读-写功能允许对于任何组执行基础操作写或擦除,而同时读出任何其他组。对于写操作,在真值表2中的LCR-ACTIVE-WRITE命令序列必须在接连的时钟周期内完成。然而,为了简化同步快闪控制器操作,在命令序列中可以发出没有限制的数目的NOP或COMMAND INHIBIT。为了附加保护,在三个周期内,这些命令序列必须具有相同的组地址。如果在LCR-ACTIVE-WRITE命令序列期间组地址改变,或如果命令序列不是接续的(除了NOP和COMMAND INHIBIT以外,它们是许可的),写和擦除状态比特(SR4和SR5)将被设置,以及操作被禁止。

在功率接通以后和在对器件发出任何工作命令以前,同步快闪存储器被初始化。在功率被加到VCC、VCCQ和VCCP(同时地)以及时钟是稳定以后,RP#从LOW转移到HIGH。在RP#转移到HIGH以后,需要一个延时(在一个实施例中,100μs的延时),以便完成内部器件初始 化。在完成器件初始化时器件处在阵列读模式,以及可执行的命令可被发出到器件。

为了读出器件ID、制造商兼容性ID、器件保护比特和每个块保护比特,发出READ DEVICE CONFIGURATION(90H)命令。在这个模式下,特定的地址被发出来读出想要的信息。制造商兼容性ID在000000H处被读出;器件ID在000001H处被读出。制造商兼容性ID和器件ID在DQ0-DQ7处输出。器件保护比特在000003H处被读出;以及每个块保护比特在每个块内的第三地址位置(xx0002H)处被读出。器件和块保护比特在DQ0处输出。

需要在接连的时钟边沿处的三个接连的命令来把数据输入到阵列(NOP和COMMAND INHIBIT许可处在周期之间)。在第一周期,利用在A0-A7处的WRITE SETUP(40H)给出LOAD COMMAND REGISTER命令,以及组地址在BA0、BA1上被发出。下一个命令是ACTIVE,它激活行地址和确认组地址。第三周期是WRITE,在此期间发布开始的列、组地址、和数据。ISM状态比特在接着的时钟边沿(经过CAS等待时间)处被设置。在ISM执行WRITE时,ISM状态比特(SR7)将是0。在ISM控制下对组的READ操作可能产生不正确的数据。当ISM状态比特(SR7)被设置为逻辑1时,WRITE被完成,以及组将处在阵列读模式,并准备好可执行的命令。写入到硬件保护的块,也要求RP#管脚在第三周期(WRITE)之前被设置为VHH,以及RP#必须保持在VHH,直至ISM WRITE操作完成为止。如果LCR-ACTIVE-WRITE命令序列没有在接连的周期完成或组地址在三个周期的任一个内改变,则写和擦除状态比特(SR4和SR5)被设置。在ISM起动WRITE后,它不能被中断,除了由RESET或通过功率降低这个部件以外。在WRITE期间这样做,可能打乱被写入的数据。

执行ERASE序列将把块内的所有的比特设置为逻辑1。对于执行ERASE所必须的命令序列类似于WRITE的命令序列。为了提供对于偶然块擦除的附加安全性,需要在接连的时钟边沿处的三个接连的命令来起动块的ERASE。在第一周期,把A0-A7处的ERASE SETUP(20H)发布给LOAD COMMAND REGISTER,以及要被擦除的块的组地址在BA0,BA1上被发出。下一个命令是ACTIVE,其中A10,A11,BA0,BA1提供要被擦除的块的地址。第三周期是WRITE,在此期间在DQ0-DQ7处给出ERASE CONFIRM(DOH),以及重新发布组地址。ISM状态比特在接着的时钟边沿(经过CAS等待时间)处被设置。在ERASE CONFIRM(D0H)被发布后,ISM将开始所寻址的块的ERASE。对于其中存在所寻址的块的组的任何的READ操作可能输出不正确的数据。当ERASE操作完成时,该组处在阵列读模式,并准备好可执行的命令。擦除被硬件保护的块,也要求RP#管脚在第三周期(WRITE)之前被设置为VHH,以及RP#必须保持在VHH,直至ERASE完成(SR7=1)为止。如果LCR-ACTIVE-WRITE命令序列没有在接连的周期完成(NOP和COMMAND INHIBIT许可处在周期之间)或组地址在一个或多个命令周期内改变,则写和擦除状态比特(SR4和SR5)将被设置,以及操作被禁止。

模式寄存器148的内容可以用WRITE NVMODE REGISTER命令被复制到NV模式寄存器147中。在写入到NV模式寄存器之前,ERASE NVMODEREGISTER命令序列必须被完成,以便把NV模式寄存器中所有的比特设置为逻辑1。为了执行ERASE NVMODE REGISTER和WRITE NVMODEREGISTER所必须的命令序列类似于WRITE的命令序列。对于完成ERASENVMODE REGISTER和WRITE NVMODE REGISTER所必须的LCR-ACTIVE-WRITE命令的更多的信息可参阅真值表2。在ERASE NVMODEREGISTER或WRITE NVMODE REGISTER命令序列的WRITE周期被登记后,READ命令可被发出到阵列。在当前的ISM操作被完成和SR7=1之前,将不允许新的WRITE操作。

执行BLOCK PROTECT序列,对于给定的块允许进行第一级的软件/硬件保护。存储器包括16比特寄存器,它具有相应于16个可保护的块的一个比特。存储器也具有寄存器,以提供被使用来保护整个器件不受到写入和擦除操作的器件比特。为了执行BLOCK PROTECT所必须的命令序列类似于WRITE的命令。为了提供对于偶然块保护的附加安全性,需要三个接连的命令周期来起动BLOCK PROTECT。在第一周期,把A0-A7处的PROTECT SETUP(60H)命令发布给LOAD COMMAND REGISTER,以及要被保护的块的组地址在BA0、BA1上被发出。下一个命令是ACTIVE,它起动在要保护的块中的行,以及确认组地址。第三周期是WRITE,在此期间在DQ0-DQ7处发布BLOCK PROTECT CONFIRM(01H),以及重新发布组地址。ISM状态比特在接着的时钟边沿(经过CAS等待时间)处被设置。ISM将开始保护操作。如果LCR-ACTIVE-WRITE没有 在接连的周期完成(NOP和COMMAND INHIBIT许可处在周期之间)或组地址改变,则写和擦除状态比特(SR4和SR5)将被设置,以及操作被禁止。当ISM状态比特(SR7)被设置为逻辑1时,PROTECT已完成,以及该组将处在阵列读模式,并准备好可执行的命令。一旦块保护比特被设置为1(保护的),它只能被复位为0,如果UNPROTECT ALL BLOCKS命令的话。UNPROTECT ALL BLOCKS命令序列类似于BLOCK PROTECT命令;然而,在第三周期,利用UNPROTECT ALL BLOCKS COMFIRM(D0H)命令发出WRITE,以及地址是“不用管它”。对于附加信息,参阅真值表2。在位置0和15处的块具有附加安全性。一旦在位置0和15处的块保护比特被设置为1(保护的),每个比特就只能被复位为0,如果RP#在UNPROTECT操作的第三周期之前被加到VHH,以及保持在VHH,直至操作完成(SR7=1)为止。另外,如果器件保护比特被设置,则RP#必须在第三周期之前被加到VHH,及保持在VHH,直至BLOCK PROTECT或UNPROTECT ALL BLOCKS操作完成为止。为了检验块的保护状态,可以发出READ DEVICE CONFIGURATION(90H)命令。

执行DEVICE PROTECT序列,把器件保护比特设置为1,以及阻止块保护比特修正。为了执行DEVICE PROTECT所必须的命令序列类似于WRITE的命令。需要三个接连的命令周期来起动DEVICE PROTECT序列。在第一周期,把A0-A7处的PROTECT SETUP(60H)命令发布给LOADCOMMAND REGISTER,以及组地址在BA0、BA1上被发出。组地址是“不用管它”,但相同的组地址必须在所有的三个周期内被使用。下一个命令是ACTIVE。第三周期是WRITE,在此期间在DQ0-DQ7处发布DEVICEPROTECT(F1H),以及RP#被加到VHH。ISM状态比特在接着的时钟边沿(经过CAS等待时间)处被设置。可执行的命令可被发布到器件。RP#必须保持在VHH,直至WRITE完成(SR7=1)为止。在当前的ISM操作完成前,将不允许新的WRITE操作。一旦器件保护比特被设置,它就不能被复位到0。对于器件保护比特被设置为1,BLOCK PROTECT或BLOCKUNPROTECT被阻止,除非RP#在任一个操作期间处在VHH。器件保护比特不影响WRITE或ERASE操作。对于块和器件保护操作的更多的信息,可参阅表4。

表4 保护操作真值表

在ISM状态比特(SR7)被设置后,器件/组(SR0)、器件保护(SR3)、组A0(SR1)、组A1(SR2)、写/保护块(SR4)和擦除/非保护(SR5)状态比特可被检验。如果SR3、SR4、SR5状态比特之一或组合被设置,则在操作期间出现错误。ISM不能复位SR3、SR4或SR5比特。为了清除这些比特,必须给出CLEAR STATUS REGISTER(50H)命令。表5列出错误的组合。

表5 状态寄存器错误译码

同步快闪存储器被设计和被制造,满足先进的代码和数据存储要求。为了确保这个可靠性级,VCCP在WRITE或ERASE期间必须保持为Vcc。在这些限制以外的操作可以减小可对器件执行的WRITE和ERASE周期的数目。每个块是对于100,000WRITE/ERASE周期的耐久性的最小值被设计和被处理的。

同步快闪存储器提供可以在阵列读模式下被利用来节省功率的几个功率节省特性。深度功率降低模式可以通过把RP#加到VSS±0.2V而被允许。在这个模式下的电流抽取(ICC)是低的,诸如50μA的最大值。当CS#是HIGH时,器件将进入工作等待模式。在这个模式下,电流也是低的,诸如30mA的最大ICC电流。如果在写、擦除、或保护操作期间CS#被加到HIGH,则ISM将继续WRITE操作,以及器件消耗工作的Iccp功率,直至操作完成为止。

参照图16,图上表示按照本发明的一个实施例的自定时写序列的流程图。序列包括装载命令寄存器(代码40H)、接受工作的命令和行地址、以及接受写命令和列地址。然后,序列提供状态寄存器轮询,以确定写入是否完成。该轮询监视状态寄存器比特7(SR7),以确定它是否被设置为1。可以包括可任选的状态检验。当写入完成时,阵列被置于阵列读模式。

参照图17,图上提供了按照本发明的一个实施例的完全的写状态-检验序列的流程图。该序列查看状态寄存器比特4(SR4),以确定它是否被设置为0。如果SR4是1,则在写操作中有错误。序列也查看状态寄存器比特3(SR3),以确定它是否被设置为0。如果SR3是1,则在写操作期间有不正确的写错误。

参照图18,图上提供按照本发明的一个实施例的自定时块擦除序列的流程图。该序列包括装载命令寄存器(代码20H),以及接受工作的命令和行地址。存储器然后确定块是否被保护。如果它不被保护,则存储器对该块执行写操作(D0H),以及对于完成情形监视状态寄存器。可以执行任选的状态检验,以及存储器被置于阵列读模式。如果块是保护的,则不允许擦除,除非RP#信号处在提高了的电压(VHH)。

图19表示按照本发明的一个实施例的完全的块擦除状态-检验序列的流程图。该序列监视状态寄存器,以确定是否出现命令序列错 误(SR4或SR5=1)。如果SR3被设置为1,则出现不正确的擦除或非保护的错误。最后,如果SR5被置为1,则发生块擦除或非保护错误。

图20是按照本发明的一个实施例的块保护序列的流程图。该序列包括装载命令寄存器(代码60H),以及接受工作的命令和行地址。存储器然后确定块是否被保护。如果它不被保护,则存储器对该块执行写操作(01H),以及对于完成情形监视状态寄存器。可以执行任选的状态检验,以及存储器被置于阵列读模式。如果块是保护的,则不允许擦除,除非RP#信号处在提高了的电压(VHH)。

参阅图21,图上提供了按照本发明的一个实施例的完全的块状态-检验序列的流程图。该序列监视状态寄存器比特3、4、和5,以确定是否检测到错误。

图22是按照本发明的一个实施例的器件保护序列的流程图。该序列包括装载命令寄存器(代码60H),以及接受工作的命令和行地址。存储器然后确定RP#是否处在VHH。存储器执行写操作(F1H),以及对于完成情形监视状态寄存器。可以执行任选的状态检验,以及存储器被置于阵列读模式。

图23是按照本发明的一个实施例的块非保护序列的流程图。该序列包括装载命令寄存器(代码60H),以及接受工作的命令和行地址。存储器然后确定该存储器件是否被保护。如果它不被保护,则存储器确定引导位置(块0和15)是否被保护。如果没有一个块被保护,则存储器对该块执行写操作(D0H),以及对于完成情形监视状态寄存器。可以执行任选的状态检验,以及存储器被置于阵列读模式。如果器件是保护的,则不允许擦除,除非RP#信号处在提高了的电压(VHH)。同样地,如果引导位置是保护的,则存储器确定是否所有的块应当是不保护的。

图24显示初始化和装载模式寄存器运行的时序。模式寄存器通过接受装载模式寄存器命令和在地址线上接受工作代码(操作码)而被编程。把运行码装入该模式寄存器中。如上所述,在功率接通后,非易失性模式寄存器的内容被自动地装载到模式寄存器,以及不一定需要模式寄存器操作。

图25表示时钟中止模式操作的时序,以及图26表示另一个脉冲串读操作的时序。图27表示交替的组读出访问的时序。这里,需要工 作的命令来改变组地址。图28上表示全页脉冲串读操作。应当指出,完全页脉冲串不是自终结的,而需要终结的命令。

图29通过使用数据屏蔽信号表示读操作的时序。DQM信号被使用来屏蔽数据输出,这样,在DQ连接上不提供Dout m+1。

参照图30,图上表示写操作的时序,后面跟随对不同的组的读出。在这个操作中,对组a执行写操作,以及对组b执行随后的读出。在每个组中访问同一个行。

参照图31,图上表示写操作的时序,后面跟随对同一个组的读出。在这个操作中,对组a执行写操作,以及对组a执行随后的读出。对于读操作访问不同的行,以及存储器必须等待先前的写操作被完成。这是与图30的读操作不同的,其中读操作并不由于写操作而被延时。

同步快闪存储器提供没有等待时间的写操作。这是与SDRAM不同的,SDRAM要求系统提供对于写操作的等待时间,就像读操作那样。所以写操作并不从系统总线中取走与SDRAM花费的一样多的周期。因此,可改进系统读通过量,见图12,其中写入的数据Din在与写命令和列地址同一个时钟周期上被提供。图12的时钟周期T1不需要是NOP命令(见图30)。读命令可以在跟随在写数据后面的下一个时钟周期上被提供。因此,虽然读操作需要DQ连接在读命令后的预定的数目的时钟周期内(等待时间)保持为可以得到的,但DQ连接可以紧接在写命令被提供后(没有等待时间)被使用。这样,本发明允许零总线换向能力。这是大大地不同于SDRAM的,在SDRAM中当在读和写操作之间交替时在系统总线上需要大量等待。同步快闪存储器提供这两个特性,以及可提高总线通过量。

参照图32,本发明的系统32包括同步存储器302,它具有内部的写锁存器304,被使用来存储在DQ输入端306上接受的写数据。写锁存器被耦合到存储器阵列310。另外,存储器阵列可被安排成多个可寻址的块。数据可被写入到一个块,而同时可对其他的块执行读操作。阵列的存储单元可以是非易失性存储单元。数据通信连接306被使用于与外部设备(诸如处理器320或其他存储器控制器)的双向通信。

数据缓冲器330可被耦合到数据通信连接,以便管理双向数据通信。这个缓冲器可以是传统的FIFO或流水线的输入/输出缓冲器电路。 写锁存器被耦合在缓冲器与存储器阵列之间,以便锁存在数据通信连接上提供的数据。最后,控制电路被提供来管理在阵列上执行的读和写操作。

通过锁存输入写数据,数据总线306(DQ)可被释放以及通过使用锁存的数据执行写操作。在执行第一写操作的同时,随后的、对存储器的写操作可被禁止。然而,可以得到总线,以便在存储器上立刻执行读操作。本发明不应当与传统的输入/输出缓冲器结构混淆。也就是,虽然现有的存储器器件使用在DQ输入路径上的输入缓冲器和在DQ输出路径上的输出缓冲器,但是用于读和写操作的时钟等待时间被保持为相同的。本发明可包括输入/输出缓冲器电路来提供与DQ路径和外部处理器的接口。附加的写锁存器允许存储器来隔离对存储器的一个区域的写路径/操作,而同时允许在其他存储器区域上的数据读操作。

现有的快闪存储器器件具有非常有限的同时操作能力。也就是,现有的快闪存储器典型地在执行写操作的同时,阻碍从存储器的读出。某些存储器器件通过中止正在进行的写操作、然后允许对阵列的读出,而允许写入的同时进行读出。另外的快闪存储器通过提供有限的扇区、这些扇区可被写入而存储器的其余部分可供读出使用,而允许写入的同时进行读出。这样的快闪存储器的目的是消除系统中对于分开的EEPROM的需要。有限的扇区空间提供在快闪存储器中的EEPROM单元,以及留下存储器的其余部分用于快闪操作。

本发明提供被安排成类似于SDRAM的组结构的快闪阵列。在一个实施例中,64M的同步快闪存储器被划分成四个组,它们具有与64MSDRAM相同的寻址。这些组被进一步分成更小的可寻址的扇区,它们可被擦除或被编程。存储器允许基于组的同时的读和写。因此,一个组可被写入,而同时可以对任何其他的组执行同时读出。

正如本领域技术人员已知的,SDRAM可以在每个组打开一个公共的行。读和写操作可以在打开的行和跨过阵列的组上顺序地执行。

本同步快闪存储器具有类似于SDRAM的组结构,允许在一个组被写入的同时在每个组中打开一行。参照图33,图上表示本发明的处理系统400的一个实施例。同步快闪存储器410通过双向数据总线435被耦合到多个处理器440,442,444和446。存储器包括被排列成多个组412,414,416和418的非易失性存储单元的阵列。一般地示出读/ 写电路430以便管理与阵列的数据通信。在操作时,处理器,诸如处理器440,可起动对于阵列组412的行420的写操作。在执行写操作时,第二处理器,诸如处理器442,可以从第二阵列组的行420中读出数据。这允许四个处理器在同步快闪存储器上独立地工作。本发明并不限于四个组或四个处理器。单个或多个处理器可对于一个组执行写操作,而同时从其余的存储器阵列组读出数据,例如见图32。因此,可以同时进行写操作和多个同时的读操作。

如上所述,本发明的同步快闪存储器可以执行组特定的读操作,而同时对另一个组执行写操作。当第一和第二个外部处理器试图对存储器读和写时,出现一个问题。也就是,如果处理器试图对同一个存储器块执行操作,则这两个处理器需要知道,正在对存储器执行哪些操作,以避免竞争。在现有的系统中,总线主机被使用来跟踪由多个处理器执行的同时操作。为了减小总线主机的开销,可以提供两个任选项。

一个任选项是在存储器中包括自动读状态模式,它在试图对存储器执行第二操作时输出状态寄存器的内容。也就是,当对存储器执行写操作时,在存储器上执行的任何读操作会输出状态寄存器的内容。这个任选项通过输出状态数据而中断读操作,即使是试图对不同的阵列块执行读操作。第二个任选项是要求处理器读出状态寄存器来确定存储器的写状态。利用这个任选项再次中断读操作。

本发明可提供两个状态读出模式,来避免在对于不同的阵列组的同时读操作时的干扰。在本同步快闪存储器中提供的第一状态模式提供整个存储器器件的状态。也就是,状态寄存器表示是否正在对存储器阵列或非阵列寄存器执行写操作。这个状态模式,在这里被称为存储器状态模式,由来自外部处理器的请求而被选择地激活。响应于存储器状态命令,存储器的控制电路在DQ连接上提供状态寄存器数据。

第二状态模式是存储器阵列组特定的模式。在这个模式下,状态数据被自动地提供在DQ连接上。也就是,如果处理器对于阵列组起动写操作,则该组被置于组状态模式。在写操作正在被执行的同时,任何以后的、从该组读出的企图导致在DQ连接上输出状态寄存器数据。因此,存储器控制电路允许多处理器系统互相不干扰地一起工作。

存储器包括组寄存器450(图33),它可被设置来识别哪个阵列组 正在被写入。在操作时,存储器对组寄存器进行编程,以及使用组寄存器作为指针。在读操作期间,把读访问与组寄存器进行比较,以及如果在该组地址处有正在进行的写操作,则存储器自动输出状态寄存器数据。所以,本发明可以减小总线主机的开销,因此,可以允许更好的多处理器能力。

单个脉冲串状态

如上所述,现有的快闪存储器包括单个状态读操作。在这些存储器中,一旦存储器进入写模式,从存储器读出的任何企图都提供状态寄存器的内容。这允许用户监视写操作如何在进行。

本发明具有状态读模式,它用状态读命令输出来自状态寄存器的数据。而且,同步快闪存储器可以通过使用装载命令寄存器操作被编程,以建立脉冲串长度和时钟等待时间。这些设置值主要在读操作期间被使用来控制输出数据的时序。现有的快闪存储器其间的问题是,输出的寄存器数据没有为受控的脉冲串长度和等待时间的输出作好准备。

本存储器可被置于寄存器读模式,以及在一系列时钟周期(脉冲串)内输出寄存器数据。脉冲串的长度通过对模式寄存器进行编程而被预先规定,正如以上说明的。例如,模式寄存器可被设置为具有4个字的脉冲串长度和3的时钟等待时间。在接受到状态寄存器读命令后,由于时钟等待时间,本存储器在3个时钟周期后输出状态寄存器内容,以及由于脉冲串长度设置值,在4个周期内在总线(DQ连接)上继续输出状态寄存器内容。寄存器读操作不限于状态寄存器读数,也可应用于读出器件识别寄存器、制造商识别寄存器、或用来存储操作数据的任何多个工作寄存器。

通过使用脉冲串长度和时钟等待时间设置值来控制寄存器数据输出可减小在存储器器件中进行写操作的同时读出时的混淆。例如,如果用户需要知道在存储器器件中操作的状态,则可以起动读状态命令,以及状态寄存器数据在全脉冲串长度内被输出。

结论

同步快闪存储器包括非易失性存储单元的阵列。存储器阵列被排列成行和列,以及可被进一步排列成可寻址的块。数据通信连接被使用来与外部设备(诸如,处理器或其他存储器控制器)进行双向数据 通信。存储器可以在一系列时钟周期期间在数据通信连接上输出来自存储寄存器的数据,以提供寄存器数据的脉冲串。存储器还可以按照规定的时钟等待时间值提供寄存器数据。寄存器数据可包括状态数据、操作设置值数据、制造识别、和存储器器件识别。

Claims (38)

1.一种操作存储器器件的方法,包括:

为所述存储器器件设置脉冲串长度;

为所述存储器器件设置时钟等待时间周期,以及

响应于在写操作期间接收的读寄存器命令控制来自寄存器的数据输出。

2.权利要求1的方法,其中脉冲串长度和时钟等待时间被存储在模式寄存器中。

3.权利要求1的方法,其中控制数据输出还包括在所述存储器器件的数据通信连接上从所述寄存器输出。

4.权利要求1的方法,其中:

操作所述存储器器件还包括使用脉冲串长度设置和时钟等待时间设置对状态读寄存器进行编程;并且其中

输出存储器器件状态还包括

将存储器置于状态寄存器读模式;以及

根据状态读寄存器编程,对于一系列时钟周期,从所述状态读寄存器输出非阵列数据;

其中所述状态读寄存器允许外部处理器在写入、擦除和保护操作期间监视内部状态机的状态,并且其中模式寄存器被用于限定所述存储器器件的特定操作,包括选择脉冲串长度、脉冲串类型、CAS等待时间和工作模式中的至少一个。

5.权利要求4的方法,其中输出还包括:

使用编程的脉冲串长度设置和时钟等待时间设置控制状态读寄存器数据输出。

6.权利要求4的方法,还包括:

在状态读命令开始时提供来自所述状态读寄存器的存储器状态信号。

7.权利要求4的方法,其中所述脉冲串长度设置是四个字并且所述时钟等待时间设置是三个周期。

8.权利要求1的方法,其中设置脉冲串长度和设置时钟等待时间周期还包括:

在模式寄存器中存储所述脉冲串长度和所述时钟等待时间周期,并且使用存储在所述模式寄存器中的所述脉冲串长度和所述时钟等待时间对所述存储器器件进行编程。

9.权利要求8的方法,其中控制数据输出还包括:

当在存储器操作运行时接收到状态请求时,基于接收到所述状态请求输出存储器器件状态,其中在对应于所述脉冲串长度的多个时钟周期上执行输出。

10.权利要求8的方法,还包括在接收到所述状态请求后延迟输出所述存储器器件状态所述时钟等待时间周期。

11.权利要求8的方法,其中输出存储器器件状态还包括在存储器操作期间从状态寄存器输出内部状态机的状态。

12.权利要求1或8的任何一个的方法,其中对脉冲串长度进行编程包括建立x个周期的读脉冲串长度。

13.权利要求1或8的任何一个的方法,其中对时钟等待时间进行编程包括建立y个周期的时钟等待时间。

14.权利要求1或8的任何一个的方法,其中控制数据输出还包括在x个接连的时钟周期上从所述存储器器件输出数据。

15.权利要求13的方法,还包括在接收到所述状态请求后延迟输出所述存储器器件状态所述时钟等待时间周期。

16.权利要求15的方法,还包括:

在接收寄存器读命令之后延迟来自寄存器的数据输出所述时钟等待时间周期。

17.权利要求16的方法,其中控制数据输出还包括使用模式寄存器来限定所述存储器器件的特定操作,包括选择脉冲串长度、脉冲串类型、时钟等待时间周期和工作模式中的至少一个。

18.权利要求17的方法,还包括在写入、擦除和保护操作期间监视所述存储器器件的状态寄存器,所述状态寄存器在存储器工作期间输出内部状态机的状态。

19.一种存储器器件,包括:

存储器单元阵列;

寄存器;

时钟信号输入连接;和

控制电路,响应于寄存器读命令在输出连接上提供来自所述寄存器的数据,所述控制电路适于执行用于输出数据的方法,包括:

为将从所述寄存器输出的数据设置脉冲串长度;

为将从所述寄存器输出的数据设置时钟等待时间周期;以及

响应于在存储器器件工作期间正被接收的读寄存器命令控制来自所述寄存器的数据输出。

20.权利要求19的存储器器件,其中所述控制电路还适于设置x个周期的脉冲串长度。

21.权利要求20的存储器器件,其中所述控制电路还适于在x个接连的时钟周期从所述寄存器输出数据。

22.权利要求20的存储器器件,其中所述控制电路还适于在接收到读寄存器命令后延迟来自所述寄存器的输出所述时钟等待时间周期。

23.权利要求22的存储器器件,其中所述控制电路还适于使用模式寄存器来限定所述存储器器件的特定操作,包括选择脉冲串长度、脉冲串类型、时钟等待时间周期和工作模式中的至少一个。

24.权利要求23的存储器器件,其中所述控制电路还适于在写入、擦除和保护操作期间监视存储器器件的状态寄存器,所述状态寄存器在存储器工作期间包含内部状态机的状态。

25.权利要求19的存储器器件,其中所述控制电路还适于在所述存储器器件的数据通信连接上从所述寄存器输出。

26.一种用于操作存储器器件的方法,所述方法包括:

对所述存储器器件的阵列执行写操作;

在写操作的执行期间在第一时钟周期向所述存储器器件的输入提供寄存器数据的状态寄存器读命令;以及

在多个时钟周期期间在所述存储器器件的数据通信连接上接收状态寄存器数据,其中在提供所述状态寄存器读命令后延迟接收所述寄存器数据预定的时钟等待时间周期。

27.权利要求26的方法,其中所述多个时钟周期包括四个字并且所述多个时钟周期基本上为三个周期。

28.权利要求26的方法,还包括接收所述多个时钟周期和所述预定的时钟等待时间周期。

29.权利要求26的方法,其中执行写操作、提供寄存器读命令和接收寄存器数据是由耦合到所述存储器器件的处理器实现的。

30.权利要求26的方法,还包括接收操作数据、状态日期、制造商标识和存储器器件标识。

31.权利要求26的方法,其中写操作能够在一组阵列上执行,同时从剩余的存储器阵列组读取数据。

32.权利要求31的方法,其中所述存储器器件能够执行一组特定的读操作,同时在其它组上执行写操作。

33.一种用于在具有处理器的系统中操作存储器器件的方法,所述方法包括:

设置所述存储器器件的脉冲串长度以限定输出寄存器数据的多个时钟周期;

设置时钟等待时间周期;

在所述存储器器件上执行写操作;

在所述写操作的执行期间在所述存储器器件上执行寄存器数据的寄存器读命令;以及

在脉冲串长度期间在所述存储器器件的数据通信连接上接收寄存器数据的脉冲串,其中在提供所述寄存器读命令后延迟接收寄存器数据的脉冲串等于所述时钟等待时间周期的时间。

34.权利要求33的方法,其中所述时钟等待时间周期是从2,4,8或16个时钟周期选择的。

35.权利要求33的方法,其中所述寄存器数据包括操作数据,状态数据,制造商标识或存储器器件标识之一。

36.权利要求33的方法,其中所述处理器通过双向数据通信总线与所述存储器器件进行通信。

37.权利要求33的方法,其中所述多个时钟周期包括四个字并且所述多个时钟周期是基本上三个周期。

38.权利要求33的方法,其中所述存储器器件是包括具有非易失性存储器单元的存储器阵列的闪存储器器件。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/626,190 US6728798B1 (en) | 2000-07-28 | 2000-07-28 | Synchronous flash memory with status burst output |

| US09/626190 | 2000-07-28 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN01816420A Division CN100578659C (zh) | 2000-07-28 | 2001-07-27 | 具有状态脉冲串输出的同步快闪存储器 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN101930794A true CN101930794A (zh) | 2010-12-29 |

Family

ID=24509337

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2009102217820A Pending CN101930794A (zh) | 2000-07-28 | 2001-07-27 | 具有状态脉冲串输出的同步快闪存储器 |

| CN01816420A Expired - Fee Related CN100578659C (zh) | 2000-07-28 | 2001-07-27 | 具有状态脉冲串输出的同步快闪存储器 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN01816420A Expired - Fee Related CN100578659C (zh) | 2000-07-28 | 2001-07-27 | 具有状态脉冲串输出的同步快闪存储器 |

Country Status (9)

| Country | Link |

|---|---|

| US (4) | US6728798B1 (zh) |

| EP (1) | EP1305804B1 (zh) |

| JP (1) | JP3809909B2 (zh) |

| KR (1) | KR100511820B1 (zh) |

| CN (2) | CN101930794A (zh) |

| AT (1) | ATE492880T1 (zh) |

| AU (1) | AU2001277210A1 (zh) |

| DE (2) | DE60143700D1 (zh) |

| WO (1) | WO2002011148A1 (zh) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103403805A (zh) * | 2011-03-23 | 2013-11-20 | 株式会社东芝 | 半导体存储装置及其控制方法 |

| CN104951402A (zh) * | 2014-03-26 | 2015-09-30 | 三星电子株式会社 | 存储装置及其操作方法和计算系统 |

| CN104981873A (zh) * | 2013-03-12 | 2015-10-14 | 桑迪士克科技股份有限公司 | 在发送写入数据到存储器的同时从存储器读取数据的系统和方法 |

Families Citing this family (49)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6728798B1 (en) * | 2000-07-28 | 2004-04-27 | Micron Technology, Inc. | Synchronous flash memory with status burst output |

| US20030204675A1 (en) * | 2002-04-29 | 2003-10-30 | Dover Lance W. | Method and system to retrieve information from a storage device |

| JP4010400B2 (ja) * | 2002-06-14 | 2007-11-21 | シャープ株式会社 | 半導体記憶装置およびデータ書き込み制御方法 |

| US7149824B2 (en) * | 2002-07-10 | 2006-12-12 | Micron Technology, Inc. | Dynamically setting burst length of memory device by applying signal to at least one external pin during a read or write transaction |

| US7254690B2 (en) * | 2003-06-02 | 2007-08-07 | S. Aqua Semiconductor Llc | Pipelined semiconductor memories and systems |

| US8122187B2 (en) * | 2004-07-02 | 2012-02-21 | Qualcomm Incorporated | Refreshing dynamic volatile memory |

| CN100530146C (zh) * | 2004-08-26 | 2009-08-19 | 鸿富锦精密工业(深圳)有限公司 | Bios在线烧录方法 |

| US20060143330A1 (en) * | 2004-12-23 | 2006-06-29 | Oliver Kiehl | Method for data transmit burst length control |

| US7640392B2 (en) | 2005-06-23 | 2009-12-29 | Qualcomm Incorporated | Non-DRAM indicator and method of accessing data not stored in DRAM array |

| US7230876B2 (en) * | 2005-02-14 | 2007-06-12 | Qualcomm Incorporated | Register read for volatile memory |

| US7620783B2 (en) * | 2005-02-14 | 2009-11-17 | Qualcomm Incorporated | Method and apparatus for obtaining memory status information cross-reference to related applications |

| KR100762259B1 (ko) | 2005-09-12 | 2007-10-01 | 삼성전자주식회사 | 버스트 읽기 레이턴시 기능을 갖는 낸드 플래시 메모리장치 |

| US9262326B2 (en) * | 2006-08-14 | 2016-02-16 | Qualcomm Incorporated | Method and apparatus to enable the cooperative signaling of a shared bus interrupt in a multi-rank memory subsystem |

| US7904639B2 (en) * | 2006-08-22 | 2011-03-08 | Mosaid Technologies Incorporated | Modular command structure for memory and memory system |

| US7593279B2 (en) * | 2006-10-11 | 2009-09-22 | Qualcomm Incorporated | Concurrent status register read |

| KR101364443B1 (ko) * | 2007-01-31 | 2014-02-17 | 삼성전자주식회사 | 메모리 시스템, 이 시스템을 위한 메모리 제어기와 메모리,이 시스템의 신호 구성 방법 |

| US8086785B2 (en) | 2007-02-22 | 2011-12-27 | Mosaid Technologies Incorporated | System and method of page buffer operation for memory devices |

| WO2008101316A1 (en) | 2007-02-22 | 2008-08-28 | Mosaid Technologies Incorporated | Apparatus and method for using a page buffer of a memory device as a temporary cache |

| KR100813631B1 (ko) * | 2007-03-19 | 2008-03-14 | 삼성전자주식회사 | 읽기 성능을 향상시킬 수 있는 플래시 메모리 장치 |

| WO2009050806A1 (ja) * | 2007-10-18 | 2009-04-23 | Fujitsu Limited | 記憶装置、データ伝送方法及び伝送制御回路 |

| US9354890B1 (en) | 2007-10-23 | 2016-05-31 | Marvell International Ltd. | Call stack structure for enabling execution of code outside of a subroutine and between call stack frames |

| CN101903953B (zh) | 2007-12-21 | 2013-12-18 | 莫塞德技术公司 | 具有功率节省特性的非易失性半导体存储器设备 |

| US8291248B2 (en) | 2007-12-21 | 2012-10-16 | Mosaid Technologies Incorporated | Non-volatile semiconductor memory device with power saving feature |

| US7841436B2 (en) | 2008-01-21 | 2010-11-30 | Amigo Mobility International | Personal mobility vehicle |

| KR100955684B1 (ko) * | 2008-10-02 | 2010-05-06 | 주식회사 하이닉스반도체 | 플래그신호 생성회로 및 반도체 메모리 장치 |

| US8762621B2 (en) * | 2008-10-28 | 2014-06-24 | Micron Technology, Inc. | Logical unit operation |

| KR101638764B1 (ko) * | 2008-12-19 | 2016-07-22 | 휴렛 팩커드 엔터프라이즈 디벨롭먼트 엘피 | 균일한 판독 대기시간을 위한 중복 데이터 저장 |

| US20100287217A1 (en) * | 2009-04-08 | 2010-11-11 | Google Inc. | Host control of background garbage collection in a data storage device |

| US9582443B1 (en) | 2010-02-12 | 2017-02-28 | Marvell International Ltd. | Serial control channel processor for executing time-based instructions |

| US8582382B2 (en) * | 2010-03-23 | 2013-11-12 | Mosaid Technologies Incorporated | Memory system having a plurality of serially connected devices |

| US8843692B2 (en) | 2010-04-27 | 2014-09-23 | Conversant Intellectual Property Management Inc. | System of interconnected nonvolatile memories having automatic status packet |

| KR101817159B1 (ko) * | 2011-02-17 | 2018-02-22 | 삼성전자 주식회사 | Tsv를 가지는 인터포저를 포함하는 반도체 패키지 및 그 제조 방법 |

| KR20120098325A (ko) * | 2011-02-28 | 2012-09-05 | 에스케이하이닉스 주식회사 | 비휘발성 메모리 시스템 및 이를 위한 특성 정보 설정 방법 |

| US9098694B1 (en) * | 2011-07-06 | 2015-08-04 | Marvell International Ltd. | Clone-resistant logic |

| US9471484B2 (en) | 2012-09-19 | 2016-10-18 | Novachips Canada Inc. | Flash memory controller having dual mode pin-out |

| US9430411B2 (en) * | 2013-11-13 | 2016-08-30 | Sandisk Technologies Llc | Method and system for communicating with non-volatile memory |

| KR102164019B1 (ko) * | 2014-01-27 | 2020-10-12 | 에스케이하이닉스 주식회사 | 버스트 랭스 제어 장치 및 이를 포함하는 반도체 장치 |

| US10141039B2 (en) * | 2014-03-10 | 2018-11-27 | Everspin Technologies, Inc. | Burst length defined page size |

| JP6420139B2 (ja) * | 2014-12-26 | 2018-11-07 | シナプティクス・ジャパン合同会社 | 半導体デバイス |

| US10063376B2 (en) | 2015-10-01 | 2018-08-28 | International Business Machines Corporation | Access control and security for synchronous input/output links |

| US10120818B2 (en) | 2015-10-01 | 2018-11-06 | International Business Machines Corporation | Synchronous input/output command |

| US11776591B2 (en) * | 2019-09-26 | 2023-10-03 | Arm Limited | Concurrent access techniques utilizing wordlines with the same row address in single port memory |

| US11386937B2 (en) | 2019-10-12 | 2022-07-12 | Arm Limited | System device and method for providing single port memory access in bitcell array by tracking dummy wordline |

| CN110955387B (zh) * | 2019-10-25 | 2023-10-24 | 合肥沛睿微电子股份有限公司 | 自适应识别闪存类型方法及计算机可读取存储介质及装置 |

| TWI780653B (zh) * | 2019-11-08 | 2022-10-11 | 大陸商合肥沛睿微電子股份有限公司 | 識別快閃記憶體類型的方法及其裝置 |

| TWI780654B (zh) * | 2019-11-08 | 2022-10-11 | 大陸商合肥沛睿微電子股份有限公司 | 調整識別快閃記憶體類型的裝置及其方法 |

| US11720281B2 (en) * | 2020-12-11 | 2023-08-08 | Micron Technology, Inc. | Status information retrieval for a memory device |

| WO2023009122A1 (en) * | 2021-07-29 | 2023-02-02 | Hewlett-Packard Development Company, L.P. | Minimize delay times for status checks to flash memory |

| FR3138709A1 (fr) * | 2022-08-04 | 2024-02-09 | STMicroelectronics (Alps) SAS | Dispositif à mémoire FLASH |

Family Cites Families (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR940006094B1 (ko) | 1989-08-17 | 1994-07-06 | 삼성전자 주식회사 | 불휘발성 반도체 기억장치 및 그 제조방법 |

| JP3319105B2 (ja) | 1993-12-15 | 2002-08-26 | 富士通株式会社 | 同期型メモリ |

| KR970001699B1 (ko) * | 1994-03-03 | 1997-02-13 | 삼성전자 주식회사 | 자동프리차아지기능을 가진 동기식 반도체메모리장치 |

| US5696917A (en) | 1994-06-03 | 1997-12-09 | Intel Corporation | Method and apparatus for performing burst read operations in an asynchronous nonvolatile memory |

| USRE36532E (en) * | 1995-03-02 | 2000-01-25 | Samsung Electronics Co., Ltd. | Synchronous semiconductor memory device having an auto-precharge function |

| US5570381A (en) * | 1995-04-28 | 1996-10-29 | Mosaid Technologies Incorporated | Synchronous DRAM tester |

| US5661054A (en) | 1995-05-19 | 1997-08-26 | Micron Technology, Inc. | Method of forming a non-volatile memory array |

| US5600605A (en) | 1995-06-07 | 1997-02-04 | Micron Technology, Inc. | Auto-activate on synchronous dynamic random access memory |

| US5666321A (en) | 1995-09-01 | 1997-09-09 | Micron Technology, Inc. | Synchronous DRAM memory with asynchronous column decode |

| JP2874619B2 (ja) | 1995-11-29 | 1999-03-24 | 日本電気株式会社 | 半導体記憶装置 |

| US5749086A (en) | 1996-02-29 | 1998-05-05 | Micron Technology, Inc. | Simplified clocked DRAM with a fast command input |

| WO1998013828A1 (fr) * | 1996-09-26 | 1998-04-02 | Mitsubishi Denki Kabushiki Kaisha | Memoire a semi-conducteur du type synchrone |

| US5787457A (en) | 1996-10-18 | 1998-07-28 | International Business Machines Corporation | Cached synchronous DRAM architecture allowing concurrent DRAM operations |

| US5974514A (en) | 1996-11-12 | 1999-10-26 | Hewlett-Packard | Controlling SDRAM memory by using truncated burst read-modify-write memory operations |

| JP4057084B2 (ja) | 1996-12-26 | 2008-03-05 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| US5825710A (en) | 1997-02-26 | 1998-10-20 | Powerchip Semiconductor Corp. | Synchronous semiconductor memory device |

| KR100248353B1 (ko) | 1997-04-09 | 2000-03-15 | 김영환 | 반도체 메모리 소자 |

| US5892777A (en) | 1997-05-05 | 1999-04-06 | Motorola, Inc. | Apparatus and method for observing the mode of a memory device |

| US5903496A (en) | 1997-06-25 | 1999-05-11 | Intel Corporation | Synchronous page-mode non-volatile memory with burst order circuitry |

| JP3161384B2 (ja) * | 1997-09-16 | 2001-04-25 | 日本電気株式会社 | 半導体記憶装置とそのアクセス方法 |

| US6141247A (en) | 1997-10-24 | 2000-10-31 | Micron Technology, Inc. | Non-volatile data storage unit and method of controlling same |

| KR100274602B1 (ko) * | 1997-11-20 | 2000-12-15 | 윤종용 | 동기형 메모리 장치 |

| US5917724A (en) * | 1997-12-20 | 1999-06-29 | Ncr Corporation | Method for predicting disk drive failure by monitoring the rate of growth of defects within a disk drive |

| JPH11203864A (ja) | 1998-01-14 | 1999-07-30 | Mitsubishi Electric Corp | 同期型半導体記憶装置 |

| KR100306965B1 (ko) * | 1998-08-07 | 2001-11-30 | 윤종용 | 동기형반도체메모리장치의데이터전송회로 |

| FI990038A (fi) * | 1999-01-11 | 2000-07-12 | Nokia Mobile Phones Ltd | Menetelmä dynaamisen muistin virkistämiseksi |

| US6785764B1 (en) * | 2000-05-11 | 2004-08-31 | Micron Technology, Inc. | Synchronous flash memory with non-volatile mode register |

| US6728798B1 (en) * | 2000-07-28 | 2004-04-27 | Micron Technology, Inc. | Synchronous flash memory with status burst output |

| US6580659B1 (en) * | 2000-08-25 | 2003-06-17 | Micron Technology, Inc. | Burst read addressing in a non-volatile memory device |

| US6480429B2 (en) * | 2001-02-12 | 2002-11-12 | Micron Technology, Inc. | Shared redundancy for memory having column addressing |

-

2000

- 2000-07-28 US US09/626,190 patent/US6728798B1/en not_active Expired - Fee Related

-

2001

- 2001-07-27 CN CN2009102217820A patent/CN101930794A/zh active Pending

- 2001-07-27 WO PCT/US2001/023695 patent/WO2002011148A1/en active IP Right Grant

- 2001-07-27 AT AT01955000T patent/ATE492880T1/de not_active IP Right Cessation

- 2001-07-27 DE DE60143700T patent/DE60143700D1/de not_active Expired - Lifetime

- 2001-07-27 KR KR10-2003-7001296A patent/KR100511820B1/ko not_active IP Right Cessation

- 2001-07-27 AU AU2001277210A patent/AU2001277210A1/en not_active Abandoned

- 2001-07-27 CN CN01816420A patent/CN100578659C/zh not_active Expired - Fee Related

- 2001-07-27 JP JP2002516785A patent/JP3809909B2/ja not_active Expired - Fee Related

- 2001-07-27 EP EP01955000A patent/EP1305804B1/en not_active Expired - Lifetime

- 2001-07-27 DE DE1305804T patent/DE1305804T1/de active Pending

-

2004

- 2004-04-26 US US10/831,823 patent/US7096283B2/en not_active Expired - Fee Related

-

2005

- 2005-08-31 US US11/216,953 patent/US7603534B2/en not_active Expired - Fee Related

-

2009

- 2009-09-30 US US12/570,570 patent/US8010767B2/en not_active Expired - Fee Related

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103403805A (zh) * | 2011-03-23 | 2013-11-20 | 株式会社东芝 | 半导体存储装置及其控制方法 |

| CN103403805B (zh) * | 2011-03-23 | 2016-01-27 | 株式会社东芝 | 半导体存储装置及其控制方法 |

| US9256523B2 (en) | 2011-03-23 | 2016-02-09 | Kabushiki Kaisha Toshiba | Semiconductor storage device and control method thereof |

| US9582414B2 (en) | 2011-03-23 | 2017-02-28 | Kabushiki Kaisha Toshiba | Semiconductor storage device and control method thereof |

| CN104981873A (zh) * | 2013-03-12 | 2015-10-14 | 桑迪士克科技股份有限公司 | 在发送写入数据到存储器的同时从存储器读取数据的系统和方法 |

| CN104981873B (zh) * | 2013-03-12 | 2018-01-02 | 桑迪士克科技有限责任公司 | 在发送写入数据到存储器的同时从存储器读取数据的系统和方法 |

| TWI616884B (zh) * | 2013-03-12 | 2018-03-01 | 桑迪士克科技有限責任公司 | 自記憶體讀取資料同時將寫入資料傳送至該記憶體之系統及方法 |

| CN104951402A (zh) * | 2014-03-26 | 2015-09-30 | 三星电子株式会社 | 存储装置及其操作方法和计算系统 |

| CN104951402B (zh) * | 2014-03-26 | 2019-07-19 | 三星电子株式会社 | 存储装置及其操作方法和计算系统 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050289313A1 (en) | 2005-12-29 |

| WO2002011148A1 (en) | 2002-02-07 |

| KR100511820B1 (ko) | 2005-09-05 |

| KR20030028556A (ko) | 2003-04-08 |

| DE60143700D1 (zh) | 2011-02-03 |

| US8010767B2 (en) | 2011-08-30 |

| US20100088484A1 (en) | 2010-04-08 |

| EP1305804B1 (en) | 2010-12-22 |

| CN100578659C (zh) | 2010-01-06 |

| US6728798B1 (en) | 2004-04-27 |

| US7096283B2 (en) | 2006-08-22 |

| CN1466762A (zh) | 2004-01-07 |

| JP3809909B2 (ja) | 2006-08-16 |

| JP2004505404A (ja) | 2004-02-19 |

| DE1305804T1 (de) | 2003-11-27 |

| US7603534B2 (en) | 2009-10-13 |

| ATE492880T1 (de) | 2011-01-15 |

| US20040199713A1 (en) | 2004-10-07 |

| EP1305804A1 (en) | 2003-05-02 |

| AU2001277210A1 (en) | 2002-02-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100578659C (zh) | 具有状态脉冲串输出的同步快闪存储器 | |

| US6615307B1 (en) | Flash with consistent latency for read operations | |

| US6442076B1 (en) | Flash memory with multiple status reading capability | |

| KR100438635B1 (ko) | 동기 플래시 메모리에서 프리차지 동작의 소거 | |

| US6580659B1 (en) | Burst read addressing in a non-volatile memory device | |

| US6459617B1 (en) | Method and circuitry for bank tracking in write command sequence | |

| US7278004B2 (en) | Burst write in a non-volatile memory device | |

| US6851026B1 (en) | Synchronous flash memory with concurrent write and read operation | |

| US6728161B1 (en) | Zero latency-zero bus turnaround synchronous flash memory | |

| US20040057320A1 (en) | Top/bottom symmetrical protection scheme for flash | |

| JP3631209B2 (ja) | 読み出し処理におけるレイテンシを一致させたフラッシュ | |

| KR100508041B1 (ko) | 동기식 플래시 메모리에서의 인터페이스 커맨드 아키텍쳐 | |

| KR100438634B1 (ko) | 기록 및 판독 동작을 동시에 행하는 동기식 플래시 메모리 | |

| KR100495848B1 (ko) | 제로-레이턴시-제로 버스 전환 동기 플래시 메모리 | |

| JP2003529878A (ja) | 不揮発性モードレジスタを有するシンクロナスフラッシュメモリ | |

| JP2003529881A (ja) | フラッシュ用のトップ/ボトム対称保護スキーム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |

Application publication date: 20101229 |