CN101794774B - 半导体集成电路 - Google Patents

半导体集成电路 Download PDFInfo

- Publication number

- CN101794774B CN101794774B CN2010101038722A CN201010103872A CN101794774B CN 101794774 B CN101794774 B CN 101794774B CN 2010101038722 A CN2010101038722 A CN 2010101038722A CN 201010103872 A CN201010103872 A CN 201010103872A CN 101794774 B CN101794774 B CN 101794774B

- Authority

- CN

- China

- Prior art keywords

- unit

- gate pads

- wiring layer

- gate

- another

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 37

- 238000000926 separation method Methods 0.000 claims abstract description 16

- 239000002184 metal Substances 0.000 claims description 42

- 230000015572 biosynthetic process Effects 0.000 claims description 7

- 239000010410 layer Substances 0.000 description 88

- 238000009826 distribution Methods 0.000 description 58

- 238000013461 design Methods 0.000 description 37

- 230000008859 change Effects 0.000 description 19

- 230000000052 comparative effect Effects 0.000 description 14

- 238000004519 manufacturing process Methods 0.000 description 12

- 238000000034 method Methods 0.000 description 12

- 239000000945 filler Substances 0.000 description 10

- 239000000758 substrate Substances 0.000 description 8

- 238000010276 construction Methods 0.000 description 7

- 239000012535 impurity Substances 0.000 description 7

- 230000008569 process Effects 0.000 description 7

- 230000008901 benefit Effects 0.000 description 5

- 238000009792 diffusion process Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 230000005684 electric field Effects 0.000 description 5

- 230000011664 signaling Effects 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 3

- 230000007547 defect Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000003780 insertion Methods 0.000 description 2

- 230000037431 insertion Effects 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 238000011084 recovery Methods 0.000 description 2

- 238000003786 synthesis reaction Methods 0.000 description 2

- 238000010923 batch production Methods 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 238000013519 translation Methods 0.000 description 1

- 230000003313 weakening effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0207—Geometrical layout of the components, e.g. computer aided design; custom LSI, semi-custom LSI, standard cell technique

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/118—Masterslice integrated circuits

- H01L27/11803—Masterslice integrated circuits using field effect technology

- H01L27/11807—CMOS gate arrays

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Engineering & Computer Science (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Abstract

本发明提供半导体集成电路,其包括:多个标准单元,包括具有栅极电极的晶体管,并且彼此组合布置;金属配线层,互连标准单元以形成所希望的电路;以及多个储备单元,具有栅极电极,与该金属配线层不连接,并且设置在标准单元的周边上,其中标准单元和储备单元的每个栅极电极都具有栅极焊盘部分和两个栅极手指部分,两个栅极手指部分从栅极焊盘部分延伸到在预定的方向上彼此相对的侧,并且储备单元的栅极焊盘部分在垂直于所述预定方向的方向上的长度等于或大于该金属配线层中最小线宽的三倍与最小间隔距离的两倍的总和值。

Description

技术领域

本发明涉及半导体集成电路,其中所希望的电路通过彼此组合地设置多个电路单元并且由金属配线层互连这些单元而形成,这些电路单元(例如标准单元)包括具有栅极电极的晶体管。

背景技术

因为在半导体LSI(大规模集成电路)的小型化上已经取得进步,所以逻辑电路元件内的延迟(在下文将这样的延迟称为“栅极延迟”)和配线延迟之间的比率发生了很大的变化。

先前小型化不很先进的LSI,考虑到整个LSI或整个电路模块的信号延迟,在元件中具有很高的栅极延迟与配线延迟比。因此,在LSI设计的逻辑合成阶段中整个信号通道的延迟估算中,除非在估算每个栅极延迟上存在错误,否则延迟总量与预测没有太大偏差。

在近来的半导体工艺中,小型化的进步增加了配线延迟与总信号延迟的比率。因此,正确地估算配线延迟是重要的。

然而,在逻辑合成阶段中,不知道配线布局的状态,因此不能确定配线延迟,并且难于估算。因此,难于估算整个信号通道中操作的计时(timing)。

例如,除非可以以一定程度的精度估算直到连接到特定栅极电路的多个输入的每个的前段的电路部分中的延迟量,否则考虑到相对于栅极电路操作的每个输入延迟和可承受延迟量(延迟余量),不能估算计时。在这样各个栅极电路中的计时估算被加合,并且在整个信号通道对纠正操作进行计时设计。然而,配线延迟的不确定性将大量的错误引入整个信号通道上的计时估算中。

因此,由逻辑合成工具估算的通道延迟时间和实际完成的LSI的通道延迟时间彼此偏离,并且倾向于产生错误操作,即错误逻辑反转。因降低电压而保证噪声余量上的困难也促使错误逻辑反转频率的增加。

另外,半导体元件的小型化能使更多的逻辑栅极电路结合,使逻辑变得复杂,并且增加了逻辑错误的频率。

出于这样的原因,在完成设计之前或之后或样品评估时,希望增加来自客户要求设计的ECO(工程更改通知(Engineering Change Orders):设计后对电路更改的要求)。

作为低成本、短时间处理ECO的方法,已知在标准单元布置的未使用部分中嵌入用于设计后更改的储备单元(reserve cell)的方法(例如,见日本专利公开No.2006-269900)。

在下文,将储备单元称为“ECO单元”或“ECO填充物”。另外,在下文将这样的设计方法称为“ECO单元辅助设计”。

发明内容

通常,标准单元的两个垂直方向(所谓的垂直方向和水平方向)上的至少一个尺寸被标准化为几个类型,例如约三种类型。在所谓的垂直方向上的尺寸被称为标准单元的“高度”,并且该高度被标准化或统一为约三种类型。因为单元的尺寸(高度)与垂直于半导体基板方向的结构高度混淆,因此造成误解,所以单元尺寸在下文不称为“高度”。取而代之,为了方便起见,该尺寸在下文将称为“共同单元长度”。

尽管在整个LSI中存在标准单元的几种类型的共同单元长度,但是为了有效地布置单元,从局部来看,相同的共同单元长度用于相同电路块。

因此,制备具有相同共同单元长度的各种类型的标准单元,并且在程序库中登记。通常,标准单元的内部配线等图案的布置空间在共同单元长度方向上受限。

另一方面,根据栅极电路的规模,在垂直于标准单元的共同单元长度方向的方向(所谓的水平方向)上具有各种不同的尺寸。为了方便起见,在垂直于共同单元长度的方向上的单元尺寸将称为“任意单元长度”。

用于处理ECO的上述储备单元中的用于晶体管形成的元件隔离区域和杂质扩散层的一部分继承了标准单元的标准规范。

然而,对于上述储备单元的栅极电极层和金属配线层,确定了对ECO单元的独特规范(标准)。

在ECO单元辅助设计中,在样品评估时不满足客户要求的特征缺陷是被预期的,或者在实际的样品评估中可以发现特征缺陷。在此情况下,通过储备单元(ECO单元)进行延迟调整。例如,从相邻ECO单元改变的缓冲器等插入具有太大延迟量的通道中。从相邻改变且对应于所希望的附加延迟量的数目的反相器等插入希望被提供更大延迟量的通道中。

另外,ECO单元用于恢复逻辑错误。

在通过这样的ECO单元的延迟调整或逻辑错误的恢复中,仅在相邻于需要调整或恢复的通道的ECO单元中附加地设计从第一接触的上层,而不改变ECO单元的基本构造或水平和垂直尺寸。因此,在需要延迟调整的位置上,对于从程序库读取的标准单元的延迟调整,最终进行从储备单元到所希望的栅极电路单元(功能等同于标准单元)的改变。

然而,在布置标准单元后,ECO单元设置在自由空间中,在共同单元长度方向上具有限制。因此,在共同单元长度方向上难于自由地绕开金属配线层。

在绕行困难时,通常采用连接系统,就通过较高的金属配线层的图案而言,增加了所采用的金属配线的层数并消除对绕行的需求。然而,所采用的金属配线的层数的增加提高了制造成本,因此半导体产品会失掉价格竞争力。

附带地,对于诸如标准单元和ECO单元等的电路单元重要的是,晶体管特性不会轻易地改变。

所希望的是提供这样的半导体集成电路,其能够增加配线的自由度,而不增加金属配线的层数,并且其电路单元的图案中晶体管特征不会轻易改变。

在本发明的第一实施例中,所提供的半导体集成电路包括:多个标准单元,包括具有栅极电极的晶体管,并且彼此组合设置;金属配线层,互连多个标准单元,以形成所希望的电路;以及多个储备单元,具有栅极电极,与金属配线层不连接,并且设置在多个标准单元的周边上。在该半导体电路中,多个标准单元和所述多个储备单元的每个栅极电极都具有栅极焊盘部分和两个栅极手指部分,两个栅极手指部分从栅极焊盘部分延伸到在预定的方向上彼此相对的侧,并且多个储备单元的栅极焊盘部分在垂直于预定方向的方向上的长度等于或大于金属配线层中最小线宽的三倍与最小间隔距离的两倍的总和值。

根据具有该构造的半导体集成电路,设定储备单元的栅极焊盘部分在垂直于栅极手指部分的方向上的长度为上述的预定值(然而,当然,长度不应超过在该方向上的单元尺寸)的要求。因此,例如,通过所谓的下桥结构(underbridge structure)使得与栅极焊盘部分的作为桥线(bridge line)的部分的配线交叉成为可能,而不需绕行金属配线层到栅极手指部分的端侧。就是说,该栅极焊盘部分的长度等于或大于金属配线层中最小线宽的三倍与最小间隔距离的两倍的总和值,并且使金属配线层与栅极焊盘部分的中间部分交叉。此时,在交叉的金属配线层宽度方向上的两侧,存在以最小分隔距离设置金属配线层的空间。因此,金属配线层可以连接在桥线的一端侧和另一端侧二者(栅极焊盘部分的一部分)。

对于桥线所需的栅极焊盘部分的长度方向希望是所谓的任意单元长度方向。在此情况下的任意单元长度方向是沿着栅极手指部分垂直于共同单元长度方向(预定方向)的方向。为了易于标准单元的设计和布置,共同单元长度标准化为一种类型的长度。另一方面,任意单元长度方向上的单元长度不受这种规则限制。通过应用栅极焊盘部分在任意单元长度方向上的长度为预定值或更大的上述要求,可以略微增加任意单元长度方向上的单元尺寸。然而,任意单元长度方向上的尺寸增加不涉及大于尺寸增加的缺点,例如,作为削弱在基于单元电路设计中获得的易于布置的结果产生不必要空间的大的缺点。

栅极焊盘部分是给栅极提供电压(信号)的部分。当栅极焊盘部分在一个长栅极手指部分的一个侧端时,因栅极电阻的作用,在栅极手指部分的长度方向上,电场以不均匀的方式施加给晶体管沟道。当在晶体管当中施加电场的方式变化时,晶体管的特征也倾向于变化。尽管在栅极焊盘部分在栅极手指部分的两个侧端时电场被不均匀地施加,但是共同单元长度方向上的单元尺寸增加对应于一个栅极焊盘部分的量。

另一方面,在根据第一实施例的半导体集成电路中,两个栅极手指部分从栅极焊盘部分延伸到在预定的方向上(共同单元长度方向)彼此相对的侧。该构造补偿了栅极电阻的差别和电场施加方式上的不均匀性,该不均匀性由栅极电阻的差值引起。结果,减少了晶体管特征的变化,而不涉及单元尺寸在共同单元长度方向上的增加。

在根据本发明的第二实施例中,所提供的半导体集成电路包括:多个电路单元,包括晶体管,并且布置为彼此组合;以及金属配线层,互连多个电路单元,以形成所希望的电路。在该半导体电路中,多个电路单元内的晶体管的栅极电极具有栅极焊盘部分和从栅极焊盘部分延伸到在预定的方向上彼此相对的侧的两个栅极手指部分,并且在形成所希望的电路的该多个电路单元的至少一个中的栅极焊盘部分在垂直于述预定方向的方向上的长度等于或大于金属配线层中最小线宽的三倍与最小间隔距离的两倍的总和值。

在上述的第二实施例中,栅极焊盘部分在所谓任意单元长度方向上的长度等于或大于金属配线层中最小线宽的三倍与最小间隔距离的两倍的总和值的要求的应用不限于储备单元。就是说,栅极焊盘可以形成在所谓的标准单元中,以满足能实现这样下桥结构的最大长度要求。因此,在第二实施例中,“电路单元”用作包括储备单元和标准单元的概念。

根据本发明,能够提供这样的半导体集成电路,其可以增加配线的自由度而不增加金属配线的层数和在共同单元长度方向上的尺寸,并且具有图案不易受晶体管特性变化的电路单元。

附图说明

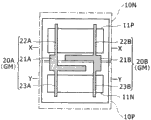

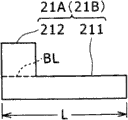

图1A是示意性地示出根据实施例的集成电路的平面图,着重于单元布置,图1B是根据实施例的ECO单元的构成示例的平面图,而图1C是栅极焊盘部分的放大图;

图2是在根据实施例的ECO单元配线后的示例所示的反相器的平面图;

图3A是根据比较示例的ECO单元的平面图,图3B是根据比较示例的ECO单元配线后反相器的平面图,而图3C是另一个比较示例的配线示例所示的NAND栅极电路的平面图;

图4是比较示例的配线的另一个示例的平面图;

图5是比较示例的配线的另一个示例的平面图;

图6是比较示例的配线的另一个示例的平面图;

图7是与图4至6相反应用本发明的配线示例的平面图;

图8是在实施例中描述设计方法程序的流程图;

图9是紧接着布置标准单元后的平面图;以及

图10A和10B是示出阱结构的集成电路的示意性截面图。

具体实施方式

在下文,将参考附图以半导体集成电路为例,描述本发明的优选实施例,在该半导体集成电路中,通过ECO单元对标准单元进行特性调整或从逻辑错误的恢复。

下面的描述以下面的顺序进行。

1.总布局

2.ECO单元的构造

3.ECO单元的配线的第一示例

4.ECO单元的配线的第二示例

5.设计程序的流程

6.修改示例

<1.总布局>

图1A是示意性地示出根据实施例的集成电路的平面图,着重于单元的布置。

图1A中的每个方块区域都称为单元。由符号“SC”表示的单元为标准单元(standard cell)。标准单元SC为反相器(inverter)和NAND栅极等的功能电路单元,是在程序库中事先设计、标准化和登记的。标准单元SC是一套数据,但是可以涉及基于数据制造的装置的一部分。正如稍后将详细描述的,在半导体集成电路的设计中,组合和布置程序库中登记的标准单元。这种布置基本上将电源电压线和参考电压线(例如,GND线)在数据上彼此连接。在布置后,通过连接信号线等获得所希望的电路。至于此点的这种布置和配线是通过设计辅助装置在数据上的操作。

图1A是着重于半导体集成电路单元的单元布置的示意性平面图。图1A也用作数据上的单元布置示意图。

如图1A所示,通过组合和布置各种尺寸的标准单元SC而实现所希望的电路。根据各标准单元SC的功能电路的属性和标准单元SC的组合可以任意实现在此情况下所希望的电路,只要所希望的电路是逻辑电路。图1A为普通的示意图,并且所希望的电路自身的属性是任意的。

在ASIC(专用集成电路,Application Specific Integrated Circuit)和ASSP(专用标准产品,Application Specific Standard Product)等的设计中,采用标准单元设计系统。ASIC是为每个客户的特定使用开发和制造的IC。ASSP是为多个客户开发和制作作为通用目的部分的IC。

下面将描述标准单元SC的尺寸。

在沿着彼此垂直的两个边之一的方向上,标准单元SC在单元长度上通常被标准化或统一。在下文,将该单元长度方向称为“共同单元长度方向(common cell lenghh direction)”。共同单元长度方向上的尺寸(共同单元长度)不限定为一种类型,但是可以是几种类型,例如,从整个IC上看为三种类型。然而,在一种电路模块的局部上看,共同单元长度为一个均匀长度。在图1A中,在图1A的纸面的垂直方向上设定相同的单元尺寸,因此该方向是共同单元长度方向。

在垂直于共同单元长度方向的方向上,单元尺寸可以任意确定。然而,尽管是任意的,但是由于要求设计效率和一致性,通常确定可以离散取值的尺寸(由栅格数规定)。在下文,将垂直于共同单元长度方向的方向称为“任意单元长度方向(arbitrary cell length direction)”。

在本实施例中,为了处理ECO,ECO单元(写成“ECO填充物”)布置在标准单元SC周围的自由空间上。

在共同单元长度方向,ECO单元与标准单元SC具有相同的尺寸。尽管在图1A中ECO单元具有相同的单元尺寸,但是在任意单元长度方向上ECO单元可以取几种类型的单元尺寸。

在对所希望的电路的贡献程度上,ECO单元与标准单元SC不同。

标准单元SC自身形成所希望的电路。另一方面,ECO单元布置为“储备单元”,通常不形成所希望的电路。

在标准单元SC的布置和配线上不存在问题时,ECO单元仅起填充自由空间的填充物的作用。然而,在样品评估时,当存在来自要求设计的客户的工程更改通知(Engineering Change Order,ECO)时,必须处理ECO,并且此时使用ECO单元。稍后将描述使用ECO单元的方法。

<2.ECO单元的构造>

图1B示出了ECO单元的构造示例。

图1B的平面图是ECO单元的布局图,该ECO单元用于实现诸如反相器或NAND栅极等的最基本的栅极电路。

图1B所示的ECO单元的半导体基板具有用于形成PMOS晶体管的N型阱(在下文,称为N阱)10N和用于形成NMOS晶体管的P型阱(在下文,称为P阱)10P。N阱10N和P阱10P形成为在半导体基板内的共同单元长度方向上彼此分隔。

附带地,例如,稍后描述的形成源极区域和漏极区域等的杂质扩散层(11P和11N)形成在N阱10N和P阱10P的图案内侧。另外,例如,可以采用阱中阱结构或三阱结构。除了采用阱中阱结构外,图1B的N阱10N和P阱10P代表不形成元件隔离区域的两个基板区域,并且表示N型杂质层或N型杂质层的一部分形成在两个基板区域的一侧,而P型杂质层或P型杂质层的一部分形成在另一侧。

另外,稍后将在修改示例的部分中描述阱中阱结构。

在共同单元长度方向上,图1B的纸面上部中的N阱10N将称为“PMOS形成区域”。图1B的纸面下部中的P阱10P将称为“NMOS形成区域”。

形成由栅极金属层GM组成的两个栅极电极20A和20B。例如,在此情况下的栅极金属层GM具有多晶硅单层结构或多晶硅与高熔点金属的多层结构。通过光刻和蚀刻将栅极金属层GM处理成预定的图案而同时形成栅极电极20A和20B。

栅极电极20A和20B的每一个都具有一个栅极焊盘部分和两个栅极手指部分(gate finger section)整体形成的图案。

更具体地讲,栅极电极20A具有栅极焊盘部分21A,设置在PMOS形成区域10N和NMOS形成区域10P之间的边界周围。正如图1C所示的希望的示例,栅极焊盘部分21A具有L-形状的图案,其中在任意单元长度方向上狭长的金属配线交叉部分211和主干部分(trunk section)212一体地形成为该L-形状。如图1B和图1C所示的希望示例,栅极电极20A具有栅极手指部分22A,其从主干部分212的端侧延伸以与P型扩散层11P交叉。栅极电极20A具有栅极手指部分23A,其从金属配线交叉部分211的长边的中间延伸以与N型扩散层11N交叉。

栅极手指部分22A和23A的宽度限定晶体管的所谓栅极长度。栅极手指部分22A与P型扩散层11P交叉的部分的长度限定PMOS晶体管的所谓栅极宽度。栅极手指部分23A与N型扩散层11N交叉的部分的长度限定NMOS晶体管的所谓栅极宽度。

类似地,栅极电极20B具有栅极焊盘部分21B,设置在PMOS形成区域10N和NMOS形成区域10P之间的边界周围。与栅极焊盘部分21A一样,栅极焊盘部分21B希望具有金属配线交叉部分211和主干部分212一体地形成的L-形状的图案。

在此情况下,栅极焊盘部分21B设置在栅极焊盘部分21A附近。此时,栅极焊盘部分21A和21B彼此接近地设置使得栅极焊盘部分21A和21B的L-形状彼此组合,并且栅极焊盘部分21A和21B总体上包含在矩形区域中。栅极焊盘部分21A和21B的L-形状彼此组合且栅极焊盘部分21A和21B包含在矩形区域中的这种布置不是必要的。然而,当栅极焊盘部分具有L-形状时,这种组合布置很大地节省总的布置面积,从这一点来讲是所希望的。

栅极焊盘部分21B具有通过将栅极焊盘部分21A旋转180度获得的手指图案。

因此,如图1B和图1C所示,栅极电极20B具有栅极手指部分22B,其从栅极焊盘部分21B中的金属配线交叉部分211的长边中间延伸以与P型扩散层11P交叉。栅极电极20B具有栅极手指部分23B,其从主干部分212的端侧延伸以与N型扩散层11N交叉。

栅极手指部分22B和23B的宽度限定晶体管的所谓栅极长度。栅极手指部分22B与P型扩散层11P交叉的部分的长度限定PMOS晶体管的所谓栅极宽度。栅极手指部分23B与N型扩散层11N交叉的部分的长度限定NMOS晶体管的所谓栅极宽度。

如图1C所示,栅极焊盘部分21A和21B的每一个都在任意单元长度方向上具有预定长度L。“任意单元长度方向上的长度”是指该方向上最大部分的尺寸。另外,预定长度L采用满足预定长度L“等于或大于金属配线层中最小线宽的三倍与最小间隔距离的两倍的总和值”的值。附带地,预定长度L的上限是任意单元长度方向上的单元尺寸。在金属配线层中的连接是必要的时,满足该要求的内容是清楚的,因此稍后将在ECO单元的配线示例部分中予以描述。

只要满足该要求,栅极焊盘部分21A和21B的形状是任意的,而不需要为L-形状。

当由标准单元SC形成的所希望的电路中存在逻辑错误(连接错误)时,ECO单元(ECO填充物)连接为所希望的电路的一部分以恢复逻辑错误。

在某些情况下变得清楚的是,例如,尽管不存在连接错误,但是因为延迟量的估算不同,所以倾向于发生错误操作(错误逻辑反转)。在此情况下,因为对于错误操作的不敏感,ECO单元连接为所希望电路的一部分,并且进行延迟调整。

另外,在恢复逻辑错误时,需要同时进行延迟调整。

仅在需要ECO单元的上述情况下,在必要位置处在ECO单元中进行金属配线层的连接。

下面,将描述ECO单元的(金属配线层的)配线的几个示例。

<3.ECO单元的配线的第一示例>

图2示出了在实现允许从纸面的左侧和右侧进行输入的反相器时ECO单元的配线示例。

图2所示ECO单元的布局通过以下方式进行:给图1B的接地布局增加提供在图中未示出的第一层间绝缘膜的第一层中的接触(第一接触:1C)和第一层的金属配线层(第一配线层:1M)的布置。

更具体地讲,如图2所示,栅极电极20A和栅极电极20B的栅极手指部分将P型扩散层11P分成三个部分。

P型扩散层11P的三个扩散层部分的宽中间部分通过第一接触41(1C)连接到由第一接触41上的第一配线层(1M)形成的电源电压供给线VDD的分支部分。电源电压供给线VDD的主干线沿着单元边界设置在任意单元长度方向上。

类似地,栅极电极20A和栅极电极20B的其他栅极手指部分将N型扩散层11N分成三个部分。

N型扩散层11N的三个扩散层部分的宽中间部分通过第一接触42(1C)连接到由第一接触42上的第一配线层(1M)形成的参考电压供给线VSS的分支部分。参考电压供给线VSS的主干线沿着与电源电压供给线VDD相对侧的单元边界设置在任意单元长度方向上。

PMOS晶体管形成为具有与P型扩散层11P交叉的栅极电极20A的栅极手指部分22A作为栅极。PMOS晶体管的源极区域形成在连接到第一接触41(1C)的P型扩散层部分中。与连接到第一接触41(1C)的P型扩散层部分相对侧的P型扩散层部分形成PMOS晶体管的漏极区域,栅极手指部分22A插设在这些P型扩散层部分之间。

两个第一接触43(1C)和44(1C)形成在PMOS晶体管的漏极区域上。

NMOS晶体管形成为具有与N型扩散层11N交叉的栅极电极20A的栅极手指部分23A作为栅极。NMOS晶体管的源极区域形成在连接到第一接触42(1C)的N型扩散层部分中。与连接到第一接触42(1C)的N型扩散层部分相对侧的N型扩散层部分形成NMOS晶体管的漏极区域,栅极手指部分23A插设在这些N型扩散层部分之间。

一个第一接触45(1C)形成在NMOS晶体管的漏极区域上。

栅极焊盘部分21A提供为具有连接PMOS晶体管和NMOS晶体管的栅极的作用以及接触(停放)焊盘的作用的栅极部分。

第一接触46(1C)形成为接近栅极焊盘部分21A的金属配线交叉部分211的一个端部。第一输入线31(1M)连接到第一接触46(1C)。

第一接触47(1C)形成在接近金属配线交叉部分211的另一个端部的一侧。第二输入线32(1M)连接到第一接触47(1C)。

第一输入线31(1M)和第二输入线32(1M)可以根据设置反相器之前的阶段中沿任意单元长度方向设置栅极电路的一侧(图2的纸面的左侧和右侧)可选地提供。作为选择,第二输入线32(1M)可以用于分支成来自第一输入线31的信号通过图2所示ECO单元(反相器)然后输出的通道和该信号不通过ECO单元(反相器)的通道。

金属配线交叉部分211形成任意单元长度方向上的长条形状,目的是加宽两个第一接触46(1C)和47(1C)之间的区域。

作为一种内部连接线的漏极连接线33(1M)设置在两个第一接触46(1C)和47(1C)之间,以与金属配线交叉部分211垂直。漏极连接线33(1M)的一个端部侧通过第一接触43(1C)和44(1C)连接到PMOS晶体管的漏极区域。漏极连接线33(1M)的另一个端部侧通过第一接触45(1C)连接到NMOS晶体管的漏极区域。

尽管因为输出方向不确定而没有在图2中具体示出,但是该输出可以从任意单元长度方向的任何一个方向(图2的纸面的左方向和右方向)中的漏极连接线33(1M)获取。

对于这样的金属配线交叉部分211,第一配线层(1M)可以垂直于金属配线交叉部分211的中间部分附近,并且接触可以提供在垂直部分的两侧。为此,金属配线交叉部分211的最小长度(图1C中的符号“L”)的要求是能够形成3倍的配线和2倍的配线间的间隔的长度,假设接触的宽度与配线层宽度相同。换言之,对金属配线交叉部分211的要求是满足这样的条件:金属配线交叉部分211在任意单元长度方向上的长度“等于或大于金属配线层中的最小线宽的三倍与最小间隔距离的两倍的总和值”。

[比较示例]

图3A、3B和3C示出了没有应用本发明的ECO单元,与图1B和图2中的ECO单元相反。图3A示出了尚未连接配线的ECO单元。图3B和图3C示出了配线后的ECO单元。图3B代表了通过配线实现反相器(INV.)单元的情况。图3C代表通过配线实现NAND单元的情况。

图3A至3C所示的栅极电极20C和20D具有两个栅极手指部分(22A和23A或22B和23B)。这两个栅极手指部分分别与P型扩散层11P和N型扩散层11N交叉。栅极电极20C和20D具有与图1B和图2中的栅极电极20A和20B相同的栅极手指部分的构造。

栅极电极20C和20D在栅极焊盘部分的形状上与栅极电极20A和20B不同。比较示例中的栅极电极20C和20D的栅极焊盘部分21C具有矩形形状。该矩形形状具有一尺寸以简单地起接触停放焊盘(contact landing pad)的作用。

图3B所示的反相器(INV.)没有使用右侧的栅极,这一情况本身是非必须的。

在此情况下重要的是,栅极焊盘部分21C是矩形的形状并具有一尺寸,而不没有由图2中的配线可交叉的任意单元长度方向上的预定长度L。因此,在任意单元长度方向上固定形成输入(IN)和输出(OUT)的配线层的位置。在图3B的示例中,输入(IN)固定为来自纸面右侧的输入,并且输出(OUT)固定为到纸面左侧的输出。因此,为了输入和输出可以在图2中任意单元长度方向上的任何一侧,通过牺牲栅极宽度而为配线绕行提供空间或者利用第二配线层(2M)作为更高的层是必要的。

同样,在提供信号不通过反相器的分支通道的情况下,通过牺牲栅极宽度而为配线绕行提供空间或者利用第二配线层(2M)作为更高的层是必要的。

在图3C所示的两输入NAND电路中,输出(OUT)可以产生到左右任何一侧的输出。然而,输出(OUT)的配线是两个输入的障碍,即第一输入(IN1)和第二输入(IN2)的障碍。因此,为了任意地分配第一输入(IN1)和第二输入(IN2)到左右的一侧,通过牺牲栅极宽度而为配线绕行提供空间或者利用第二配线层(2M)作为更高的层是必要的。同样,在提供信号不通过NAND栅极的分支通道的情况下,通过牺牲栅极宽度而为配线绕行提供空间或者利用第二配线层(2M)作为更高的层是必要的。

另一方面,图2所示的本实施例能使输入和输出任意地分配到左侧和右侧。另外,可以提供信号不通过ECO单元的通道。此时,不必提供通过牺牲栅极宽度而用于配线绕行的空间。此外,不必使用作为更高的层的第二配线层(2M)。

因此,可以提高配线的自由度,而不增加金属配线的层数。

<4.ECO单元的配线的第二示例>

图7是示出本实施例中配线的第二示例的布局的示意图。图4至6示出了配线的第二示例的比较示例。

由这些附图中所示的ECO单元实现的电路是配线更加复杂时的示例。为了获得所希望的特性,图4中的点划线表示的节点之间的连接需要用尽可能短的配线长度建立。

对于比较示例(图4)中表示的这种要解决的问题,图5的比较示例采用更高的第二层(第二配线层:2M)的金属配线层,因此具有相应增加制造成本的缺点。

图6的比较示例具有长连接线30(1M),用于形成绕行路径而取代第二配线层(2M)。在此情况下的绕行路径仅能够在共同单元长度方向上大且具有配线余量的块中的标准单元SC的情况下是可能的。

在图5和图6所示的比较示例相比,如图7应用本发明的配线的第二示例与图6中的连接线30(1M)相比具有较短的形成绕行路径的连接线31(1M)。这是因为用于连接线31的接触提供在栅极焊盘部分的金属配线交叉部分211(GM)的端部。结果,可以进行配线而不造成由于使用第二配线层2M或在共同单元长度方向上的增加等引起的成本增加。

如上述配线的第二示例所示,通过应用本发明的示例,本发明可实施为优化配线的便利。

<5.设计程序的流程>

设计后的电路改变(ECO)的要求发生在自家公司内或客户的样品评估阶段。因为一旦制造了光掩模以及制造了产品或样品后就引起大量的附加成本,所以采用ECO的设计系统的优点在于,该设计系统使光掩模后的电路更改相对容易。

因此,采用这样ECO的设计系统通常称为“掩模后ECO(Post MaskECO)”。“掩模后ECO”对于恢复LSI试制后显示错误的计时估算中的错误或短周转时间(short turnaround time,TAT)的逻辑错误是有效的系统。

图8示出了包括“掩模后ECO”流程的LSI设计的流程。

在LSI设计中,在步骤ST1中进行结构设计。在步骤ST2中进行寄存器转移电平(RTL)设计。在步骤ST3中,通过来自RTL的合成工具产生网络列表(Netlist)100。网络列表是指电子电路中终端之间连接上的信息数据。

在步骤ST4中,网络列表100输入到配置与布线(P&R)工具,并且进行布局设计。

在根据标准单元的块的布局设计中,P&R工具将标准单元从网络列表100和计时限制设置在优化位置。

图9示出了设置和配线的标准单元SC后的状态。

在图9的阶段上,通过与图1A比较显示,自由空间产生在标准单元SC周围的位置。自由空间的产生率通常约为10%至30%,尽管取决于LSI的使用等会有差别。

在图8所示的“掩模后ECO”流程中,ECO单元(ECO填充物)设置在不设置标准单元SC的位置上,如图1A所示。

“掩模后ECO”系统提供两种ECO单元,即ECO填充物和ECO逻辑单元(ECO逻辑单元)。上述配线的第一示例或配线的第二示例中所示的ECO逻辑单元可以通过给ECO填充物配线而产生。然而,对于较短的TAT,“掩模后ECO”系统以预期的电路形式在预先的程序库中登记逻辑单元,并且在发生位置上用逻辑单元取代ECO填充物。

ECO填充物具有图3A(比较示例)或图1B(本实施例)的布局形式。

已经描述了布局形式,因此在其下面的描述中将予以省略。

返回到图8,在步骤ST5中制造光掩模(Mask)。在步骤ST6中,采用制造的光掩膜在试制的基础上生产LSI。在步骤ST7中,评估在试制基础上生产的LSI,例如,以确定响应预定的输入是否获得正确的输出、甚至在输入有意延迟到一定程度时是否获得正确的输出,以及甚至存在频率变化或电压变化时是否获得正确的输出。

当不存在逻辑错误而有充分的计时余量时,确定在步骤ST8中不存在问题。流程进行到步骤ST9,开始批量生产。

在步骤ST8中检测到问题时,在步骤ST10中进行网络列表纠正,因此重写配置与布线所用的网络列表100。

因此,纠正了任何逻辑错误。因延迟量的过大或不足而存在计时偏移时,为了在具有问题的通道上减少延迟量或增加延迟量,通过ECO单元纠正电路部分。

再一次执行步骤ST4至ST7中的通过配置与布线的布局设计、光掩模制造、LSI试生产和LSI评估。在步骤ST8中确定问题已解决时,工艺进行到步骤ST9中的批量生产。然而,当问题解决不充分时,或者当发现另一个问题时,重复步骤ST4至ST8和步骤ST10,直到问题解决。

在再一次进行布局设计中,通过在已经设置ECO填充物的位置上设置所希望的ECO逻辑单元,在“掩模后ECO”的流程中进行纠正。

此时,仅通过从第一接触(1C)在上层中进行纠正就可以纠正错误。当电路具有验证痕迹记录或者客户要求的规范不严格时,例如,在批量生产时,在部分LSI上可以执行优先评估,而不执行图8所示的试生产。就是说,当希望缩短TAT时,在处理完成到栅极的LSI批量生产时的晶片组(在一个时期中要处理的晶片的集合)被事先停机。以封装组件作为评估样品评估晶片的一部分或者评估的芯片。在评估中没有发现问题时,制造和批量生产相同晶片批量的其它晶片。

由此,可以缩短TAT。

下面,将详细描述上述ECO单元构造的优点。

第一优点是,甚至在共同单元长度(所谓的单元高度)很小时,也能配线,而不牺牲晶体管的栅极宽度。

通常,包括在基于标准单元的ASIC和ASSP等中的ECO单元的单元高度(共同单元长度方向上的单元尺寸)需要与标准单元SC的单元高度的相符。由于近期的半导体已经被小型化和提高了集成度,已经降低了标准单元SC的高度(共同单元长度方向上的单元尺寸)。因此,ECO单元的布局设计正在变难。

第二优点是与焊盘布置的良好兼容性,以抑制晶体管特性上的变化。

由于半导体已经被小型化,晶体管水平上的变化已经提高。因此,栅极金属(GM)的图案形状需要一形状以使给沟道施加的电场均匀。因此,在栅极金属(GM)的图案形状上具有更大的限制。

具体地讲,当接触提供在标准单元SC的共同单元长度方向上的两个端部的第一配线层(1M)和栅极金属(GM)之间时,制造时晶体管的性能会变化。因此,接触需要提供在(标准)单元的中间部分。

根据本实施例具有金属配线交叉部分211的栅极焊盘部分21A和21B在配线与栅极金属的交叉集中的单元的中间部分上适合于配线和栅极金属的交叉。因此,当由于需要在共同单元长度方向上的中间部分周围设置栅极焊盘部分,而对栅极金属(GM)的图案形状存在很大限制时,本发明可以适当地与栅极电极的形状组合地应用。结果,在所采用的ECO单元中获得极好的晶体管特性,以加入到所希望的电路。

第三优点是,金属配线层可以仅用最少数目的第一配线层(1M)形成。

标准单元SC的布局设计中采用的金属层数在LSI制造成本上具有很大冲击。

尤其重要的是,所希望的LSI为诸如ASIC等的低成本,以具有少量的金属层。

节点改变(所采用配线层的水平转变)发生在标准单元SC的布局设计。

具体地讲,用(GM+1M)或(GM+1M+2M:第二配线层)进行布置设计。在此情况下,当然,(GM+1M+2M)使用更多的金属配线层,因此增加了LSI的制造成本。

在标准单元用(GM+1M)设计时,与ECO单元相比布局容易,这是因为栅极的形状可以自由确定。

另一方面,固定ECO单元的栅极形状。因此,在用(gate+1M)进行布局设计时,栅极形状需设计为能进行节点改变。

在这方面,本实施例可以通过金属配线交叉部分的形状形成下桥结构(underbridge structure),而不是采用第二配线层2M的节点改变。因此,可由对应于所用小的配线层数而降低成本。附带地,通过应用本发明可以略微增加任意单元长度方向上的单元尺寸。然而,对于任意单元长度方向上的单元扩大具有余量。另外,在很多情况下任意单元长度方向上的单元扩大执行到不必要的区域,因此不导致任何缺点。即使单元扩大是缺点,单元扩大也不干扰布置的规则性,与共同单元长度方向上的单元扩大不同,因此不是很大的缺点。

附带地,节点改变相当于在标准单元和ECO单元中进行。下桥结构用于任何单元中。

通常,在标准单元的情况下,栅极(和杂质扩散层)的平面图案形状可以自由确定,因此下桥结构可以相对易于制造。

另一方面,在ECO单元的情况下,在首先确定栅极形状后,单元间的连接和单元内的连接仅需第一接触(1C)和第一配线层(1M)进行。因此,在ECO单元中制作下桥结构比在标准单元中更加困难。

本发明可以应用于标准单元和ECO单元二者。然而,出于上述原因,当应用于ECO单元时,本发明具有大的作用。

如上所述,根据本实施例,能够提供这样的半导体集成电路,其可增加配线的自由度,而不增加金属配线的层数,并且具有不易改变晶体管特性的图案化的电路单元。

<6.修改示例>

例如,对ECO单元的平面图案形状为图1B所示的L-形状的情况进行了上面的描述。此时,栅极焊盘部分21A可以是任何形状,只要至少获得如图1C所示必要的长度L。然而,正如已经描述的,在图1B所示的左、右侧组合两个栅极焊盘部分的L-形状使得整个布置高效且减少空间。

在布置三个以上的栅极时,两侧的两个栅极之外的栅极的栅极焊盘部分优选对设置在左右侧之一的另一个栅极焊盘部分保持图1B的关系。在三个栅极的情况下,中间栅极的栅极焊盘部分形成至少部分具有L-形状的图案,该L-形状能与设置在左右任一侧的另一个栅极焊盘部分组合。在此情况下的“至少部分具有”是这样的效果:具有L-形状的部分之外的部分不需要存在,而在具有L-形状的部分之外的部分存在时,具有L-形状的部分之外部分的形状是任意的。

假设图1B中的栅极电极20B的栅极焊盘部分21B是中间的栅极焊盘部分,则中间的栅极焊盘部分和该中间的栅极焊盘部分左侧的另一个栅极焊盘部分21A的L-形状具有图1B中的相互关系。反过来假设图1B中的栅极电极20A的栅极焊盘部分21A是中间的栅极焊盘部分,则中间的栅极焊盘部分和中间的栅极焊盘部分右侧的另一个栅极焊盘部分21B的L-形状具有图1B中的相互关系。

在上面的描述中,ECO单元中的栅极焊盘部分希望满足栅极焊盘部分的最小长度L的要求。

然而,该要求可以由标准单元SC满足。因此,它足以使ECO单元和标准单元SC中的至少一个满足栅极焊盘部分的最小长度L的要求。

接下来,将描述包括阱中阱结构的截面结构的示例。

图10A是沿着图1B的X-X线剖取的示意性截面图。图10B是沿着图1B的Y-Y线剖取的示意性截面图。

图10A和图10B所示的半导体集成电路形成在由P型硅等制造的P型半导体基板(P基板1)中。

N阱10N在P基板1内形成为大且深。因此,N阱10N称为“深N阱”。

如图10B所示,比N阱10N具有小的面积和更浅的结的P阱10P形成在N阱10N内。

图1B所示的N阱10N表示从平面图案中附图中没有示出的元件隔离区域打开的部分。类似地,图1B所示的P阱10P表示从平面图案中附图中没有示出的元件隔离区域打开的部分。

附带地,可以任意采用这样的阱中阱结构。

本发明包含于2009年1月23日提交到日本专利局的日本优先权专利申请JP 2009-012955中公开的相关主题,其全部内容通过引用结合于此。

本领域的技术人员应当理解的是,在所附权利要求或其等同特征的范围内,根据设计需要和其他因素,可以进行各种修改、结合、部分结合和替换。

Claims (8)

1.一种半导体集成电路,包括:

多个标准单元,包括具有栅极电极的晶体管,并且彼此组合布置;

金属配线层,互连所述多个标准单元,以形成所希望的电路;以及

多个储备单元,具有栅极电极,所述多个储备单元与所述金属配线层不连接,并且设置在所述多个标准单元的周边,其中,

所述多个标准单元和所述多个储备单元的每个栅极电极都具有栅极焊盘部分和两个栅极手指部分,所述两个栅极手指部分从所述栅极焊盘部分延伸到在预定方向上彼此相对的侧,并且

所述多个储备单元的所述栅极焊盘部分在垂直于所述预定方向的方向上的长度等于或大于所述金属配线层中最小线宽的三倍与最小间隔距离的两倍的总和值。

2.根据权利要求1所述的半导体集成电路,

其中所述预定方向是使一个单元长度成为预定的统一长度的共同单元长度方向,并且

所述多个储备单元的所述栅极焊盘部分具有金属配线交叉部分,所述金属配线交叉部分在垂直于所述共同单元长度方向的任意单元长度方向上的长度等于或大于所述金属配线层中所述最小线宽的三倍与所述最小间隔距离的两倍的总和值。

3.根据权利要求2所述的半导体集成电路,其中所述多个储备单元的所述栅极焊盘部分具有主干部分和所述金属配线交叉部分,并且所述金属配线交叉部分具有从所述主干部分延伸到所述任意单元长度方向上的至少一侧的L-形状平面图案部分。

4.根据权利要求3所述的半导体集成电路,

其中所述多个储备单元具有包括所述栅极焊盘部分的多个所述栅极电极,

在储备单元内彼此相邻的两个所述栅极焊盘部分的每一个都具有包括所述主干部分和所述金属配线交叉部分的所述L-形状平面图案部分,并且

所述两个栅极焊盘部分之一的所述L-形状平面图案部分和另一个栅极焊盘部分的L-形状平面图案部分彼此组合,以包含在矩形区域中,并且设置为彼此邻近。

5.根据权利要求1所述的半导体集成电路,

其中所述多个储备单元具有包括所述栅极焊盘部分的多个所述栅极电极,并且

储备单元内彼此相邻的两个所述栅极焊盘部分的各自的至少一部分彼此组合,以包含在矩形的区域中,并且设置为彼此邻近。

6.根据权利要求1所述的半导体集成电路,

其中所述半导体集成电路具有多个电路块,并且

至少同一电路块内所述预定方向上的单元长度在所述多个标准单元和所述多个储备单元之间、所述多个标准单元之间以及所述多个储备单元之间是相同的。

7.一种半导体集成电路,包括:

多个标准单元,包括具有栅极电极的晶体管,并且彼此组合布置;

金属配线层,互连所述多个标准单元,以形成所希望的电路;以及

多个储备单元,具有栅极电极,并且所述多个储备单元设置在所述多个标准单元的周边,其中,

所述多个标准单元和所述多个储备单元的每个栅极电极都具有栅极焊盘部分和两个栅极手指部分,所述两个栅极手指部分从所述栅极焊盘部分延伸到在预定方向上彼此相对的侧,并且

所述多个储备单元的所述栅极焊盘部分在垂直于所述预定方向的方向上的长度等于或大于所述金属配线层中最小线宽的三倍与最小间隔距离的两倍的总和值;

其中所述金属配线层连接到所述多个储备单元中的至少一个预定储备单元,由此所述预定储备单元形成所述所希望的电路的一部分,并且

所述预定储备单元采用所述栅极焊盘部分中长度等于或大于所述总和值的部分作为下桥线,金属配线层中的第一金属配线与所述下桥线的中间部分交叉,并且在与所述第一金属配线相同的金属配线层中的第二金属配线和第三金属配线连接到所述下桥线的一个端部侧和另一个端部侧。

8.一种半导体集成电路,包括:

多个电路单元,包括晶体管,并且布置为彼此组合;以及

金属配线层,互连所述多个电路单元,以形成所希望的电路,

其中所述多个电路单元内的所述晶体管的栅极电极具有栅极焊盘部分和从所述栅极焊盘部分延伸到在预定方向上彼此相对的侧的两个栅极手指部分,并且

在形成所述所希望的电路的所述多个电路单元的至少一个中的所述栅极焊盘部分在垂直于所述预定方向的方向上的长度等于或大于所述金属配线层中最小线宽的三倍与最小间隔距离的两倍的总和值。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP012955/09 | 2009-01-23 | ||

| JP2009012955A JP5509599B2 (ja) | 2009-01-23 | 2009-01-23 | 半導体集積回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101794774A CN101794774A (zh) | 2010-08-04 |

| CN101794774B true CN101794774B (zh) | 2012-03-21 |

Family

ID=42353457

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2010101038722A Expired - Fee Related CN101794774B (zh) | 2009-01-23 | 2010-01-25 | 半导体集成电路 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7919793B2 (zh) |

| JP (1) | JP5509599B2 (zh) |

| CN (1) | CN101794774B (zh) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5552775B2 (ja) | 2009-08-28 | 2014-07-16 | ソニー株式会社 | 半導体集積回路 |

| CN102129493B (zh) * | 2011-03-02 | 2013-03-06 | 福州瑞芯微电子有限公司 | 数字ic设计流程中实现自动化eco网表的方法 |

| KR20130031036A (ko) | 2011-09-20 | 2013-03-28 | 삼성전자주식회사 | Eco 논리 셀 및 eco 논리 셀을 이용한 설계 변경 방법 |

| US9831230B2 (en) * | 2013-08-13 | 2017-11-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Standard cell layout, semiconductor device having engineering change order (ECO) cells and method |

| KR102419644B1 (ko) * | 2015-10-26 | 2022-07-11 | 삼성전자주식회사 | Eco 셀, 그것의 레이아웃 및 eco 셀을 포함하는 집적 회로 |

| CN108701653B (zh) * | 2016-02-25 | 2022-07-29 | 株式会社索思未来 | 半导体集成电路装置 |

| US10846452B2 (en) * | 2016-07-01 | 2020-11-24 | Globalfoundries Inc. | Method, apparatus and system for wide metal line for SADP routing |

| US9634026B1 (en) | 2016-07-13 | 2017-04-25 | Qualcomm Incorporated | Standard cell architecture for reduced leakage current and improved decoupling capacitance |

| US11488947B2 (en) * | 2019-07-29 | 2022-11-01 | Tokyo Electron Limited | Highly regular logic design for efficient 3D integration |

| US11270992B2 (en) * | 2019-11-05 | 2022-03-08 | Samsung Electronics Co., Ltd. | Semiconductor devices |

| US11488948B2 (en) | 2020-03-30 | 2022-11-01 | Samsung Electronics Co., Ltd. | Semiconductor devices, layout design methods for the same, and methods for fabricating the same |

| CN114664725A (zh) * | 2020-12-23 | 2022-06-24 | 华润微电子(重庆)有限公司 | GaN器件互联结构及其制备方法 |

| CN113161346B (zh) * | 2021-03-17 | 2022-04-01 | 长鑫存储技术有限公司 | 集成电路及其布局方法 |

| US11868697B2 (en) * | 2021-08-27 | 2024-01-09 | Taiwan Semiconductor Manufacturing Co., Ltd | Base layout cell |

| US20230298997A1 (en) * | 2022-03-17 | 2023-09-21 | Macronix International Co., Ltd. | Routing pattern |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0828485B2 (ja) * | 1988-06-20 | 1996-03-21 | 日本電信電話株式会社 | 相補型misマスタスライスlsiの基本セル |

| JP3130918B2 (ja) * | 1990-10-31 | 2001-01-31 | 富士通株式会社 | 設計変更用セル及びこれを用いたレイアウト方法 |

| JP3060673B2 (ja) * | 1991-11-13 | 2000-07-10 | 日本電気株式会社 | 半導体集積回路 |

| JP3152642B2 (ja) * | 1998-01-29 | 2001-04-03 | 三洋電機株式会社 | 半導体集積回路装置 |

| JP4620942B2 (ja) * | 2003-08-21 | 2011-01-26 | 川崎マイクロエレクトロニクス株式会社 | 半導体集積回路のレイアウト方法、そのレイアウト構造、およびフォトマスク |

| JP2006269900A (ja) | 2005-03-25 | 2006-10-05 | Yamaha Corp | 半導体集積回路の設計方法 |

| JP2007141971A (ja) * | 2005-11-15 | 2007-06-07 | Matsushita Electric Ind Co Ltd | 半導体集積回路の設計方法 |

| US7562326B2 (en) * | 2007-08-09 | 2009-07-14 | United Microelectronics Corp. | Method of generating a standard cell layout and transferring the standard cell layout to a substrate |

-

2009

- 2009-01-23 JP JP2009012955A patent/JP5509599B2/ja not_active Expired - Fee Related

- 2009-11-03 US US12/588,938 patent/US7919793B2/en not_active Expired - Fee Related

-

2010

- 2010-01-25 CN CN2010101038722A patent/CN101794774B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP5509599B2 (ja) | 2014-06-04 |

| US7919793B2 (en) | 2011-04-05 |

| JP2010171243A (ja) | 2010-08-05 |

| US20100187573A1 (en) | 2010-07-29 |

| CN101794774A (zh) | 2010-08-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101794774B (zh) | 半导体集成电路 | |

| USRE48831E1 (en) | Semiconductor integrated circuit | |

| US7919792B2 (en) | Standard cell architecture and methods with variable design rules | |

| US8039874B2 (en) | Semiconductor integrated circuit | |

| CN106407496B (zh) | 设计半导体装置的布图的方法和制造半导体装置的方法 | |

| US7800136B2 (en) | Semiconductor integrated circuit and semiconductor integrated circuit design method | |

| CN108400129B (zh) | 具有接触跨接线的集成电路 | |

| CN101673711B (zh) | 半导体集成电路器件及其制造方法 | |

| CN103035639A (zh) | 集成电路及其设计方法 | |

| TWI666561B (zh) | 用於在fdsoi中實施後偏置之放置及繞線方法 | |

| CN107463724B (zh) | 用于设计和制造半导体器件的方法以及相应的半导体器件 | |

| US7747976B2 (en) | Semiconductor cell with power layout not contacting sides of its rectangular boundary and semiconductor circuit utilizing semiconductor cells | |

| CN112310224A (zh) | 半导体器件 | |

| JPH1050849A (ja) | シミュレーション方法及び装置 | |

| US20080029786A1 (en) | Integrated circuit with spare cells | |

| US20230097189A1 (en) | Integrated circuit layout including standard cells and method to form the same | |

| US20040183103A1 (en) | Semiconductor integrated circuit having an oblique global signal wiring and semiconductor integrated circuit wiring method | |

| JP4229998B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US20060097395A1 (en) | Integrated circuit design for routing an electrical connection | |

| JP2011199034A (ja) | 半導体装置 | |

| CN115831970A (zh) | 集成电路器件及制造方法 | |

| JP5630856B2 (ja) | 半導体装置 | |

| US20230290767A1 (en) | Semiconductor devices | |

| US20230099326A1 (en) | Integrated circuit, method for forming a layout of integrated circuit using standard cells | |

| CN118471948A (zh) | 集成电路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20120321 Termination date: 20220125 |