CN100576450C - 制造半导体器件的方法 - Google Patents

制造半导体器件的方法 Download PDFInfo

- Publication number

- CN100576450C CN100576450C CN200510116124A CN200510116124A CN100576450C CN 100576450 C CN100576450 C CN 100576450C CN 200510116124 A CN200510116124 A CN 200510116124A CN 200510116124 A CN200510116124 A CN 200510116124A CN 100576450 C CN100576450 C CN 100576450C

- Authority

- CN

- China

- Prior art keywords

- polysilicon layer

- layer

- polysilicon

- space

- recess

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 57

- 238000000034 method Methods 0.000 title claims description 67

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims abstract description 188

- 229920005591 polysilicon Polymers 0.000 claims abstract description 188

- 239000000758 substrate Substances 0.000 claims abstract description 51

- 238000009413 insulation Methods 0.000 claims abstract description 46

- 238000004519 manufacturing process Methods 0.000 claims abstract description 13

- 238000005530 etching Methods 0.000 claims description 33

- 238000005516 engineering process Methods 0.000 claims description 28

- 230000008569 process Effects 0.000 claims description 18

- 238000001039 wet etching Methods 0.000 claims description 14

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 claims description 10

- 230000015572 biosynthetic process Effects 0.000 claims description 9

- 239000000203 mixture Substances 0.000 claims description 7

- 238000005498 polishing Methods 0.000 claims description 5

- 238000006243 chemical reaction Methods 0.000 claims description 2

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 claims 2

- 239000000908 ammonium hydroxide Substances 0.000 claims 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims 2

- QOSATHPSBFQAML-UHFFFAOYSA-N hydrogen peroxide;hydrate Chemical compound O.OO QOSATHPSBFQAML-UHFFFAOYSA-N 0.000 claims 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 22

- 239000000243 solution Substances 0.000 description 17

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 14

- 238000007667 floating Methods 0.000 description 14

- 229920002120 photoresistant polymer Polymers 0.000 description 8

- 239000000377 silicon dioxide Substances 0.000 description 8

- 239000011248 coating agent Substances 0.000 description 7

- 238000000576 coating method Methods 0.000 description 7

- 239000012535 impurity Substances 0.000 description 7

- 229910052814 silicon oxide Inorganic materials 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 239000003085 diluting agent Substances 0.000 description 5

- 239000007789 gas Substances 0.000 description 5

- 239000006227 byproduct Substances 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- 229910021332 silicide Inorganic materials 0.000 description 4

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 4

- 230000008878 coupling Effects 0.000 description 3

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 230000006872 improvement Effects 0.000 description 3

- 229920000620 organic polymer Polymers 0.000 description 3

- 238000012797 qualification Methods 0.000 description 3

- -1 ring fluororesin Polymers 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- 238000001505 atmospheric-pressure chemical vapour deposition Methods 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- POLCUAVZOMRGSN-UHFFFAOYSA-N dipropyl ether Chemical compound CCCOCCC POLCUAVZOMRGSN-UHFFFAOYSA-N 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000003780 insertion Methods 0.000 description 2

- 230000037431 insertion Effects 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 150000004291 polyenes Chemical class 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 2

- 229910021342 tungsten silicide Inorganic materials 0.000 description 2

- 238000001947 vapour-phase growth Methods 0.000 description 2

- VTWDKFNVVLAELH-UHFFFAOYSA-N 2-methylcyclohexa-2,5-diene-1,4-dione Chemical compound CC1=CC(=O)C=CC1=O VTWDKFNVVLAELH-UHFFFAOYSA-N 0.000 description 1

- 229910019044 CoSix Inorganic materials 0.000 description 1

- VGGSQFUCUMXWEO-UHFFFAOYSA-N Ethene Chemical compound C=C VGGSQFUCUMXWEO-UHFFFAOYSA-N 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- UFWIBTONFRDIAS-UHFFFAOYSA-N Naphthalene Chemical compound C1=CC=CC2=CC=CC=C21 UFWIBTONFRDIAS-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 229910002367 SrTiO Inorganic materials 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000002784 hot electron Substances 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 230000008447 perception Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000002002 slurry Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 230000005641 tunneling Effects 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

Abstract

一种制造半导体器件的方法,包括,在衬底上形成绝缘图形。绝缘图形具有露出衬底表面的至少一个开口。然后,在衬底上形成第一多晶硅层,以便第一多晶硅层填充开口。第一多晶硅层还包括在其中的空隙。第一多晶硅层的上部被除去,以便空隙扩大到凹部,以及凹部被露出。在衬底上形成第二多晶硅层,以便第二多晶硅层填充凹部。

Description

要求的优先权

根据35 USC§119,要求2004年10月26日申请的韩国专利申请号2004-85629的优先权,在此将其内容全部引入作为参考。

技术领域

本发明的例子实施例总的来说涉及制造半导体器件的方法。更具体,本发明涉及在半导体器件的制造过程中除去多晶硅层中形成的空隙的方法。

背景技术

通常,半导体存储器件分为易失性存储器和非易失性存储器,易失性存储器包括动态随机存取存储器(DRAM)和静态随机存取存储器(SRAM),非易失性存储器包括只读存储器(ROM)、电可擦和可编程ROM(EEPROM)以及快闪存储器。经过一段时间之后,易失性存储器中的存储的数据丢失,但是,该数据具有快速输入/输出功能。相反,经过一段时间之后,非易失性存储器中的数据不丢失,但是,数据输入/输出功能比易失性存储器更慢。

快闪存储器通常使用福勒-诺德海姆(F-N)隧穿效应或沟道热电子注射效应输入/输出数据。

在制造快闪存储器单元的一般方法中,可以在半导体衬底上设置隔离层。在隔离层上可以形成氧化物层。氧化物层可以被构图,直至部分半导体衬底被露出,以形成氧化物层图形。在后续步骤中,可以在露出部分上形成浮栅。在所得结构上可以顺序地形成隧道氧化物层和第一多晶硅层。第一多晶硅层可以被平整,直至隧道氧化物层被露出,以形成浮栅。然后隧道氧化物层和氧化物层图形可以被部分地刻蚀。在所得结构上可以形成介质层。在介质层上可以顺序地形成第二多晶硅层、硅化钨层以及硬掩模层。第二多晶硅层、钨层以及硬掩模层可以被构图,以形成控制栅。杂质可以被注入通过浮栅露出的部分半导体衬底中,以形成杂质区。

根据上述方法,浮栅由部分地露出半导体衬底的氧化物层图形自对准。

最近,随着半导体器件变得更集成,被部分地露出半导体衬底的氧化物层图形限定的开口的高宽比也增加。当高宽比增加时,由于氧化物层图形的几何尺寸,在用于填充开口的多晶硅层中可能产生空隙。

当多晶硅层被平整时,空隙可以被露出。空隙可能损坏浮栅上的介质层的击穿电压性能,和/或可以减小快闪存储器的耦合比。空隙也可以损坏介质层的漏电流性能。

发明内容

本发明涉及一种制造半导体器件的方法,其减小多晶硅层中的空隙的效果。

在本发明的实施例中,一种制造半导体器件的方法包括在衬底上形成绝缘图形。绝缘图形具有露出衬底表面的至少一个开口。

然后,在衬底上形成第一多晶硅层,以便第一多晶硅层填充开口。第一多晶硅层也包括在其中的空隙。第一多晶硅层的上部被除去,以便空隙扩大到凹部,以及凹部被露出。在衬底上形成第二多晶硅层,以便第二多晶硅层填充凹部。

附图说明

参考附图从其示例性实施例的详细描述将更明白本发明,其中:

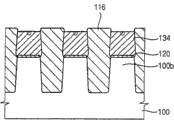

图1至12是说明根据本发明的实施例制造半导体器件的方法的剖面图;

图13至17是说明根据本发明的另一实施例制造半导体器件的方法的剖面图;以及

图18至22是说明根据本发明的另一实施例制造半导体器件的方法的剖面图。

具体实施方式

现在参考附图更完全地描述本发明,附图中示出了本发明的例子实施例。但是,本发明可以以许多不同的形式体现,不应该被认为是局限于在此阐述的实施例。相反,这些实施例被提供作为教导例子。在图中,为了清楚可以放大层和区域的尺寸和相对尺寸。

应当理解,当元件或层被称为在其它元件或层“上”、“连接到”或“耦合到”其它元件或层时,它可以被直接连接或耦合到其他元件,或可以存在插入的元件或层。相反,当一个元件称为直接在其它元件或层“上”或“直接连接到”或“直接耦合到”其它元件或层时,不存在插入元件或层。在整篇中,相同的数字始终指相同的元件。在此使用的术语“和/或”包括一个或多个相关列项的任意和所有组合。

应当理解,尽管在此可以使用术语第一、第二等来描述各个元件、组件、区域、和/或部分,但是这些元件、组件、区域、层和/或部分不应该受这些术语限制。这些术语仅仅是用来使元件、组件、区域、层或部分与其它区域、层或部分相区别。因此,在不脱离本发明的教导的条件下,下面论述的第一元件、组件、区域、层或部分可以称为第二元件、组件、区域、层或部分。

为了便于描述,在此可以使用空间相对术语,例如“在...底下”,“在...下面”,“下”,“在...之上”,“向上”,“上”等来描述一个元件或部件与图中所示的另一(些)元件或部件的关系。应当理解空间相对术语是用来包括除图中描绘的取向之外的使用或操作中器件的不同取向。例如,如果图中的器件被翻转,那么描述为在其他元件或部件“下面”或“底下”的元件将定向在其他元件或部件“上面”。因此示例性术语“在...之下”可以包括“在...之上”和“在...之下”的两种取向。器件可以被另外定向(旋转90度或其他取向),由此解释在此使用的空间相对描述词。

在此使用的专业词汇是仅仅用于描述特定的实施例,而不打算限制本发明。如在此使用的单数形式“a”,“an”和“the”同样打算包括复数形式,除非上下文另外清楚地表明。还应当理解,说明书中使用术语“comprises”和/或“comprising”说明陈述的部件、整体、步骤、操作、元件、和/或组件的存在,但是不排除存在或增加一个或多个其他部件、整体、步骤、操作、元件、组件和/或其组。

在此参考剖面图描述本发明的实施例,剖面图是本发明的理想化实施例(和中间结构)的示意图。照此,将预想由于制造工艺和/或容差图例形状的变化。因此,本发明的实施例不应该被认为是局限于在此图示的区域的特定形状,而是将包括由制造所得的形状的偏差。例如,图示为矩形的注入区一般地将具有圆润的或弯曲的特点和/或在其边缘具有注入浓度的梯度,而不是从注入区至非注入区的二元变化。同样,通过注入形成的掩埋区可以引起掩埋区和通过其进行注入的表面之间区域中发生某些注入。因此,图中所示的区域本质上是示意性的,且它们的形状不打算图示器件区域的实际形状,以及不打算限制本发明的范围。

除非另外限定,在此使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解相同的意思。还应当理解例如在通常使用的词典中定义的那些术语应该解释为具有符合相关技术的环境中的意思且不被理想化解释或过度地形式感知,除非在此清楚地限定。

图1至12是说明根据本发明的实施例制造半导体器件的方法的剖面图。

图1是说明在半导体衬底上形成的衬垫氧化物层和掩模层的剖面图,以及图2是由图1中的掩模层形成的掩模图形的剖面图。

参考图1和2,在半导体衬底100如硅晶片上可以形成衬垫氧化物层102,然后在衬垫氧化物层102上可以形成掩模层104。

可以通过使用SiH2Cl2气体、SiH4气体和NH3气体的低压化学气相淀积(LPCVD)工艺或等离子体增强化学气相淀积(PECVD)工艺,在衬垫氧化物层102上形成掩模层104至约的厚度,掩模层104可以包括氮化硅。

在掩模层104上可以形成光刻胶膜(未示出)。光刻胶膜可以通过光刻工艺部分地构图,以在掩模层104上形成光刻胶图形106。通过光刻胶图形106可以部分地露出掩模层104。

在图2中,可以使用光刻胶图形106作为刻蚀掩模,顺序地刻蚀衬垫氧化物层102和掩模层104,以形成露出隔离区100a的掩模图形108和衬垫氧化物层图形110。具体,掩模图形108和衬垫氧化物层图形110限定露出隔离区100a的第一开口112。

在例子本实施例中,通过使用等离子体或反应离子刻蚀的干法刻蚀工艺可以刻蚀衬垫氧化物层102和掩模层104。

在形成掩模图形108和衬垫氧化物图形110之后,通过使用O2等离子体的灰化工艺和/或剥离工艺,从掩模图形108除去光刻胶图形106。

图3是说明使用图2中的掩模图形在半导体衬底的表面部分形成的沟槽的剖面图。图4是说明具有场绝缘图形的沟槽的剖面图。

参考图3和4,使用掩模图形108作为刻蚀掩模刻蚀隔离区100a,以在半导体衬底100内形成沟槽114,在第一方向上跨越半导体衬底100(例如,进入和出自)。沟槽114可以具有约1,000至约的深度,例如,约

如上所述,在使用光刻胶图形106形成第一开口112之后,可以使用掩模图形108形成沟槽114。选择性地,可以使用光刻胶图形106在一个处理室中同时就地形成第一开口112和沟槽114。

在沟槽114和第一开口112中可以形成场绝缘层(未示出)。场绝缘层可以包括氧化硅,如不掺杂的硅玻璃(USG)、四乙基原硅酸酯(TEOS)以及高密度等离子体(HDP)氧化物。在例子实施例中,使用包括SiH4气体、氧气(O2)以及氩气(Ar)的等离子源形成的HDP氧化物可以用来形成场绝缘层。

场绝缘层可以通过化学机械抛光(CMP)工艺来平整,直到掩模图形108的表面被露出,以形成场绝缘图形116。场绝缘图形116可以用作隔离层,以及可以限定半导体衬底100的有源区100b。

图5是说明露出由图4中的场绝缘图形116限定的有源区100b的第二开口的剖面图。

参考图5,可以通过干法刻蚀工艺或湿法刻蚀工艺除去掩模图形108和衬垫氧化物层图形110,以形成露出有源区100b的第二开口118。第二开口118被场绝缘图形116限定。例如,湿法刻蚀工艺可以使用包括磷和稀释的氢氟酸溶液的蚀刻液。在除去掩模图形108和衬垫氧化物层110中,可以部分地刻蚀场绝缘图形116的表面部分。

图6是说明在图5中的有源区和场绝缘图形上形成的第一多晶硅层的剖面图。

参考图6,可以在露出的有源区100b上形成第一介质层(或隧道氧化物层)120。第一介质层120可以通过热氧化工艺由氧化硅来形成。选择性地,第一介质层可以由掺有氟(F)的氧化硅层、掺有碳(C)的氧化硅层和/或具有低介电常数的介质层形成。

具有低介电常数的介质层可以包括有机聚合物如聚烯丙醚(polyallylether)树脂、环氟树脂、硅氧烷共聚物、氟化的聚烯丙醚树脂、五氟苯乙烯(pentafluorinestyrene)、聚四氟苯乙烯(polytetrafluorinestyrene)树脂、氟化的聚酰亚胺树脂、氟化的聚萘(polynaftalene)以及氟化的多晶硅-金属硅化物(polycide)树脂。这些有机聚合物可以单独使用或组合使用。有机聚合物可以通过等离子体增强的化学气相淀积(PECVD)、高密度等离子体化学气相淀积(HDP-CVD)、大气压化学气相淀积(APCVD)和/或旋涂工艺形成。

在第一介质层120和场绝缘图形116上可以形成第一多晶硅层122,以及第一多晶硅层122可以填充第二开口118。在例子实施例中,第一多晶硅层122可以通过低压化学气相淀积(LPCVD)来形成。可以通过杂质扩散工艺、离子注入工艺和就地掺杂工艺将杂质注入第一多晶硅层122。

当形成第一多晶硅层122时,由于场绝缘图形116和第二开口的几何尺寸,在第一多晶硅层122内可能形成具有几十埃宽度的空隙124。空隙124的尺寸和数目可以与第二开口118的高宽比成正比。空隙124可能损坏随后形成的浮栅的电性能。空隙124可以在第一方向中延伸。此外,一般,在第一方向中局部地布置多个空隙124。

图7是说明图5中的第二开口中形成的第一多晶硅图形的剖面图。

参考图7,第一多晶硅层122可以被平整,以在第二开口118中形成第一初步多晶硅图形126。第一多晶硅层122可以通过CMP工艺抛光,直至场绝缘图形116的表面被露出,以在第二开口118中形成第一初步多晶硅图形126。在第一初步多晶硅图形126的形成过程中,该平面化可以露出第一多晶硅层122中的空隙124。露出的空隙124a可以具有“V”形剖面图,以及具有约50至的宽度。通过第一方向上的第一初步多晶硅图形126的上表面的中心部分可以断续地露出多个露出的空隙124a。

图8是说明图5中的第二开口中形成的第二多晶硅图形的剖面图。

在例子实施例中,可以通过湿法刻蚀工艺部分地刻蚀第一初步多晶硅图形126,以形成第二初步多晶硅图形128。刻蚀工艺可以增加露出空隙124a的尺寸,产生具有约100至约的平均宽度的凹部130。湿法刻蚀工艺可以使用蚀刻液如标准的清洗液(SC-1)或新标准清洗液(NSC-1)。在刻蚀第一初步多晶硅图形126中产生的、残留在第一初步多晶硅图形126上的浆料以及副产物被除去。

NSC-1可以包括约3-10∶1∶60-200的摩尔比的NH4OH、H2O2和H2O,可以是约4∶1∶95的摩尔比。在示例性实施例中,可以在约70至约90℃的温度下,例如约80℃下执行该刻蚀工艺。

当第一初步多晶硅图形126被部分地刻蚀,以产生第二初步多晶硅图形128时,场绝缘图形116的表面也可能被部分地刻蚀。例如,如果在约70℃的温度下使用蚀刻剂如包括约1∶4∶20的摩尔比的NH4OH、H2O2和H2O的SC-1刻蚀第一初步多晶硅图形126,那么第一初步多晶硅图形126的多晶硅和第一绝缘图形116的氧化硅之间的刻蚀选择率约为5.5∶1。换句话说,多晶硅的刻蚀速率可以约为以及氧化硅的刻蚀速率可以约为

选择性地,如果在约80℃的温度下,通过约4∶1∶95的摩尔比的NH4OH、H2O2和H2O的NSC-1刻蚀第一多晶硅图形126,那么第一初步多晶硅图形126和第一绝缘图形116的氧化硅之间的刻蚀选择率可以是约12.5∶1。换句话说,多晶硅的刻蚀速率可以约为以及氧化硅的刻蚀速率可以约为

通过扩大露出的空隙124a有选择地形成的凹部130具有“U”形状,由此用如下所述的后续步骤形成的第二多晶硅层填充凹部130更容易。

当第一初步多晶硅图形126被刻蚀时,SC-1或NSC1的过氧化氢(H2O2)和第一初步多晶硅图形126相互起反应,以在第二初步多晶硅图形128上形成包括氧化硅的副产物层(未示出)。副产物层可能损坏随后形成的浮栅的电性能。因此,可以通过使用稀释氢氟酸的湿法刻蚀工艺来除去副产物层。

图9是说明在图8中的第二初步多晶硅图形上形成的第二多晶硅层的剖面图。

参考图9,在初步第二多晶硅图形128和场绝缘图形116上形成第二多晶硅层132。如图所示,第二多晶硅层132填充凹部130。形成第二多晶硅层132的方法可以基本上与形成第一多晶硅层122的方法相同。

图10和11是说明图5中的第二开口中形成的第二多晶硅图形的剖面图。

参考图10,第二多晶硅层132可以被部分地除去,以形成多晶硅图形134,可以用作之后形成浮栅的部件。除填充凹部130的部分之外,第二多晶硅层132可以被除去,以形成多晶硅图形134。

参考图11,通过部分地除去第二多晶硅层132露出的多晶硅图形134的表面部分可以被连续地除去。多晶硅图形134的厚度可以根据浮栅的希望厚度来控制。

多晶硅图形134可以使用蚀刻剂,例如,SC-1和/或NSC-1来刻蚀。可以根据刻蚀时间控制用于部分地除去第二多晶硅层132和第二多晶硅图形134的刻蚀工艺,刻蚀时间对应于将被刻蚀的希望量。在示例性实施例中,希望的刻蚀量可以基本上等于或大于第二多晶硅层132的厚度。例如,希望的刻蚀量可以基本上等于或约大于1至大于第二多晶硅层132的厚度。

图12是说明图11中的浮栅上形成的控制栅层和第二介质层的剖面图。

参考图12,为了增加半导体器件如快闪存储器的耦合比,可以通过例如各向异性刻蚀工艺或各向同性刻蚀工艺刻蚀在半导体衬底100的表面上突出的场绝缘图形116的上部,以部分地露出多晶硅图形134的侧壁。为了减小或防止第一介质层120被刻蚀场绝缘图形116中使用的蚀刻剂损坏,在场绝缘图形116的刻蚀过程中不应该需要露出第一介质层120。其间,可以根据刻蚀时间控制刻蚀工艺。例如,可以使用包括稀释的氢氟酸溶液的蚀刻剂除去场绝缘图形116的上部。

在场绝缘图形116和多晶硅图形134上可以形成第二介质层136。第二介质层136的例子可以包括具有氧化物/氮化物/氧化物(ONO)的复合介质层和/或具有高介电常数的介质层。复合介质层可以通过LPCVD工艺来形成。用于形成具有高介电常数的介质层的氧化物的例子包括Y2O3、HfO2、ZrO2、Nb2O5、BaTiO3和SrTiO3。这些氧化物可以单独使用或组合使用。此外,具有高介电常数的介质层可以通过原子层淀积(ALD)工艺或CVD工艺来形成。第二介质层136、多晶硅图形134和第一介质层120可以被连续地构图,以形成浮栅。

在第二介质层136上可以形成控制栅层142。控制栅层142可以包括第一导电层138、第二导电层140,第一导电层138包括掺杂的多晶硅,第二导电层140包括金属硅化物,例如,硅化钨(WSix)、硅化钛(TiSix)、硅化钴(CoSix)和/或硅化钽(TaSix)。

控制栅层142可以通过刻蚀工艺构图,以在第二介质层136上形成在第二方向上延伸的控制栅(未示出),第二方向基本上垂直于第一方向。

选择性地,在栅极结构的两侧,杂质可以被注入半导体衬底100的有源区100b中,以形成源区/漏区(未示出),由此完成半导体器件,例如快闪存储器件。

在制造不超过90nm宽度的有源区的半导体器件中可以容易地采用本实施例的方法。此外,在制造具有超过约90nm宽度的有源区的半导体器件可以采用本实施例的方法。

图13至17是说明根据本发明的另一实施例制造半导体器件的方法的剖面图。

在本实施例中,可以执行与根据图1至5如上所述相同的工序步骤,以产生可以限定半导体衬底200的有源区202的场绝缘图形210,在跨越半导体衬底200的第一方向上延伸。如图13所示,场绝缘图形210可以具有位于半导体衬底200内的下部,以及在半导体衬底200上突出的上部。

可以用和图6中的第一介质层120和第一多晶硅层122相同的方法,在半导体衬底200上形成第一介质层212和第一多晶硅层。因此,如图13所示,可以通过化学机械抛光(CMP)工艺平整在场绝缘图形210和第一介质层212上形成的第一多晶硅层(未示出),以形成被场绝缘图形210和介质层212限定的第一初步多晶硅图形214。在半导体衬底200的有源区202上可以形成第一介质层212,第一介质层212可以包括氧化硅或低介电常数材料(或具有低介电常数的材料)。

在形成第一多晶硅层中可以产生第一初步多晶硅图形214的上部中的空隙216。

图14是说明图13中的第一介质层上形成的第二初步多晶硅图形的剖面图。图15是说明图13中的第一介质层上形成的第三初步多晶硅图形的剖面图。

参考图14和15,第一初步多晶硅图形214的表面部分可以被除去,以形成露出空隙216a的第二初步多晶硅图形218。第二初步多晶硅图形218的表面部分被除去,以形成第三初步多晶硅图形222和凹部220。

在例子实施例中,使用SC-1溶液和/或NSC-1溶液顺序地刻蚀第二初步多晶硅图形218和第三初步多晶硅图形222。通过扩大露出的空隙216a形成凹部220。凹部220可以形成在对应于露出空隙216a的位置处。露出的空隙216a可以具有约50至约的宽度,以及凹部220可以具有约100至约的平均宽度。

在形成凹部220的刻蚀工艺中通过SC-1溶液和/或NSC-1溶液中的过氧化氢(H2O2)和多晶硅之间的反应形成的氧化硅层(未示出)可以被除去。例如,可以使用稀释的氢氟酸除去氧化硅层。

图16是说明在图15中的第三初步多晶硅图形上形成的第二多晶硅层的剖面图。图17是说明图15中的第三初步多晶硅图形上形成的多晶硅图形的剖面图。

参考图16和17,在第三初步多晶硅图形222上形成第二多晶硅层224,以填充凹部220。第二多晶硅层224可以具有不少于约凹部130的平均宽度的0.5倍的厚度。第二多晶硅层224,例如,可以具有约50至约的厚度。

第二多晶硅层224可以被部分地除去,以形成将用作部分第一介质层212上的浮栅的多晶硅图形226。通过使用SC-1溶液和/或NSC-1溶液的湿法刻蚀工艺可以除去第二多晶硅层224。

选择性地,第二多晶硅层224和第三初步图形222可以被部分地和/或顺序地除去,以形成多晶硅图形226。

在形成多晶硅图形226之后,可以使用稀释的氢氟酸溶液部分地除去场绝缘图形210,以部分地露出多晶硅图形226的侧壁。在多晶硅图形226上顺序地形成第二介质层(未示出)和控制栅层(未示出)。控制栅层可以被构图,以形成在基本上垂直于多晶硅图形226的延伸方向的方向上延伸的控制栅。第二介质层、多晶硅图形226和第一介质层212可以被连续地构图,以露出半导体衬底的有源区202。在露出的有源区202上可以形成源区/漏区(未示出)。杂质可以被注入露出的有源区202中,以形成源区/漏区。

在此省略了与制造控制栅和源区/漏区相同的上述元件和步骤。

图18和22是说明根据本发明的另一示例性实施例制造半导体器件的方法的剖面图。

图18和19是说明在半导体衬底的有源区上形成的第一初步多晶硅图形和第一介质层的剖面图。

在该实施例,可以执行与上面根据图1至5所述相同的工序步骤,以产生形成在半导体衬底300上的场绝缘图形310。场绝缘图形310可以在跨越半导体衬底300的第一方向上延伸。在半导体衬底300中可以掩埋部分场绝缘图形310。半导体衬底300的有源区302可以被场绝缘图形310限定。

可以用和图6中的第一介质层120和第一多晶硅层122相同的方法,在半导体衬底300上形成第一介质层312和第一多晶硅层。在半导体衬底300上可以形成第一介质层312,例如氧化硅层。在第一介质层312和场绝缘图形310上可以形成第一多晶硅层(未示出)。第一多晶硅层可以充分地填充被场绝缘图形310和第一介质层312限定的空间。

可以执行化学机械抛光(CMP)工艺,直至场绝缘图形310的上表面被露出,由此在第一介质层312上形成第一初步多晶硅图形314。同时,通过CMP工艺露出第一多晶硅层中的空隙316。

在此省略了如参考图1至7所示的形成第一初步多晶硅图形314的工序步骤。

在CMP工序之后,可以使用稀释的氢氟酸溶液部分地除去场绝缘图形310的上部,以部分地露出第一初步多晶硅图形314的侧壁。

图20是说明图18中的第一介质层上形成的第二初步多晶硅图形的剖面图。

可以通过使用稀释的氢氟酸溶液的湿法刻蚀工艺除去,在刻蚀第一初步多晶硅图形314中,通过过氧化氢(H2O2)和第一初步多晶硅图形314之间的反应在第二初步多晶硅图形320上形成的副产物层,如氧化硅层。

选择性地,当在第一初步多晶硅图形314的上表面下布置空隙时,使用SC-1溶液和/或NSC-1溶液刻蚀需要的时间可以被控制,以通过第一初步多晶硅图形314的上表面露出空隙316。露出的空隙316可以被扩大,以形成凹部318。

图21是说明在图20中的第二初步多晶硅图形上形成的第二多晶硅层的剖面图。

参考图21,在第二初步多晶硅图形320和场绝缘图形310的上表面和侧壁上可以形成第二多晶硅层322。

如图21所示,在第二初步多晶硅图形320上可以形成第二多晶硅层322,以填充空隙316。第二多晶硅层322可以具有不少于约凹部318的平均宽度的0.5倍的厚度。例如,第二多晶硅层322可以具有约50至约的厚度。

图22是说明图18中的第二介质层中形成的第二多晶硅图形的剖面图。

参考图22,第二多晶硅层322和第二初步多晶硅图形320的一部分可以被部分地除去,以形成多晶硅图形324。可以根据刻蚀时间控制形成多晶硅图形324的刻蚀工艺。在示例性实施例中,希望的厚度可以不少于第二多晶硅层322的厚度。因此,场绝缘图形310上的部分第二多晶硅层322可以被完全地除去。

在多晶硅图形324上可以顺序地形成第二介质层(未示出)和控制栅层(未示出)。控制栅层可以被构图,以形成在垂直于第一方向的第二方向上延伸的控制栅。第二介质层、多晶硅图形324和第一介质层312可以被连续地构图,以露出半导体衬底300的有源区302。在露出的有源区302的两侧上可以形成源区/漏区(未示出)。

如上所述,在制造包括具有不超过约90nm宽度的有源区的半导体器件中,可以采用根据例子实施例制造半导体器件的方法。

根据本发明的例子实施例,在具有浮栅的半导体器件的制造过程中产生的空隙可以被除去。因此,浮栅上的第二介质层可以具有改进的绝缘击穿电压性能和/或漏电流性能。同时,可以增加电容器的耦合比。

此外,在制造包括具有不超过约90nm宽度的有源区的半导体器件中可以有效地采用形成本发明的例子实施例的方法。

上文是本发明的例子实施例的说明以及不允许认为是其限制。尽管已经描述了本发明的例子实施例,但是所属领域的技术人员将容易地理解在不显著地脱离本发明的新颖性教导和优点的条件下,例子实施例的许多改进是可能的。由此,所有这种改进确定为包括在权利要求限定的本发明的范围内。因此,应当理解上文是本发明的说明以及不允许认为是限于公开的特定实施例,以及对公开例子实施例以及其他实施例的改进确定为包括在附加的权利要求的范围内。

Claims (34)

1.一种制造半导体器件的方法,包括:

在衬底上形成绝缘图形,绝缘图形具有露出衬底表面的至少一个开口;

在衬底上形成第一多晶硅层,以便第一多晶硅层填充开口,第一多晶硅层包括在其中的空隙;

除去第一多晶硅层的上部,以便空隙扩大到凹部,以及凹部被露出;以及

在衬底上形成第二多晶硅层,以便第二多晶硅层填充凹部。

2.根据权利要求1的方法,其中在形成凹部中的除去步骤将空隙的宽度从50至100埃的范围扩大到100至300埃的范围。

3.根据权利要求2的方法,其中形成第二多晶硅层步骤形成不少于凹部宽度的0.5倍厚度的第二多晶硅层。

4.根据权利要求1的方法,其中除去步骤通过湿法刻蚀扩大空隙以形成凹部。

5.根据权利要求4的方法,其中湿法刻蚀工艺使用氢氧化铵、过氧化氢和水的混合物。

6.根据权利要求1的方法,其中该除去步骤包括:

平整第一多晶硅层,以露出空隙;以及

扩大空隙,以形成凹部。

7.根据权利要求6的方法,其中通过化学机械抛光执行平整步骤。

8.根据权利要求6的方法,其中扩大步骤通过湿法刻蚀扩大空隙以形成凹部。

9.根据权利要求6的方法,在形成第一多晶硅层步骤之前,还包括:

在衬底的露出部分上形成第一介质。

10.根据权利要求9的方法,在平整化步骤之后和在扩大步骤之前,还包括:

除去绝缘图形的上部,以露出第一多晶硅层的侧壁。

11.根据权利要求10的方法,其中除去绝缘图形的上部步骤不使绝缘图形的高度减小低于衬底的上表面。

12.根据权利要求10的方法,还包括:

除去第二多晶硅层的上部。

13.根据权利要求12的方法,其中除去第二多晶硅层的上部步骤刻蚀第二多晶硅层,以便不在凹部中的部分第二多晶硅层被完全地除去。

14.根据权利要求12的方法,还包括:

在除去第二多晶硅层的上部后,在衬底上形成第二介质层。

15.根据权利要求14的方法,还包括:

在第二介质层上形成控制栅层。

16.根据权利要求15的方法,其中沿第一方向形成第一多晶硅层,以及沿垂直于第一方向的第二方向形成第二介质和控制栅层。

17.根据权利要求15的方法,其中形成控制栅层步骤形成第一和第二导电层的控制栅层。

18.根据权利要求1的方法,其中除去步骤除去第一多晶硅层的至少部分上部,以及通过湿法刻蚀扩大空隙以形成凹部。

19.根据权利要求18的方法,其中湿法刻蚀除去第一多晶硅层的至少部分上部,以便空隙被露出。

20.根据权利要求18的方法,其中在湿法刻蚀第一多晶硅层之前除去步骤平整第一多晶硅层。

21.根据权利要求1的方法,在形成第一多晶硅层步骤之前,还包括:

在衬底的露出部分上形成第一介质。

22.根据权利要求21的方法,还包括:

除去第二多晶硅层的上部。

23.根据权利要求22的方法,其中除去第二多晶硅层的上部步骤刻蚀第二多晶硅层,以便不在凹部中的部分第二多晶硅层被完全地除去。

24.根据权利要求22的方法,在除去第二多晶硅层的上部步骤之后,还包括:

除去绝缘图形的上部,以露出第一多晶硅层的侧壁。

25.根据权利要求24的方法,其中除去绝缘图形的上部步骤不使绝缘图形的高度减小低于半导体衬底的上表面。

26.根据权利要求24的方法,还包括:

在除去第二多晶硅层的上部后,在衬底上形成第二介质层。

27.根据权利要求26的方法,还包括:

在第二介质层上形成控制栅层。

28.根据权利要求27的方法,其中沿第一方向形成第一多晶硅层,以及沿垂直于第一方向的第二方向形成第二介质和控制栅层。

29.根据权利要求27的方法,其中形成控制栅层步骤形成第一和第二导电层的控制栅层。

30.一种制造半导体器件的方法,包括:

形成具有开口的图形,开口露出衬底的表面;

在该图形和露出衬底的表面上形成第一多晶硅层,以填充开口;

平整第一多晶硅层,直至图形的上表面被露出,以在开口中形成第一多晶硅图形;

通过在第一多晶硅图形的上表面有选择地形成凹部来除去第一多晶硅图形中的空隙;

在该图形上形成第二多晶硅层;以及

部分地除去第二多晶硅层,以形成第二多晶硅图形。

31.根据权利要求30的方法,其中通过使用氢氧化铵(NH4OH)、过氧化氢(H2O2)和水(H2O)的混合物的湿法刻蚀工艺除去空隙。

32.根据权利要求31的方法,还包括除去通过过氧化氢(H2O2)和第一多晶硅图形之间的反应形成的氧化物。

33.根据权利要求30的方法,其中通过扩大空隙形成凹部,该空隙通过平整第一多晶硅层从第一多晶硅图形的上表面露出。

34.根据权利要求30的方法,其中形成凹部包括:

露出第一多晶硅图形中的空隙;以及

扩大露出的空隙,以形成凹部。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020040085629 | 2004-10-26 | ||

| KR1020040085629A KR100552588B1 (ko) | 2004-10-26 | 2004-10-26 | 반도체 장치의 제조 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1779916A CN1779916A (zh) | 2006-05-31 |

| CN100576450C true CN100576450C (zh) | 2009-12-30 |

Family

ID=36206703

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200510116124A Expired - Fee Related CN100576450C (zh) | 2004-10-26 | 2005-10-26 | 制造半导体器件的方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7582559B2 (zh) |

| JP (1) | JP5068442B2 (zh) |

| KR (1) | KR100552588B1 (zh) |

| CN (1) | CN100576450C (zh) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100763228B1 (ko) * | 2006-03-20 | 2007-10-04 | 삼성전자주식회사 | 비휘발성 반도체 메모리 소자의 제조 방법 |

| US7998809B2 (en) * | 2006-05-15 | 2011-08-16 | Micron Technology, Inc. | Method for forming a floating gate using chemical mechanical planarization |

| TWI316746B (en) | 2006-10-03 | 2009-11-01 | Macronix Int Co Ltd | Non-volatile memory and method of manufacturing the same |

| KR100790999B1 (ko) * | 2006-10-17 | 2008-01-03 | 삼성전자주식회사 | 더블 패터닝 공정을 이용하는 반도체 소자의 미세 패턴형성 방법 |

| CN101770954A (zh) * | 2008-12-29 | 2010-07-07 | 中芯国际集成电路制造(上海)有限公司 | 快闪存储器的形成方法 |

| KR101652879B1 (ko) | 2010-05-25 | 2016-09-02 | 삼성전자주식회사 | 비휘발성 메모리 소자 및 이의 제조방법 |

| KR20120026313A (ko) * | 2010-09-09 | 2012-03-19 | 삼성전자주식회사 | 비휘발성 메모리 소자 및 그 제조 방법 |

| US8722320B2 (en) * | 2011-07-27 | 2014-05-13 | Micron Technology, Inc. | Lithography method and device |

| US8846452B2 (en) * | 2012-08-21 | 2014-09-30 | Infineon Technologies Ag | Semiconductor device package and methods of packaging thereof |

| US20140273467A1 (en) * | 2013-03-14 | 2014-09-18 | Intermolecular Inc. | Polycrystalline-silicon etch with low-peroxide apm |

| CN104716084B (zh) * | 2013-12-12 | 2017-10-27 | 华邦电子股份有限公司 | 半导体元件的制造方法 |

| CN105336591B (zh) * | 2014-07-01 | 2018-10-23 | 中芯国际集成电路制造(上海)有限公司 | 浮栅的制作方法 |

| JP2017152531A (ja) * | 2016-02-24 | 2017-08-31 | 東京エレクトロン株式会社 | 基板処理方法 |

| US10559571B2 (en) | 2017-04-13 | 2020-02-11 | Samsung Electronics Co., Ltd. | Methods of fabricating semiconductor memory devices |

| CN110931432A (zh) * | 2018-09-19 | 2020-03-27 | 长鑫存储技术有限公司 | 半导体器件及其制备方法 |

| CN109616409B (zh) * | 2018-12-04 | 2021-03-23 | 武汉新芯集成电路制造有限公司 | 一种多晶硅沉积方法、闪存及其制作方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3362970B2 (ja) * | 1994-08-19 | 2003-01-07 | 株式会社東芝 | 不揮発性半導体記憶装置及びその製造方法 |

| JP3264326B2 (ja) | 1999-03-17 | 2002-03-11 | 日本電気株式会社 | 半導体装置の製造方法 |

| KR100356821B1 (ko) | 2000-02-28 | 2002-10-18 | 주식회사 하이닉스반도체 | 반도체장치의 비휘발성 메모리 소자 및 그 제조방법 |

| KR100415518B1 (ko) * | 2000-06-30 | 2004-01-31 | 주식회사 하이닉스반도체 | 플래쉬 메모리 셀의 제조 방법 |

| KR100400037B1 (ko) * | 2001-02-22 | 2003-09-29 | 삼성전자주식회사 | 콘택 플러그를 구비하는 반도체 소자 및 그의 제조 방법 |

| US6908862B2 (en) * | 2002-05-03 | 2005-06-21 | Applied Materials, Inc. | HDP-CVD dep/etch/dep process for improved deposition into high aspect ratio features |

| KR100590396B1 (ko) | 2002-07-04 | 2006-06-15 | 주식회사 하이닉스반도체 | 플래시 메모리 셀의 제조 방법 |

| KR100482366B1 (ko) * | 2002-07-15 | 2005-04-13 | 삼성전자주식회사 | 반도체 메모리 소자의 스토리지 캐패시터 제조방법 |

| KR100539275B1 (ko) * | 2004-07-12 | 2005-12-27 | 삼성전자주식회사 | 반도체 장치의 제조 방법 |

-

2004

- 2004-10-26 KR KR1020040085629A patent/KR100552588B1/ko active IP Right Grant

-

2005

- 2005-10-14 US US11/249,515 patent/US7582559B2/en not_active Expired - Fee Related

- 2005-10-20 JP JP2005305543A patent/JP5068442B2/ja not_active Expired - Fee Related

- 2005-10-26 CN CN200510116124A patent/CN100576450C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1779916A (zh) | 2006-05-31 |

| US7582559B2 (en) | 2009-09-01 |

| KR100552588B1 (ko) | 2006-02-15 |

| US20060088987A1 (en) | 2006-04-27 |

| JP5068442B2 (ja) | 2012-11-07 |

| JP2006128673A (ja) | 2006-05-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100576450C (zh) | 制造半导体器件的方法 | |

| US7410869B2 (en) | Method of manufacturing a semiconductor device | |

| US7459364B2 (en) | Methods of forming self-aligned floating gates using multi-etching | |

| KR100475081B1 (ko) | Sonos형 eeprom 및 그 제조방법 | |

| KR100436406B1 (ko) | 부유 게이트를 갖는 반도체 기억 장치 및 그 제조 방법 | |

| US7498233B2 (en) | Method of forming an insulation layer structure having a concave surface and method of manufacturing a memory device using the same | |

| US6570215B2 (en) | Nonvolatile memories with floating gate spacers, and methods of fabrication | |

| US7186607B2 (en) | Charge-trapping memory device and method for production | |

| US7902059B2 (en) | Methods of forming void-free layers in openings of semiconductor substrates | |

| US20080197403A1 (en) | Semiconductor device | |

| KR100313695B1 (ko) | 반도체 장치의 제조 방법 | |

| KR20030069800A (ko) | 단일 면 매립 스트랩 | |

| CN101022126B (zh) | 半导体器件及其相关制造方法 | |

| KR20030001230A (ko) | 반도체 장치 및 그 제조 방법 | |

| US6537880B1 (en) | Method of fabricating a high density NAND stacked gate flash memory device having narrow pitch isolation and large capacitance between control and floating gates | |

| JP2005530357A (ja) | 導電スペーサで拡張されたフローティングゲート | |

| KR100589058B1 (ko) | 불휘발성 메모리 장치 및 이를 형성하기 위한 방법 | |

| US6962852B2 (en) | Nonvolatile memories and methods of fabrication | |

| CN100446257C (zh) | 动态随机存取存储器及其制造方法 | |

| KR20060012695A (ko) | 반도체 장치의 제조 방법 | |

| KR100652383B1 (ko) | 반도체 장치의 제조 방법 | |

| KR20070064763A (ko) | 반도체 소자의 형성 방법 | |

| KR20060025262A (ko) | 반도체 장치의 제조 방법 | |

| KR20060112772A (ko) | 반도체 장치의 제조 방법 | |

| US20100124807A1 (en) | Method of manufacturing semiconductor device having step gates |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20091230 Termination date: 20211026 |

|

| CF01 | Termination of patent right due to non-payment of annual fee |