CN100524812C - 具有改进的ldmos设计的集成电路结构 - Google Patents

具有改进的ldmos设计的集成电路结构 Download PDFInfo

- Publication number

- CN100524812C CN100524812C CNB2003801057172A CN200380105717A CN100524812C CN 100524812 C CN100524812 C CN 100524812C CN B2003801057172 A CNB2003801057172 A CN B2003801057172A CN 200380105717 A CN200380105717 A CN 200380105717A CN 100524812 C CN100524812 C CN 100524812C

- Authority

- CN

- China

- Prior art keywords

- region

- semiconductor layer

- source

- conductivity type

- gate electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D48/00—Individual devices not covered by groups H10D1/00 - H10D44/00

- H10D48/30—Devices controlled by electric currents or voltages

- H10D48/32—Devices controlled by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H10D48/36—Unipolar devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

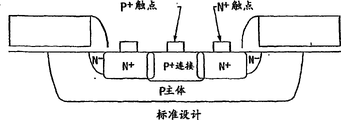

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/65—Lateral DMOS [LDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0281—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of lateral DMOS [LDMOS] FETs

- H10D30/0285—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of lateral DMOS [LDMOS] FETs using formation of insulating sidewall spacers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/393—Body regions of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0212—Manufacture or treatment of FETs having insulated gates [IGFET] using self-aligned silicidation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/83—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/62—Electrodes ohmically coupled to a semiconductor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/661—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes the conductor comprising a layer of silicon contacting the insulator, e.g. polysilicon having vertical doping variation

- H10D64/662—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes the conductor comprising a layer of silicon contacting the insulator, e.g. polysilicon having vertical doping variation the conductor further comprising additional layers, e.g. multiple silicon layers having different crystal structures

- H10D64/663—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes the conductor comprising a layer of silicon contacting the insulator, e.g. polysilicon having vertical doping variation the conductor further comprising additional layers, e.g. multiple silicon layers having different crystal structures the additional layers comprising a silicide layer contacting the layer of silicon, e.g. polycide gates

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/315,517 US6870218B2 (en) | 2002-12-10 | 2002-12-10 | Integrated circuit structure with improved LDMOS design |

| US10/315,517 | 2002-12-10 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1757118A CN1757118A (zh) | 2006-04-05 |

| CN100524812C true CN100524812C (zh) | 2009-08-05 |

Family

ID=32468724

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2003801057172A Expired - Fee Related CN100524812C (zh) | 2002-12-10 | 2003-12-09 | 具有改进的ldmos设计的集成电路结构 |

Country Status (8)

| Country | Link |

|---|---|

| US (3) | US6870218B2 (enExample) |

| JP (1) | JP2006510206A (enExample) |

| KR (1) | KR101030178B1 (enExample) |

| CN (1) | CN100524812C (enExample) |

| AU (1) | AU2003296321A1 (enExample) |

| DE (1) | DE10393858T5 (enExample) |

| TW (1) | TWI355074B (enExample) |

| WO (1) | WO2004053939A2 (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102681370A (zh) * | 2012-05-09 | 2012-09-19 | 上海宏力半导体制造有限公司 | 光刻套刻方法和提高ldmos器件击穿稳定性的方法 |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6870218B2 (en) * | 2002-12-10 | 2005-03-22 | Fairchild Semiconductor Corporation | Integrated circuit structure with improved LDMOS design |

| JP4800566B2 (ja) * | 2003-10-06 | 2011-10-26 | ルネサスエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| US7180132B2 (en) * | 2004-09-16 | 2007-02-20 | Fairchild Semiconductor Corporation | Enhanced RESURF HVPMOS device with stacked hetero-doping RIM and gradual drift region |

| JP4907920B2 (ja) * | 2005-08-18 | 2012-04-04 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US7736984B2 (en) * | 2005-09-23 | 2010-06-15 | Semiconductor Components Industries, Llc | Method of forming a low resistance semiconductor contact and structure therefor |

| CN100370625C (zh) * | 2005-10-14 | 2008-02-20 | 西安电子科技大学 | 可集成的高压p型ldmos晶体管结构及其制备方法 |

| KR100778861B1 (ko) * | 2006-12-12 | 2007-11-22 | 동부일렉트로닉스 주식회사 | Ldmos 반도체 소자의 제조 방법 |

| US8035159B2 (en) * | 2007-04-30 | 2011-10-11 | Alpha & Omega Semiconductor, Ltd. | Device structure and manufacturing method using HDP deposited source-body implant block |

| KR100840667B1 (ko) * | 2007-06-26 | 2008-06-24 | 주식회사 동부하이텍 | 수평형 디모스 소자 및 그 제조방법 |

| US8063443B2 (en) | 2007-10-30 | 2011-11-22 | Fairchild Semiconductor Corporation | Hybrid-mode LDMOS |

| JP5329118B2 (ja) * | 2008-04-21 | 2013-10-30 | セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー | Dmosトランジスタ |

| US7906810B2 (en) * | 2008-08-06 | 2011-03-15 | United Microelectronics Corp. | LDMOS device for ESD protection circuit |

| US8138558B2 (en) * | 2010-08-20 | 2012-03-20 | Great Wall Semiconductor Corporation | Semiconductor device and method of forming low voltage MOSFET for portable electronic devices and data processing centers |

| JP5700649B2 (ja) * | 2011-01-24 | 2015-04-15 | 旭化成エレクトロニクス株式会社 | 半導体装置の製造方法 |

| CN103456734B (zh) * | 2012-05-28 | 2016-04-13 | 上海华虹宏力半导体制造有限公司 | 一种非对称ldmos工艺偏差的监控结构及其制造方法 |

| US9337284B2 (en) * | 2014-04-07 | 2016-05-10 | Alpha And Omega Semiconductor Incorporated | Closed cell lateral MOSFET using silicide source and body regions |

| US10038063B2 (en) | 2014-06-10 | 2018-07-31 | International Business Machines Corporation | Tunable breakdown voltage RF FET devices |

| US9397090B1 (en) * | 2015-04-10 | 2016-07-19 | Macronix International Co., Ltd. | Semiconductor device |

| CN108493113A (zh) * | 2018-03-30 | 2018-09-04 | 北京时代民芯科技有限公司 | 一种低电阻抗辐照vdmos芯片的制造方法 |

| TWI666681B (zh) * | 2018-07-18 | 2019-07-21 | 帥群微電子股份有限公司 | 半導體功率元件及其製造方法 |

| CN111200020B (zh) * | 2019-04-15 | 2021-01-08 | 合肥晶合集成电路股份有限公司 | 高耐压半导体元件及其制造方法 |

| US20210020630A1 (en) * | 2019-04-15 | 2021-01-21 | Nexchip Semiconductor Co., Ltd. | High-voltage tolerant semiconductor element |

| US12295155B2 (en) * | 2020-07-14 | 2025-05-06 | Newport Fab, Llc | Asymmetric halo-implant body-source-tied semiconductor-on-insulator (SOI) device |

| US11581215B2 (en) * | 2020-07-14 | 2023-02-14 | Newport Fab, Llc | Body-source-tied semiconductor-on-insulator (SOI) transistor |

| CN116207142B (zh) * | 2023-05-04 | 2023-07-18 | 合肥晶合集成电路股份有限公司 | 一种半导体结构及其制作方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0747966A2 (en) * | 1995-06-07 | 1996-12-11 | Harris Corporation | High efficiency quasi-vertical DMOS in MOS or BICMOS process |

| US5792687A (en) * | 1996-08-01 | 1998-08-11 | Vanguard International Semiconductor Corporation | Method for fabricating high density integrated circuits using oxide and polysilicon spacers |

| US5930630A (en) * | 1997-07-23 | 1999-07-27 | Megamos Corporation | Method for device ruggedness improvement and on-resistance reduction for power MOSFET achieved by novel source contact structure |

| US6049104A (en) * | 1997-11-28 | 2000-04-11 | Magepower Semiconductor Corp. | MOSFET device to reduce gate-width without increasing JFET resistance |

| US6277695B1 (en) * | 1999-04-16 | 2001-08-21 | Siliconix Incorporated | Method of forming vertical planar DMOSFET with self-aligned contact |

Family Cites Families (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5578574A (en) * | 1978-12-09 | 1980-06-13 | Victor Co Of Japan Ltd | Manufacture of insulated-gate field-effect transistor |

| US4883767A (en) * | 1986-12-05 | 1989-11-28 | General Electric Company | Method of fabricating self aligned semiconductor devices |

| JPH03244135A (ja) * | 1990-02-22 | 1991-10-30 | New Japan Radio Co Ltd | Mosトランジスタの製造方法 |

| US5079608A (en) | 1990-11-06 | 1992-01-07 | Harris Corporation | Power MOSFET transistor circuit with active clamp |

| US5272098A (en) * | 1990-11-21 | 1993-12-21 | Texas Instruments Incorporated | Vertical and lateral insulated-gate, field-effect transistors, systems and methods |

| CN1019720B (zh) | 1991-03-19 | 1992-12-30 | 电子科技大学 | 半导体功率器件 |

| JPH0897410A (ja) * | 1994-07-01 | 1996-04-12 | Texas Instr Inc <Ti> | 自己整合した横型dmosトランジスタの製造法 |

| US5585294A (en) * | 1994-10-14 | 1996-12-17 | Texas Instruments Incorporated | Method of fabricating lateral double diffused MOS (LDMOS) transistors |

| EP0730309B1 (en) * | 1995-02-21 | 1998-10-14 | STMicroelectronics S.r.l. | A high voltage MOSFET structure with field plate electrode and process for its fabrication |

| US5567634A (en) * | 1995-05-01 | 1996-10-22 | National Semiconductor Corporation | Method of fabricating self-aligned contact trench DMOS transistors |

| EP0741416B1 (en) * | 1995-05-02 | 2001-09-26 | STMicroelectronics S.r.l. | Thin epitaxy RESURF ic containing HV p-ch and n-ch devices with source or drain not tied to grounds potential |

| KR0143459B1 (ko) * | 1995-05-22 | 1998-07-01 | 한민구 | 모오스 게이트형 전력 트랜지스터 |

| US5684319A (en) * | 1995-08-24 | 1997-11-04 | National Semiconductor Corporation | Self-aligned source and body contact structure for high performance DMOS transistors and method of fabricating same |

| JP3528420B2 (ja) * | 1996-04-26 | 2004-05-17 | 株式会社デンソー | 半導体装置およびその製造方法 |

| US5960275A (en) * | 1996-10-28 | 1999-09-28 | Magemos Corporation | Power MOSFET fabrication process to achieve enhanced ruggedness, cost savings, and product reliability |

| US5879968A (en) * | 1996-11-18 | 1999-03-09 | International Rectifier Corporation | Process for manufacture of a P-channel MOS gated device with base implant through the contact window |

| KR100204805B1 (ko) * | 1996-12-28 | 1999-06-15 | 윤종용 | 디엠오에스 트랜지스터 제조방법 |

| KR100225411B1 (ko) * | 1997-03-24 | 1999-10-15 | 김덕중 | LDMOS(a lateral double-diffused MOS) 트랜지스터 소자 및 그의 제조 방법 |

| US5907169A (en) * | 1997-04-18 | 1999-05-25 | Megamos Corporation | Self-aligned and process-adjusted high density power transistor with gate sidewalls provided with punch through prevention and reduced JFET resistance |

| EP0880183A3 (en) * | 1997-05-23 | 1999-07-28 | Texas Instruments Incorporated | LDMOS power device |

| US5854099A (en) * | 1997-06-06 | 1998-12-29 | National Semiconductor Corporation | DMOS process module applicable to an E2 CMOS core process |

| US6252278B1 (en) | 1998-05-18 | 2001-06-26 | Monolithic Power Systems, Inc. | Self-aligned lateral DMOS with spacer drift region |

| KR100301071B1 (ko) * | 1998-10-26 | 2001-11-22 | 김덕중 | 디모스(dmos)트랜지스터및그제조방법 |

| JP2000208759A (ja) * | 1999-01-12 | 2000-07-28 | Rohm Co Ltd | 半導体装置 |

| KR20000051294A (ko) * | 1999-01-20 | 2000-08-16 | 김덕중 | 전기적 특성이 향상된 디모스 전계 효과 트랜지스터 및 그 제조 방법 |

| US6198127B1 (en) | 1999-05-19 | 2001-03-06 | Intersil Corporation | MOS-gated power device having extended trench and doping zone and process for forming same |

| US6365932B1 (en) * | 1999-08-20 | 2002-04-02 | Denso Corporation | Power MOS transistor |

| US6376878B1 (en) | 2000-02-11 | 2002-04-23 | Fairchild Semiconductor Corporation | MOS-gated devices with alternating zones of conductivity |

| US7115946B2 (en) * | 2000-09-28 | 2006-10-03 | Kabushiki Kaisha Toshiba | MOS transistor having an offset region |

| JP2002314065A (ja) * | 2001-04-13 | 2002-10-25 | Sanyo Electric Co Ltd | Mos半導体装置およびその製造方法 |

| JP3431909B2 (ja) * | 2001-08-21 | 2003-07-28 | 沖電気工業株式会社 | Ldmosトランジスタの製造方法 |

| US6661042B2 (en) * | 2002-03-11 | 2003-12-09 | Monolithic System Technology, Inc. | One-transistor floating-body DRAM cell in bulk CMOS process with electrically isolated charge storage region |

| US6870218B2 (en) * | 2002-12-10 | 2005-03-22 | Fairchild Semiconductor Corporation | Integrated circuit structure with improved LDMOS design |

-

2002

- 2002-12-10 US US10/315,517 patent/US6870218B2/en not_active Expired - Fee Related

-

2003

- 2003-12-09 TW TW092134753A patent/TWI355074B/zh not_active IP Right Cessation

- 2003-12-09 AU AU2003296321A patent/AU2003296321A1/en not_active Abandoned

- 2003-12-09 KR KR1020057010197A patent/KR101030178B1/ko not_active Expired - Fee Related

- 2003-12-09 DE DE10393858T patent/DE10393858T5/de not_active Withdrawn

- 2003-12-09 CN CNB2003801057172A patent/CN100524812C/zh not_active Expired - Fee Related

- 2003-12-09 WO PCT/US2003/038931 patent/WO2004053939A2/en not_active Ceased

- 2003-12-09 JP JP2004559410A patent/JP2006510206A/ja active Pending

-

2005

- 2005-03-01 US US11/069,900 patent/US7220646B2/en not_active Expired - Lifetime

-

2007

- 2007-02-16 US US11/675,759 patent/US7608512B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0747966A2 (en) * | 1995-06-07 | 1996-12-11 | Harris Corporation | High efficiency quasi-vertical DMOS in MOS or BICMOS process |

| US5792687A (en) * | 1996-08-01 | 1998-08-11 | Vanguard International Semiconductor Corporation | Method for fabricating high density integrated circuits using oxide and polysilicon spacers |

| US5930630A (en) * | 1997-07-23 | 1999-07-27 | Megamos Corporation | Method for device ruggedness improvement and on-resistance reduction for power MOSFET achieved by novel source contact structure |

| US6049104A (en) * | 1997-11-28 | 2000-04-11 | Magepower Semiconductor Corp. | MOSFET device to reduce gate-width without increasing JFET resistance |

| US6277695B1 (en) * | 1999-04-16 | 2001-08-21 | Siliconix Incorporated | Method of forming vertical planar DMOSFET with self-aligned contact |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102681370A (zh) * | 2012-05-09 | 2012-09-19 | 上海宏力半导体制造有限公司 | 光刻套刻方法和提高ldmos器件击穿稳定性的方法 |

| CN102681370B (zh) * | 2012-05-09 | 2016-04-20 | 上海华虹宏力半导体制造有限公司 | 光刻套刻方法和提高ldmos器件击穿稳定性的方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050239253A1 (en) | 2005-10-27 |

| KR20050085383A (ko) | 2005-08-29 |

| KR101030178B1 (ko) | 2011-04-18 |

| AU2003296321A8 (en) | 2004-06-30 |

| WO2004053939A3 (en) | 2005-07-21 |

| US7220646B2 (en) | 2007-05-22 |

| US20040108548A1 (en) | 2004-06-10 |

| TWI355074B (en) | 2011-12-21 |

| WO2004053939A2 (en) | 2004-06-24 |

| CN1757118A (zh) | 2006-04-05 |

| US7608512B2 (en) | 2009-10-27 |

| AU2003296321A1 (en) | 2004-06-30 |

| DE10393858T5 (de) | 2007-03-15 |

| JP2006510206A (ja) | 2006-03-23 |

| US20070141792A1 (en) | 2007-06-21 |

| US6870218B2 (en) | 2005-03-22 |

| TW200503266A (en) | 2005-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100524812C (zh) | 具有改进的ldmos设计的集成电路结构 | |

| US7687335B2 (en) | Self aligned gate JFET structure and method | |

| US7649225B2 (en) | Asymmetric hetero-doped high-voltage MOSFET (AH2MOS) | |

| US7964933B2 (en) | Integrated circuit including power diode | |

| US8168494B2 (en) | Trench MOS transistor and method of manufacturing the same | |

| CN101661955B (zh) | 横向扩散金属氧化物半导体器件及其制造方法 | |

| KR100611111B1 (ko) | 고주파용 모오스 트랜지스터, 이의 형성 방법 및 반도체장치의 제조 방법 | |

| CN119050141A (zh) | 利用埋置绝缘层作为栅极介电质的高压晶体管 | |

| JP2003347546A (ja) | 垂直型dmos素子及びその製造方法 | |

| US7544558B2 (en) | Method for integrating DMOS into sub-micron CMOS process | |

| US20080009118A1 (en) | Metal oxide semiconductor device and fabricating method thereof | |

| US5512769A (en) | High breakdown voltage semiconductor device and method of fabricating the same | |

| KR0165347B1 (ko) | 고내압 트랜지스터 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20090805 Termination date: 20161209 |