CN100481444C - 模块集成电路芯片载体 - Google Patents

模块集成电路芯片载体 Download PDFInfo

- Publication number

- CN100481444C CN100481444C CNB038093618A CN03809361A CN100481444C CN 100481444 C CN100481444 C CN 100481444C CN B038093618 A CNB038093618 A CN B038093618A CN 03809361 A CN03809361 A CN 03809361A CN 100481444 C CN100481444 C CN 100481444C

- Authority

- CN

- China

- Prior art keywords

- carrier

- path

- platform

- pillar

- liner

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/14—Structural association of two or more printed circuits

- H05K1/141—One or more single auxiliary printed circuits mounted on a main printed circuit, e.g. modules, adapters

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0652—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00 the devices being arranged next and on each other, i.e. mixed assemblies

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06517—Bump or bump-like direct electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06572—Auxiliary carrier between devices, the carrier having an electrical connection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00011—Not relevant to the scope of the group, the symbol of which is combined with the symbol of this group

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01015—Phosphorus [P]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1532—Connection portion the connection portion being formed on the die mounting surface of the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0216—Reduction of cross-talk, noise or electromagnetic interference

- H05K1/023—Reduction of cross-talk, noise or electromagnetic interference using auxiliary mounted passive components or auxiliary substances

- H05K1/0231—Capacitors or dielectric substances

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0266—Marks, test patterns or identification means

- H05K1/0268—Marks, test patterns or identification means for electrical inspection or testing

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0296—Conductive pattern lay-out details not covered by sub groups H05K1/02 - H05K1/0295

- H05K1/0298—Multilayer circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/14—Structural association of two or more printed circuits

- H05K1/144—Stacked arrangements of planar printed circuit boards

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in the printed circuit board, e.g. insert mounted components [IMC]

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in the printed circuit board, e.g. insert mounted components [IMC]

- H05K1/183—Components mounted in and supported by recessed areas of the printed circuit board

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/04—Assemblies of printed circuits

- H05K2201/045—Hierarchy auxiliary PCB, i.e. more than two levels of hierarchy for daughter PCBs are important

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/04—Assemblies of printed circuits

- H05K2201/049—PCB for one component, e.g. for mounting onto mother PCB

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09009—Substrate related

- H05K2201/09036—Recesses or grooves in insulating substrate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09954—More mounting possibilities, e.g. on same place of PCB, or by using different sets of edge pads

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10431—Details of mounted components

- H05K2201/10507—Involving several components

- H05K2201/10515—Stacked components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10621—Components characterised by their electrical contacts

- H05K2201/10734—Ball grid array [BGA]; Bump grid array

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/15—Position of the PCB during processing

- H05K2203/1572—Processing both sides of a PCB by the same process; Providing a similar arrangement of components on both sides; Making interlayer connections from two sides

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/341—Surface mounted components

- H05K3/3431—Leadless components

- H05K3/3436—Leadless components having an array of bottom contacts, e.g. pad grid array or ball grid array components

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Testing Of Individual Semiconductor Devices (AREA)

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

- Structures For Mounting Electric Components On Printed Circuit Boards (AREA)

- Measuring Leads Or Probes (AREA)

- Wire Bonding (AREA)

- Combinations Of Printed Boards (AREA)

- Tests Of Electronic Circuits (AREA)

Abstract

本发明揭示了一种用于以三维阵列在电路板上排列半导体芯片的装置和方法。本发明揭示了一种独特的芯片载体,在该载体上任何IC芯片可定位成在电路板上一个芯片在另一个芯片之上。另外,载体可用于试验载体上和载体下的IC芯片而不必将载体和芯片从系统中拆下,即使它们是BGA或CSP型的也是如此。载体包括暴露的试验点以进行在位试验。

Description

本申请根据美国专利法119(e)要求对于申请于2002年2月26日,题为“A Modular Integrated Circuit Chip Carrier”的美国临时申请系列号60/360473的优先权。

本专利文件揭示的内容的一部分包含受到版权保护的材料。本版权的所有人对于任何人复制出现在专利和商标局的专利文档或记录中的本专利公开的内容不表示异议,否则在任何情况下均保留全部版权。

发明领域

本发明涉及一种集成电路的载体。更具体地说,涉及一种使装配在印刷电路板上的集成电路芯片的密度得以提高,除此之外还适合于将广泛的各种标准的IC芯片封装结构以三维阵列连接到印刷电路板的集成电路的载体,以及当载体和芯片被连接到更大系统的电路中时用于试验该载体和芯片的系统和方法。

发明背景

半导体芯片通常被连接到印刷电路板或相似的结构上,印刷电路板或相似结构转而再将这些芯片,包括印刷电路板上的其他芯片互连到该芯片将和其一起工作的计算机电路的其余部分中去。以前,这些芯片被以简单的二维阵列分散在印刷电路板的大平面上。近年来,计算机工业的趋势已经朝向印刷电路板上的芯片的密度更高的排列构型。之所以这样做的原因是对于更大的随机访问计算机存储器,对于更快的计算机,对于更紧凑的计算机的不断增加的要求,以及通过增加印刷电路板上电路的密度降低印刷电路板的成本的推动。上世纪80年代中期,工业上从将计算机芯片通过印刷电路板上的孔附着到印刷电路板的技术发展到应用各种表面安装的技术。随着表面安装技术的出现,常规的印刷电路板上的通孔被安装在印刷电路板表面的导电安装垫取代。芯片通过诸如DIP等各种构型的导线连接到印刷电路板上。这样就出现了多层电路板以及在该电路板的各个层次之间走向的互连导线的复杂的网络。反过来这又促进了印刷电路板上芯片密度的提高,不仅减小了电路板的尺寸,而且通过减少信号在电路板上的芯片之间必须穿越的距离而提高了计算机的速度。

向表面安装技术的转变导致了在印刷电路板上以各种构型定位芯片以提高印刷电路板上芯片的密度从而减小芯片之间的距离以提高整个系统的运行速度的实践。将芯片互相分层或定位以形成三维阵列是用于在印刷电路上提高芯片密度的一种方法。将芯片互相定位或分层以形成三维阵列的实践尤其适用于向其电路提供冗余度的存储器芯片。在印刷电路板上堆叠半导体芯片的明显优点的一个实例在美国专利6313998号中叙述,该专利所有人和本申请属于同一个实体,其内容通过引用而结合在本文中。美国专利6313998揭示了一种带有导线的载体以及一种将一个芯片定位在另一个芯片上面的方法。

然而,计算机工业的技术在不断发展,现在工业上的总的趋势是,对于大多数半导体芯片的封装发展到应用球栅阵列(BGA)型的连接。典型的BGA配置由一组芯片封装底部上的BGA衬垫和一个印刷电路板上的相应的镜像阵列组成。然后芯片封装通过焊料球连接到电路板上。BGA型的连接提供了若干优点,其中之一是消除了将芯片封装连接到电路板的导线。BGA连接的应用减少了信号必须穿越的距离,也消除了由导线产生的阻抗和其他干扰。本技术领域的熟练人员都很好地连接其他的优点。

但是BGA型的连接也有其本身的问题,其中之一是当BGA连接的器件被连接到电路板的电路或其他器件上时不能对其进行试验。另一方面,通过导线连接的IC封装很容易进行试验,同时该器件仍连接到电路中,因为长导线很方便地有附接在其上的试验探头。另一方面,通过连接本性连接的BGA连接的器件不可能在其连接到电路上的同时进行直接的甚至是间接的试验。通过连接本性连接的BGA芯片封装由不能看见的不暴露的盲垫连接。BGA型连接的另一个问题是需要开发堆叠芯片的新技术,因为如果不是大多数也有许多用于堆叠芯片的技术是用于利用导线的集成电路封装,不能方便地适合于BGA型的连接。另外,大多数现有的用于将芯片形成三维阵列的芯片堆叠器件和方法趋向于非常复杂。它们通常不能和标准的IC封装一起工作,即使其是导线型和或BGA型的并通常需要为了实施而对芯片封装本身进行修改。另外,为了将这些器件和标准的电路板装置和相似的工艺形成一体,如果不是大多数也有许多现有的堆叠方法需要特殊的制造步骤和/或机器。

工业上不断发展新的封装技术以减小尺寸和增强信号质量。各种芯片比例封装(CSP)就在这些当前的开发中。倒装片是这类封装的一种变型。就像BGA连接一样,倒装片或CSP封装依靠的是不暴露的盲垫。

这样,所需要的是能在电路板上堆叠半导体芯片封装的技术和设备,这些电路板能和由BGA,CSP或其他类型的技术连接的封装一起使用。这样的技术和相关的器件必须能接受和连接电路板上的堆叠的三维阵列,不需对将和该设备和方法一起使用的标准的半导体芯片封装进行修改。另外,这样的技术和设备应能允许进行各种芯片和相关元件的试验,不需将需进行试验的芯片或元件从其连接到整个系统的电路中移走。

概述

本发明的一个目的是提供一种在电路板上堆叠半导体芯片的方法和设备。本发明的另一个目的是提供一种能和电路板装配工作形成一体,不用修改现存技术的方法和设备。本发明的还有一个目的是提供一种能用于不修改现存的半导体芯片封装堆叠半导体芯片的方法和设备。

本发明所有的目的都通过提供一种用于堆叠集成电路芯片的载体而实现,在载体具有:a)一个带有顶表面和底表面的平台;b)在该平台的第一侧的一个第一支柱和在该平台的第二侧的一个第二支柱,该支柱提供对平台的支撑并产生平台下表面下的一个空间;c)在其顶表面有一个BGA衬垫图形的平台,用于在该BGA衬垫图形的顶表面上接纳至少一个集成芯片,该图形的每个衬垫的底表面被连接到一个通路,该通路通过平台通到平台的下层,其中该通路连接到一个朝向第一或第二支柱延伸的导电通道;d)具有支柱通路的第一和第二支柱,该通路通过每个支柱从支柱的底部向上延伸到支柱的顶部,其中每个支柱通路连接到平台中的一个特定的导电通道,该特定的导电通道连接到一个从衬垫图形的衬垫的衬垫下降的特定的通路;和e)其中载体形成一个模块单元,该模块单元可在平台的顶表面上接受至少一个集成芯片并将芯片连接到该载体被附接到其上的印刷电路板,并在载体的底表面下的空间中提供用于将至少一个其他的集成电路芯片附接到载体被附接到其上的电路板的空间。

在本发明的载体的另一个方面中,在第一支柱中的向上延伸的通路向上延伸到平台的第一侧面的顶边缘,从而暴露在平台的顶表面上的向上延伸的通路的顶表面,在第二支柱中的向上延伸的通路向上延伸到平台的第二侧面的顶边缘,从而暴露在平台的顶表面上的向上延伸的通路的顶边缘。

在本发明的另一个变型中提供了一种将芯片倚靠的衬垫直接定位在下降通路上方的方法。做到这一点的方法是通过用一种非导电的或导电的填充材料填充到通路被制造以后留在通路中的中空部分中。这样通过回避使衬垫从通路偏置的要求而减小了衬垫必须的空间。

在本发明的另一个方面提供了一种能和BGA型连接器,CSP型连接器或其他相似连接器配置一起使用的系统。另外,当元件还连接到本发明的载体以及连接到电路板时本发明还通过提供可得到的接触衬垫点而提供了一种试验该元件的方法,在一个实施例中,这些接触衬垫点包括对于试验探针的电气接地。

附图简述

通过结合附图的下文的叙述对本发明能有更好的理解。这些附图为:

图1是本发明的载体的优选实施例的透视图;

图2是本发明的连接到电路板并堆叠两个IC芯片的载体的侧视图;

图3是本发明的载体以及该载体和其一起连接到电路板的元件的分解视图;

图4是取自图1描绘的载体的I-I线的截面图;

图5A是先有技术的将BGA衬垫连接到电路板的方法的示意图;

图5B是图5A的BGA衬垫和连接的剖面图;

图5C是本发明的优选实施例中使用的连接技术的剖面图;

图5D是本发明的优选实施例中使用的连接技术的剖面图;

图6是在本发明的载体的下走线层上的典型电路的示意图;

图7A-7D提供了构成本发明的载体的一个实例的各个层次的各种主要层次的实例;

图8A是本发明的载体的一种形式的主要层次的剖面示意图;

图8B是本发明的载体的显示构成该载体的层次的部分的剖面图;

图8C是本发明的载体的支柱的衬垫和通路的一部分的一个实施例的剖面图;

图9是本发明的附接到带有堆叠的BGA器件的电路板的载体的一种形式的部分剖面的透视图;

图10是本发明的带有BGA器件的双堆叠载体的分解视图;

图11是本发明的堆叠BGA器件的两个载体的端视图;

图12是本发明的堆叠BGA器件的两个载体的侧视图;

图13是本发明的载体的另一种形式的视图,该形式中IC芯片被附着到载体的两个侧面;

图14提供了将衬垫连接在图13描绘的形式的载体上的一种方法的示意图;

图15是取自图14的II-II线的剖面图;

图16是本发明的载体已经附接到其上以及IC芯片被置于载体的顶部之前的电路板的顶视图;

图17是图16的电路板在IC芯片已经附着到每个载体顶部时的视图;

图18是本发明可和其一起工作的另一种BGA阵列的示意图;

图19提供了图18描绘的载体的衬垫之间的销连接的表;

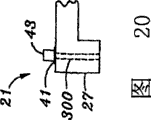

图20是本发明的载体的显示从去耦电容衬垫下降的通路的一角的视图;

图21是本发明的带有另一种去耦电容衬垫位置的载体的透视图;

图21A是图21的载体的取自XX-XX线的剖面图;

图21B是本发明的显示另一种去耦电容连接方法的载体的一角的视图;

图22是本发明的载体的衬底层上的电气连接的示意图。

优选实施例的详细描述

本发明提供了一种芯片载体,该载体能在印刷电路板上以三维的阵列在一起堆叠或排列两个或多个芯片并将堆叠的芯片结合到电路板的电路中去。图1是本发明的芯片载体21的优选实施例的透视图。芯片载体21有顶平台23和两个侧支柱25和27。在平台23顶部上的BGA衬垫29A和29B的阵列被定位成接纳通过BGA衬垫阵列的方法连接的IC芯片。如下文将讨论和说明,衬垫29A和29B连接到下降到平台23的通路,然后由横向通到支柱25和27中的通路的导线连接。支柱25和27中的每个通路的顶部暴露的部分33可以在每个支柱25和27上的平台23的顶部边缘上看见。如下文将叙述和说明,支柱25和27中的每个通路通过支柱25和27以及焊料球37可附着其上的衬垫或暴露部分的端部下降。在其一个优选实施例中的载体21具有用于在平台23的顶部接纳去耦电容43的衬垫41。如下文将说明,去耦电容通过适当放置的通路和导线连接到电路中。另外,与IC芯片相邻的去耦电容的设置增强了工作性能。本发明就这样提供了适当的除去电容的去耦。

图2提供了本发明的连接到带有集成电路(IC)芯片51和52的电路板49载体21的侧视图。IC芯片51通过衬垫29A和29B(图1所示)的方法连接到载体21。IC芯片52通过相似的BGA衬垫阵列组连接到电路板49。去耦电容43位于载体21上其平台23的角上。如上所述,IC芯片51的BGA阵列的球61附着到其上的平台23上衬垫29A和29B的阵列具有在其下面下降到平台23中的通路,通路连接到导线,导线连接到支柱25和27中的通路。焊料球37将支柱25和27中的通路的底部连接到电路板49并提供到电路板49的最后电气连接。IC芯片52通过电路板49上未显示的典型的BGA衬垫阵列中的焊料球63连接到电路板49。

在图1和2中描绘的本发明的实施例中,去耦电容43的衬垫有其自己的在焊料球37中终止的通过每个支柱25和27下降的导电通路。去耦电容用于阻抗控制,辅助控制返回电流和储存电荷。

图3提供了电路板49,IC芯片52,载体21和IC芯片51的分解图。载体21通过BGA衬垫阵列65A和65B的方法连接到电路板49。电路板49有一系列通过应用和载体21相同或相似的载体以三维阵列排列的IC芯片组。电路板49为典型的印刷电路板,具有形成层压结构的金属化的和预浸料坯薄片的各个层次,其上带有未显示的导线,导线连接各种器件,在该情况中,这些器件是IC芯片52,载体21以及IC芯片51。电路板49沿其底边缘有连接器69,当电路板40被插入计算机的适当的插座中时,连接器将电路板49内的内部导线连接到系统的其余部分。电路板49是可保持IC存储器芯片或相似芯片的典型的电路板。图3仅用于提供在其中本发明能被利用的一种设置的实例。本发明能被用于印刷电路板的包括将其定位到计算机的主要母板上的广泛变化的其他构型。

优选实施例中的载体21被做成和印刷电路相同的形式,其具有层压层,通路和导线敷设在载体21的平台23的层次和支柱25和27中。图4提供了载体21的取自图1的I-I线的剖面图。平台21在顶部有衬垫29A和29B以及通路73A,73B,73C和73D。通路73A,73B,73C和73D下降到导电通道75A,75B,75C和75D。衬垫75B的导电通道在通道75A的背后因此由75A隐藏。还有,导电通道75C部分由导电通道75D隐藏。很自然,所有的导电通道都互相电气隔离。虽然从该透视图中导电通道75A,75B,75C和75D显示出如下文用另一图解释的那样在一起走向,但这仅是透视图的问题。从每一个通路73A,73B,73C和73D的导电通道75A,75B,75C和75D的走向都通向支柱25和27中之一的通路。通过从通路73D走向支柱27中的通路77D的导电通道75D和从通路73A走向支柱25中的通路77A的导电通道75A能清楚地说明这一点。导电通道和通路是电气传导的通道。

在优选实施例中通路用铜芯制成,导电通道也用铜制成。这样,通路77D和77A为铜芯,通路73A,73B,73C和73D为铜芯。在优选实施例中导电通道75A,75B和75D都用铜制成。很自然,载体21的所有其他通路和导电通道都用铜制成如图4所示的相同的形式。但是也可用任何适当的导电材料。如图4所示以及可从图1和图3看到,支柱25和27的通路的顶端具有在支柱25和27的顶部的平台23的两个顶边缘上出现的暴露的端部。支柱25和27的通路不必暴露诸如通路77A的79A和通路77D的79D的顶端以提供载体的功能,实际上,作为一种替代的设计,这些顶端可以由平台23覆盖。但是,构造这些带有暴露顶端的通路给载体21不少此处简短提及或下文将详尽解释的独特的特征。支柱25和27的通路的暴露的顶端提供了暴露的接触点,当载体的内部电路,IC芯片51和52都被连接到印刷电路板时通过这些接触点可以对其进行试验。暴露的顶端也提供了散热的通道。另外,暴露的顶端在互相的顶部提供了放置一个或多个和载体21相似的载体以形成载体和IC芯片的多重堆叠的三维阵列。另外,将通路73A,73B,73C和73D从平台23上的BGA衬垫延伸到平台23的底部为载体添加了额外的散热能力。另一个选择是在安装和试验期间是支柱中的通路的顶部暴露,而在安装和试验完成以后将其覆盖。另外,事实是,在优选实施例中,载体被制成和电路板相似的分层形式,通路也可以是不通的或被隐埋的以及是相通的通路。

在本发明的优选实施例中,BGA衬垫29A和29B的通路73被直接置于平台23的顶部上BGA阵列的衬垫下。这是放置通路的一种独特的方法,因为如显示一个BGA衬垫81和通路83的顶端以及连接导电连接环节84的图5A所示将通路从衬垫偏置是一种通常的做法。将衬垫81从衬垫83偏置的一个原因是因为其有一个中空的中心核心86这样的事实。中空的中心核心86是下述事实的结果,因为铜82或其他导电材料是通过电镀工艺涂覆的,电镀工艺通常都留下中空的核心。这样,因为中空核心86的存在就不可能在通路83上面构造衬垫。图5B是取自图5A的V-V线的通路83的剖面图。图5B显示带有铜内衬83的通路85中的中空核心86。在一个标准的制造工艺中,通过电路板的一个或多个层次下降的通路由一个小的机械钻头,激光钻具或其他装置切割,可以达到相似的结果。一旦通路被钻通就用通常是铜的导电材料涂覆。但是,衬垫可以如图5A和5B所示从通路偏置,不背离本发明的精神。但是,这些技术如所指出的那样有其缺陷。

在优选实施例中本发明提供了一个固体核心的通路而不是中空的轴或核心86。一种形式如图5C所示。图5C显示了根据本发明的一个替代实施例的通路87和BGA衬垫89的构型。图5C中的通路88可以通过形成铜88或其他导电材料87的层次制造,载体的层次形成在其中以形成通路88的通道。应该注意上述将向下下降的通路直接放置在载体的顶部上的衬垫下减小了载体和相关电路所需的空间。本发明提供的另一种替代是在涂覆导电材料以后留在通路中的中空核心中填充非导电的或导电的材料。图5D显示了填充导电的或非导电的材料91以后的中空核心86,这样,随着用导电材料92和91填充中空核心86,通路90被填成实心的。这样,衬垫93可以被敷设到通路90的顶部。很自然,载体21中的通路以及支柱25和27中的通路可以用相同的形式制造。

作为载体的下走线层的示意图的图6提供了可怎样为根据本发明的优选实施例制作的载体构型电路的实例的示意图。载体21的BGA阵列的通路73由导电衬垫75连接到支柱中的特定通路77。作为参照,图4的剖面图取自图6所示的I-I线。如从图6以及其他图中可看到,优选实施例中支柱的通路77被排列成交错的阵列以沿载体21的边缘有优化的空间。图6中也可以看见去耦电容衬垫的连接件93。本发明的载体的一个独特的特征是在平台顶部上的衬垫的阵列图形可被容易地构型成能容纳当前制造的IC芯片封装的广泛的变型,几乎不用或完全不用改变载体的结构。载体21的内部电路可以构型成容纳IC芯片的广泛的变型并提供IC芯片到电路板的适当的连接。

如上所述,在优选实施例中,本发明的载体被制成和标准的印刷电路板相同的形式。在优选实施例中,载体可以有两个到四个或更多个层次。图7A,7B,7C和7D提供了可构成载体的顶部平台的各个层次的示意图。图7A描绘了包含导电通道75的底层。图7B描绘了内部接地层,图7C描绘了内部电源层以及图7D描绘了带有IC芯片将连接到其上的衬垫排列的顶层。图7B和7C是所描绘层次的负视图,图7A和7D为正视图。另外,在图7D的本发明的优选实施例中,通路的暴露端79和BGA阵列的衬垫73和载体的表面67的周围电气隔离。在优选实施例中,表面区域73是诸如铜的导电材料。在优选实施例中,一个包围每个衬垫73但和衬垫73电气隔离的小区域67提供相邻于每个衬垫73和通路79的顶部的接地区域用于试验等目的。在技术上众所周知,图7A,7B,7C和7D描绘的层次由将所有层次粘合在一起但将其电气隔离的预浸料坯层分离。

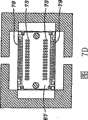

是可构成带有图7A到7D描绘的各个层次的载体的各个层次顺序的示意侧视图。在图8A中,走线层101是最底层。其次是预浸料坯层102,接地层103在其上。位于载体中心的核心层104和接地层103相邻。然后,电源层105后是预浸料坯层106,最后是顶走线层107。

用和载体将附接到其上的印刷电路板相同的材料制作载体21提供了很多明显的优点。这些优点有,载体21将和将要连接到其上的印刷电路板的电路中的其他元件相协调。在设计过程中将本发明的芯片载体21结合到电路板的电路中不会造成明显的问题,因为载体的电气特征将被很好地了解并且和电路中的其他元件相协调。

在本发明的优选实施例中,支柱110和111也用预浸料坯层压型的材料制成。支柱将建立在层压材料的各个层次中。也可以用诸如注射模制工艺的其他方法。

图8B提供了本发明的载体的支柱112和平台113的一部分的另一个剖面图。上面讨论的各个层次可从顶层114开始看到,顶层114有BGA衬垫的图形,在其下面是第一预浸料坯层115。工业上众所周知的预浸料坯层是在导电层之间提供绝缘以及提供形成电路板或在本情况下为形成载体必须的刚度和支撑的层压材料。在第一预浸料坯层115下是电源平面层116,在其下侧面有一个第二预浸料坯层117。在第二预浸料坯层117下是接地平面118,在其下面是第三预浸料坯层119。最后在平台113的底部是下走线层120。各个层次114,115,116,117,118,119和120就这样形成了优选实施例中的平台113。对于形成支柱112,这些层次再继续形成第四预浸料坯层121,另一个中间层122,第五预浸料坯层123并且结束于底层124,在底层124的底部是通路77的衬垫125。如上所述的通路77通过平台113的顶边缘下降,通过支柱112而终止于衬垫125,焊料球126被附着到衬垫125,用于如下文将叙述的将载体连接到电路板或另一个载体。在本发明的优选实施例中,支柱112中通路77的顶部79终止于衬垫127。

图8B的截面中仅显示了支柱112的一个通路77A,因为在优选实施例中沿载体的边缘的通路77A为交错的以节省空间通过平台边缘下降到支柱中的支柱通路可以边对边地对准并不背离本发明的原理。本说明书中如上述讨论在剖面图上显示并在其他图中描绘的通路73将IC芯片封装的BGA衬垫阵列的衬垫128连接到导线75,导线75再依次连接到通路77A。如上所述导电通道75由铜线制成。但是,也可用任何其他适当的导电材料。如在本说明书中的其他地方指出的,在优选实施例中,通路77和73为在载体的制造工艺期间形成的实心的铜核心。构成通路的导电核心终止在载体的每个支柱的顶部和底部并因此而提供了散热的通道。如本说明书的其他部分指出的,在其中形成通路的这些通道也可以通过在载体的层次中钻孔和在孔中镀铜或其他适当的导电材料而制作。

如上所述以多层次的形式制造载体提供了不少优点,其做到载体和电路板的阻抗匹配,可以使载体适应和任何标准的IC芯片一起工作而不必修改芯片等。另外,分步骤的层压工艺,深度走线或其他构造方法可以用于制作载体中的通路和导电通道。虽然所揭示的优选实施例以和多层次的电路板相同的形式制作,也可以有各种不需要载体有多层次的应用。该用于各种应用的载体可以通过注射模制工艺或相似的工艺制作。即使通过注射模制工艺制作的载体,其结构也还是可以修改的。

如上所述,半导体工业已经为集成电路芯片普遍采用了BGA型的连接器。用BGA型的连接器连接的系统性能上的改进以及其他的原因已经规定了从导线到BGA连接的转变。但是用导线将集成电路芯片连接到电路板或其他保持器的一个优点是这样的事实,如果芯片或相关器件安装以后发生问题,可以容易地通过导线对元件进行试验,无需从电路中取下元件。但对于由BGA连接的芯片,为了试验元件,必须将问题单元从印刷电路板或其他器件附着的电路上取下,因为当主体单元被连接到电路时是触及不到连接单元的球的。但是将芯片或其他单元从其发生问题的电路中取下可完全改变其工作特性,因此如果不可能确定初始问题的实际原因将使工作变得很困难。可以有不少方法接近芯片或器件发生问题的工作设定,但是进行该工作所需的时间和努力将使其变得很昂贵,而且效率不高,还会发生工艺上的错误。

本发明的一个明显的优点是提供了一种当IC芯片以及载体都还被连接到印刷电路板的电路上时就能对其进行试验的手段和方法。如上所述,这可以通过图9中未显示的支柱中的通路77的暴露的顶端来实现。图9提供了本发明的连接到电路板131的载体130的一角的透视图。通过BGA阵列连接到载体130的IC芯片132被连接到载体的顶部。另一个IC芯片被连接到载体130底下的电路板131上。支柱135中通路的暴露的顶端134的阵列的一部分被沿载体130的顶部边缘暴露。被给予通路的顶端79的暴露的位置,来自一个或多个试验器件的探测点136和137可以被置于抵靠住暴露的顶端并进行各种试验以确定电路和器件发生的任何问题的原因。这种对都还被连接在印刷电路板上的本发明的载体和连接到其上以及定位在其下的IC芯片或其他BGA器件进行试验的能力不仅使试验结果很精确,而且使试验效率高和容易操作。利用支柱的通路的暴露的顶端79进行的试验可以成为在自动制造工艺期间进行的标准质量控制试验的一部分。这可以用多种方法进行,包括使用带有多探点的抓斗式试验设备,这些探点将根据需要随时连接到支柱中的通路的顶部的暴露的阵列134中。

参考图8C和9,向上延伸的通路的暴露的顶端79和平台顶部的周围区域67电气隔离。通路和BGA阵列69的衬垫也通过材料80和平台23的顶部的周围区域67电气隔离。在优选实施例中,许多顶部区域67覆盖铜层。该铜层被用作散热片。顶绝缘层68覆盖层67的一部分。这也为试验单元71提供了方便的接地接触点。例如图9和图8C中的探针136或137之一可以被置于抵靠住一个通路的顶端79,另一个可以被置于抵靠区域67形成接地。被试验的在本发明的载体上的电路以及相关IC芯片具有高速和高复杂性,非常精确的试验设备也需要进行试验。相邻于试验将在其上进行的接触点设置接地将使试验很方便,因为试验设备的探点136和137经常在试验探针71中互相相邻地放置,如图8C所示。

本发明的载体的结构为用于电路试验的相邻接地提供了一个附加的替代。支柱中暴露的通路的一个或多个顶端将最可能为一个接地连接。这样,在进行一次试验中,该暴露的通路可被用作接地试验,不必为试验点提供一个特殊的相邻的接地位置。

上文提及的相关于提供暴露的通路顶部134(图9)的另一个优点是在一个放大的三维阵列中堆叠多载体和IC芯片的能力。图10是芯片和载体怎样堆叠的分解图。在图10中,第一BGA器件139通过标准BGA阵列附着到电路板140上。依次载体141通过位于BGA器件139的任何一侧的BGA衬垫142的阵列连接到电路板。依次BGA器件145用BGA衬垫阵列147连接到载体141顶部。依次载体149通过载体141的支柱中的通路的暴露的顶端的阵列150的方法附着到载体141。最后,BGA器件153通过载体149顶部的BGA衬垫154的阵列的方法附着到载体149。虽然图10中只画出两个可堆叠的载体,多重载体可以和附着的BGA器件一起互相堆叠。图11提供了电路板167上形成放大的三维阵列的两个层叠的载体161和附着的BGA器件163的端视图。图12提供了堆叠的载体阵列和BGA器件的侧视图。图12中,在每个载体161下面的BGA器件由于每个载体161的支柱169的位置而不能看到。

本发明的载体201的另一种形式在图13中描绘。载体201被附着到印刷电路板205。IC芯片210以上述方式附着到载体201。但是,IC芯片211被附着到载体201的平台215的词表面213而不是附着到载体下面的电路板205。用沿载体201的底表面213定位的BGA衬垫阵列将IC芯片附着到载体201的底部。该阵列和上述阵列相同。可以进行任何数量的不同的电路连接依次将IC芯片通过载体201连接到电路中去。事实上,该数量非常多,难以描述。这是本发明的一个明显的优点,载体可以和适当的BGA衬垫阵列和电路一起构型以保持能适配到载体201的平台215的顶部或底部上的空间的实际上任何种类的IC芯片。

图14提供了可以被和存储器IC芯片一起使用的衬垫的一种潜在的电路排列的视图,该种排列给出了带有载体201(图13)的电路的冗余度。在图14中,实线轮廓的顶衬垫220位于载体的平台的顶部。在顶部的每个衬垫220由实线223连接到一个通路225。如上所述,通路通过平台下降到平台的底层,在该处每个通路连接到以轮廓线形式显示的线227。依次每条线227连接到在载体的底部以轮廓线形式显示的衬垫229。如图中可见,每个在顶部的衬垫220和在底部的衬垫229都连接到同一个通路。但是,在底部的衬垫从在顶部的衬垫偏置。这是因为这样的事实,此处用的实例是存储器芯片,该存储器芯片将具有相同的排列,当被置于载体的任何一侧时,可从在本实例中使用的存储器IC芯片连接在一起的相同的衬垫将互相偏置,其时每个芯片的底部互相面对。图15提供了图14显示的平台的取自II-II线的剖面图。如图中可见,顶部220A上的衬垫由线223A连接到通路225A。通路225A通过平台230下降。通路225A连接到线227A。线227A依次连接到衬垫229A。

图13描绘的载体形式的一个优点是,印刷电路板可以做成标准的构型,和图13描绘的载体201一起工作。这样,必须被连线以处理IC芯片的元件只有载体201。

图16提供了带有载体253的印刷电路板251的一个实例。在图16中,将位于载体253顶部的IC芯片还没有添加。这样可以看到,将用来附着IC芯片的BGA衬垫255被附着到每个载体253的顶部。还可以看到在通过平台和下面的支柱下降的通路的顶部的衬垫257。在图17中,IC芯片已经附着到载体253的顶部。BGA衬垫255不再被看到,因为现在芯片259将其覆盖。但是,在每个通过载体的平台和支柱下降的通路的顶部的衬垫257被很清楚地看到并能因上文和下文叙述的试验和其他目的而触及。

很自然,在每个载体上的BGA衬垫阵列255可以用任何数量的不同方法构型,从而如果一种IC芯片处在图16描绘的阵列或诸如图18描绘的矩阵型的阵列的任何其他构型中,就能接受该IC芯片可能有的任何类型的BGA衬垫阵列。因为载体能以广泛变化的不同的方法容易地进行连线,该载体能被设计成和任何标准的IC芯片封装一起工作而不需修改IC芯片的封装。本发明的载体确实是一种模块器件。实际上,载体提供了一种用于将IC芯片附着到电路板的标准的但是灵活的销对准方法。

还有,如上所述,本发明为BGA,CSP和很多其他类型的IC芯片封装提供了一种独特的三维装置。本发明还提供了适当的电容去耦。另外,本发明还提供探测或试验点,为信号采样提供阵列257(在一些图中为79),为局部装配提供试验点等。还有,本发明还提供了相邻于载体顶部的探测点的紧密靠近的接地点,不管IC芯片是否被置于载体的顶部,这些接地点都可以得到。

本发明的另外一个优点是其可以被应用在三维的单侧面的重流通制造工艺中。IC芯片的第一层可以被置于电路板上,然后载体被如图16所示地置于该芯片的上面,最后第二组IC芯片可如图17所示地置于载体的顶部。一旦这种构型完成,整个电路板以及被置于其顶部的零件仅必须经过一个单重流通工艺以完成制造。可以用诸如标准的拾取和插装机的标准的制造机械安装全部IC芯片以及载体。如上所述,在几个地方可以使用标准的未经修改的IC芯片封装,因为载体能被交错以接受任何标准的IC芯片,也可以包括带有导线的芯片,以及带有BGA衬垫,倒装片,CSP等的芯片。另外,载体可以被置于用于制造工艺的传送带上或以标准的JEDEC型的盘传送。

图18提供了在一个优选实施例中的载体301的顶部出现的衬垫的示意图。如图中所示,有一个用于连接IC芯片的衬垫303的矩阵。如图中所示,有一个八列五行的实心衬垫矩阵用于接纳IC芯片。如在技术上众所周知,所有的衬垫或其任何组合都可被用于连接适当的IC芯片。另外,如可在每一面看到,出现一个支柱衬垫305A和305B的阵列。如上文指出,这些衬垫以适当的图形连接到IC衬垫矩阵303。另外,在每一个角307有用于电容器或其他类型的适当器件的衬垫。如图中所示,每个销都有一个适当的标示,诸如Vdd,或DQ2,或NC等。例如,在图18所示的构型中,衬垫DQ0被连接到支柱通路衬垫310。如图所示,支柱衬垫被标示为传统形式的各种销。通过参考图19的表,衬垫303的矩阵和每个支柱上的衬垫之间的连接由销转换表指示。这仅是可能的衬垫连接的一个实例,该实例可以做成用于有更大变化的不同类型的芯片,带有能和载体301连接的各种不同的衬垫构型。

图20提供了去耦电容43怎样如上所述地电连接的示意图。电容器43位于两个分离的衬垫(图1)上,每个衬垫都连接到分离的通路,一个连接到接地,另一个连接到电源。在图20中,去耦电容43置于衬垫41上。衬垫41连接到通路300,通路300通过载体21的支柱27下降,在图20中可看到载体21的一角。通路300被连接到未显示的电路板上的适当的衬垫上。很自然,图1中描绘了去耦电容连接两个衬垫每个衬垫由分离的通路连接到电源或接地的连接点,从而成为电路的电子结构的一部分。

在另一种变型中的本发明如图21所示能用于将去耦电容303定位在载体301上的各种不同的位置上。去耦电容303到系统的电气连接可以用各种方法实现。图21A所示的一种变型,载体301的取自图20的X-X线的剖面图描绘了去耦电容303所在的衬垫305和306怎样由通路连接到如上所述构成载体301的结构的内部接地309和电源平面310。内部电源平面310连接到支柱中的至少一个通路311,内部电源平面309连接到支柱中的一个通路312。很自然,所有连接到内部电源平面310的连接点和所有连接到内部电源平面309的连接点电气隔离。在图21B描绘的另一种变型中,从去耦电容303所在的衬垫305和306下降的通路314和315连接到导线317和318,导线317和318再依次直接连接到提供电源和接地连接点的支柱325中的通路320和321。

图22提供了本发明的载体的布线衬底层401上的布线布局的一种形式。在图22的布线布局中可以看到从IC芯片被连接到其上的平台的顶部的衬垫下降的通路403的一部分。另外,支柱中的通路405的各个部分沿载体的边缘出现。另外,导电通道407的走向处在通路部分403和通路部分405之间。任何计算机系统的重要的操作方面之一都是提供适当的信号运动的时序。可能在一毫秒甚至在一微微秒内消失的信号可以经常产生由计算机当前运行的速度给出的运行问题。另外,趋势是提高运行的时钟信号的次数和计算机的速度,这样,时序在将来将成为甚至更居决定性的地位。本发明的一个优点是其能将存储器或其他类型的芯片以三维的形式排列,这样的形式能减少连接线的长度。这在计算机技术中通常是决定性的并且明显有助于运行速度的提高。事实上,在计算机操作系统中的快速时钟循环期间,信号必须以协调的方式运动并在时钟循环期间到达特定的端点。如果信号必须在其上以协调的方式运动的导线对于每个信号都一样长,就能得到明显减少从协调信号产生的问题的作用。本发明的载体的另一个优点是如果几个信号必须在同时在相邻的导线上运动,通过交错通路位置匹配衬底上的导线长度,可以使导线有精确的相同的长度。如图22描绘的布线布局所示,一些在通路组403到通路组405之间走向的导线407在许多连接中有相等的长度。例如,图22中标有407的所有导线都有相同的长度。另外,在图22的布线布局的另一侧,在通路部分403和通路部分405之间走向的导线有相同的长度410。这样,如果被置于载体上的芯片同时需要多重信号的精确的平行传输,在载体上提供相同长度的传输线明显地减小了平行信号传输的协调性的可能的损失。

虽然对本发明参考其优选实施例进行了具体的显示和叙述,在技术上熟练的人员将理解的是,可以对本发明在形式和细节上作出各种变化而不背离本发明的精神和范围。

Claims (52)

1.一种用于在电路板上以三维阵列排列集成电路芯片的载体,所述载体包括:

a)一个带有顶表面和底表面的平台;

b)在所述平台的第一侧的第一支柱和在所述平台的第二侧的第二支柱,所述支柱为所述平台提供支撑,从而在所述平台的底表面下产生一个空间;

c)所述平台在其顶表面有一个连接衬垫的图形用于在连接衬垫的图形的顶表面上接纳至少一个集成电路芯片,衬垫的所述图形的每个衬垫的底侧连接到通过所述平台下降到所述平台的下层的通路,其中所述通路连接到朝向所述第一或第二支柱延伸的导电通道;

d)所述第一和第二支柱具有通过每个支柱从所述支柱的底部到所述支柱的顶部向上延伸的支柱通路,其中每个所述支柱通路连接到所述平台中的一个特定的导电通道,该特定的导电通道连接到一个从连接衬垫的图形的衬垫的衬垫下降的特定的通路;

e)其中所述第一支柱中的所述向上延伸的支柱通路延伸至所述平台的所述第一侧的顶边缘,从而暴露在所述平台的所述顶表面上的所述向上延伸的支柱通路的顶表面,在所述第二支柱中的所述向上延伸的支柱通路向上延伸到所述平台的所述第二侧的顶边缘,从而暴露在所述平台的所述顶表面上的所述向上延伸的支柱通路的顶边缘;

f)其中所述载体形成一个模块单元,该模块单元能在连接衬垫的所述图形上的所述平台的顶表面上接受至少一个集成电路芯片,并将该芯片连接到印刷电路板,其中所述载体被附接到该印刷电路板,并在所述载体的底表面下的空间提供一个用于至少将第二集成电路芯片附着到所述载体被附接到其上的电路板上的空间;和

g)其中所述通路是通过用导电材料镀覆孔形成。

2.如权利要求1所述的载体,其特征在于,所述向上延伸的通路具有一个导电材料的核心。

3.如权利要求1所述的载体,其特征在于,所述平台的所述连接衬垫的所述图形可以变化以形成多种不同的阵列图形,从而使得所述载体得以广泛地容纳各种具有不同阵列图形的集成电路芯片,其中,在所述通路和所述连接衬垫之间,以及在所述通路和所述支柱之间的所述导电通道可以被构型为以多种不同的构型将所述平台上的所述连接衬垫图形连接到电路板。

4.如权利要求1所述的载体,其特征在于,集成电路芯片可被导线连接到衬垫阵列。

5.如权利要求1所述的载体,其特征在于,用导电材料镀覆所述孔后留在所述孔中的中空的空间被用预先选择的材料填充从而去除所述中空的空间,并且允许将连接衬垫定位在所述通路的顶部,从而必须避免所述衬垫从所述通路偏置。

6.如权利要求5所述的载体,其特征在于,所述预先选择的材料是一种非导电材料。

7.如权利要求5所述的载体,其特征在于,所述预先选择的材料是一种导电材料。

8.如权利要求4所述的载体,其中:

a)在所述第一支柱中的所述向上延伸的通路的所述顶部暴露的顶端位于有第一预先确定的图形的所述平台的所述第一侧的顶部圆周边缘,在所述第二支柱中的所述向上延伸的通路的所述顶部暴露的顶端位于有第二预先确定的图形的所述平台的所述第二侧的顶部圆周边缘,以及

b)所述平台的所述顶表面的面积尺度为,所述平台的所述顶表面能在所述顶表面容纳由连接衬垫的图形连接的至少一个集成电路芯片,同时留下未经覆盖且能触及的所述向上延伸的通路的顶部暴露的顶端的所述第一预先确定的图形和所述向上延伸的通路的顶部暴露的顶端的所述第二预先确定的图形。

9.如权利要求1所述的载体,其特征在于,所述第一和第二支柱是多个支撑所述平台的支柱。

10.如权利要求1所述的载体,其特征在于,所述衬垫在所述通路的正上方。

11.如权利要求1所述的载体,其特征在于,所述衬垫偏离所述通路。

12.如权利要求1所述的载体,其特征在于,所使用的连接衬垫从BGA衬垫或Chip规模衬垫的集合中选择。

13.如权利要求1所述的载体,其特征在于,所述第二集成电路芯片位于所述平台的所述表面的底面上,且通过在所述第一和第二支柱和所述平台内的通孔和导线连接至电路板。

14.如权利要求1所述的载体,其特征在于,进一步包括用于将至少一个去耦电容电气连接到所述载体的衬垫。

15.如权利要求14所述的载体,其特征在于,其中用于所述至少一个去耦电容的所述衬垫连接到所述载体中的电源层或接地层,从而将所述至少一个去耦电容连接到电路中。

16.如权利要求14所述的载体,其特征在于,用于所述至少一个去耦电容的所述衬垫连接到支柱中的通路,当所述载体被附接到电路板时,所述通路连接到所述电路板上的电源和接地连接点,从而将所述至少一个去耦电容连接到电路中。

17.如权利要求16所述的载体,其特征在于,所述衬垫位于所述支柱的顶部。

18.如权利要求1所述的载体,其特征在于,其中所述载体被制造成为相似于标准电路板的形式的多层板。

19.如权利要求1所述的载体,其特征在于,所述载体由注射模制工艺制造。

20.如权利要求1所述的载体,其特征在于,所述通路由从台阶层压法或深度布线法的集合中选择的工艺制造。

21.如权利要求1所述的载体,其特征在于,当所述载体附接到电路板时,所述第二集成电路芯片直接连接到在所述载体的所述平台的所述底面下的电路。

22.一种用于在电路板上以三维阵列排列集成电路芯片的载体,所述载体包括:

a)一个带有顶表面和底表面的平台;

b)在所述平台的第一侧的第一支柱和在所述平台的第二侧的第二支柱,所述支柱为所述平台提供支撑,从而在所述平台的底表面下产生一个空间;

c)所述平台在其顶表面有一个连接衬垫的图形用于在连接衬垫的图形的顶表面上接纳至少一个集成电路芯片,衬垫的所述图形的每个衬垫的底侧连接到通过所述平台下降到所述平台的下层的通路,其中所述通路连接到朝向所述第一或第二支柱延伸的导电通道;

d)所述第一和第二支柱具有通过每个支柱从所述支柱的底部到所述支柱的顶部向上延伸的支柱通路,其中每个所述支柱通路连接到所述平台中的一个特定的导电通道,该特定的导电通道连接到一个从连接衬垫的图形的衬垫的衬垫下降的特定的通路;

e)其中所述载体形成一个模块单元,该模块单元能在连接衬垫的所述图形上的所述平台的顶表面上接受至少一个集成电路芯片,并将该芯片连接到印刷电路板,其中所述载体被附接到该印刷电路板,并在所述载体的底表面下的空间提供一个用于至少将第二集成电路芯片附接到所述载体被附接到其上的电路板上的空间;

f)其中所述第一支柱中的所述向上延伸的支柱通路延伸至所述平台的所述第一侧的顶边缘,从而暴露在所述平台的所述顶表面上的所述向上延伸的通路的顶表面,在所述第二支柱中的所述向上延伸的支柱通路向上延伸到所述平台的所述第二侧的顶边缘,从而暴露在所述平台的所述顶表面上的所述向上延伸的通路的顶边缘;以及

g)其中所述支柱通路是通过用导电材料镀覆孔形成。

23.如权利要求22所述的载体,其特征在于,所述向上延伸的通路适于提供热耗散。

24.如权利要求22所述的载体,其特征在于:

a)在所述第一支柱中的所述向上延伸的通路的所述顶部暴露的顶端位于有第一预先确定的图形的所述平台的所述第一侧的顶部圆周边缘,在所述第二支柱中的所述向上延伸的通路的所述顶部暴露的顶端位于有第二预先确定的图形的所述平台的所述第二侧的顶部圆周边缘,

b)所述平台的所述顶表面的面积尺度为,所述平台的所述顶表面能在所述顶表面容纳由连接衬垫的图形连接的至少一个集成电路芯片,同时留下未经覆盖且能触及的所述向上延伸的通路的顶部暴露的顶端的所述第一预先确定的图形和所述向上延伸的通路的顶部暴露的顶端的所述第二预先确定的图形;

c)其中所述第一支柱的所述通路的所述底部暴露的底端有为所述第一预先确定的图形的镜面图象的预先确定的图形,所述第二支柱的所述通路的所述底部暴露的底端有为所述第二预先确定的图形的镜面图象的预先确定的图形;和

d)其中和所述第一载体在所述第一和第二预先确定的图形和第一和第二预先确定的图形的所述第一和第二镜面图象的尺度和排列中完全一致的第二载体可以被堆叠在所述第一载体上,所述第一载体的所述通路的所述顶部暴露的顶端和所述第二载体的所述底部暴露的底端电气接触。

25.如权利要求24所述的载体,其特征在于,至少一个集成电路芯片可被连接到所述电路板上所述第一载体的底表面下的空间中,至少一个集成电路芯片可被连接到所述第一载体上的所述平台的所述顶表面上,至少一个集成电路芯片可被连接到所述第二载体的所述平台的所述顶表面上,以及所有所述集成电路芯片可被电气连接到所述电路板的电路中。

26.如权利要求24所述的载体,其特征在于,多个相同的载体可被一个在另一个上地放置以形成互相电气连接的载体的三维阵列。

27.如权利要求25所述的载体,其特征在于,在两个载体的所述平台上连接衬垫的所述图形可以变化以使所述载体以不同的阵列图形容纳广泛的各种集成电路芯片,其中在所述连接衬垫的所述衬垫的所述通路和所述支柱的所述通路之间的所述导电通道可以被构型成以多种不同的构型将所述平台上的连接衬垫的所述图形连接到电路板。

28.如权利要求26所述的载体,其特征在于,所述多个载体的所述平台上的连接衬垫阵列的所述图形可以变化以使所述载体容纳广泛的各种集成电路芯片衬垫阵列图形,其中在所述连接衬垫阵列的所述衬垫的所述通路和所述支柱的所述通路之间的所述导电通道可以被构型成以多种不同的构型将所述平台上的所述衬垫连接到在所述第一和第二支柱中的所述通路。

29.如权利要求24所述的载体,其特征在于,在所述第二载体的所述支柱中所述向上延伸的通路的所述暴露的顶端在所述第一和第二载体以及任何附着的集成电路芯片被连接到电路板时提供用于试验所述载体和所述集成电路芯片的接触点。

30.如权利要求25所述的载体,其特征在于,在所述第二载体的所述支柱中所述向上延伸的通路的所述暴露的顶端在所述第一和第二载体以及任何附着的集成电路芯片被连接到电路时提供用于试验所述载体和所述集成电路芯片的接触点。

31.如权利要求26所述的载体,其特征在于,在最顶部载体的所述支柱中所述向上延伸的通路的所述暴露的顶端在所述多个堆叠的载体以及任何附着的集成电路芯片被连接到电路时提供用于试验所述载体和所述集成电路芯片的接触点。

32.如权利要求22所述的载体,其特征在于,所述衬垫位于所述通路的正上方。

33.如权利要求22所述的载体,其特征在于,所述衬垫偏离所述通路。

34.如权利要求22所述的载体,其特征在于,在所述支柱中的通路的所述顶部暴露的顶端当该载体被连接到带有至少一个连接到所述载体的集成电路芯片的电路板时提供对所述载体进行单分析的分析点。

35.如权利要求22所述的载体,其特征在于,在所述支柱中的所述通路的所述顶部暴露的顶端被用于试验或信号分析,其中至少一个接地点相邻于所述通路的所述顶部暴露的顶端以便利信号的分析或试验。

36.如权利要求35所述的载体,其特征在于,所述至少一个接地点从相邻于所述支柱中的所述通路的所述顶部暴露的顶端的特定接地区域的集合中选择,或至少一个所述通路的所述顶部暴露的顶端为接地点。

37.如权利要求35所述的载体,其特征在于,其中所述信号分析或试验通过探针点进行。

38.如权利要求22所述的载体,其特征在于,当所述载体被附接到电路板时,所述支柱通路的暴露的顶端提供测试点以测试所述载体连接。

39.如权利要求22所述的载体,其特征在于,其中用导电材料镀覆所述孔后留在所述孔中的中空的空间被填充预先选择的材料从而去除所述中空的空间,将连接衬垫定位在所述通路的顶部并且必须避免所述衬垫从所述通路偏置。

40.如权利要求39所述的载体,其特征在于,所述预先选择的材料是不导电材料。

41.如权利要求39所述的载体,其特征在于,所述预先选择的材料是导电材料。

42.如权利要求39所述的载体,其中:

a)在所述第一支柱中的所述向上延伸的通路的所述顶部暴露的顶端位于具有第一预先确定的图形的所述平台的所述第一侧的顶部圆周边缘,在所述第二支柱中的所述向上延伸的通路的所述顶部暴露的顶端位于具有第二预先确定的图形的所述平台的所述第二侧的顶部圆周边缘,以及

b)所述平台的所述顶表面的面积尺度为,所述平台的所述顶表面能在所述顶表面容纳由连接衬垫的图形连接的至少一个集成电路芯片,同时留下未经覆盖且能触及的所述向上延伸的通路的顶部暴露的顶端的所述第一预先确定的图形和所述向上延伸的通路的顶部暴露的顶端的所述第二预先确定的图形;

43.一种用于在电路板上以三维阵列排列集成电路芯片的载体,所述载体包括:

a)一个带有顶表面和底表面的平台;

b)在所述平台的第一侧的第一支柱和在所述平台的第二侧的第二支柱,所述支柱为所述平台提供支撑,从而在所述平台的底表面下产生一个空间;

c)所述平台在其顶表面有一个连接衬垫的图形用于在连接衬垫的图形的顶表面上接纳至少一个集成电路芯片,衬垫的所述图形的每个衬垫的底侧连接到通过所述平台下降到所述平台的下层的通路,其中所述通路连接到朝向所述第一或第二支柱延伸的导电通道;

d)所述第一和第二支柱具有通过每个支柱从所述支柱的底部到所述支柱的顶部向上延伸的支柱通路,其中每个所述支柱通路连接到所述平台中的一个特定的导电通道,该特定的导电通道连接到一个从连接衬垫的图形的衬垫的衬垫下降的特定的通路;

e)其中所述第一支柱中的所述向上延伸的支柱通路延伸至所述平台的所述第一侧的顶边缘,从而暴露在所述平台的所述顶表面上的所述向上延伸的支柱通路的顶表面,在所述第二支柱中的所述向上延伸的支柱通路向上延伸到所述平台的所述第二侧的顶边缘,从而暴露在所述平台的所述顶表面上的所述向上延伸的支柱通路的顶边缘;

f)其中所述载体形成一个模块单元,该模块单元能在连接衬垫的所述图形上的所述平台的顶表面上接受至少一个集成电路芯片,并将该芯片连接到印刷电路板,其中所述载体被附接到该印刷电路板,并在所述载体的底表面下的空间提供一个用于至少将第二集成电路芯片附着到所述载体被附接到其上的电路板上的空间;

g)进一步包括用于电气连接至少一个去耦电容的到所述载体的衬垫;

h)其中用于所述至少一个去耦电容的所述衬垫连接到支柱中的通路,当所述载体被附接到电路板时,所述通路连接到所述电路板上的电源和接地连接点,从而将所述至少一个去耦电容连接到电路中;以及

i)其中用于至少一个去耦电容的所述衬垫由第二通路连接到所述支柱中的所述通路,该第二通路连接到导电通道,该导电通道依次连接到所述支柱中的所述通路。

44.一种在电路板上以三维阵列排列集成电路芯片的方法,所述方法包括下列步骤:

a)提供一个用于接纳第一集成电路芯片的平台;

b)提供至少一个支撑支柱以支撑所述平台并从而形成一个载体;

c)当载体被连接到电路板时,通过该平台和支柱将所述芯片电气连接到电路板;

d)以在平台的底部下有一个空间的构型形成至少一个支柱和平台,这样,当载体被附接到电路板时在平台下有一个用于将第二集成电路芯片连接到电路板的空间;

e)在载体上提供当载体被附接到电路板和集成电路芯片被连接到平台的顶部时能被触及的试验触点,该步骤包括在至少一个支柱的顶部提供通路的暴露的顶端;

f)其中将集成电路芯片电气连接到平台载体被附在其上的板的步骤如下:提供从平台的顶部上的连接衬垫向下延伸到载体中的连接层的导电通路;将通路连接到连接层中的导电线;确定通向至少一个支柱的导电线的走向;在至少一个的将有预先选择的图形的导电线连接到其上的支柱中提供导电通路;使至少一个的支柱中的导电通路从该通路连接到导电线的地点下降到至少一个的支柱的底部;在用于将载体连接到电路板的连接衬垫处的至少一个的支柱的底部终止导电通路;

g)其中提供从平台下降的通路和在至少一个支柱中的通路的步骤包括:在平台或者支柱中提供孔;在孔中淀积导电材料;和

h)包括进一步把其它填充材料淀积到淀积导电材料到孔中的步骤完成后所留下的中空空间中去除。

45.如权利要求44所述的方法,其特征在于,所述淀积其它填充材料的步骤包括淀积不导电填充材料。

46.如权利要求44所述的方法,其特征在于,所述淀积其它填充材料的步骤包括淀积导电填充材料。

47.一种用于在电路板上以三维阵列排列集成电路芯片的载体,所述载体包括:

a)用于提供接纳第一集成电路芯片的平台的装置;

b)用于支撑所述平台从而形成一个载体的装置,所述载体带有在载体下的一个空间,从而当所述载体被附接到电路板时为将第二集成电路芯片连接到电路板提供空间;

c)在所述载体被连接到电路板时,通过所述支撑所述平台的装置将连接到所述载体的顶部的第一集成电路芯片电气连接到电路板的装置;

d)其中,当所述载体被连接到电路板时通过所述支撑所述平台的装置将连接到所述载体的顶部的第一集成电路芯片电气连接到电路板的装置包括:

i)从在平台的顶部上的多个连接衬垫向下延伸到所述载体中的连接水平的导电通路;

ii)在所述连接层中连接到从连接衬垫向下延伸的导电通路的导线;

iii)其中支承装置是至少一个支柱和连至所述至少一个支柱的导线;

iv)在至少一个的支柱中有预先选择的图形的导电线连接到其上的导电通路;

v)其中在至少一个的支柱中的导电通路从该通路连接到导电线的地点下降到至少一个的支柱的底部;并且终止在用于将载体连接到电路板的连接衬垫处的至少一个的支柱的底部;

e)其中平台和至少一个的支柱中的导电通路通过导电材料被淀积在其中的孔形成;

f)其中孔包括淀积到所留下的中空空间中的填充材料,导电材料被淀积到孔中,从而为被置于通路的所述顶部暴露的顶端上的衬垫提供支撑。

48.如权利要求47所述的载体,其特征在于,所述填充材料是非导电填充材料。

49.如权利要求47所述的载体,其特征在于,所述填充材料是导电填充材料。

50.如权利要求47所述的载体,其特征在于,位于载体上的,当载体被附接到电路板上以及第一集成电路芯片被连接到平台时能触及的试验接触点是通过在至少一个的支柱的顶部提供通路的暴露的顶端而形成。

51.如权利要求50所述的载体,其特征在于,所述至少一个支柱是两个支柱。

52.一种用于在电路板上以三维阵列排列集成电路芯片的载体,所述载体包括:

a)一个用于接纳第一集成电路芯片的平台;

b)至少一个用于支撑所述平台从而形成一个载体的支柱,所述载体带有在所述载体下的一个空间,从而当所述载体被附接到电路板时为将第二集成电路芯片连接到电路板提供空间;

c)当所述载体被连接到电路板时,从用于接纳和连接第一集成电路芯片的所述平台的顶部上的连接衬垫,通过所述平台和所述至少一个的支柱到在所述一个支柱的底部的连接点的导电通道;

d)进一步包括用于将至少一个去耦电容电气连接到所述载体的衬垫;

e)其中用于所述至少一个去耦电容的所述衬垫连接到支柱中的通路,当所述载体被附接到电路板时,所述通路连接到所述电路板上的电源和接地连接点,从而将所述至少一个去耦电容连接到电路中,所述支柱中的通路向上延伸至所述平台的顶边缘,从而在所述平台的顶表面上暴露出该向上延伸的通路的顶边缘;和

f)其中用于至少一个去耦电容的所述衬垫由第二通路连接到所述支柱中的所述通路,该第二通路连接到导电通道,该导电通道依次连接到所述支柱中的所述通路。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US36047302P | 2002-02-26 | 2002-02-26 | |

| US60/360,473 | 2002-02-26 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1650429A CN1650429A (zh) | 2005-08-03 |

| CN100481444C true CN100481444C (zh) | 2009-04-22 |

Family

ID=27766230

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB038093618A Expired - Fee Related CN100481444C (zh) | 2002-02-26 | 2003-02-21 | 模块集成电路芯片载体 |

Country Status (10)

| Country | Link |

|---|---|

| EP (1) | EP1481424B1 (zh) |

| JP (2) | JP2006505919A (zh) |

| KR (1) | KR100980356B1 (zh) |

| CN (1) | CN100481444C (zh) |

| AU (1) | AU2003216362A1 (zh) |

| ES (1) | ES2440770T3 (zh) |

| HK (1) | HK1071637A1 (zh) |

| MY (1) | MY135660A (zh) |

| TW (1) | TWI282157B (zh) |

| WO (1) | WO2003073506A2 (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106061232A (zh) * | 2016-06-27 | 2016-10-26 | 北京空间机电研究所 | 一种用于遥感相机多片ccd器件盲插的装置及盲插方法 |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN100378970C (zh) * | 2005-04-22 | 2008-04-02 | 北京中星微电子有限公司 | 多用负载板 |

| US10251273B2 (en) * | 2008-09-08 | 2019-04-02 | Intel Corporation | Mainboard assembly including a package overlying a die directly attached to the mainboard |

| US8299809B2 (en) | 2009-09-21 | 2012-10-30 | International Business Machines Corporation | In-line characterization of a device under test |

| US8941221B2 (en) * | 2011-09-30 | 2015-01-27 | Mediatek Inc. | Semiconductor package |

| CN102569247A (zh) * | 2012-01-17 | 2012-07-11 | 华为终端有限公司 | 集成模块、集成系统板和电子设备 |

| US20140307391A1 (en) * | 2013-04-13 | 2014-10-16 | Infineon Technologies Ag | Three dimensional packaging |

| TWI591352B (zh) | 2013-06-07 | 2017-07-11 | 金士頓數位股份有限公司 | 測試裝置 |

| CN104681510A (zh) * | 2013-12-03 | 2015-06-03 | 晟碟信息科技(上海)有限公司 | 用于嵌入半导体裸片的桥结构 |

| TWI719241B (zh) * | 2017-08-18 | 2021-02-21 | 景碩科技股份有限公司 | 可做電性測試的多層電路板及其製法 |

| CN108376674B (zh) * | 2018-05-04 | 2024-03-08 | 扬州扬杰电子科技股份有限公司 | 一种vdmos功率器件塑封防分层翘曲结构 |

| KR102151989B1 (ko) * | 2018-09-06 | 2020-09-04 | 주식회사 지로이아이 | Psr 적용 쓰루홀 타입 단면 인쇄회로기판 |

| KR102187538B1 (ko) * | 2018-09-17 | 2020-12-07 | 주식회사 지로이아이 | 쓰루홀 타입 단면형 인쇄회로기판 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5065227A (en) * | 1990-06-04 | 1991-11-12 | International Business Machines Corporation | Integrated circuit packaging using flexible substrate |

| US5579207A (en) * | 1994-10-20 | 1996-11-26 | Hughes Electronics | Three-dimensional integrated circuit stacking |

| KR100266693B1 (ko) * | 1998-05-30 | 2000-09-15 | 김영환 | 적층가능한 비지에이 반도체 칩 패키지 및 그 제조방법 |

| GB2364440B (en) | 1999-05-07 | 2004-05-26 | Seagate Technology Llc | Surface mount ic stacking method and device |

| AU2461801A (en) * | 1999-12-28 | 2001-07-09 | Intel Corporation | Interconnect structure and method of fabrication therefor |

| JP2001210954A (ja) * | 2000-01-24 | 2001-08-03 | Ibiden Co Ltd | 多層基板 |

| US6487078B2 (en) | 2000-03-13 | 2002-11-26 | Legacy Electronics, Inc. | Electronic module having a three dimensional array of carrier-mounted integrated circuit packages |

-

2003

- 2003-02-21 AU AU2003216362A patent/AU2003216362A1/en not_active Abandoned

- 2003-02-21 JP JP2003572090A patent/JP2006505919A/ja active Pending

- 2003-02-21 EP EP03742896.8A patent/EP1481424B1/en not_active Expired - Lifetime

- 2003-02-21 ES ES03742896.8T patent/ES2440770T3/es not_active Expired - Lifetime

- 2003-02-21 KR KR1020047013372A patent/KR100980356B1/ko not_active IP Right Cessation

- 2003-02-21 WO PCT/US2003/005359 patent/WO2003073506A2/en active Application Filing

- 2003-02-21 CN CNB038093618A patent/CN100481444C/zh not_active Expired - Fee Related

- 2003-02-24 MY MYPI20030627A patent/MY135660A/en unknown

- 2003-02-26 TW TW092104108A patent/TWI282157B/zh not_active IP Right Cessation

-

2005

- 2005-05-30 HK HK05104529.7A patent/HK1071637A1/xx not_active IP Right Cessation

-

2006

- 2006-02-21 JP JP2006044465A patent/JP2006186391A/ja active Pending

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106061232A (zh) * | 2016-06-27 | 2016-10-26 | 北京空间机电研究所 | 一种用于遥感相机多片ccd器件盲插的装置及盲插方法 |

| CN106061232B (zh) * | 2016-06-27 | 2019-03-26 | 北京空间机电研究所 | 一种用于遥感相机多片ccd器件盲插的装置及盲插方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1481424B1 (en) | 2013-09-25 |

| MY135660A (en) | 2008-06-30 |

| TW200402854A (en) | 2004-02-16 |

| HK1071637A1 (en) | 2005-07-22 |

| CN1650429A (zh) | 2005-08-03 |

| KR20050077730A (ko) | 2005-08-03 |

| TWI282157B (en) | 2007-06-01 |

| KR100980356B1 (ko) | 2010-09-06 |

| ES2440770T3 (es) | 2014-01-30 |

| WO2003073506A3 (en) | 2003-11-06 |

| EP1481424A2 (en) | 2004-12-01 |

| JP2006505919A (ja) | 2006-02-16 |

| AU2003216362A1 (en) | 2003-09-09 |

| WO2003073506A2 (en) | 2003-09-04 |

| JP2006186391A (ja) | 2006-07-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7796400B2 (en) | Modular integrated circuit chip carrier | |

| CN100481444C (zh) | 模块集成电路芯片载体 | |

| CN106409700B (zh) | 介电材凹穴内设有电性元件的可堆叠式线路板制作方法 | |

| CN104733332B (zh) | 具有堆叠式封装能力的半导体封装件及其制作方法 | |

| TW478118B (en) | High density design for organic chip carriers | |

| US4933045A (en) | Thin film multilayer laminate interconnection board assembly method | |

| US4237522A (en) | Chip package with high capacitance, stacked vlsi/power sheets extending through slots in substrate | |

| US4970106A (en) | Thin film multilayer laminate interconnection board | |

| GB1586523A (en) | Integrated circuit assemblies | |

| US8580581B2 (en) | Substrate for electronic device, stack for electronic device, electronice device, and method for manufacturing the same | |

| EP1753274A2 (en) | Alternating micro-vias and through-hole vias for a BGA interconnect grid in order to create improved PCB routing channels | |

| CN110197823A (zh) | 面板级芯片装置及其封装方法 | |

| CN100525578C (zh) | 用于提高电路板的定线密度的方法和这种电路板 | |

| CN103811362A (zh) | 层叠封装结构及其制作方法 | |

| US6354000B1 (en) | Method of creating an electrical interconnect device bearing an array of electrical contact pads | |

| CN109803494B (zh) | 电路板及其制造方法 | |

| US20090277677A1 (en) | Electronic Assemblies without Solder and Method for their Design, Prototyping, and Manufacture | |

| CN107167685A (zh) | 倒装焊接的电学测试方法及系统 | |

| CN103887272A (zh) | 电子模块以及其制造方法 | |

| CN108109974A (zh) | 具有电磁屏蔽及散热特性的半导体组件及制作方法 | |

| US6591490B1 (en) | Method of constructing a multilayer electric apparatus | |

| CN117457661A (zh) | 一种显示模块及显示面板 | |

| CN107958883A (zh) | 具有散热座的散热增益型面对面半导体组件及制作方法 | |

| JPS5987895A (ja) | 多層プリント基板 | |

| JPS6269588A (ja) | 配線基板およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20090422 Termination date: 20170221 |