CN100345254C - 用低能量等离子体增强化学气相沉积法形成高迁移率硅锗结构 - Google Patents

用低能量等离子体增强化学气相沉积法形成高迁移率硅锗结构 Download PDFInfo

- Publication number

- CN100345254C CN100345254C CNB028273095A CN02827309A CN100345254C CN 100345254 C CN100345254 C CN 100345254C CN B028273095 A CNB028273095 A CN B028273095A CN 02827309 A CN02827309 A CN 02827309A CN 100345254 C CN100345254 C CN 100345254C

- Authority

- CN

- China

- Prior art keywords

- substrate

- layer

- growth room

- growing system

- growth

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015572 biosynthetic process Effects 0.000 title claims description 3

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 title abstract 3

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical group [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 title description 4

- 238000000034 method Methods 0.000 claims abstract description 52

- 239000000758 substrate Substances 0.000 claims abstract description 43

- 239000007789 gas Substances 0.000 claims abstract description 35

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 13

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims abstract description 12

- 239000004065 semiconductor Substances 0.000 claims abstract description 12

- 239000010703 silicon Substances 0.000 claims abstract description 11

- 239000001257 hydrogen Substances 0.000 claims abstract description 7

- 229910052739 hydrogen Inorganic materials 0.000 claims abstract description 7

- 239000011248 coating agent Substances 0.000 claims description 19

- 238000000576 coating method Methods 0.000 claims description 19

- 238000004519 manufacturing process Methods 0.000 claims description 10

- 230000003746 surface roughness Effects 0.000 claims description 10

- 239000012535 impurity Substances 0.000 claims description 8

- 239000000126 substance Substances 0.000 claims description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 3

- 239000004094 surface-active agent Substances 0.000 claims description 3

- 238000000151 deposition Methods 0.000 claims 3

- 239000007792 gaseous phase Substances 0.000 claims 3

- 125000004435 hydrogen atom Chemical class [H]* 0.000 abstract description 4

- 229910006990 Si1-xGex Inorganic materials 0.000 abstract 2

- 229910007020 Si1−xGex Inorganic materials 0.000 abstract 2

- 239000002019 doping agent Substances 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 55

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 42

- 238000005229 chemical vapour deposition Methods 0.000 description 25

- 239000011247 coating layer Substances 0.000 description 14

- 238000001451 molecular beam epitaxy Methods 0.000 description 10

- 238000000038 ultrahigh vacuum chemical vapour deposition Methods 0.000 description 10

- 230000000694 effects Effects 0.000 description 6

- 229910052732 germanium Inorganic materials 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 4

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 3

- 230000006835 compression Effects 0.000 description 3

- 238000007906 compression Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 241000193935 Araneus diadematus Species 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- 238000005336 cracking Methods 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 238000010891 electric arc Methods 0.000 description 2

- 230000035515 penetration Effects 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229910008310 Si—Ge Inorganic materials 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 238000000429 assembly Methods 0.000 description 1

- 230000000712 assembly Effects 0.000 description 1

- 238000010923 batch production Methods 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000000407 epitaxy Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000001534 heteroepitaxy Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 238000006386 neutralization reaction Methods 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 239000002243 precursor Substances 0.000 description 1

- 238000001289 rapid thermal chemical vapour deposition Methods 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000008719 thickening Effects 0.000 description 1

- NFACJZMKEDPNKN-UHFFFAOYSA-N trichlorfon Chemical compound COP(=O)(OC)C(O)C(Cl)(Cl)Cl NFACJZMKEDPNKN-UHFFFAOYSA-N 0.000 description 1

- 230000005533 two-dimensional electron gas Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/778—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface

- H01L29/7782—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface with confinement of carriers by at least two heterojunctions, e.g. DHHEMT, quantum well HEMT, DHMODFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02373—Group 14 semiconducting materials

- H01L21/02381—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02439—Materials

- H01L21/02441—Group 14 semiconducting materials

- H01L21/0245—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02496—Layer structure

- H01L21/02502—Layer structure consisting of two layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02496—Layer structure

- H01L21/0251—Graded layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02532—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/0262—Reduction or decomposition of gaseous compounds, e.g. CVD

Abstract

半导体的制造方法的步骤包括:采用一种高密度低能量等离子体增强化学气相沉积(LEPECVD)方法:生长速度为2nm/秒以上,基片温度为400℃至850℃和在气体入口处的活性气体总流量为5sccm至200sccm,以分级Si1-xGex层与一非分级Si1-xGex层在一硅基片上形成一虚拟基片;采用一低密度低能量等离子体增强化学气相沉积(LEPECVD)方法:使氢(H2)注入生长室,基片温度保持在400℃与500℃之间和以脉冲方式使一掺杂气体注入生长室,以提供调制掺杂层,在一包含Ge沟与至少一调制掺杂层的虚拟基片上形成一激活区。

Description

技术领域

本发明涉及硅锗结构的形成,更具体地说,涉及一些出现急增电子空穴迁移率的异质结构。例如,采用以下的方法可以形成调制掺杂场效应晶体管结构(例如,MODFET结构)和调制掺杂量子阱结构(例如,MODQW结构)。

背景技术

工业目前正在采用一些新的材料与材料组合物,以改进诸如晶体管的半导体器件。这样可提高集成电路(ICs)的处理速度与性能。

一典型的例子是在硅上配置硅锗(SiGe)。图1所示为一众所周知的SiGe异质结构器件10的实例。该器件10包括一(001)定向的硅基片11。一分级的SiGe层12位于Si基片11上。层12是考虑到晶格常数由硅的晶格常数逐渐地改变成主要由SiGe层12中的Ge浓度所确定的晶格常数。所述例子中,一成分不变的缓冲层13在该分级SiGe层12上形成。该SiGe层12与缓冲层13作为在随后的工序中形成的其他层的虚拟基片。该虚拟基片上形成一组有源元件层14。所述器件10的左边的图15所述为Ge的浓度。所述SiGe层12中的Ge浓度(x)由x=0渐渐增加至x=xf。所述层12的厚度一般是几微米,以保证缺陷结集低。

现行有几种广泛采用的SiGe器件10的制造方法,例子如,分子束外延(MBE)与超高真空化学气相沉积(UHV-CVD)。采用所述方法制作富含Ge的SiGe结构与器件则很困难。已知的方法的另一缺点是生长率慢。为了确保缺陷结集在一可接受的水平,故而要求SiGe层12的厚度为某一最小值。这样,形成所述硅锗层则需要相当长的时间。因此,对于工业性大量生产是非常不利的。

有两种不同的UHV-CVD具方法。第一种称为热壁式UHV-CVD和第二种称为冷壁式UHV-CVD或快速热CVD(RTCVD)。

热壁式CVD非常适合批量处理并在低的基片温度(一般在450℃和550℃之间)下进行。采用热壁UHV-CVD可在SiGe缓冲层上形成应变Si沟。Ismail等人曾在题为“Si/SiGe调制掺杂异质结构中极高的电子迁移率”(Appl.Phys.Lett,Vol.66,p.1077,1995)中报导,极高电子迁移率大于105cm2/Vs。所述热壁式UHV-CVD具有以下一些缺点,例如:

-据B.S.Meyerson等人在题为“硅/锗低温外延的共同生长现象”(Appl.Phys.Lett.,Vol.53,p.2555,1988)中报导,纯Si在约550℃的基片温度下生长率(大约纳米/分钟)慢;

-由所谓交叉线因松弛引起的大表面的粗糙度。浓度梯度(分级率)越陡,所述交叉线的效应则越明显。高度上高低的差距通常约为30nm(纳米),即使在一具有较低的表面Ge浓渡(xf=0.3)的缓冲层的表面上。如M.Arafa等人在题为“高性能Si/SiGe场效应晶体管的器件与制造问题”(Mat.Sci.Soc.,Symp.Proc.Vol.533,p.83)中所述,表面粗糙度对MODFETs的品质具有不利的作用。

-如P.M.Mooney等人在题为“SiGe技术:异质外延和高速微电子学”(Annu.Rev.Mater.Sci.,Vol.30,pp.335,2000)中所述,热壁方法特别在高Ge浓度时难以控制。因此,所述热壁方法不适合高迁移率空穴传输。这样,采用热壁技术并不能获得具有纯Ge沟的高性能p-MODFETs。

冷壁CVD适合用作处理单晶片。所述处理通常在700℃以上进行。在E.A.Fitzgerald等人所写题为“在Si基片上生长具有低贯穿式位错密度的完全松弛的GexSix-1层”(Appl.Phys.Lett.,Vol.59,p.811,1991)的论文中,可找到有关分级SiGe缓冲层的第一项结果。当基片温度在800℃和900℃之间,表面粗糙度比用热壁方法制作的层表面粗糙度大。报告指出,当缓冲层的Ge浓度增加时,在Si0.7Ge0.3缓冲层上的一30纳米的RMS-粗糙度将趋向更大的表面粗糙度。详情请参阅S.B.Samavedan等人的文章,题为“松弛的Ge/Si-Ge(分级)/Si结构中的新型位错结构与表面形态效应”(J.Appl.Phys,Vol.81,p.3108,1997)。

当采用冷壁UHV-CVD制作(RMS粗糙度大于30nm)时,SiGe缓冲层非常粗糙,其中浓度成梯度,以致于在缓冲层的表面上获得100%Ge。如未经化学机械抛光(CMP)则不能在这些粗糙表面上形成异质结构器件。详情请参照E.A.Fitzgerald等人的文章,题为“采用渐进式SiGe层与化学机械抛光来控制Si上的Ge的贯穿式位错密度”(Appl.Phys.Lett,Vol.72,p.1718,1998)。

直至现在,还没有任何报导整个叠层采用冷壁UHV-CVD制作MODFET结构和高迁移率的空穴输送器件。

另一众所周知的处理技术是低压化学气相沉积(LPCVD)。正如A.C.Churchill等人的文章,题为“高温下生长的松弛的SiGe层上的Si/SiGe异体结构中的高迁移率二维电子气”(Semicond.Sci.Technol.,Vol.12,p.943,1998)中报导,LPCVD方法中的较高的处理温度也会导致大的表面粗糙度。所述情况也发生在分级率低于10%/μm。据报导,当缓冲层表面的Ge浓度为xf=0.24和基片温度为800℃时,RMS粗糙度可高达6nm。详情请参照D.J.Wallis等人的文章,题为“松弛的SiGe层中的嵌镶晶体倾斜度及其与位错结构、表面粗糙度和生长条件的关系”(Mat.Res.Soc.Symp.Proc.,533,p.77,1998)。

表面上的Ge浓度为100%(即xf=1)的分级缓冲层具有较大的粗糙度,即RMS为160nm。

正如冷壁UHV-CVD,LPCVD不适合制造一需要高空穴迁移率的结构。

如上所述,MBE是另一广泛采用制作半导体结构的方法。采用一MBE方法可制作一虚拟基片(图1的层12与层13),而不会有严重的难题出现。由于层的化学成分基本上与基片温度无关,故而通过选择适当的温度图和分级率可以优化虚拟基片层的松弛和表面粗糙度,正如J.-H.Li等人的文章,题为“组成上分级的Si/Si1-xGex缓冲层的应变松弛和表面形态学”(J.-Vac.Sci.Technol.,Vol.B16,p.1610,1998)和E.A.Fitzgerald等人的文章(APL,Vol.59,p.811,1991)中所述。

MBE最严重的缺点是蒸发坩锅的容量有限。这在使厚的SiGe缓冲层生长时特别不利,如T.Hackbarth等人的文章,题为“MBE生长加厚松弛的SiGe缓冲层的可供选择的方案”(Thin Solid Films,Vol.369,p.148,2000)中所述。因此,MBE不适用于SiGe器件的工业规模生产。

对于一虚拟基片上具有大量Ge的压缩应变沟的器件,其趋向三维生长。具体来说,纯Ge层除了在约300℃的低基片温度下生长之外,其呈现显明的表面粗糙度。然而,在目前尚不能接受这样低温下的器件的电气性质。

本发明的目的是提供一种经改进的SiGe结构的制作方法,例如,MODFET结构或MODQW结构。

本发明的另一目的是提供一种具有经改进空穴电导率的SiGe器件的制作方法。

本发明的再一目的是提供经改进的SiGe异质结构的器件。

本发明的又一目的是提供一种实施SiGe器件的制作方法的生长系统。

发明内容

本发明依赖于一种低能量等离子体增强化学气相沉积(LEPECVD)方法。

本发明提出一种半导体结构的制作方法,其步骤包括:

-采用高密度低能量等离子体增强化学气相沉积(LEPECVD)方法:生长速度为2nm/秒以上,基片温度在400℃与850℃之间和在气体入口有一总活性气体流量为5sccm~200sccm(标准厘米3/分),以分级Si1-xGex层和非分级Si1-xGex层在一硅基片上形成一虚拟基片。

此外,所述方法的步骤还包括:

-采用一低密度低能量等离子体增强化学气相沉积(LEPECVD)的方法:使氢气(H2)进入生长室,基片温度维持在400℃与500℃之间和以脉冲方式使一掺杂气体进入生长室,以提供调制掺杂层,在一包含一Ge沟和至少一调制掺杂层的虚拟基片上形成一激活区。

本发明提出一种半导体器件。该器件包括一硅基片、一分级Si1-xGex层、一具有恒定Ge含量的Si1-xGex缓冲层和一位于所述Si1-xGex缓冲层上的激活区。该激活区包含至少一调制掺杂层和一在4.2k具有70000与87000cm2/Vs空穴迁移率的Ge沟。

本发明提出一种生长系统。该系统包括一具有气体入口的生长室。该系统的设置可实施一低能量等离子体增强化学气相沉积(LEPECVD)方法,该方法包括至少二个处理步骤,其中:

-把第一处理步骤的系统参数调整到:基片温度为400℃~850℃,气体入口处总活性气体量为5sccm~200sccm,以使生长率为2nm/s以上;以及

-把第二处理步骤的系统参数调整到:基片温度维持在400℃~850℃,使氢气(H2)注入生长室和采用脉冲方式使掺杂气体注入生长室,以使至少一层调制掺杂。

本发明的优点在于可防止或甚至避免已知方法的障碍与缺点。所述器件可实现至今未知的空穴迁移率。所述生长率急剧增加,因此,使本发明的方法能够用于以工业规模制作半导体器件。另一些优点从以下详细的描述将更为明显。

附图说明

以下,将结合附图对本发明、本发明的进一步目的及优点作更详细叙述,其中:

图1所示为SiGe异质结构半导体器件的截面示意图;

图2所示为本发明的低能量等离子体增强化学气相沉积(LEPECVD)系统的截面示意图;

图3所示为本发明的Ge浓度随时间变化的示意图;

图4所示为本发明的不同试样的空穴迁移率随温度变化的示意图;

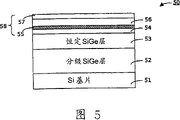

图5所示为本发明的SiGe异质结构半导体器件的截面示意图;

图6所示为本发明的另一SiGe异质结构半导体器件的截面示意图;

图7所示为本发明的Ge浓度随时间变化的示意图;和

图8所示为本发明的生长系统的方块图。

具体实施方式

本发明的原理是利用两种不同晶格参数的材料互相在其上生长时应变的层外延。例如,当锗(Ge)沉积在一较小晶格参数的基片上时,Ge的原子与其下的原子排成一行以使Ge压缩地应变。在应变的Ge中,例如,空穴遇到较少的阻力,就会流得较快。这效果可用于实现较快的器件而不用缩少单个器件的尺寸。

硅原子之间的空间比锗的晶格小。因此,一SiGe层的晶格常数比硅的晶格常数大。SiGe晶格常数随Ge的浓度升高而增大。

本发明是依靠低能等离子体增强化学气相沉积(LEPECVD)。图2所示为一典型的LEPECVD系统20。LEPECVD基于在一等离子体室22里的热灯丝21与生长室23的壁和/或一辅助阳极24之间的一低压DC电弧的放电。一SiGe层将在其上形成的基片25直接暴露在高强度但低能量的等离子体中。该基片的电压约-12V(伏特)诸如防止任何高能离子的损害。一偏压控制器31施加一适当的偏压。所述LEPECVD的特征在于等离子体电势是接近0V。必要的活性气体(例如,H2、SiH4、GeH4和PH3)通过一孔26和一气体入口30直接注入生长室23,同时,氩(Ar)放电气体则通过一孔27供入等离子体室22,该室与生长室23连接并由一细孔28分开。高强度的等离子体使前驱气体(例如,SiH4和GeH4等)非常有效地裂化,以致于Si与SiGe薄膜具有特别高的生长率。此外,生长率通过使等离子体限制在由围绕在生长室23的线圈产生的磁场中得以增强。采用一适当电压使AC电流通过所述灯丝21。约120A的电流使灯丝21加热至要求的温度。另外,用一约25V的DC电压电源32在灯丝21与地之间产生一电弧放电。该系统20还包括一涡轮分子泵29。

LEPECVD系统的进一步详情业已在诸如PCT专利申请WO 98/58099中描述。所述PCT专利申请的详情则用作一起参考。

LEPECVD系统的优点是可以获得特高的等离子体密度。本发明的虚拟基片是采用高密度的等离子体生长。所述活性气体的裂化对高密度等离子体非常有效,以致于增加生长动力。基片温度在400℃与850℃之间则可能有高达10nm/s的极高生长率。除了传统的CVD系统以外,LEPECVD系统中的生长率在特定的温度范围内差不多完全与基片的温度无关。

本发明业已证明,一LEPECVD系统中的SiGe生长率几乎与生长室中以一固定的总流量的反应气体的浓度无关。传统的CVD系统中,生长率与气体的浓度之间具有强烈的相关性。

本发明采用一种称为调制掺杂的方法,借此在如图2中所述的一LEPECVD系统中实现掺杂。所述调制掺杂的基本原理与其他生长方法差不多相同。掺杂层与空穴运载沟不直接接触,例如像Xie等人在Appl.Phys.Lett.(Vol.63,p.2263,1993)中所发表的论文中所述。图3中所述为一如何实现掺杂的典型的例子,其中Ge的浓度以时间(秒)的函数表示。该图本身表明了Ge沟在生长前、生长中和生长后的Ge流。10个维时约以每次脉冲接续时间约为70秒的10次乙硼烷脉冲41实现所述掺杂。在这些乙硼烷脉冲41中使Ge流减至零。图5所示为本发明相应的异质结构器件50。该器件包括一Si基片51,其上形成一虚拟SiGe基片。该虚拟基片包括一分级SiGe层52和一Ge浓度恒定的缓冲层53。请注意不同的层的厚度并不按照比例绘制。一激活区58位于该虚拟基片上。该激活区包括一包覆层54,所述层的Ge浓度比层53里的Ge浓度低。Ge沟55设置在包覆层54上。一调制掺杂包覆层56和一Si覆盖层57盖在沟55上。Ge浓度减少的包覆层54与56确保所述激活区58的应变补偿。

图4所示为空穴迁移率(cm2/Vs)随温度(绝对温度K)变化的曲线图,该图采用本发明的方法,在纯Ge沟中得出。采用本发明的方法就可在4.2K获得70000与87000cm2/Vs之间的迁移率。请特别留意87000cm2/Vs的迁移率。所述迁移率比文献中所报导的现行4.2K的55000cm2/Vs大得多(请参看Xie等人发表的上述论文)。所述两个案例的载体密度差不多相同,即LEPECVD的试样为6.18×1011cm-2和Xie等人的MBE试样为5.5×1011cm-2。请注意,后者的案例由于粗糙的表面,调制掺杂一定要在Ge沟以下的层中进行。在沟形成以前进行所述调制掺杂步骤所得的这种构形是不利的,因为掺杂物可能扩散或偏析到沟中。此外,由于掺杂层与栅极之间的大距离,这种构形不适合晶体管基的应用。

采用一LEPECVD系统实行本发明的步骤,就可以很高的生长率来生长具有很高空穴迁移率的合成器件。当SiGe层12(参看图1)在xf=70%和厚度为8μm下以10%/μm分级和层13的厚度约为1μm时,可达到约5-10nm/s的生长率。MBE系统的典型生长率为0.1至.3nm/s。在可比较的基片温度下,一UHV-CVD系统的生长率至少低一个数量级。

本发明采用400℃至850℃的低基片温度,最好为450℃至750℃。此外,当虚拟基片形成时,等离子体的密度比激活区外延生长时的密度高出大约十倍。

最后但并非最不重要的,激活区生长时,把H2注入生长室23中,其作为表面活性剂降低Si和Ge原子在表面扩散。这样使三维生长减少。还可以制作具有界限分明(精确的)界面。采用标准的MBE方式则无法实现所述界限分明的界面。

室温的迁移率对MODFET应用特别重要。采用本发明方法制作的器件的分析揭示,在293K下调制掺杂Ge的空穴迁移率最高达到约3000cm2/Vs。所述数值可与一采用MBE方法达到的1700cm2/Vs的空穴迁移率相比高。这样的迁移率是采用MBE业己获得的最好的。详情参见Madhavi等人的论文(J.Appl.Phys.,Vol.89,p.2497,2001)。

如图5中所示,图1中的器件10可通过在应变Ge沟的每一边各增加一包覆层得以改进。这个案例中,两层包覆层与所述沟一起形成有源器件层14。这些包覆层的Ge浓度可以是x=60%,例如,层13的Ge浓度为x=70%。每一层的厚度可以是约150nm。因为包覆层的Ge浓度比层13的Ge浓度低,所以使包覆层拉伸应变,而Ge沟呈现压缩应变。

根据本发明的另一实施例,在虚拟基片形成时故意改变基片温度。这是可能的,因为在温度范围400℃至850℃,LEPECVD系统的生长率几乎完全与基片温度无关。

图6和7所示为另一实施例。器件60与图5中所示的器件相似。该器件包括一Si基片61,其上形成一虚拟SiGe基片。该虚拟基片包括一分级SiGe层62和一具有恒定Ge浓度的缓冲层63(x=0.6)。请注意不同的层没有按照厚度比例绘制。一激活区68位于虚拟基片上。该区还包括一包覆层64,其Ge浓度(x=0.55)比层63的Ge浓度低。该包覆层64包括调制掺杂。Ge沟65位于所述调制掺杂包覆层64上。另一调制掺杂包覆层66和一Si覆盖层67盖着沟65。Ge浓度减少的两包覆层供给激活区68的应变补偿。图7所示为Ge浓度的分布。请注意每一调制掺杂层64与66只包括一掺杂峰值。

根据本发明,一种半导体结构的制作方法包括以下的步骤:

-采用一种高密度低能量等离子体增强化学气相沉积(LEPECVD)方法,其条件如下:

i.生长率2nm/s以上;

ii.基片温度在400℃与850℃之间;以及

iii.在生长室的气体入口处的活性气体总流量是在5sccm至200sccm;

在一硅基片上形成一虚拟基片,其包括一分级Si1-xGex层(0≤x≤xf)和一具有恒定Ge浓度(x=xf)的Si1-xGex层;

-采用一种低密度低能量等离子体增强化学气相沉积(LEPECVD)方法,通过以上步骤:

i.把作为表面活性剂的氢(H2)注入生长室;

ii.使基片温度维持在400℃与500℃之间;以及

iii.以脉冲方式把掺杂气体注入生长室,为调制掺杂层提供保证;

在所述包括一Ge沟与至少一调制掺杂层的虚拟基片上形成一激活区。

本发明的方法可作多种变换。

根据本发明,可以在一特定生长系统80实现使本发明的方法能够用作自动处理。图8所示为一例子。这样一种生长系统80包括一具有气体入口和其他组件的生长室23,其与图2所示相似。装置该生长系统80以便实施一种包括至少两个处理步骤的低能量等离子体增强化学气相沉积(LEPECVD)方法。在第一处理步骤中,调整该系统的参数至:基片温度为400℃至850℃和在气体入口处活性气总流量为5sccm至200sccm,以使一生长率在2nm/s以上。在第二处理步骤中,调整该系统的参数,使一基片温度维持在400℃至500℃。此外,在第二处理步骤时,把氢(H2)注入该生长室23和以脉冲方式把掺杂气体注入该生长室23,以使调制掺杂至少一层。

如图8示意所述,该生长系统80可包括一处理控制器81,其最好是一具有适合的软体模块82与83的计算机,以便控制根据本发明的系统参数。

用本发明的方法可以形成SiGe层,其RMS表面粗糙度为5nm或少于5nm。

本发明的概念十分适用于晶体管、传感器、光谱仪、量子计算机和其他器件/系统。

Claims (20)

1.一种在一具有气体入口(30)的生长室(23)中的半导体异质结构的制作方法,其包括以下步骤:

-采用一种高密度低能量等离子体增强化学气相沉积方法,其条件如下:

i.生长率为2nm/s以上;

ii.基片温度在400℃与850℃之间;以及

iii.在生长室的气体入口处的活性气体总流量为5sccm至200sccm之间;

在一硅基片(11;51;61)上形成一虚拟基片,其包括一分级Si1-xGex层(12;52;62)和一具有恒定Ge浓度的Si1-xGex层(13;53;63);

-采用一种低密度低能量等离子体增强化学气相沉积方法,通过以下步骤:

i.把作为表面活性剂的氢注入生长室(23);

ii.使基片温度维持在400℃与500℃之间;以及

iii.以脉冲方式把掺杂气体注入生长室(23),为调制掺杂层(56;64)提供保证;

在所述虚拟基片上形成一包括一Ge沟(55;65)与一调制掺杂层(56;64)的激活区(14;58;68)。

2.根据权利要求1所述的方法,其特征在于所述虚拟基片形成时,使基片温度在400℃与800℃之间的范围变化。

3.根据权利要求2所述的方法,其特征在于所述温度范围为450℃-750℃。

4.根据权利要求1或2或3所述的方法,其特征在于所述激活区(14;58;68)形成时,使基片温度保持在450℃。

5.根据权利要求1或2或3所述的方法,其特征在于用乙硼烷作为掺杂气体。

6.根据权利要求1或2或3所述的方法,其特征在于所述基片的电势为-12V和所述等离子体电势则接近0V。

7.根据权利要求1或2或3所述的方法,其特征在于SiH4和GeH4由气体入口(30)注入所述生长室(23)。

8.根据权利要求1或2或3所述的方法,其特征在于所述生长率为2nm/s至10nm/s之间。

9.根据权利要求1或2或3所述的方法,其特征在于所述高密度低能量等离子体的密度比低密度低能量等离子体的密度高十倍。

10.一种异质结构半导体器件,其包括一硅基片(11;51;61)、一分级Si1-xGex层(12;52;62)、一具有恒定Ge浓度的Si1-xGex缓冲层(13;53;63)、一位于所述Si1-xGex缓冲层(13;53;63)上的激活区(14;58;68)、所述激活区(14;58;68)包括至少一调制掺杂层(56;64)和一Ge沟(55;65),其在4.2K下的空穴迁移率为70000至87000cm2/Vs之间。

11.根据权利要求10所述的器件,其特征在于所述Si1-xGex缓冲层(13;53;63)和/或分级Si1-xGex层(12;52;62)的均方根表面粗糙度小于5nm。

12.一种生长系统(80),其包括一具有气体入口(30)的生长室(23),该生长系统(80)被设置为实施一包括至少两个处理步骤的低能量等离子体增强化学气相沉积方法,其中:

-在第一处理步骤中,调整该系统的参数至:基片温度为400℃至850℃之间和在气体入口处的活性气体的总流量为5sccm至200sccm之间,以使一生长率在2nm/s以上;

-在第二处理步骤中,调整该系统的参数至:基片温度保持在400℃至500℃之间,使氢注入该生长室(23)和以脉冲方式使一掺杂气体注入该生长室(23),以使调制掺杂至少一层。

13.根据权利要求12所述的生长系统,其特征在于所述生长系统包括一处理控制器(81),以便相应地控制系统参数。

14.根据权利要求13所述的生长系统,其特征在于所述处理控制器是一具有适当软体模块(82,83)的计算机。

15.根据权利要求13所述的生长系统,其特征在于使所述处理控制器(81)能够在第一处理步骤中,在给定的400℃与800℃的范围之间改变基片的温度。

16.根据权利要求15所述的生长系统,其特征在于所述给定范围为450℃-750℃之间。

17.根据权利要求13所述的生长系统,其特征在于使所述处理控制器(81)能够在第二处理步骤中维持该基片温度在450℃。

18.根据权利要求13所述的生长系统,其特征在于使所述处理控制器(81)能够控制将作为掺杂气体的乙硼烷注入生长室(23)。

19.根据权利要求13所述的生长系统,其特征在于使所述处理控制器(81)能够调整参数,以便使基片的电势保持-12V和等离子体电势接近0V。

20.根据权利要求13所述的生长系统,其特征在于使所述处理控制器(81)能够控制SiH4和GeH4注入生长室(23)。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP01127834A EP1315199A1 (en) | 2001-11-22 | 2001-11-22 | Formation of high-mobility silicon-germanium structures by low-energy plasma enhanced chemical vapor deposition |

| EP01127834.8 | 2001-11-22 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1615540A CN1615540A (zh) | 2005-05-11 |

| CN100345254C true CN100345254C (zh) | 2007-10-24 |

Family

ID=8179316

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028273095A Expired - Fee Related CN100345254C (zh) | 2001-11-22 | 2002-09-05 | 用低能量等离子体增强化学气相沉积法形成高迁移率硅锗结构 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7115895B2 (zh) |

| EP (1) | EP1315199A1 (zh) |

| JP (1) | JP2005510081A (zh) |

| CN (1) | CN100345254C (zh) |

| AU (1) | AU2002335310A1 (zh) |

| WO (1) | WO2003044839A2 (zh) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6855436B2 (en) * | 2003-05-30 | 2005-02-15 | International Business Machines Corporation | Formation of silicon-germanium-on-insulator (SGOI) by an integral high temperature SIMOX-Ge interdiffusion anneal |

| AU2003223991A1 (en) * | 2003-03-26 | 2004-10-18 | Eidgenoessische Technische Hochschule Zuerich | Formation of thin semiconductor layers by low-energy plasma enhanced chemical vapor deposition and semiconductor heterostructure devices |

| EP1513233B1 (en) * | 2003-09-05 | 2008-10-29 | Epispeed S.A. | InGaAs/GaAs lasers on Silicon produced by LEPECVD and MOCVD |

| EP1745165B1 (en) | 2004-04-30 | 2011-03-30 | Dichroic cell s.r.l. | Method for producing virtual ge substrates for iii/v-integration on si(001) |

| JP2007250903A (ja) * | 2006-03-16 | 2007-09-27 | Matsushita Electric Ind Co Ltd | ヘテロ接合バイポーラトランジスタおよびその製造方法 |

| EP2049939A1 (en) * | 2006-08-11 | 2009-04-22 | Paul Scherrer Institut | Light modulators comprising si-ge quantum well layers |

| JP5308336B2 (ja) | 2006-08-25 | 2013-10-09 | ブレイン アンド サイエンス エルエルシー | 被験者の特定認知感情状態を検出するシステム |

| FR2914783A1 (fr) * | 2007-04-03 | 2008-10-10 | St Microelectronics Sa | Procede de fabrication d'un dispositif a gradient de concentration et dispositif correspondant. |

| US20110017127A1 (en) * | 2007-08-17 | 2011-01-27 | Epispeed Sa | Apparatus and method for producing epitaxial layers |

| US8237126B2 (en) * | 2007-08-17 | 2012-08-07 | Csem Centre Suisse D'electronique Et De Mictrotechnique Sa | X-ray imaging device and method for the manufacturing thereof |

| EP2251897B1 (en) * | 2009-05-13 | 2016-01-06 | Siltronic AG | A method for producing a wafer comprising a silicon single crystal substrate having a front and a back side and a layer of SiGe deposited on the front side |

| TWI562195B (en) | 2010-04-27 | 2016-12-11 | Pilegrowth Tech S R L | Dislocation and stress management by mask-less processes using substrate patterning and methods for device fabrication |

| CN103165420B (zh) * | 2011-12-14 | 2015-11-18 | 中国科学院上海微系统与信息技术研究所 | 一种SiGe中嵌入超晶格制备应变Si的方法 |

| KR102142707B1 (ko) * | 2013-06-19 | 2020-08-07 | 엘지이노텍 주식회사 | 반도체 기판, 발광 소자 및 전자 소자 |

| CN105632927B (zh) * | 2014-10-30 | 2018-09-07 | 中芯国际集成电路制造(上海)有限公司 | Pmos晶体管的形成方法 |

| KR102465536B1 (ko) * | 2016-06-08 | 2022-11-14 | 삼성전자주식회사 | 반도체 장치의 제조 방법 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5241197A (en) * | 1989-01-25 | 1993-08-31 | Hitachi, Ltd. | Transistor provided with strained germanium layer |

| US5442205A (en) * | 1991-04-24 | 1995-08-15 | At&T Corp. | Semiconductor heterostructure devices with strained semiconductor layers |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0380077A3 (en) * | 1989-01-25 | 1990-09-12 | Hitachi, Ltd. | Transistor provided with strained germanium layer |

| ATE394794T1 (de) * | 1999-03-12 | 2008-05-15 | Ibm | Ge kanal-heterostruktur mit hoher geschwindigkeit für feldeffektanordnungen |

-

2001

- 2001-11-22 EP EP01127834A patent/EP1315199A1/en not_active Withdrawn

-

2002

- 2002-09-05 JP JP2003546385A patent/JP2005510081A/ja active Pending

- 2002-09-05 CN CNB028273095A patent/CN100345254C/zh not_active Expired - Fee Related

- 2002-09-05 WO PCT/EP2002/009922 patent/WO2003044839A2/en active Application Filing

- 2002-09-05 AU AU2002335310A patent/AU2002335310A1/en not_active Abandoned

- 2002-09-05 US US10/496,245 patent/US7115895B2/en not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5241197A (en) * | 1989-01-25 | 1993-08-31 | Hitachi, Ltd. | Transistor provided with strained germanium layer |

| US5442205A (en) * | 1991-04-24 | 1995-08-15 | At&T Corp. | Semiconductor heterostructure devices with strained semiconductor layers |

Non-Patent Citations (2)

| Title |

|---|

| A PLASMA PROCESS FOR ULTRAFAST DEPOSITION OF SIGE GRADEDBUFFER LAYERS C ROSENBLAD H ,VONKANEL M UMMER A DOMMANN,E MULLER,APPLIED PHYSICS LETTERS,Vol.76 No.4 2000 * |

| A plasma process for ultrafast deposition of SiGe gradedbuffer layers C.ROSENBLAD,H.VONKANEL,M.KUMMER,A.DOMMANN,E.MULLER,APPLIED PHYSICS LETTERS,Vol.76 No.4 2000 * |

Also Published As

| Publication number | Publication date |

|---|---|

| AU2002335310A8 (en) | 2003-06-10 |

| WO2003044839A2 (en) | 2003-05-30 |

| AU2002335310A1 (en) | 2003-06-10 |

| WO2003044839A3 (en) | 2003-10-30 |

| JP2005510081A (ja) | 2005-04-14 |

| EP1315199A1 (en) | 2003-05-28 |

| US7115895B2 (en) | 2006-10-03 |

| CN1615540A (zh) | 2005-05-11 |

| US20050116226A1 (en) | 2005-06-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100345254C (zh) | 用低能量等离子体增强化学气相沉积法形成高迁移率硅锗结构 | |

| CN1210763C (zh) | 半导体器件及其生产工艺 | |

| CN1226775C (zh) | 半导体衬底的制造方法和半导体器件的制造方法 | |

| CN1181561C (zh) | 半导体装置 | |

| TWI222106B (en) | Semiconductor substrate, field-effect transistor, and their production methods | |

| CN1263089C (zh) | 制造半导体基质的方法 | |

| CN1723545A (zh) | 用于高迁移率器件的SiGe应变弛豫缓冲层及其制造方法 | |

| CN1444253A (zh) | 生产松弛SiGe基质的方法 | |

| CN1770391A (zh) | 半导体结构及其制造方法 | |

| US20040092085A1 (en) | Semiconductor crystal film and method for preparation thereof | |

| CN1574226A (zh) | 形成绝缘体上硅锗衬底材料的方法、衬底材料及异质结构 | |

| CN1711625A (zh) | 通过离子注入和热退火获得的在Si或绝缘体上硅衬底上的弛豫SiGe层 | |

| US20070134901A1 (en) | Growth of GaAs expitaxial layers on Si substrate by using a novel GeSi buffer layer | |

| TWI394275B (zh) | 增強遷移率之SiGe異質接面雙極電晶體 | |

| CN1726581A (zh) | 应变绝缘体上硅(ssoi)及其形成方法 | |

| JPH08227863A (ja) | 半導体層中のドーパント拡散制御プロセス及びそれにより形成された半導体層 | |

| CN1086514C (zh) | 具有减小电阻的化合物半导体器件 | |

| CN101057008A (zh) | 在衬底上生长Si-Ge半导体材料和器件的方法 | |

| CN1894775A (zh) | 在MOSFET结构中形成应变Si-沟道的方法 | |

| US6744079B2 (en) | Optimized blocking impurity placement for SiGe HBTs | |

| CN1763908A (zh) | 具有一平滑的磊晶层的半导体元件及其制造方法 | |

| CN1417844A (zh) | 硅锗/硅的化学气相沉积生长方法 | |

| JP2002241195A (ja) | エピタキシャル多層膜の製造方法及びエピタキシャル多層膜 | |

| Ismail et al. | Si/SiGe quantum wells: fundamentals to technology | |

| US7678645B2 (en) | Formation of thin semiconductor layers by low-energy plasma enhanced chemical vapor deposition and semiconductor heterostructure devices |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20071024 Termination date: 20150905 |

|

| EXPY | Termination of patent right or utility model |