WO2024100467A1 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- WO2024100467A1 WO2024100467A1 PCT/IB2023/059255 IB2023059255W WO2024100467A1 WO 2024100467 A1 WO2024100467 A1 WO 2024100467A1 IB 2023059255 W IB2023059255 W IB 2023059255W WO 2024100467 A1 WO2024100467 A1 WO 2024100467A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- insulator

- conductor

- region

- oxide semiconductor

- oxide

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 1037

- 239000012212 insulator Substances 0.000 claims abstract description 2132

- 239000004020 conductor Substances 0.000 claims abstract description 1104

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims abstract description 97

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 72

- 239000010703 silicon Substances 0.000 claims abstract description 72

- 229910052757 nitrogen Inorganic materials 0.000 claims abstract description 49

- 229910052739 hydrogen Inorganic materials 0.000 claims description 121

- 239000001257 hydrogen Substances 0.000 claims description 121

- 239000012535 impurity Substances 0.000 claims description 88

- 239000013078 crystal Substances 0.000 claims description 84

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 24

- -1 iodine, hydrogen Chemical class 0.000 claims description 23

- 229910052799 carbon Inorganic materials 0.000 claims description 21

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 claims description 16

- 239000000460 chlorine Substances 0.000 claims description 16

- 229910052801 chlorine Inorganic materials 0.000 claims description 16

- 229910052731 fluorine Inorganic materials 0.000 claims description 14

- 239000011737 fluorine Substances 0.000 claims description 14

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 claims description 12

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 claims description 12

- 229910052794 bromium Inorganic materials 0.000 claims description 12

- 125000001153 fluoro group Chemical group F* 0.000 claims description 8

- 230000010354 integration Effects 0.000 abstract description 7

- 239000010408 film Substances 0.000 description 199

- 239000010410 layer Substances 0.000 description 194

- 229910052760 oxygen Inorganic materials 0.000 description 194

- 239000001301 oxygen Substances 0.000 description 192

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 188

- 230000015654 memory Effects 0.000 description 182

- 230000006870 function Effects 0.000 description 162

- 239000000463 material Substances 0.000 description 129

- 150000004706 metal oxides Chemical class 0.000 description 129

- 229910044991 metal oxide Inorganic materials 0.000 description 128

- 230000015572 biosynthetic process Effects 0.000 description 115

- 238000000034 method Methods 0.000 description 109

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 97

- 239000000758 substrate Substances 0.000 description 91

- 210000004027 cell Anatomy 0.000 description 79

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 65

- 229910052751 metal Inorganic materials 0.000 description 64

- 230000004888 barrier function Effects 0.000 description 61

- 238000003860 storage Methods 0.000 description 56

- 229910052581 Si3N4 Inorganic materials 0.000 description 54

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 54

- 238000000231 atomic layer deposition Methods 0.000 description 50

- 125000004429 atom Chemical group 0.000 description 48

- 239000002184 metal Substances 0.000 description 39

- 238000009792 diffusion process Methods 0.000 description 37

- 239000002356 single layer Substances 0.000 description 33

- 239000000203 mixture Substances 0.000 description 31

- 239000011701 zinc Substances 0.000 description 28

- 239000003990 capacitor Substances 0.000 description 27

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 25

- 230000000694 effects Effects 0.000 description 24

- 238000012545 processing Methods 0.000 description 24

- 238000003491 array Methods 0.000 description 23

- 230000007547 defect Effects 0.000 description 23

- 150000004767 nitrides Chemical class 0.000 description 23

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 22

- 229910001868 water Inorganic materials 0.000 description 22

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 21

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 21

- 229910052782 aluminium Inorganic materials 0.000 description 21

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 21

- 229910052814 silicon oxide Inorganic materials 0.000 description 21

- 229910052735 hafnium Inorganic materials 0.000 description 20

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 19

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 19

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 18

- 229910052733 gallium Inorganic materials 0.000 description 18

- 229910052738 indium Inorganic materials 0.000 description 18

- 150000002431 hydrogen Chemical class 0.000 description 16

- 238000004519 manufacturing process Methods 0.000 description 16

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 16

- 229910052721 tungsten Inorganic materials 0.000 description 16

- 239000010937 tungsten Substances 0.000 description 16

- 238000010586 diagram Methods 0.000 description 15

- 230000005669 field effect Effects 0.000 description 15

- 239000011810 insulating material Substances 0.000 description 15

- 230000008569 process Effects 0.000 description 15

- 238000004544 sputter deposition Methods 0.000 description 15

- 239000012298 atmosphere Substances 0.000 description 14

- 239000002346 layers by function Substances 0.000 description 14

- 229910000449 hafnium oxide Inorganic materials 0.000 description 13

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 13

- 238000010438 heat treatment Methods 0.000 description 13

- 230000003647 oxidation Effects 0.000 description 13

- 238000007254 oxidation reaction Methods 0.000 description 13

- 230000005621 ferroelectricity Effects 0.000 description 12

- 230000003071 parasitic effect Effects 0.000 description 12

- 239000000126 substance Substances 0.000 description 12

- 238000005229 chemical vapour deposition Methods 0.000 description 11

- 238000005530 etching Methods 0.000 description 11

- 239000007789 gas Substances 0.000 description 11

- 239000011229 interlayer Substances 0.000 description 11

- 230000004048 modification Effects 0.000 description 11

- 238000012986 modification Methods 0.000 description 11

- 239000011787 zinc oxide Substances 0.000 description 11

- 239000000969 carrier Substances 0.000 description 10

- 229910052746 lanthanum Inorganic materials 0.000 description 10

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 10

- 230000002093 peripheral effect Effects 0.000 description 10

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 9

- 239000002243 precursor Substances 0.000 description 9

- 239000000523 sample Substances 0.000 description 9

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 9

- 229910052715 tantalum Inorganic materials 0.000 description 9

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 9

- 239000010936 titanium Substances 0.000 description 9

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 8

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 8

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 8

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 8

- 229910001195 gallium oxide Inorganic materials 0.000 description 8

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 8

- 125000004430 oxygen atom Chemical group O* 0.000 description 8

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 8

- 239000004417 polycarbonate Substances 0.000 description 8

- 229910052712 strontium Inorganic materials 0.000 description 8

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 8

- 229910052719 titanium Inorganic materials 0.000 description 8

- 229910001928 zirconium oxide Inorganic materials 0.000 description 8

- 238000004458 analytical method Methods 0.000 description 7

- 238000004364 calculation method Methods 0.000 description 7

- 230000005684 electric field Effects 0.000 description 7

- 230000005855 radiation Effects 0.000 description 7

- 229910052707 ruthenium Inorganic materials 0.000 description 7

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 7

- 229910052727 yttrium Inorganic materials 0.000 description 7

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 7

- VZSRBBMJRBPUNF-UHFFFAOYSA-N 2-(2,3-dihydro-1H-inden-2-ylamino)-N-[3-oxo-3-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propyl]pyrimidine-5-carboxamide Chemical compound C1C(CC2=CC=CC=C12)NC1=NC=C(C=N1)C(=O)NCCC(N1CC2=C(CC1)NN=N2)=O VZSRBBMJRBPUNF-UHFFFAOYSA-N 0.000 description 6

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 6

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 6

- AFCARXCZXQIEQB-UHFFFAOYSA-N N-[3-oxo-3-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propyl]-2-[[3-(trifluoromethoxy)phenyl]methylamino]pyrimidine-5-carboxamide Chemical compound O=C(CCNC(=O)C=1C=NC(=NC=1)NCC1=CC(=CC=C1)OC(F)(F)F)N1CC2=C(CC1)NN=N2 AFCARXCZXQIEQB-UHFFFAOYSA-N 0.000 description 6

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 6

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 238000005516 engineering process Methods 0.000 description 6

- 229910052736 halogen Inorganic materials 0.000 description 6

- 150000002367 halogens Chemical class 0.000 description 6

- 239000002994 raw material Substances 0.000 description 6

- 239000010409 thin film Substances 0.000 description 6

- 229910052726 zirconium Inorganic materials 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical group [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 5

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 5

- MKYBYDHXWVHEJW-UHFFFAOYSA-N N-[1-oxo-1-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propan-2-yl]-2-[[3-(trifluoromethoxy)phenyl]methylamino]pyrimidine-5-carboxamide Chemical compound O=C(C(C)NC(=O)C=1C=NC(=NC=1)NCC1=CC(=CC=C1)OC(F)(F)F)N1CC2=C(CC1)NN=N2 MKYBYDHXWVHEJW-UHFFFAOYSA-N 0.000 description 5

- 229910052779 Neodymium Inorganic materials 0.000 description 5

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 5

- 229910052796 boron Inorganic materials 0.000 description 5

- 230000008859 change Effects 0.000 description 5

- 238000006243 chemical reaction Methods 0.000 description 5

- 239000011248 coating agent Substances 0.000 description 5

- 238000000576 coating method Methods 0.000 description 5

- 150000001875 compounds Chemical class 0.000 description 5

- 239000000470 constituent Substances 0.000 description 5

- 238000000151 deposition Methods 0.000 description 5

- 229910003437 indium oxide Inorganic materials 0.000 description 5

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 5

- 229910052749 magnesium Inorganic materials 0.000 description 5

- 239000011777 magnesium Substances 0.000 description 5

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 5

- 230000004044 response Effects 0.000 description 5

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 5

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical group CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 description 4

- 229910052684 Cerium Inorganic materials 0.000 description 4

- 101001094647 Homo sapiens Serum paraoxonase/arylesterase 1 Proteins 0.000 description 4

- 101000621061 Homo sapiens Serum paraoxonase/arylesterase 2 Proteins 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- 102100035476 Serum paraoxonase/arylesterase 1 Human genes 0.000 description 4

- 102100022824 Serum paraoxonase/arylesterase 2 Human genes 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 4

- 150000004770 chalcogenides Chemical class 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 229910052732 germanium Inorganic materials 0.000 description 4

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 4

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- 230000000737 periodic effect Effects 0.000 description 4

- 239000011295 pitch Substances 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 4

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910052723 transition metal Inorganic materials 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- 229910052725 zinc Inorganic materials 0.000 description 4

- YLZOPXRUQYQQID-UHFFFAOYSA-N 3-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)-1-[4-[2-[[3-(trifluoromethoxy)phenyl]methylamino]pyrimidin-5-yl]piperazin-1-yl]propan-1-one Chemical compound N1N=NC=2CN(CCC=21)CCC(=O)N1CCN(CC1)C=1C=NC(=NC=1)NCC1=CC(=CC=C1)OC(F)(F)F YLZOPXRUQYQQID-UHFFFAOYSA-N 0.000 description 3

- 229910018137 Al-Zn Inorganic materials 0.000 description 3

- 229910018573 Al—Zn Inorganic materials 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 3

- 229910052693 Europium Inorganic materials 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 238000004833 X-ray photoelectron spectroscopy Methods 0.000 description 3

- 230000001154 acute effect Effects 0.000 description 3

- 229910052783 alkali metal Inorganic materials 0.000 description 3

- 150000001340 alkali metals Chemical class 0.000 description 3

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 3

- 150000001342 alkaline earth metals Chemical class 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 230000003247 decreasing effect Effects 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- OGPBJKLSAFTDLK-UHFFFAOYSA-N europium atom Chemical compound [Eu] OGPBJKLSAFTDLK-UHFFFAOYSA-N 0.000 description 3

- 238000000605 extraction Methods 0.000 description 3

- YZZNJYQZJKSEER-UHFFFAOYSA-N gallium tin Chemical compound [Ga].[Sn] YZZNJYQZJKSEER-UHFFFAOYSA-N 0.000 description 3

- KQHQLIAOAVMAOW-UHFFFAOYSA-N hafnium(4+) oxygen(2-) zirconium(4+) Chemical compound [O--].[O--].[O--].[O--].[Zr+4].[Hf+4] KQHQLIAOAVMAOW-UHFFFAOYSA-N 0.000 description 3

- 230000006872 improvement Effects 0.000 description 3

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 3

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 3

- 239000000395 magnesium oxide Substances 0.000 description 3

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 3

- 125000004433 nitrogen atom Chemical group N* 0.000 description 3

- 230000035699 permeability Effects 0.000 description 3

- 239000012466 permeate Substances 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 3

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 3

- 229910052714 tellurium Inorganic materials 0.000 description 3

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- 229910052720 vanadium Inorganic materials 0.000 description 3

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 3

- 235000012431 wafers Nutrition 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 229910052582 BN Inorganic materials 0.000 description 2

- PZNSFCLAULLKQX-UHFFFAOYSA-N Boron nitride Chemical compound N#B PZNSFCLAULLKQX-UHFFFAOYSA-N 0.000 description 2

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- 229910052688 Gadolinium Inorganic materials 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 2

- NIPNSKYNPDTRPC-UHFFFAOYSA-N N-[2-oxo-2-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)ethyl]-2-[[3-(trifluoromethoxy)phenyl]methylamino]pyrimidine-5-carboxamide Chemical compound O=C(CNC(=O)C=1C=NC(=NC=1)NCC1=CC(=CC=C1)OC(F)(F)F)N1CC2=C(CC1)NN=N2 NIPNSKYNPDTRPC-UHFFFAOYSA-N 0.000 description 2

- 229910052777 Praseodymium Inorganic materials 0.000 description 2

- 229910052773 Promethium Inorganic materials 0.000 description 2

- 229910052772 Samarium Inorganic materials 0.000 description 2

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910020994 Sn-Zn Inorganic materials 0.000 description 2

- 229910009069 Sn—Zn Inorganic materials 0.000 description 2

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 2

- 241000724291 Tobacco streak virus Species 0.000 description 2

- DBKNIEBLJMAJHX-UHFFFAOYSA-N [As]#B Chemical compound [As]#B DBKNIEBLJMAJHX-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 229910052787 antimony Inorganic materials 0.000 description 2

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 2

- 238000013528 artificial neural network Methods 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- 229910052454 barium strontium titanate Inorganic materials 0.000 description 2

- 229910052797 bismuth Inorganic materials 0.000 description 2

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 2

- 229910052793 cadmium Inorganic materials 0.000 description 2

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 2

- 229910052791 calcium Inorganic materials 0.000 description 2

- 239000011575 calcium Substances 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 229910052798 chalcogen Inorganic materials 0.000 description 2

- 150000001787 chalcogens Chemical class 0.000 description 2

- 238000013527 convolutional neural network Methods 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- JAONJTDQXUSBGG-UHFFFAOYSA-N dialuminum;dizinc;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Al+3].[Al+3].[Zn+2].[Zn+2] JAONJTDQXUSBGG-UHFFFAOYSA-N 0.000 description 2

- 238000002003 electron diffraction Methods 0.000 description 2

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 2

- UIWYJDYFSGRHKR-UHFFFAOYSA-N gadolinium atom Chemical compound [Gd] UIWYJDYFSGRHKR-UHFFFAOYSA-N 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 230000012447 hatching Effects 0.000 description 2

- 230000020169 heat generation Effects 0.000 description 2

- 238000001095 inductively coupled plasma mass spectrometry Methods 0.000 description 2

- 238000002354 inductively-coupled plasma atomic emission spectroscopy Methods 0.000 description 2

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 2

- 229910052451 lead zirconate titanate Inorganic materials 0.000 description 2

- 230000007774 longterm Effects 0.000 description 2

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 2

- 229910052752 metalloid Inorganic materials 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- PUDIUYLPXJFUGB-UHFFFAOYSA-N praseodymium atom Chemical compound [Pr] PUDIUYLPXJFUGB-UHFFFAOYSA-N 0.000 description 2

- VQMWBBYLQSCNPO-UHFFFAOYSA-N promethium atom Chemical compound [Pm] VQMWBBYLQSCNPO-UHFFFAOYSA-N 0.000 description 2

- 239000000376 reactant Substances 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 2

- 229910052711 selenium Inorganic materials 0.000 description 2

- 239000011669 selenium Substances 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 238000005476 soldering Methods 0.000 description 2

- 238000005477 sputtering target Methods 0.000 description 2

- 239000011593 sulfur Substances 0.000 description 2

- 229910052717 sulfur Inorganic materials 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- SDDGNMXIOGQCCH-UHFFFAOYSA-N 3-fluoro-n,n-dimethylaniline Chemical compound CN(C)C1=CC=CC(F)=C1 SDDGNMXIOGQCCH-UHFFFAOYSA-N 0.000 description 1

- DEXFNLNNUZKHNO-UHFFFAOYSA-N 6-[3-[4-[2-(2,3-dihydro-1H-inden-2-ylamino)pyrimidin-5-yl]piperidin-1-yl]-3-oxopropyl]-3H-1,3-benzoxazol-2-one Chemical compound C1C(CC2=CC=CC=C12)NC1=NC=C(C=N1)C1CCN(CC1)C(CCC1=CC2=C(NC(O2)=O)C=C1)=O DEXFNLNNUZKHNO-UHFFFAOYSA-N 0.000 description 1

- ZCYVEMRRCGMTRW-UHFFFAOYSA-N 7553-56-2 Chemical compound [I] ZCYVEMRRCGMTRW-UHFFFAOYSA-N 0.000 description 1

- 210000002925 A-like Anatomy 0.000 description 1

- 229910018140 Al-Sn Inorganic materials 0.000 description 1

- 229910018564 Al—Sn Inorganic materials 0.000 description 1

- FIPWRIJSWJWJAI-UHFFFAOYSA-N Butyl carbitol 6-propylpiperonyl ether Chemical compound C1=C(CCC)C(COCCOCCOCCCC)=CC2=C1OCO2 FIPWRIJSWJWJAI-UHFFFAOYSA-N 0.000 description 1

- YZCKVEUIGOORGS-OUBTZVSYSA-N Deuterium Chemical compound [2H] YZCKVEUIGOORGS-OUBTZVSYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 101000967087 Homo sapiens Metal-response element-binding transcription factor 2 Proteins 0.000 description 1

- 101001071233 Homo sapiens PHD finger protein 1 Proteins 0.000 description 1

- 101000612397 Homo sapiens Prenylcysteine oxidase 1 Proteins 0.000 description 1

- 102100040632 Metal-response element-binding transcription factor 2 Human genes 0.000 description 1

- 229910016001 MoSe Inorganic materials 0.000 description 1

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 1

- 102100036879 PHD finger protein 1 Human genes 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 238000005411 Van der Waals force Methods 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- BVKXKLLXKLOWJS-UHFFFAOYSA-N [In+3].[O-2].[Zn+2].[Al+3].[In+3] Chemical compound [In+3].[O-2].[Zn+2].[Al+3].[In+3] BVKXKLLXKLOWJS-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- 238000013473 artificial intelligence Methods 0.000 description 1

- JRPBQTZRNDNNOP-UHFFFAOYSA-N barium titanate Chemical compound [Ba+2].[Ba+2].[O-][Ti]([O-])([O-])[O-] JRPBQTZRNDNNOP-UHFFFAOYSA-N 0.000 description 1

- 229910002113 barium titanate Inorganic materials 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- LNMGXZOOXVAITI-UHFFFAOYSA-N bis(selanylidene)hafnium Chemical compound [Se]=[Hf]=[Se] LNMGXZOOXVAITI-UHFFFAOYSA-N 0.000 description 1

- WVMYSOZCZHQCSG-UHFFFAOYSA-N bis(sulfanylidene)zirconium Chemical compound S=[Zr]=S WVMYSOZCZHQCSG-UHFFFAOYSA-N 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 239000002775 capsule Substances 0.000 description 1

- 125000004432 carbon atom Chemical group C* 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910052800 carbon group element Inorganic materials 0.000 description 1

- 229910002090 carbon oxide Inorganic materials 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000007812 deficiency Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 229910052805 deuterium Inorganic materials 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- NKZSPGSOXYXWQA-UHFFFAOYSA-N dioxido(oxo)titanium;lead(2+) Chemical compound [Pb+2].[O-][Ti]([O-])=O NKZSPGSOXYXWQA-UHFFFAOYSA-N 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- 238000010292 electrical insulation Methods 0.000 description 1

- 230000005670 electromagnetic radiation Effects 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 1

- 238000005247 gettering Methods 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 229910021389 graphene Inorganic materials 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 239000005431 greenhouse gas Substances 0.000 description 1

- NRJVMVHUISHHQB-UHFFFAOYSA-N hafnium(4+);disulfide Chemical compound [S-2].[S-2].[Hf+4] NRJVMVHUISHHQB-UHFFFAOYSA-N 0.000 description 1

- 125000005842 heteroatom Chemical group 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- BDVZHDCXCXJPSO-UHFFFAOYSA-N indium(3+) oxygen(2-) titanium(4+) Chemical compound [O-2].[Ti+4].[In+3] BDVZHDCXCXJPSO-UHFFFAOYSA-N 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 230000002452 interceptive effect Effects 0.000 description 1

- PNDPGZBMCMUPRI-UHFFFAOYSA-N iodine Chemical compound II PNDPGZBMCMUPRI-UHFFFAOYSA-N 0.000 description 1

- 229910052740 iodine Inorganic materials 0.000 description 1

- 239000011630 iodine Substances 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 239000005435 mesosphere Substances 0.000 description 1

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 1

- MHWZQNGIEIYAQJ-UHFFFAOYSA-N molybdenum diselenide Chemical compound [Se]=[Mo]=[Se] MHWZQNGIEIYAQJ-UHFFFAOYSA-N 0.000 description 1

- CWQXQMHSOZUFJS-UHFFFAOYSA-N molybdenum disulfide Chemical compound S=[Mo]=S CWQXQMHSOZUFJS-UHFFFAOYSA-N 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 1

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910052699 polonium Inorganic materials 0.000 description 1

- HZEBHPIOVYHPMT-UHFFFAOYSA-N polonium atom Chemical compound [Po] HZEBHPIOVYHPMT-UHFFFAOYSA-N 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000098 polyolefin Polymers 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 229910052761 rare earth metal Inorganic materials 0.000 description 1

- 230000000306 recurrent effect Effects 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000000851 scanning transmission electron micrograph Methods 0.000 description 1

- HVEIXSLGUCQTMP-UHFFFAOYSA-N selenium(2-);zirconium(4+) Chemical compound [Se-2].[Se-2].[Zr+4] HVEIXSLGUCQTMP-UHFFFAOYSA-N 0.000 description 1

- 229910021428 silicene Inorganic materials 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical class [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

- 229910002076 stabilized zirconia Inorganic materials 0.000 description 1

- 239000005437 stratosphere Substances 0.000 description 1

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 239000005439 thermosphere Substances 0.000 description 1

- ITRNXVSDJBHYNJ-UHFFFAOYSA-N tungsten disulfide Chemical compound S=[W]=S ITRNXVSDJBHYNJ-UHFFFAOYSA-N 0.000 description 1

- 238000010792 warming Methods 0.000 description 1

- 239000013585 weight reducing agent Substances 0.000 description 1

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 1

- TYHJXGDMRRJCRY-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) tin(4+) Chemical compound [O-2].[Zn+2].[Sn+4].[In+3] TYHJXGDMRRJCRY-UHFFFAOYSA-N 0.000 description 1

- OPCPDIFRZGJVCE-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) titanium(4+) Chemical compound [O-2].[Zn+2].[In+3].[Ti+4] OPCPDIFRZGJVCE-UHFFFAOYSA-N 0.000 description 1

- 229910000859 α-Fe Inorganic materials 0.000 description 1

Images

Definitions

- One aspect of the present invention relates to a semiconductor device, a memory device, and an electronic device. Another aspect of the present invention relates to a method for manufacturing the semiconductor device.

- one embodiment of the present invention is not limited to the above technical field.

- Examples of technical fields of one embodiment of the present invention include semiconductor devices, display devices, light-emitting devices, power storage devices, memory devices, electronic devices, lighting devices, input devices (e.g., touch sensors), input/output devices (e.g., touch panels), driving methods thereof, or manufacturing methods thereof.

- a semiconductor device refers to any device that can function by utilizing semiconductor characteristics.

- Semiconductor elements such as transistors, as well as semiconductor circuits, arithmetic devices, and memory devices, are one embodiment of semiconductor devices.

- Display devices (such as liquid crystal display devices and light-emitting display devices), projection devices, lighting devices, electro-optical devices, power storage devices, memory devices, semiconductor circuits, imaging devices, electronic devices, and the like may be said to have semiconductor devices.

- a CPU is a collection of semiconductor elements that have semiconductor integrated circuits (at least transistors and capacitors) that are processed from semiconductor wafers and made into chips, and on which electrodes that serve as connection terminals are formed.

- IC chips Semiconductor circuits (IC chips) such as LSIs, CPUs, and memories are mounted on circuit boards, such as printed wiring boards, and are used as components in a variety of electronic devices.

- transistors are widely used in electronic devices such as integrated circuits (ICs) and image display devices (also simply referred to as display devices).

- ICs integrated circuits

- image display devices also simply referred to as display devices.

- Silicon-based semiconductor materials are widely known as semiconductor thin films that can be used in transistors, but oxide semiconductors are also attracting attention as other materials.

- Patent Document 1 discloses a low-power consumption CPU that utilizes the property of low leakage current of transistors using oxide semiconductors.

- Patent Document 2 discloses a memory device that can retain stored contents for a long period of time by utilizing the property of low leakage current of transistors using oxide semiconductors.

- Patent Document 3 and Non-Patent Document 1 disclose a technique for increasing the density of integrated circuits by stacking a first transistor using an oxide semiconductor film and a second transistor using an oxide semiconductor film to provide multiple overlapping memory cells.

- Patent Document 4 discloses a technique for increasing the density of integrated circuits by vertically arranging the channel of a transistor using an oxide semiconductor film.

- An object of one embodiment of the present invention is to provide a semiconductor device that can be miniaturized or highly integrated.

- An object of one embodiment of the present invention is to provide a semiconductor device with high operating speed.

- An object of one embodiment of the present invention is to provide a semiconductor device having good electrical characteristics.

- An object of one embodiment of the present invention is to provide a semiconductor device with little variation in the electrical characteristics of transistors.

- An object of one embodiment of the present invention is to provide a highly reliable semiconductor device.

- An object of one embodiment of the present invention is to provide a semiconductor device with large on-current.

- An object of one embodiment of the present invention is to provide a semiconductor device with low power consumption.

- An object of one embodiment of the present invention is to provide a new semiconductor device.

- An object of one embodiment of the present invention is to provide a method for manufacturing a semiconductor device with high productivity.

- An object of one embodiment of the present invention is to provide a method for manufacturing a new semiconductor device.

- one object of one embodiment of the present invention is to provide a memory device that can be miniaturized or highly integrated.

- One object of one embodiment of the present invention is to provide a memory device with a large storage capacity.

- One object of one embodiment of the present invention is to provide a memory device with a high operating speed.

- One object of one embodiment of the present invention is to provide a memory device with low power consumption.

- One object of one embodiment of the present invention is to provide a novel memory device.

- One aspect of the present invention includes a first insulator, an oxide semiconductor on the first insulator, a first conductor and a second conductor on the oxide semiconductor, a second insulator on the first insulator, the first conductor, and the second conductor, a third insulator on the oxide semiconductor, and a third conductor on the third insulator, wherein the oxide semiconductor has a first region overlapping with the first conductor, a second region overlapping with the second conductor, and a third region located between the first region and the second region,

- the second insulator has an opening in a region overlapping with the third region, at least a portion of each of the third insulator and the third conductor is provided inside the opening, the first region and the second region are in contact with the first insulator and the second insulator, respectively, the third region is in contact with the first insulator and the third insulator, each of the first insulator and the second insulator has silicon and nitrogen, and the first insulator has a region with a film

- one aspect of the present invention has a first insulator, an oxide semiconductor on the first insulator, a first conductor and a second conductor on the oxide semiconductor, a second insulator on the first insulator, on the first conductor, and on the second conductor, a third insulator on the oxide semiconductor, a third conductor on the third insulator, and a fourth insulator on the third insulator and on the third conductor, wherein the oxide semiconductor has a first region overlapping with the first conductor, a second region overlapping with the second conductor, and a third region located between the first region and the second region, and the second insulator , an opening is provided in a region overlapping with the third region, at least a portion of each of the third insulator and the third conductor is provided inside the opening, the first region and the second region are in contact with the first insulator and the second insulator, respectively, the third region is in contact with the first insulator and the third insulator, each of the first insulator,

- the impurity element is preferably fluorine, chlorine, bromine, iodine, hydrogen, or carbon.

- a fourth conductor is further provided below the first insulator, and the fourth conductor has a region overlapping with the third conductor, sandwiching the first insulator, the oxide semiconductor, and the third insulator therebetween.

- the first insulator is strip-shaped and extends in the same direction as the third conductor.

- the first insulator is island-shaped, the side edge of the first insulator coincides with the side edge of the oxide semiconductor, and the second insulator contacts the side of the first insulator.

- the third region of the oxide semiconductor preferably has a crystal on the side surface near the second insulator, the crystal has a crystal structure in which multiple layers are stacked, and the layers contained in the crystal preferably extend parallel or approximately parallel to the side surface of the oxide semiconductor.

- One aspect of the present invention has a first insulator, a second insulator on the first insulator, an oxide semiconductor on the first insulator covering the top and side surfaces of the second insulator, a first conductor and a second conductor on the oxide semiconductor, a third insulator on the first insulator, the first conductor, and the second conductor, a fourth insulator on the oxide semiconductor, and a third conductor on the fourth insulator, wherein the oxide semiconductor has a first region overlapping with the first conductor, a second region overlapping with the second conductor, and a third region located between the first region and the second region.

- the third insulator has an opening in a region overlapping with the third region, at least a portion of each of the fourth insulator and the third conductor is provided inside the opening, the first region and the second region are in contact with the first insulator, the second insulator, and the third insulator, respectively, the third region is in contact with the first insulator, the second insulator, and the fourth insulator, each of the first insulator, the second insulator, and the third insulator has silicon and nitrogen, and the first insulator has a region with a film thickness of 1.0 nm or more and 5.0 nm or less.

- the height of the second insulator is greater than the length of the second insulator in the direction in which the third conductor extends.

- a fifth insulator is further provided on the fourth insulator and the third conductor, the first insulator has a region having a smaller thickness than the fifth insulator, and the concentration of impurity elements in the first insulator is higher than the concentration of impurity elements in the fifth insulator.

- the impurity element is preferably fluorine, chlorine, bromine, iodine, hydrogen, or carbon.

- the third region of the oxide semiconductor preferably has a crystal on the side near the fourth insulator, the crystal has a crystal structure in which multiple layers are stacked, and the layers contained in the crystal preferably extend parallel or approximately parallel to the surface of the oxide semiconductor.

- One aspect of the present invention has a first insulator, a second insulator, a third insulator on the first insulator, and a fourth insulator located between the second insulator and the third insulator, an oxide semiconductor on the second insulator, the third insulator, and the fourth insulator, a first conductor and a second conductor on the oxide semiconductor, a fifth insulator on the first insulator, the first conductor, and the second conductor, a sixth insulator on the oxide semiconductor, and a third conductor on the sixth insulator, wherein the oxide semiconductor has a first region overlapping with the first conductor, a second region overlapping with the second conductor, and a third region located between the first region and the second region.

- the semiconductor device has a region, the fifth insulator has an opening in a region overlapping with the third region, at least a portion of each of the sixth insulator and the third conductor is provided inside the opening, the first region contacts the second insulator and the fifth insulator, the second region contacts the third insulator and the fifth insulator, the third region contacts the fourth insulator and the sixth insulator, each of the second insulator, the third insulator, and the fifth insulator has silicon and nitrogen, the second insulator, the third insulator, and the fourth insulator have the same thickness, and the second insulator has a region with a thickness of 1.0 nm or more and 5.0 nm or less.

- An embodiment of the present invention includes a first insulator, a second insulator, a third insulator on the first insulator, and a fourth insulator located between the second insulator and the third insulator, an oxide semiconductor on the second insulator, the third insulator, and the fourth insulator, a first conductor and a second conductor on the oxide semiconductor, a fifth insulator on the first insulator, the first conductor, and the second conductor, a sixth insulator on the oxide semiconductor, a third conductor on the sixth insulator, and a seventh insulator on the sixth insulator and the third conductor, and the oxide semiconductor has a first region overlapping with the first conductor, a second region overlapping with the second conductor, and a third region located between the first region and the second region.

- the fifth insulator has an opening in a region overlapping with the third region, at least a portion of each of the sixth insulator and the third conductor is provided inside the opening, the first region contacts the second insulator and the fifth insulator, the second region contacts the third insulator and the fifth insulator, the third region contacts the fourth insulator and the sixth insulator, each of the second insulator, the third insulator, the fifth insulator, and the seventh insulator has silicon and nitrogen, the second insulator, the third insulator, and the fourth insulator have the same thickness, the second insulator has a region with a thickness smaller than that of the seventh insulator, and the concentration of the impurity element in the second insulator is higher than the concentration of the impurity element in the seventh insulator.

- the impurity element is preferably fluorine, chlorine, bromine, iodine, hydrogen, or carbon.

- a fourth conductor is further provided below the first insulator, and the fourth conductor has a region overlapping with the third conductor, sandwiching the first insulator, the fourth insulator, the oxide semiconductor, and the sixth insulator therebetween.

- each of the second insulator, the third insulator, and the fourth insulator is strip-shaped and extends in the same direction as the third conductor.

- each of the second insulator, the third insulator, and the fourth insulator is island-shaped, the side end of the second insulator coincides with the side end of the oxide semiconductor, the side end of the third insulator coincides with the side end of the oxide semiconductor, the side end of the fourth insulator coincides with the side end of the oxide semiconductor, and the fifth insulator contacts the side of the second insulator and the side of the third insulator.

- the third region of the oxide semiconductor preferably has a crystal on the side surface near the sixth insulator, the crystal has a crystal structure in which multiple layers are stacked, and the layers included in the crystal preferably extend parallel or approximately parallel to the side surface of the oxide semiconductor.

- One aspect of the present invention has a first insulator, a second insulator, a third insulator on the first insulator, and a fourth insulator located between the second insulator and the third insulator, a fifth insulator on the second insulator, the third insulator, and the fourth insulator, an oxide semiconductor on the second insulator, the third insulator, and the fourth insulator covering the upper surface and side surface of the fifth insulator, a first conductor and a second conductor on the oxide semiconductor, a sixth insulator on the first insulator, the first conductor, and the second conductor, a seventh insulator on the oxide semiconductor, and a third conductor on the seventh insulator, and the oxide semiconductor has a first region overlapping with the first conductor, a second region overlapping with the second conductor, and a first region overlapping with the second region.

- the sixth insulator has an opening in a region overlapping the third region, at least a portion of the seventh insulator and the third conductor is provided inside the opening, the first region contacts the second insulator, the fifth insulator, and the sixth insulator, the second region contacts the third insulator, the fifth insulator, and the sixth insulator, the third region contacts the fourth insulator, the fifth insulator, and the seventh insulator, each of the second insulator, the third insulator, the fifth insulator, and the seventh insulator has silicon and nitrogen, the second insulator, the third insulator, and the fourth insulator have the same thickness, and the second insulator has a region with a thickness of 1.0 nm or more and 5.0 nm or less.

- the height of the fifth insulator is greater than the length of the fifth insulator in the direction in which the third conductor extends.

- an eighth insulator is further provided on the seventh insulator and the third conductor, the second insulator has a region having a smaller thickness than the eighth insulator, and the concentration of impurity elements in the second insulator is higher than the concentration of impurity elements in the eighth insulator.

- the impurity element is preferably fluorine, chlorine, bromine, iodine, hydrogen, or carbon.

- the third region of the oxide semiconductor preferably has a crystal on the side near the seventh insulator, the crystal has a crystal structure in which multiple layers are stacked, and the layers contained in the crystal preferably extend parallel or approximately parallel to the surface of the oxide semiconductor.

- a semiconductor device that can be miniaturized or highly integrated can be provided.

- a semiconductor device with high operating speed can be provided.

- a semiconductor device having good electrical characteristics can be provided.

- a semiconductor device with less variation in electrical characteristics of transistors can be provided.

- a highly reliable semiconductor device can be provided.

- a semiconductor device with large on-current can be provided.

- a semiconductor device with low power consumption can be provided.

- a novel semiconductor device can be provided.

- a method for manufacturing a semiconductor device with high productivity can be provided.

- a method for manufacturing a novel semiconductor device can be provided.

- a memory device that can be miniaturized or highly integrated can be provided.

- a memory device with a large storage capacity can be provided.

- a memory device with a high operating speed can be provided.

- a memory device with low power consumption can be provided.

- a novel memory device can be provided.

- Fig. 1A is a plan view showing an example of a semiconductor device

- Fig. 1B to Fig. 1D are cross-sectional views showing an example of a semiconductor device

- Fig. 1E is a schematic perspective view showing an example of a semiconductor device.

- 2A and 2B are cross-sectional views showing an example of a semiconductor device.

- 3A and 3B are cross-sectional views showing an example of a semiconductor device.

- Fig. 4A is a plan view showing an example of a semiconductor device

- Figs. 4B to 4D are cross-sectional views showing an example of the semiconductor device.

- Fig. 5A is a plan view showing an example of a semiconductor device

- Figs. 5B to 5D are cross-sectional views showing an example of the semiconductor device.

- Fig. 6A is a plan view showing an example of a semiconductor device

- Figs. 6B to 6D are cross-sectional views showing an example of the semiconductor device

- Fig. 7A is a plan view showing an example of a semiconductor device

- Figs. 7B to 7D are cross-sectional views showing an example of the semiconductor device

- Fig. 8A is a plan view showing an example of a semiconductor device

- Figs. 8B to 8D are cross-sectional views showing an example of the semiconductor device.

- 9A is a plan view showing an example of a semiconductor device

- FIGS. 9B to 9D are cross-sectional views showing an example of the semiconductor device

- Fig. 10A is a plan view showing an example of a semiconductor device, and Figs.

- FIG. 10B to 10D are cross-sectional views showing an example of the semiconductor device.

- Fig. 11A is a plan view showing an example of a semiconductor device, and Figs. 11B to 11D are cross-sectional views showing an example of the semiconductor device.

- Fig. 12A is a plan view showing an example of a semiconductor device, and Figs. 12B to 12D are cross-sectional views showing an example of the semiconductor device.

- Fig. 13A is a plan view showing an example of a semiconductor device, and Figs. 13B to 13D are cross-sectional views showing an example of the semiconductor device.

- Fig. 14A is a plan view showing an example of a semiconductor device, Fig. 14B to Fig.

- FIG. 14D are cross-sectional views showing an example of a semiconductor device

- Fig. 14E is a schematic perspective view showing an example of a semiconductor device

- FIG. 15 is a cross-sectional view showing an example of a semiconductor device.

- Fig. 16A is a plan view showing an example of a semiconductor device

- Figs. 16B to 16D are cross-sectional views showing an example of the semiconductor device.

- Fig. 17A is a plan view showing an example of a semiconductor device

- Figs. 17B to 17D are cross-sectional views showing an example of the semiconductor device.

- Fig. 18A is a plan view showing an example of a semiconductor device

- Figs. 18B to 18D are cross-sectional views showing an example of the semiconductor device.

- Fig. 18A is a plan view showing an example of a semiconductor device

- Figs. 18B to 18D are cross-sectional views showing an example of the semiconductor device.

- Fig. 18A is a plan view showing

- FIG. 19A is a plan view showing an example of a semiconductor device

- Figs. 19B to 19D are cross-sectional views showing an example of the semiconductor device

- Fig. 20A is a plan view showing an example of a semiconductor device

- Fig. 20B to Fig. 20D are cross-sectional views showing an example of the semiconductor device

- Fig. 21A is a plan view showing an example of a semiconductor device

- Fig. 21B to Fig. 21D are cross-sectional views showing an example of the semiconductor device

- Fig. 22A is a plan view showing an example of a semiconductor device

- Fig. 22B to Fig. 22D are cross-sectional views showing an example of the semiconductor device.

- Fig. 22A is a plan view showing an example of a semiconductor device

- Fig. 22B to Fig. 22D are cross-sectional views showing an example of the semiconductor device.

- Fig. 22A is a plan view showing an example of a semiconductor device

- FIG. 23A is a plan view showing an example of a semiconductor device

- Fig. 23B to Fig. 23D are cross-sectional views showing an example of the semiconductor device

- Fig. 24A is a plan view showing an example of a semiconductor device

- Fig. 24B to Fig. 24D are cross-sectional views showing an example of the semiconductor device

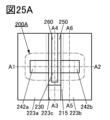

- Fig. 25A is a plan view showing an example of a semiconductor device

- Fig. 25B to Fig. 25D are cross-sectional views showing an example of the semiconductor device

- Fig. 26A is a plan view showing an example of a semiconductor device

- Fig. 26B to Fig. 26D are cross-sectional views showing an example of the semiconductor device.

- Fig. 26A is a plan view showing an example of a semiconductor device

- Fig. 26B to Fig. 26D are cross-sectional views showing an example of the semiconductor device.

- Fig. 26A is a plan view showing an example of a semiconductor device

- FIG. 27A is a plan view showing an example of a semiconductor device

- Fig. 27B to Fig. 27D are cross-sectional views showing an example of the semiconductor device

- Fig. 28A is a plan view showing an example of a semiconductor device

- Fig. 28B to Fig. 28D are cross-sectional views showing an example of the semiconductor device

- Fig. 29A is a plan view showing an example of a semiconductor device

- Fig. 29B to Fig. 29D are cross-sectional views showing an example of the semiconductor device

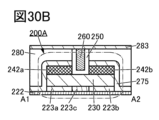

- Fig. 30A is a plan view showing an example of a semiconductor device

- Fig. 30B to Fig. 30D are cross-sectional views showing an example of the semiconductor device.

- Fig. 30A is a plan view showing an example of a semiconductor device

- Fig. 30B to Fig. 30D are cross-sectional views showing an example of the semiconductor device.

- Fig. 30A is a plan view showing an example of a semiconductor device

- FIG. 31A is a plan view showing an example of a semiconductor device

- Fig. 31B to Fig. 31D are cross-sectional views showing an example of the semiconductor device

- Fig. 32A is a plan view showing an example of a semiconductor device

- Fig. 32B to Fig. 32D are cross-sectional views showing an example of the semiconductor device

- Fig. 33A is a plan view showing an example of a semiconductor device

- Fig. 33B to Fig. 33D are cross-sectional views showing an example of the semiconductor device

- 34A and 34B are cross-sectional views showing an example of a semiconductor device

- 35A and 35B are cross-sectional views showing an example of a semiconductor device.

- Fig. 31B to Fig. 31D are cross-sectional views showing an example of the semiconductor device.

- Fig. 32A is a plan view showing an example of a semiconductor device

- Fig. 32B to Fig. 32D are cross-sectional views showing an example of the semiconductor device

- FIG. 36A is a plan view showing an example of a semiconductor device

- Fig. 36B to Fig. 36D are cross-sectional views showing an example of the semiconductor device

- Fig. 37A is a plan view showing an example of a semiconductor device

- Fig. 37B to Fig. 37D are cross-sectional views showing an example of the semiconductor device

- 38A to 38C are cross-sectional views showing an example of a semiconductor device

- 39A to 39C are cross-sectional views showing an example of a semiconductor device

- Fig. 40A is a plan view showing an example of a semiconductor device

- Fig. 40B to Fig. 40D are cross-sectional views showing an example of the semiconductor device.

- Fig. 40A is a plan view showing an example of a semiconductor device

- Fig. 40B to Fig. 40D are cross-sectional views showing an example of the semiconductor device.

- Fig. 40A is a plan view showing an example of a semiconductor device

- FIG. 41A is a plan view showing an example of a semiconductor device

- Fig. 41B to Fig. 41D are cross-sectional views showing an example of the semiconductor device.

- FIG. 42 is a cross-sectional view showing an example of a semiconductor device.

- 43A to 43D are cross-sectional views showing an example of a semiconductor device.

- 44A to 44C are cross-sectional views showing an example of a semiconductor device.

- Fig. 45A is a plan view showing an example of a semiconductor device, and Fig. 45B to Fig. 45D are cross-sectional views showing an example of the semiconductor device.

- Fig. 46A is a plan view showing an example of a semiconductor device

- Fig. 46B to Fig. 46D are cross-sectional views showing an example of the semiconductor device.

- FIG. 47A and 47B are cross-sectional views showing an example of a semiconductor device.

- 48A to 48C are cross-sectional views showing an example of a semiconductor device.

- 49A to 49C are cross-sectional views showing an example of a semiconductor device.

- Fig. 50A is a plan view showing an example of a semiconductor device

- Fig. 50B to Fig. 50D are cross-sectional views showing an example of the semiconductor device.

- FIG. 51 is a block diagram showing an example of a storage device.

- 52A and 52B are a schematic diagram and a circuit diagram showing an example of a memory device.

- 53A and 53B are schematic diagrams showing an example of a storage device.

- FIG. 54 is a circuit diagram showing an example of a memory device.

- 55A and 55B are cross-sectional views showing an example of a memory device.

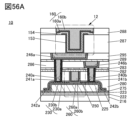

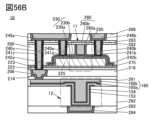

- 56A and 56B are cross-sectional views showing an example of a memory device.

- FIG. 57 is a cross-sectional view showing an example of a memory device.

- 58A and 58B are diagrams showing an example of a semiconductor device.

- 59A and 59B are diagrams showing an example of an electronic component.

- 60A and 60B are diagrams showing an example of an electronic device, and

- FIGS. 60C to 60E are diagrams showing an example of a mainframe computer.

- FIG. 61 is a diagram showing an example of space equipment.

- FIG. 62 is a diagram illustrating an example of a storage system applicable to a data center.

- FIG. 63 is a diagram for explaining the laminated structure of the laminated film.

- 64A and 64B show the results of SIMS analysis of the prepared sample.

- 65A to 65C show the results of SIMS analysis of the prepared sample.

- top views also called “top views”

- perspective views some components may be omitted from the illustration. Also, some hidden lines may be omitted from the illustration.

- ordinal numbers “first” and “second” are used for convenience and do not limit the number of components or the order of the components (e.g., the order of processes or the order of stacking). Furthermore, an ordinal number attached to a component in one place in this specification may not match an ordinal number attached to the same component in another place in this specification or in the claims.

- film and “layer” may be interchangeable depending on the circumstances.

- conductive layer may be interchangeable with the term “conductive film”.

- insulating film may be interchangeable with the term “insulating layer”.

- conductor may be interchangeable with the term “conductive layer” or the term “conductive film” depending on the circumstances.

- insulating material may be interchangeable with the term “insulating layer” or the term “insulating film” depending on the circumstances.

- parallel refers to a state in which two straight lines are arranged at an angle of -10 degrees or more and 10 degrees or less. Therefore, it also includes cases where the angle is -5 degrees or more and 5 degrees or less.

- approximately parallel refers to a state in which two straight lines are arranged at an angle of -30 degrees or more and 30 degrees or less.

- Perfect refers to a state in which two straight lines are arranged at an angle of 80 degrees or more and 100 degrees or less. Therefore, it also includes cases where the angle is 85 degrees or more and 95 degrees or less.

- approximately perpendicular refers to a state in which two straight lines are arranged at an angle of 60 degrees or more and 120 degrees or less.

- Openings include, for example, grooves and slits. Also, the area in which an opening is formed may be referred to as an opening.

- the sidewalls of the insulator at the opening in the insulator are shown as being perpendicular or approximately perpendicular to the substrate surface or the surface on which the insulator is formed, but they may also be tapered.

- a tapered shape refers to a shape in which at least a portion of the side of the structure is inclined with respect to the substrate surface or the surface on which the structure is to be formed.

- the taper angle there is a region in which the angle between the inclined side and the substrate surface or the surface on which the structure is to be formed (hereinafter, sometimes referred to as the taper angle) is less than 90°.

- the side of the structure and the substrate surface do not necessarily need to be completely flat, and may be approximately planar with a slight curvature, or approximately planar with fine irregularities.

- “same height” refers to a configuration in which the heights from a reference surface (for example, a flat surface such as a substrate surface) are equal in cross-sectional view.

- a planarization process typically a CMP process

- the surfaces treated in the CMP process have a configuration in which the heights from the reference surface are equal.

- the heights of multiple layers may differ depending on the processing device, processing method, or material of the surface treated in the CMP process. In this specification, this case is also treated as "same height”.

- first layer and a second layer when there are two layers (here, a first layer and a second layer) with different heights relative to the reference surface, and the difference in height between the top surface of the first layer and the top surface of the second layer is 20 nm or less, this is also referred to as "same height”.

- side edges coincide means that at least a portion of the contours of the stacked layers overlap when viewed in a plane. For example, this includes cases where the upper and lower layers are processed using the same mask pattern, or where a portion of the mask pattern is the same. However, strictly speaking, the contours may not overlap, and the contour of the upper layer may be located inside the contour of the lower layer, or the contour of the upper layer may be located outside the contour of the lower layer, in which case it is also referred to as "side edges coincide”.

- the first film thickness and the second film thickness being the same means that the absolute value of the difference between the first film thickness and the second film thickness divided by the first film thickness is 0.1 or less. Alternatively, it means that the absolute value of the difference between the first film thickness and the second film thickness divided by the second film thickness is 0.1 or less.

- distance A and distance B are the same means that the absolute value of the difference between distance A and distance B divided by distance A is 0.1 or less. Or, the absolute value of the difference between distance A and distance B divided by distance B is 0.1 or less.

- the semiconductor device according to one embodiment of the present invention includes a transistor.

- a in each figure shows a plan view of the semiconductor device.

- B in each figure is a cross-sectional view corresponding to the portion indicated by the dashed line A1-A2 in A of each figure, and is also a cross-sectional view in the channel length direction of the transistor.

- C in each figure is a cross-sectional view corresponding to the portion indicated by the dashed line A3-A4 in A of each figure, and is also a cross-sectional view in the channel width direction of the transistor.

- D in each figure is a cross-sectional view corresponding to the portion indicated by the dashed line A5-A6 in A of each figure. In the plan view of A in each figure, some elements are omitted to clarify the figure.

- 1A to 1D are plan views and cross-sectional views of a semiconductor device including a transistor 200.

- the semiconductor device shown in Figures 1A to 1D has an insulator 222 on a substrate (not shown), a transistor 200 on the insulator 222, an insulator 280 on the transistor 200, and an insulator 283 on the insulator 280.

- the insulators 222, 280, and 283 function as interlayer insulating films.

- the transistor 200 has an insulator 223 on the insulator 222, an oxide semiconductor 230 on the insulator 223, a conductor 242a and a conductor 242b on the oxide semiconductor 230, an insulator 275 on the insulator 223, the conductor 242a, and the conductor 242b, an insulator 250 on the oxide semiconductor 230, and a conductor 260 located on the insulator 250 and overlapping with a portion of the oxide semiconductor 230.

- the conductor 260 functions as a gate electrode of the transistor 200.

- the insulator 250 functions as a gate insulator of the transistor 200.

- the conductor 242a functions as one of the source electrode and drain electrode of the transistor 200, and the conductor 242b functions as the other of the source electrode and drain electrode of the transistor 200.

- At least a part of the region of the oxide semiconductor 230 that overlaps with the conductor 260 functions as a channel formation region of the transistor 200.

- FIG. 1E shows a schematic perspective view of the semiconductor device.

- insulator 222, insulator 223, oxide semiconductor 230, conductor 242b, insulator 250, conductor 260, insulator 275, and a portion of the surrounding area are shown cut away.

- FIG. 1E only the outlines of some components (e.g., insulator 280 and insulator 283) are shown by dashed lines.

- the oxide semiconductor 230 is provided in contact with the upper surface of the insulator 223.

- the conductor 242a and the conductor 242b are provided in contact with the upper surface of the oxide semiconductor 230.

- the insulator 275 is disposed on the insulator 223, the oxide semiconductor 230, the conductor 242a, and the conductor 242b. Specifically, the insulator 275 is provided in contact with the upper surface of the insulator 223, the side surface of the oxide semiconductor 230, the upper surface and side surface of the conductor 242a, and the upper surface and side surface of the conductor 242b.

- Insulator 280 is provided in contact with the upper surface of insulator 275.

- Each of the insulators 280 and 275 has an opening that reaches the oxide semiconductor 230.