WO2011040426A1 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- WO2011040426A1 WO2011040426A1 PCT/JP2010/066886 JP2010066886W WO2011040426A1 WO 2011040426 A1 WO2011040426 A1 WO 2011040426A1 JP 2010066886 W JP2010066886 W JP 2010066886W WO 2011040426 A1 WO2011040426 A1 WO 2011040426A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- plasma

- semiconductor device

- film

- manufacturing

- oxide film

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/02274—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32009—Arrangements for generation of plasma specially adapted for examination or treatment of objects, e.g. plasma sources

- H01J37/32192—Microwave generated discharge

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/0223—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate

- H01L21/02233—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer

- H01L21/02236—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer group IV semiconductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/30604—Chemical etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823857—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the gate insulating layers, e.g. different gate insulating layer thicknesses, particular gate insulator materials or particular gate insulator implants

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Plasma & Fusion (AREA)

- Inorganic Chemistry (AREA)

- Analytical Chemistry (AREA)

- Element Separation (AREA)

- Formation Of Insulating Films (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Memories (AREA)

Abstract

Description

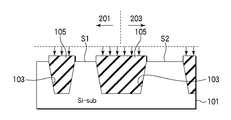

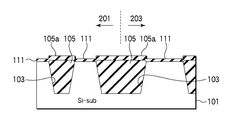

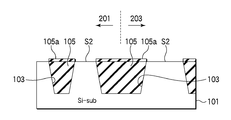

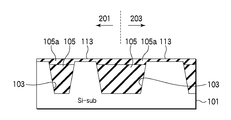

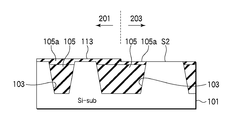

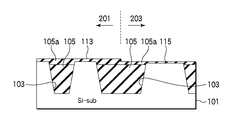

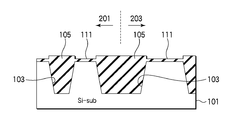

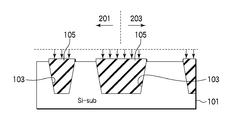

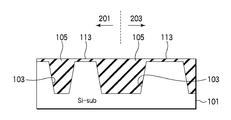

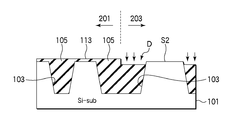

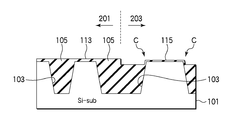

図1~図8は、本発明の半導体装置の製造方法を、半導体装置としてのトランジスタの製造におけるゲート酸化膜の形成に適用した場合の手順を示す工程図である。まず、図1は、シリコン基板101に複数のトレンチ103が形成され、各トレンチ103内に素子分離膜としての二酸化珪素膜105が埋め込まれた状態を示している。二酸化珪素膜105と二酸化珪素膜105との間は、トランジスタを形成するアクティブ領域である。図1では、異なる二つのデバイス領域を例示しており、中央の点線を境に、紙面に向かって左側が例えばI/O、セルなどに用いられるトランジスタ形成用の領域201であり、右側が例えばコアCMOSなどに用いられるトランジスタ形成用の領域203である。領域201は、高電圧トランジスタ形成用であり、領域203は、低電圧トランジスタ形成用である(なお、「高電圧」、「低電圧」の表現はあくまでも相対的な意味である)。

理する場合は、被処理体であるシリコン基板101にバイアス電圧を印加しながら行うことがより好ましい。

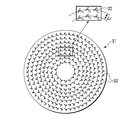

プラズマ処理装置100A,100Bは、複数のスロット状の孔を有する平面アンテナ、特にRLSA(Radial Line Slot Antenna;ラジアルラインスロットアンテナ)にて処理容器内にマイクロ波を導入することにより、高密度かつ低電子温度のマイクロ波励起プラズマを発生させ得るRLSAマイクロ波プラズマ処理装置として構成されている。プラズマ処理装置100A,100Bでは、1×1010~5×1012/cm3のプラズマ密度で、かつ0.7~2eVの低電子温度を有するプラズマによる処理が可能である。プラズマ処理装置100A,100Bは、各種半導体装置の製造過程において、シリコンを酸化して酸化珪素膜(SiO2膜)を形成するプラズマ酸化処理装置として好適に利用できる。

次に、プラズマ処理装置100Bに特徴的な構成である、載置台2にバイアスを印加するバイアス印加手段について説明する。プラズマ処理装置100Bの載置台2の表面側には電極42が埋設されている。この電極42には、給電線42aによって、マッチングボックス(M.B.)43を介してバイアス印加用の高周波電源44が接続されている。つまり、電極42に高周波電力を供給することによって、基板であるウエハWにバイアスを印加できる構成となっている。電極42、給電線42a、マッチングボックス(M.B.)43および高周波電源44は、プラズマ処理装置100Bにおいてバイアス印加手段を構成している。電極42の材質としては、例えばモリブデン、タングステンなどの導電性材料を用いることができる。電極42は、例えば網目状、格子状、渦巻き状等の形状に形成されている。

12[cm-3]以上のプラズマを形成する上で、処理ガス中のO2ガスの割合(体積比率)は、例えば1%以下が好ましく、0.2%から1%の範囲内がより好ましい。ガス流量は、例えばArガスが100~10000mL/min(sccm)、O2ガス:1~100mL/min(sccm)の範囲から、全ガス流量に対する酸素の割合が上記値となるように選択することができる。

また、プラズマ処理装置100Bを用いる場合には、プラズマ酸化処理を行なっている間、載置台2の電極42に高周波電源44から所定の周波数およびパワーの高周波電力を供給することができる。この高周波電源44から供給される高周波電力によってウエハWへバイアス電圧が印加され、プラズマの低い電子温度(0.7~2eV)を維持しつつ、プラズマ酸化処理が促進される。すなわち、バイアス電圧を印加することにより、O(1D2)ラジカルによる改質を行いつつ、プラズマ中の酸素イオンをウエハWへ引き込むことが可能であるため、シリコンの酸化レートを増大させ、低温でも膜深く改質することができる。

プラズマ処理装置100A,100Bを用いて酸素を含む処理ガスのプラズマを生成する場合、処理圧力によってプラズマ中の活性種が変化する。すなわち、プラズマ処理において設定可能な圧力範囲の中で、比較的高い圧力条件(例えば、333Pa超1333Pa以下)では、プラズマ中の活性種としてO2 +イオンやO(1D2)ラジカルは減少し、替わりにO(3P2)ラジカルが主体となる。一方、比較的低い圧力条件(333Pa以下)では、プラズマ中の活性種としてO2 +イオンやO(1D2)ラジカルが支配的となる。この条件で生成するO(1D2)ラジカルは、SiO2膜中に含まれるNやHなどの不純物を酸素原子に置き換える作用を有している。従って、O(1D2)ラジカルが支配的なプラズマによる酸化では、図17に示すように、O(1D2)ラジカルが膜中に含まれる不純物Impを酸素原子で置き換えることにより、SiO2膜の膜質が緻密化されるものと考えられる。また、このようなSiO2膜の改質効果は、被処理体であるシリコン基板101にバイアス電圧を印加しながら行うことによって、酸素イオンが引き込まれるため、いっそう増大する。本発明方法では、シリコンを酸化する工程で、O(1D2)ラジカルが生成する条件を選択してプラズマを生成し、シリコン表面と同時にSiO2膜を処理することによって、膜中の不純物が除去されて規則的なSi-O結合が形成された、欠陥の少ない緻密なSiO2膜に改質できる。そして、このように改質されたSiO2膜は、SOD膜やSOG膜、プラズマCVD膜と比較して高いウエットエッチング耐性を有することにより、後の半導体プロセスでウエットエッチングが繰返されても目減りを抑制できる。

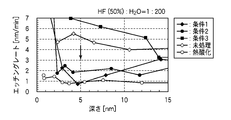

ポリシラザンを原料としてSOD法により塗布成膜し、水蒸気酸化(WVG)して形成した二酸化珪素膜(膜厚450nm)に対して、図14Aに示したものと同様のプラズマ処理装置100Aを用い、以下の条件でプラズマ処理を行った。処理後の二酸化珪素膜について、希フッ酸処理(50%HF:H2O=1:200)を行い、ウエットエッチングレートを調べた。また、比較のため、プラズマ処理を行わない二酸化珪素膜および熱酸化膜についても、同じ条件でのウエットエッチングレートを調べた。その結果を図18Aおよび図18Bに示した。なお、図18Bは図18Aの一部の条件を抜き出して示したものである。

体積流量比[(O2/Ar+O2+H2)×100];0.5~3%

体積流量比[(H2/Ar+O2+H2)×100];0.05~0.3%

処理圧力;66.6~266Pa(0.5~2Torr)

マイクロ波パワー密度;1~3W/cm2(透過板の面積1cm2あたり)

載置台2の温度;400~500℃

処理時間;360秒

(より限定した条件)

体積流量比[(O2/Ar+O2+H2)×100];0.8~1.5%

体積流量比[(H2/Ar+O2+H2)×100];0.08~0.15%

処理圧力;106.4~199.5Pa(0.8~1.5Torr)

マイクロ波パワー密度;1.2~2.4W/cm2(透過板の面積1cm2あたり)

載置台2の温度;400~500℃

処理時間;360秒

体積流量比[(O2/Ar+O2)×100];0.5~3%

処理圧力;66.6~266Pa(0.5~2Torr)

マイクロ波パワー密度;1~3W/cm2(透過板の面積1cm2あたり)

載置台2の温度;400~500℃

処理時間;360秒

(より限定した条件)

体積流量比[(O2/Ar+O2)×100];0.8~1.5%

処理圧力;106.4~199.5Pa(0.8~1.5Torr)

マイクロ波パワー密度;1.2~2.4W/cm2(透過板の面積1cm2あたり)

載置台2の温度;400~500℃

処理時間;360秒

体積流量比[(O2/Ar+O2+H2)×100];15~30%

体積流量比[(H2/Ar+O2+H2)×100];0.05~0.3%

処理圧力;239.4Pa以上(1.8Torr)

マイクロ波パワー密度;1~3W/cm2(透過板の面積1cm2あたり)

載置台2の温度;400~500℃

処理時間;360秒

(より限定した条件)

体積流量比[(O2/Ar+O2+H2)×100];20~23%

体積流量比[(H2/Ar+O2+H2)×100];0.05~0.3%

処理圧力;266~931Pa(2~7Torr)

マイクロ波パワー密度;1.2~2.4W/cm2(透過板の面積1cm2あたり)

載置台2の温度;400~500℃

処理時間;360秒

雰囲気;H2/O2=450/900mL/min(sccm)

温度;950℃

圧力;15000Pa

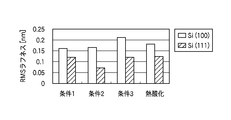

図14Aに示したものと同様のプラズマ処理装置100Aを用い、上記条件1~3でシリコン(100)面および(111)面をプラズマ酸化処理した。形成されたSiO2膜の表面と、Si/SiO2界面のRMS(平均二乗平方根)ラフネスを測定した。SiO2膜の表面のラフネスを図19、Si/SiO2界面のラフネスを図20に示した。図19および図20より、O(1D2)ラジカルが支配的となるプラズマを生成できる条件1、2で形成したSiO2膜は、熱酸化膜と比較して表面およびSi/SiO2界面のRMSラフネスが低く、より平坦化されていることがわかる。従って、条件1、2で形成したSiO2膜をトランジスタのゲート酸化膜として使用することにより、半導体装置のモビリティー特性と信頼性を改善させ、フリッカーノイズ(1/fノイズ)も低減できることが十分に予測された。

シリコン表面に5nmの厚みでスクリーン酸化膜を形成した後、11B+イオンを5eVのエネルギーで1×1013個/cm2注入した。その後、1000℃で10秒間アニールを行い、スクリーン酸化膜をウエットエッチングで除去してシリコン表面を露出させ、初期サンプルとした。この初期サンプルに、図14Aに示したものと同様のプラズマ処理装置100Aを用い、上記条件2でプラズマ酸化処理を行って3nmの二酸化珪素膜を形成した後、これを剥離し、SIMS(二次イオン質量分析計)でシリコン中のホウ素の濃度分布を調べた。比較のため、プラズマ酸化処理に替えて初期サンプルを950℃のO2/H2雰囲気で熱酸化処理した後に同様にホウ素の濃度分布を調べた。その結果を図21に示した。

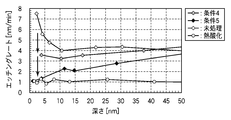

本実験では、図14Bに示したものと同様のプラズマ処理装置100Bを用い、ウエハWを載置する載置台2に高周波電力を印加しながらプラズマ酸化処理を行い、バイアス印加の効果を検証した。ポリシラザンを原料としてSOD法により成膜し、水蒸気酸化して形成した二酸化珪素膜(膜厚450nm)に対して、以下の条件でプラズマ処理を行った。処理後の二酸化珪素膜について、希フッ酸処理(50%HF:H2O=1:200)を行い、ウエットエッチングレートを調べた。また、比較のため、プラズマ処理を行わない二酸化珪素膜および熱酸化膜についても、同じ条件でのウエットエッチングレートを調べた。その結果を図22に示した。

体積流量比[(O2/Ar+O2+H2)×100];23%

体積流量比[(H2/Ar+O2+H2)×100];1.9%

処理圧力;666.7Pa(5Torr)

マイクロ波パワー密度;2.4W/cm2(透過板の面積1cm2あたり)

載置台2の温度;500℃

高周波電力の周波数:13.56MHz

高周波電力のパワー:600W(パワー密度0.85W/ウエハ1cm2当り)、

処理時間;360秒

体積流量比[(O2/Ar+O2+H2)×100];2.4%

体積流量比[(H2/Ar+O2+H2)×100];0.6%

処理圧力;40Pa(300mTorr)

マイクロ波パワー密度;0.7W/cm2(透過板の面積1cm2あたり)

載置台2の温度;500℃

高周波電力の周波数:13.56MHz

高周波電力のパワー:600W(パワー密度0.85W/ウエハ1cm2当り)、

処理時間;360秒

雰囲気;H2/O2=450/900mL/min(sccm)

温度;950℃

圧力;15000Pa

Claims (19)

- シリコン基板と、前記シリコン基板に所定間隔で形成されたトレンチと、前記トレンチ内に埋め込まれた素子分離用酸化膜と、前記素子分離用酸化膜の間に露出したシリコン表面と、を有する被処理体を準備することと、

前記シリコン表面をプラズマ酸化処理して犠牲酸化膜を形成することと、

前記犠牲酸化膜をウエットエッチングにより剥離してシリコン表面を再び露出させることと、

露出した前記シリコン表面を酸化処理して二酸化珪素膜を形成することと

を有し、

前記プラズマ酸化処理は、プラズマ処理装置の処理容器内で酸素を含む処理ガスを用いて生成させたO(1D2)ラジカルが支配的なプラズマにより行われる、半導体装置の製造方法。 - 前記酸化処理は、プラズマ処理装置の処理容器内で、酸素を含む処理ガスを用いて生成させたO(1D2)ラジカルが支配的なプラズマにより行う請求項1に記載の半導体装置の製造方法。

- 前記プラズマのO(1D2)ラジカルの密度が1×1012[cm-3]以上である請求項1に記載の半導体装置の製造方法。

- 前記処理容器内の圧力が、1.33~333Paの範囲内である、請求項3に記載の半導体装置の製造方法。

- 前記処理ガス中の酸素の割合が0.2~1%の範囲内である、請求項3に記載の半導体装置の製造方法。

- 前記処理ガスは、水素を1%以下の割合で含む請求項3に記載の半導体装置の製造方法。

- 前記プラズマは、前記処理ガスと、複数のスロットを有する平面アンテナにより前記処理室内に導入されるマイクロ波と、によって形成されるマイクロ波励起プラズマである請求項3に記載の半導体装置の製造方法。

- 前記プラズマ酸化処理の間、被処理体を載置する載置台に、高周波電力を供給する請求項3に記載の半導体装置の製造方法。

- 前記プラズマ酸化処理は、前記シリコン表面を酸化すると同時に前記素子分離用酸化膜を改質する請求項1に記載の半導体装置の製造方法。

- シリコン基板と、前記シリコン基板に所定間隔で形成されたトレンチと、前記トレンチ内に埋め込まれた素子分離用酸化膜と、前記素子分離用酸化膜の間に露出したシリコン表面と、を有する被処理体を準備することと、

前記シリコン表面を酸化処理して犠牲酸化膜を形成することと、

前記犠牲酸化膜をウエットエッチングにより剥離してシリコン表面を再び露出させることと、

露出した前記シリコン表面をプラズマ酸化処理して二酸化珪素膜を形成することと、

前記二酸化珪素膜の少なくとも一部分をウエットエッチングにより除去することと、

前記二酸化珪素膜が除去されて露出した部分のシリコン表面を酸化処理して前記二酸化珪素膜よりも厚みの薄い二酸化珪素膜を形成することと、

を有し、

前記プラズマ酸化処理は、プラズマ処理装置の処理容器内で、酸素を含む処理ガスを用いて生成させたO(1D2)ラジカルが支配的なプラズマにより行われる、半導体装置の製造方法。 - 前記露出したシリコン表面をプラズマ酸化処理して二酸化珪素膜を形成すること、および前記二酸化珪素膜の少なくとも一部分をウエットエッチングにより除去することは、繰り返し行われる、請求項10に記載の半導体装置に製造方法。

- 前記シリコン表面の酸化処理および/または前記二酸化珪素膜が除去されて露出した部分のシリコン表面の酸化処理は、プラズマ処理装置の処理容器内で、酸素を含む処理ガスを用いて生成させたO(1D2)ラジカルが支配的なプラズマにより行う請求項10に記載の半導体装置の製造方法。

- 前記プラズマのO(1D2)ラジカルの密度が1×1012[cm-3]以上である請求項10に記載の半導体装置の製造方法。

- 前記処理容器内の圧力が、1.33~333Paの範囲内である、請求項13に記載の半導体装置の製造方法。

- 前記処理ガス中の酸素の割合が0.2~1%の範囲内である、請求項13に記載の半導体装置の製造方法。

- 前記処理ガスは、水素を1%以下の割合で含む請求項13に記載の半導体装置の製造方法。

- 前記プラズマは、前記処理ガスと、複数のスロットを有する平面アンテナにより前記処理室内に導入されるマイクロ波と、によって形成されるマイクロ波励起プラズマである請求項13に記載の半導体装置の製造方法。

- 前記プラズマ酸化処理の間、被処理体を載置する載置台に、高周波電力を供給する請求項13に記載の半導体装置の製造方法。

- 前記露出したシリコン表面のプラズマ酸化処理は、前記シリコン表面を酸化すると同時に前記素子分離用酸化膜を改質する請求項10に記載の半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/498,259 US20120184107A1 (en) | 2009-09-30 | 2010-09-29 | Semiconductor device manufacturing method |

| KR1020127011218A KR101380094B1 (ko) | 2009-09-30 | 2010-09-29 | 반도체 장치의 제조 방법 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009227638 | 2009-09-30 | ||

| JP2009-227638 | 2009-09-30 | ||

| JP2010-207773 | 2010-09-16 | ||

| JP2010207773A JP2011097029A (ja) | 2009-09-30 | 2010-09-16 | 半導体装置の製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2011040426A1 true WO2011040426A1 (ja) | 2011-04-07 |

Family

ID=43826242

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2010/066886 WO2011040426A1 (ja) | 2009-09-30 | 2010-09-29 | 半導体装置の製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20120184107A1 (ja) |

| JP (1) | JP2011097029A (ja) |

| KR (1) | KR101380094B1 (ja) |

| TW (1) | TW201125071A (ja) |

| WO (1) | WO2011040426A1 (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5981206B2 (ja) * | 2012-04-20 | 2016-08-31 | 株式会社東芝 | 半導体装置の製造方法および半導体製造装置 |

| CN103258732B (zh) * | 2013-05-07 | 2016-08-24 | 上海华力微电子有限公司 | 防止硅衬底表面损伤的方法 |

| US9379132B2 (en) * | 2014-10-24 | 2016-06-28 | Sandisk Technologies Inc. | NAND memory strings and methods of fabrication thereof |

| US20160172190A1 (en) * | 2014-12-15 | 2016-06-16 | United Microelectronics Corp. | Gate oxide formation process |

| JP2016134614A (ja) * | 2015-01-22 | 2016-07-25 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| CN109071847B (zh) * | 2016-03-31 | 2022-02-01 | 株式会社Lg化学 | 用于制备阻挡膜的方法 |

| EP3291008A1 (en) * | 2016-09-06 | 2018-03-07 | ASML Netherlands B.V. | Method and apparatus to monitor a process apparatus |

| CN111627810B (zh) * | 2020-06-05 | 2022-10-11 | 合肥晶合集成电路股份有限公司 | 一种半导体结构及其制造方法 |

| WO2022006008A1 (en) | 2020-06-29 | 2022-01-06 | Applied Materials, Inc. | Control of steam generation for chemical mechanical polishing |

| KR102497494B1 (ko) * | 2021-06-03 | 2023-02-08 | 주식회사 기가레인 | 기판 배치 유닛 |

| KR102461496B1 (ko) * | 2021-06-03 | 2022-11-03 | 주식회사 기가레인 | 기판 배치 유닛 |

| CN116759325B (zh) * | 2023-08-23 | 2023-11-03 | 江苏卓胜微电子股份有限公司 | 用于监控离子注入剂量的阻值监控方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001156059A (ja) * | 1999-09-16 | 2001-06-08 | Matsushita Electronics Industry Corp | 絶縁膜の形成方法および半導体装置の製造方法 |

| JP2005072358A (ja) * | 2003-08-26 | 2005-03-17 | Seiko Epson Corp | 半導体装置の製造方法 |

| JP2008053535A (ja) * | 2006-08-25 | 2008-03-06 | Toshiba Corp | 半導体装置の製造方法及び不揮発性記憶装置の製造方法 |

| WO2009093760A1 (ja) * | 2008-01-24 | 2009-07-30 | Tokyo Electron Limited | シリコン酸化膜の形成方法、記憶媒体、および、プラズマ処理装置 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004153037A (ja) * | 2002-10-31 | 2004-05-27 | Renesas Technology Corp | 半導体装置の製造方法 |

| TW200629421A (en) * | 2005-01-12 | 2006-08-16 | Sanyo Electric Co | Method of producing semiconductor device |

| JP4989076B2 (ja) * | 2005-01-12 | 2012-08-01 | オンセミコンダクター・トレーディング・リミテッド | 半導体装置の製造方法 |

| JP4509864B2 (ja) * | 2005-05-30 | 2010-07-21 | 東京エレクトロン株式会社 | プラズマ処理方法およびプラズマ処理装置 |

| US7799649B2 (en) * | 2006-04-13 | 2010-09-21 | Texas Instruments Incorporated | Method for forming multi gate devices using a silicon oxide masking layer |

| KR101056199B1 (ko) * | 2006-08-28 | 2011-08-11 | 도쿄엘렉트론가부시키가이샤 | 플라즈마 산화 처리 방법 |

| JP5229711B2 (ja) * | 2006-12-25 | 2013-07-03 | 国立大学法人名古屋大学 | パターン形成方法、および半導体装置の製造方法 |

| JP5029089B2 (ja) * | 2007-03-26 | 2012-09-19 | 東京エレクトロン株式会社 | プラズマ処理装置用の載置台及びプラズマ処理装置 |

| TW201001543A (en) * | 2008-02-08 | 2010-01-01 | Tokyo Electron Ltd | Method for modifying insulating film with plasma |

-

2010

- 2010-09-16 JP JP2010207773A patent/JP2011097029A/ja active Pending

- 2010-09-29 TW TW099133059A patent/TW201125071A/zh unknown

- 2010-09-29 WO PCT/JP2010/066886 patent/WO2011040426A1/ja active Application Filing

- 2010-09-29 US US13/498,259 patent/US20120184107A1/en not_active Abandoned

- 2010-09-29 KR KR1020127011218A patent/KR101380094B1/ko active IP Right Grant

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001156059A (ja) * | 1999-09-16 | 2001-06-08 | Matsushita Electronics Industry Corp | 絶縁膜の形成方法および半導体装置の製造方法 |

| JP2005072358A (ja) * | 2003-08-26 | 2005-03-17 | Seiko Epson Corp | 半導体装置の製造方法 |

| JP2008053535A (ja) * | 2006-08-25 | 2008-03-06 | Toshiba Corp | 半導体装置の製造方法及び不揮発性記憶装置の製造方法 |

| WO2009093760A1 (ja) * | 2008-01-24 | 2009-07-30 | Tokyo Electron Limited | シリコン酸化膜の形成方法、記憶媒体、および、プラズマ処理装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW201125071A (en) | 2011-07-16 |

| KR20120069754A (ko) | 2012-06-28 |

| US20120184107A1 (en) | 2012-07-19 |

| JP2011097029A (ja) | 2011-05-12 |

| KR101380094B1 (ko) | 2014-04-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2011040426A1 (ja) | 半導体装置の製造方法 | |

| JP5073482B2 (ja) | シリコン酸化膜の製造方法、その制御プログラム、記憶媒体及びプラズマ処理装置 | |

| US8372761B2 (en) | Plasma oxidation processing method, plasma processing apparatus and storage medium | |

| KR101088233B1 (ko) | 반도체 장치의 제조 방법, 플라즈마 산화 처리 방법 및 플라즈마 처리 장치 | |

| TWI415187B (zh) | Selective plasma treatment | |

| JP5231233B2 (ja) | プラズマ酸化処理方法、プラズマ処理装置、及び、記憶媒体 | |

| KR101102690B1 (ko) | 실리콘 산화막의 형성 방법, 플라즈마 처리 장치 및 기억 매체 | |

| US20110017586A1 (en) | Method for forming silicon oxide film, storage medium, and plasma processing apparatus | |

| WO2006025363A1 (ja) | シリコン酸化膜の形成方法、半導体装置の製造方法およびコンピュータ記憶媒体 | |

| KR101070568B1 (ko) | 실리콘 산화막의 형성 방법, 플라즈마 처리 장치 및 기억 매체 | |

| JP5231232B2 (ja) | プラズマ酸化処理方法、プラズマ処理装置、及び、記憶媒体 | |

| JP5271702B2 (ja) | シリコン酸化膜の形成方法およびシリコン酸化膜の形成装置 | |

| WO2008041599A1 (fr) | Procédé d'oxydation de plasma, support de stockage, et appareil de traitement par plasma |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| 121 | Ep: the epo has been informed by wipo that ep was designated in this application |

Ref document number: 10820541 Country of ref document: EP Kind code of ref document: A1 |

|

| WWE | Wipo information: entry into national phase |

Ref document number: 13498259 Country of ref document: US |

|

| NENP | Non-entry into the national phase |

Ref country code: DE |

|

| ENP | Entry into the national phase |

Ref document number: 20127011218 Country of ref document: KR Kind code of ref document: A |

|

| 122 | Ep: pct application non-entry in european phase |

Ref document number: 10820541 Country of ref document: EP Kind code of ref document: A1 |