KR20200044930A - 에피택셜 실리콘 웨이퍼의 제조 방법, 에피택셜 실리콘 웨이퍼, 및 고체 촬상 소자의 제조 방법 - Google Patents

에피택셜 실리콘 웨이퍼의 제조 방법, 에피택셜 실리콘 웨이퍼, 및 고체 촬상 소자의 제조 방법 Download PDFInfo

- Publication number

- KR20200044930A KR20200044930A KR1020207009158A KR20207009158A KR20200044930A KR 20200044930 A KR20200044930 A KR 20200044930A KR 1020207009158 A KR1020207009158 A KR 1020207009158A KR 20207009158 A KR20207009158 A KR 20207009158A KR 20200044930 A KR20200044930 A KR 20200044930A

- Authority

- KR

- South Korea

- Prior art keywords

- silicon wafer

- epitaxial

- carbon

- hydrogen

- epitaxial silicon

- Prior art date

Links

- 229910052710 silicon Inorganic materials 0.000 title claims abstract description 177

- 239000010703 silicon Substances 0.000 title claims abstract description 177

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 title claims abstract description 173

- 238000003384 imaging method Methods 0.000 title claims abstract description 36

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 36

- 238000000034 method Methods 0.000 title claims description 36

- 150000002500 ions Chemical class 0.000 claims abstract description 148

- 229910052799 carbon Inorganic materials 0.000 claims abstract description 53

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims abstract description 52

- 239000001257 hydrogen Substances 0.000 claims abstract description 45

- 229910052739 hydrogen Inorganic materials 0.000 claims abstract description 45

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims abstract description 40

- 239000000470 constituent Substances 0.000 claims abstract description 11

- 125000004429 atom Chemical group 0.000 claims description 24

- 230000008569 process Effects 0.000 claims description 10

- 239000006104 solid solution Substances 0.000 claims description 7

- 150000002431 hydrogen Chemical class 0.000 claims description 5

- 238000004140 cleaning Methods 0.000 claims description 3

- 238000005247 gettering Methods 0.000 abstract description 20

- 230000007547 defect Effects 0.000 abstract description 19

- 230000001678 irradiating effect Effects 0.000 abstract description 5

- 235000012431 wafers Nutrition 0.000 description 122

- 239000010410 layer Substances 0.000 description 71

- 239000007789 gas Substances 0.000 description 33

- 239000002994 raw material Substances 0.000 description 22

- 230000007246 mechanism Effects 0.000 description 18

- 230000001133 acceleration Effects 0.000 description 16

- 238000005286 illumination Methods 0.000 description 15

- 230000000052 comparative effect Effects 0.000 description 11

- 229910001385 heavy metal Inorganic materials 0.000 description 10

- 238000010884 ion-beam technique Methods 0.000 description 10

- 230000015572 biosynthetic process Effects 0.000 description 9

- 239000002019 doping agent Substances 0.000 description 9

- 210000002381 plasma Anatomy 0.000 description 8

- 239000000463 material Substances 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- AFABGHUZZDYHJO-UHFFFAOYSA-N 2-Methylpentane Chemical compound CCCC(C)C AFABGHUZZDYHJO-UHFFFAOYSA-N 0.000 description 6

- 238000011109 contamination Methods 0.000 description 6

- 239000001301 oxygen Substances 0.000 description 6

- 229910052760 oxygen Inorganic materials 0.000 description 6

- 238000004949 mass spectrometry Methods 0.000 description 5

- -1 oxygen ions Chemical class 0.000 description 5

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 5

- 239000000758 substrate Substances 0.000 description 5

- BZHMBWZPUJHVEE-UHFFFAOYSA-N 2,4-dimethylpentane Chemical compound CC(C)CC(C)C BZHMBWZPUJHVEE-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 238000011156 evaluation Methods 0.000 description 4

- 238000000605 extraction Methods 0.000 description 4

- 239000002784 hot electron Substances 0.000 description 4

- RTZKZFJDLAIYFH-UHFFFAOYSA-N Diethyl ether Chemical compound CCOCC RTZKZFJDLAIYFH-UHFFFAOYSA-N 0.000 description 3

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 3

- 239000012159 carrier gas Substances 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- MROCJMGDEKINLD-UHFFFAOYSA-N dichlorosilane Chemical compound Cl[SiH2]Cl MROCJMGDEKINLD-UHFFFAOYSA-N 0.000 description 3

- 239000012634 fragment Substances 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 3

- 239000000178 monomer Substances 0.000 description 3

- WGECXQBGLLYSFP-UHFFFAOYSA-N (+-)-2,3-dimethyl-pentane Natural products CCC(C)C(C)C WGECXQBGLLYSFP-UHFFFAOYSA-N 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 230000007797 corrosion Effects 0.000 description 2

- 238000005260 corrosion Methods 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 239000002923 metal particle Substances 0.000 description 2

- 238000002360 preparation method Methods 0.000 description 2

- 239000000047 product Substances 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- XDTMQSROBMDMFD-UHFFFAOYSA-N Cyclohexane Chemical compound C1CCCCC1 XDTMQSROBMDMFD-UHFFFAOYSA-N 0.000 description 1

- DKGAVHZHDRPRBM-UHFFFAOYSA-N Tert-Butanol Chemical compound CC(C)(C)O DKGAVHZHDRPRBM-UHFFFAOYSA-N 0.000 description 1

- DHXVGJBLRPWPCS-UHFFFAOYSA-N Tetrahydropyran Chemical compound C1CCOCC1 DHXVGJBLRPWPCS-UHFFFAOYSA-N 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 150000001793 charged compounds Chemical class 0.000 description 1

- 239000007795 chemical reaction product Substances 0.000 description 1

- 239000000460 chlorine Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 229940032122 claris Drugs 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 150000002430 hydrocarbons Chemical class 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910000073 phosphorus hydride Inorganic materials 0.000 description 1

- 238000001556 precipitation Methods 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 238000002407 reforming Methods 0.000 description 1

- 239000013049 sediment Substances 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 230000003595 spectral effect Effects 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- IHCDKJZZFOUARO-UHFFFAOYSA-M sulfacetamide sodium Chemical compound O.[Na+].CC(=O)[N-]S(=O)(=O)C1=CC=C(N)C=C1 IHCDKJZZFOUARO-UHFFFAOYSA-M 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- ZDHXKXAHOVTTAH-UHFFFAOYSA-N trichlorosilane Chemical compound Cl[SiH](Cl)Cl ZDHXKXAHOVTTAH-UHFFFAOYSA-N 0.000 description 1

- 239000005052 trichlorosilane Substances 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 238000004857 zone melting Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/322—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to modify their internal properties, e.g. to produce internal imperfections

- H01L21/3221—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to modify their internal properties, e.g. to produce internal imperfections of silicon bodies, e.g. for gettering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14636—Interconnect structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/36—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the concentration or distribution of impurities in the bulk material

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/24—Deposition of silicon only

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B29/00—Single crystals or homogeneous polycrystalline material with defined structure characterised by the material or by their shape

- C30B29/02—Elements

- C30B29/06—Silicon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02041—Cleaning

- H01L21/02043—Cleaning before device manufacture, i.e. Begin-Of-Line process

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02373—Group 14 semiconducting materials

- H01L21/02381—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02496—Layer structure

- H01L21/0251—Graded layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02532—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02658—Pretreatments

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26566—Bombardment with radiation with high-energy radiation producing ion implantation of a cluster, e.g. using a gas cluster ion beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1464—Back illuminated imager structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/14687—Wafer level processing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/14698—Post-treatment for the devices, e.g. annealing, impurity-gettering, shor-circuit elimination, recrystallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/1804—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof comprising only elements of Group IV of the Periodic Table

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02689—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using particle beams

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- High Energy & Nuclear Physics (AREA)

- Materials Engineering (AREA)

- Electromagnetism (AREA)

- Metallurgy (AREA)

- Health & Medical Sciences (AREA)

- Toxicology (AREA)

- Organic Chemistry (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Ceramic Engineering (AREA)

- Inorganic Chemistry (AREA)

- Mechanical Engineering (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Recrystallisation Techniques (AREA)

Abstract

높은 게터링 능력을 가지면서, 이면조사형(裏面照射型) 고체 촬상 소자에 있어서의 화이트 스팟 결함을 보다 억제할 수 있는 에피택셜 실리콘 웨이퍼를 얻는 것이 가능한 에피택셜 실리콘 웨이퍼의 제조 방법을 제공한다. 본 발명은, 실리콘 웨이퍼의 표면(10A)에, 버누스형 이온원 또는 IHC형 이온원을 이용하여 생성한 CnHm(n=1 또는 2, m=1, 2, 3, 4 또는 5)의 클러스터 이온(12)을 조사(照射)하여, 실리콘 웨이퍼(10) 내에, 클러스터 이온(12)의 구성 원소의 탄소 및 수소가 고용(固溶)되어 이루어지는 개질층(14)을 형성하는 제1 공정과, 이후, 표면(10A) 상에 실리콘 에피택셜층(16)을 형성하는 제2 공정을 갖고, 제1 공정에서는, 개질층(14)에 있어서의 탄소 및 수소의 농도 프로파일의 피크를, 표면(10A)으로부터 150㎚ 초과 2000㎚ 이내에 각각 위치시키는 것을 특징으로 한다.

Description

[0001] 본 발명은, 에피택셜 실리콘 웨이퍼의 제조 방법, 에피택셜 실리콘 웨이퍼, 및 고체 촬상 소자의 제조 방법에 관한 것이다.

[0002] 반도체 디바이스의 특성을 열화(劣化)시키는 요인으로서, 금속 오염을 들 수 있다. 예컨대, 이면조사형(裏面照射型) 고체 촬상 소자에서는, 상기 소자의 기판이 되는 에피텍셜 실리콘 웨이퍼에 혼입(混入)된 금속이, 고체 촬상 소자의 암전류(暗電流)를 증가시키는 요인이 되어, 화이트 스팟(white spot) 결함이라 불리는 결함을 발생시킨다. 이면조사형 고체 촬상 소자는, 배선층 등을 센서부보다 하층에 배치함으로써, 외부로부터의 광을 센서에 직접 받아들여, 암소(暗所) 등에서도 보다 선명한 화상이나 동영상을 촬영할 수 있기 때문에, 최근, 디지털 비디오 카메라나 스마트폰 등의 휴대전화에 널리 이용되고 있다. 이 때문에, 화이트 스팟 결함을 최대한 줄일 것이 요망되고 있다.

[0003] 실리콘 웨이퍼에 대한 금속의 혼입은, 주로 에피텍셜 실리콘 웨이퍼의 제조 공정 및 이면조사형 고체 촬상 소자의 제조 공정에서 발생한다. 전자(前者)의 에피텍셜 실리콘 웨이퍼의 제조 공정에 있어서의 금속 오염은, 에피택셜 성장로(爐)의 구성재(構成材)로부터의 중금속 파티클에 의한 것, 혹은, 에피택셜 성장 시의 노내(爐內) 가스로서 염소계 가스를 이용하기 때문에, 그 배관 재료가 금속 부식하여 발생하는 중금속 파티클에 의한 것 등을 고려할 수 있다. 최근, 이러한 금속 오염은, 에피택셜 성장로의 구성재를 내부식성(耐腐食性)이 우수한 재료로 교환하는 등에 의해 개선되고 있지만, 충분하지는 않다. 한편, 후자(後者)의 이면조사형 고체 촬상 소자의 제조 공정에서는, 이온 주입, 확산 및 산화 열처리 등의 각 처리 중에 있어서, 에피텍셜 실리콘 웨이퍼의 중금속 오염이 염려된다.

[0004] 이 때문에, 일반적으로는, 에피텍셜 실리콘 웨이퍼에 금속을 포획하기 위한 게터링층을 형성함으로써, 에피텍셜 실리콘 웨이퍼에 대한 금속 오염을 회피하고 있다. 예컨대, 특허문헌 1에는, 실리콘 웨이퍼에 탄소를 포함하는 클러스터 이온을 조사하여, 해당 실리콘 웨이퍼의 표면에, 탄소가 고용(固溶)되어 이루어지는 개질층을 형성하는 제1 공정과, 상기 개질층 상에 실리콘 에피택셜층을 형성하는 제2 공정을 갖는 것을 특징으로 하는 에피택셜 실리콘 웨이퍼의 제조 방법이 기재되어 있다. 여기서, 제1 공정에서는, 근접 게터링을 가능하게 하기 위해, 실리콘 웨이퍼의 표면 근방에 개질층을 형성하는 것이 바람직하다고 되어 있다. 구체적으로는, 실리콘 웨이퍼의 표면으로부터의 깊이가 150㎚ 이하인 범위 내에, 개질층에 있어서의 탄소의 깊이 방향의 농도 프로파일의 피크를 위치시키는 것이 바람직하다고 되어 있다.

[0006] 특허문헌 1에 의하면, 클러스터 이온을 조사함으로써 형성한 개질층이, 모노머 이온(싱글 이온)을 주입함으로써 형성한 이온 주입층보다 높은 게터링 능력을 가진다. 이러한 높은 게터링 능력에 의해, 이면조사형 고체 촬상 소자의 화이트 스팟 결함을 저감시킬 수 있는 것이라고 생각되고 있다. 그러나, 본 발명자들이 이후 더욱 검토한 바, 추가적인 개선의 여지가 있음이 판명되었다.

[0007] 본 발명은, 상기의 과제를 감안하여, 높은 게터링 능력을 가지면서, 이면조사형 고체 촬상 소자에 있어서의 화이트 스팟 결함을 보다 억제할 수 있는 에피택셜 실리콘 웨이퍼를 얻는 것이 가능한 에피택셜 실리콘 웨이퍼의 제조 방법을 제공하는 것을 목적으로 한다. 또한, 본 발명은, 높은 게터링 능력을 가지면서, 이면조사형 고체 촬상 소자에 있어서의 화이트 스팟 결함을 보다 억제할 수 있는 에피택셜 실리콘 웨이퍼를 제공하는 것을 목적으로 한다.

[0008] 본 발명자들은, 상기의 과제를 해결하기 위해, 이면조사형 고체 촬상 소자의 제조 공정에 대해 검토하였다. 이면조사형 고체 촬상 소자는, 예컨대 도 3에 나타낸 공정을 거쳐서 제작된다. 우선, 이면조사형 고체 촬상 소자의 기판이 되는 에피택셜 실리콘 웨이퍼를 준비한다(도 3의 (A)). 이 실리콘 에피택셜 웨이퍼는, p+ 실리콘 웨이퍼와, 상기 p+ 실리콘 웨이퍼의 표층에 형성된, 클러스터 이온의 구성 원소인 탄소가 고용되어 이루어지는 개질층(게터링층)과, 상기 개질층 상에 형성된 p- 실리콘 에피택셜층을 가진다. 다음으로, p- 실리콘 에피택셜층에 포토다이오드 등의 디바이스를 형성한 후에, p- 실리콘 에피택셜층 상에 배선층을 형성한다(도 3의 (B)). 다음으로, 에피택셜 실리콘 웨이퍼를 어닐링하여, 기판 내에 확산된 중금속을 개질층으로 끌어 들여서, 디바이스를 형성한 영역(디바이스 형성 영역)의 중금속 농도를 저감시킨다(도 3의 (C)). 다음으로, 에피택셜 실리콘 웨이퍼의 표리면(表裏面)을 반전시킨 후에, 지지 기판과 에피택셜 실리콘 웨이퍼와의 사이에 배선층이 위치하도록, 지지 기판과 에피택셜 실리콘 웨이퍼를 접합한다(도 3의 (D)). 다음으로, p+ 실리콘 웨이퍼를 연삭하여 제거한 후에, 디바이스 형성 영역(두께: 3㎛ 정도)이 남도록, p- 실리콘 에피택셜층을 박막화(薄膜化)한다(도 3의 (E)). 이상의 공정을 거쳐서, 이면조사형 고체 촬상 소자가 완성된다.

[0009] 이면조사형 고체 촬상 소자에서는, p- 실리콘 에피택셜층이 최종적으로 박막화되므로, 박막화되기 전의 p- 실리콘 에피택셜층은, 표면조사형(表面照射型) 고체 촬상 소자에 있어서의 10㎛ 정도와 비교하여, 6㎛ 정도로 얇게 설계되어 있다. 이 때문에, 종래와 같이 실리콘 웨이퍼의 표면 근방에 개질층이 존재하면, 개질층에 있어서의 탄소의 피크는, p- 실리콘 에피택셜층에 형성된 디바이스 형성 영역의 근처에 위치하게 된다. 이와 같이 탄소의 피크 위치가 디바이스 형성 영역에 가까우면, 도 3의 (C)에 나타낸 어닐링 후의 중금속의 깊이 방향의 농도 프로파일은, 개질층에 가까워짐에 따라 높은 농도를 나타내는데, 그 농도 프로파일의 끝자락(꼬리(tail))은 디바이스 형성 영역으로까지 확산된다. 이에 기인하여 이면조사형 고체 촬상 소자의 암전류가 증가하여, 화이트 스팟 결함이 생기는 경우가 있음이 판명되었다.

[0010] 따라서, 본 발명자들은, 추가적인 검토를 진행한 바, 모노머 이온을 생성하기 위한 장치로서 종래부터 이용되고 있는 버누스형(burnous-type) 이온원(ion source) 또는 IHC형 이온원을 이용하여, CnHm(n=1 또는 2, m=1, 2, 3, 4 또는 5)의 클러스터 이온을 생성하면, 종래와 동일한 조사 에너지로 비교하였을 경우에, 개질층에 있어서의 클러스터 이온의 구성 원소의 깊이 방향의 농도 프로파일의 피크를 실리콘 웨이퍼의 표면으로부터 보다 깊은 위치(150㎚를 초과하는 위치)에 형성할 수 있고, 그 결과, 높은 게터링 능력을 가지면서, 이면조사형 고체 촬상 소자에 있어서의 화이트 스팟 결함을 보다 억제할 수 있는 에피택셜 실리콘 웨이퍼를 얻을 수 있음을 알게 되었다.

[0011] 본 발명은, 상기의 지견(知見)에 근거하여 완성된 것이며, 그 요지 구성은 이하와 같다.

(1) 실리콘 웨이퍼의 표면에, 버누스형 이온원 또는 IHC형 이온원을 이용하여 생성한 CnHm(n=1 또는 2, m=1, 2, 3, 4 또는 5)의 클러스터 이온을 조사하여, 상기 실리콘 웨이퍼 내에, 상기 클러스터 이온의 구성 원소인 탄소 및 수소가 고용되어 이루어지는 개질층을 형성하는 제1 공정과,

상기 제1 공정 후에, 상기 표면 상에 실리콘 에피택셜층을 형성하는 제2 공정을 갖고,

상기 제1 공정에서는, 상기 개질층에 있어서의 상기 탄소 및 상기 수소의 깊이 방향의 농도 프로파일의 피크를, 상기 실리콘 웨이퍼의 상기 표면으로부터의 깊이가 150㎚ 초과 2000㎚ 이내인 범위에 각각 위치시키는 것을 특징으로 하는 에피택셜 실리콘 웨이퍼의 제조 방법.

[0012] (2) 상기 제1 공정에서는, 상기 클러스터 이온을 170㎂ 이상의 빔 전류치로 조사하는, 상기 (1)에 기재된 에피택셜 실리콘 웨이퍼의 제조 방법.

[0013] (3) 상기 제1 공정에서는, 상기 실리콘 웨이퍼의 틸트각 및 트위스트각이 모두 0°가 되도록, 상기 클러스터 이온의 조사를 행하는, 상기 (1) 또는 (2)에 기재된 에피택셜 실리콘 웨이퍼의 제조 방법.

[0014] (4) 상기 제1 공정과 상기 제2 공정의 사이에, 상기 실리콘 웨이퍼의 표면을 세정하는 공정을 더 갖는, 상기 (1)∼(3) 중 어느 하나에 기재된 에피택셜 실리콘 웨이퍼의 제조 방법.

[0015] (5) 실리콘 웨이퍼와, 상기 실리콘 웨이퍼 내에 형성된, 탄소 및 수소가 고용되어 이루어지는 개질층과, 상기 개질층 상에 형성된 실리콘 에피택셜층을 갖고,

상기 실리콘 웨이퍼의 표면으로부터의 깊이가 150㎚ 초과 2000㎚ 이내인 범위에, 상기 개질층에 있어서의 상기 탄소 및 상기 수소의 깊이 방향의 농도 프로파일의 피크가 각각 위치하는 것을 특징으로 하는 에피택셜 실리콘 웨이퍼.

[0016] (6) 상기 탄소의 깊이 방향의 농도 프로파일의 피크 위치와 상기 수소의 깊이 방향의 농도 프로파일의 피크 위치의 차(差)가 1000㎚ 이내인, 상기 (5)에 기재된 에피택셜 실리콘 웨이퍼.

[0017] (7) 상기 탄소의 깊이 방향의 농도 프로파일의 피크 농도와 상기 수소의 깊이 방향의 농도 프로파일의 피크 농도가 모두 1×1016atoms/㎝3 이상인, 상기 (5) 또는 (6)에 기재된 에피택셜 실리콘 웨이퍼.

[0018] (8) 상기 (1)∼(4) 중 어느 하나에 기재된 에피택셜 실리콘 웨이퍼의 제조 방법으로 제조된 에피택셜 실리콘 웨이퍼 또는 상기 (5)∼(7) 중 어느 하나에 기재된 에피택셜 실리콘 웨이퍼의 실리콘 에피택셜층에, 고체 촬상 소자를 형성하는 것을 특징으로 하는 고체 촬상 소자의 제조 방법.

[0019] 본 발명에 의하면, 높은 게터링 능력을 가지면서, 이면조사형 고체 촬상 소자에 있어서의 화이트 스팟 결함을 보다 억제할 수 있는 에피택셜 실리콘 웨이퍼를 얻을 수 있다.

[0020] 도 1은, 본 발명의 하나의 실시형태에 따른 에피택셜 실리콘 웨이퍼(100)의 제조 방법을 설명하는 모식적인 단면도이다.

도 2의 (A)는, 본 발명의 하나의 실시형태에서 이용할 수 있는 이온 조사 장치(70)의 개략도이며, (B)는, 이온원(20)으로서 버누스형 이온원을 이용하는 경우의 개략도이며, (C)는, 이온원(20)으로서 IHC형 이온원을 이용하는 경우의 개략도이다.

도 3은, 이면조사형 고체 촬상 소자의 제조 방법을 설명하는 모식적인 단면도이다.

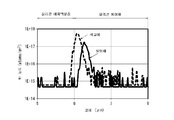

도 4는, IHC형 이온원을 이용하여 생성한 복수 종류의 이온의 매스(mass)값에 대한 빔 전류치를 나타낸 그래프이다.

도 5의 (A)는, 발명예에 의한 에피택셜 실리콘 웨이퍼(100)의 깊이 방향의 탄소 및 수소의 농도 프로파일을 나타낸 그래프이며, (B)는, (A)에 나타낸 피크 위치 근방에서의 확대도이다.

도 6의 (A)는, 비교예에 의한 에피택셜 실리콘 웨이퍼의 깊이 방향의 탄소 및 수소의 농도 프로파일을 나타낸 그래프이며, (B)는, (A)에 나타낸 피크 위치 근방에서의 확대도이다.

도 7은, 발명예 및 비교예에 대해, 에피택셜 실리콘 웨이퍼의 깊이 방향의 Ni의 농도 프로파일을 나타낸 그래프이다.

도 2의 (A)는, 본 발명의 하나의 실시형태에서 이용할 수 있는 이온 조사 장치(70)의 개략도이며, (B)는, 이온원(20)으로서 버누스형 이온원을 이용하는 경우의 개략도이며, (C)는, 이온원(20)으로서 IHC형 이온원을 이용하는 경우의 개략도이다.

도 3은, 이면조사형 고체 촬상 소자의 제조 방법을 설명하는 모식적인 단면도이다.

도 4는, IHC형 이온원을 이용하여 생성한 복수 종류의 이온의 매스(mass)값에 대한 빔 전류치를 나타낸 그래프이다.

도 5의 (A)는, 발명예에 의한 에피택셜 실리콘 웨이퍼(100)의 깊이 방향의 탄소 및 수소의 농도 프로파일을 나타낸 그래프이며, (B)는, (A)에 나타낸 피크 위치 근방에서의 확대도이다.

도 6의 (A)는, 비교예에 의한 에피택셜 실리콘 웨이퍼의 깊이 방향의 탄소 및 수소의 농도 프로파일을 나타낸 그래프이며, (B)는, (A)에 나타낸 피크 위치 근방에서의 확대도이다.

도 7은, 발명예 및 비교예에 대해, 에피택셜 실리콘 웨이퍼의 깊이 방향의 Ni의 농도 프로파일을 나타낸 그래프이다.

[0021] 이하에서는, 도면을 참조하면서 본 발명의 실시형태를 상세히 설명한다. 또한, 도 1에서는 설명의 편의상, 실제의 두께의 비율과는 달리, 실리콘 웨이퍼(10)에 대해 개질층(14) 및 실리콘 에피택셜층(16)의 두께를 과장하여 나타낸다.

[0022] (에피택셜 실리콘 웨이퍼의 제조 방법)

도 1을 참조하여, 본 발명의 하나의 실시형태에 따른 에피택셜 실리콘 웨이퍼(100)의 제조 방법을 설명한다. 본 실시형태에서는, 제1 공정에서, 실리콘 웨이퍼의 표면(10A)에, 버누스형 이온원 또는 IHC형 이온원을 이용하여 생성한 CnHm(n=1 또는 2, m=1, 2, 3, 4 또는 5)의 클러스터 이온(12)을 조사하여, 실리콘 웨이퍼(10) 내에, 클러스터 이온(12)의 구성 원소인 탄소 및 수소가 고용되어 이루어지는 개질층(14)을 형성한다(도 1의 (A), (B)). 이때, 개질층(14)에 있어서의 탄소 및 수소의 깊이 방향의 농도 프로파일의 피크를, 실리콘 웨이퍼의 표면(10A)(즉, 클러스터 이온(12)을 조사한 측의 표면)으로부터의 깊이가 150㎚ 초과 2000㎚ 이내인 범위에 각각 위치시킨다. 다음으로, 제2 공정에서, 해당 표면(10A) 상에 실리콘 에피택셜층(16)을 형성한다(도 1의 (B), (C)). 도 1의 (C)는, 상기 제조 방법에 의해 얻어진 에피택셜 실리콘 웨이퍼(100)의 모식적인 단면도이다. 이하에서는, 각 공정에 대해 상세히 설명한다.

[0023] [제1 공정]

도 1의 (A), (B)를 참조하여, 제1 공정에서는, 실리콘 웨이퍼의 표면(10A)에, 버누스형 이온원 또는 IHC형 이온원을 이용하여 생성한 CnHm(n=1, 2, m=1, 2, 3, 4 또는 5)의 클러스터 이온(12)을 조사한다. 실리콘 웨이퍼(10) 내에 주입된 클러스터 이온(12)은, 순간적으로 1350∼1400℃ 정도의 고온 상태가 되어 융해되며, 이후, 급속히 냉각되고, 실리콘 웨이퍼(10)의 소정의 깊이 위치에서, 클러스터 이온(12)의 구성 원소인 탄소 및 수소가 재(再)결정화된다. 이에 의해, 국소적으로 고농도로 고용되어 이루어지는 개질층(14)이 형성된다. 또한, 실리콘 웨이퍼(10)로서는, 초크랄스키법(CZ법)이나 부유 대역 용융법(FZ법)에 의해 육성된 단결정 실리콘 잉곳을 실톱(wire saw) 등으로 슬라이스하여 얻은 단결정 실리콘 웨이퍼를 사용할 수 있다. 혹은, 이러한 단결정 실리콘 웨이퍼에 대해, 임의의 불순물을 첨가하여, n형 또는 p형 실리콘 웨이퍼로 한 것을 이용해도 되며, 탄소 및/또는 질소를 첨가한 것을 이용해도 된다.

[0024] 제1 공정에서 형성된 개질층(14)은, 게터링 사이트로서 작용하며, 그 이유는 이하와 같이 추측된다. 즉, 실리콘 웨이퍼(10)에 주입된 탄소 및 수소는, 실리콘 단결정의 치환 위치·격자 사이에 국소적으로 고밀도로 존재한다. 그리고, 실리콘 단결정의 평형 농도 이상으로 탄소 및 수소가 고용되면, 중금속의 고용도(固溶度)(천이 금속의 포화용해도)가 매우 증가됨이 실험적으로 확인되고 있다. 즉, 평형 농도 이상으로 고용된 탄소 및 수소에 의해 중금속의 고용도가 증가되고, 이에 따라 중금속에 대한 포획률이 현저히 증가하는 것이라고 생각된다.

[0025] 여기서, 본 발명은, 버누스형 이온원 또는 IHC형 이온원을 이용하여 생성한 CnHm(n=1 또는 2, m=1, 2, 3, 4 또는 5)의 클러스터 이온을 조사하여, 개질층(14)에 있어서의 탄소 및 수소의 깊이 방향의 농도 프로파일의 피크를, 실리콘 웨이퍼의 표면(10A)으로부터의 깊이가 150㎚ 초과 2000㎚ 이내인 범위에 각각 위치시키는 것이 중요하다. 이하에서는, 버누스형 이온원 및 IHC형 이온원, 및 이들 이온원을 구비하는 이온 조사 장치(70)의 한 형태를, 도 2의 (A)∼(C)를 참조하여 상세히 설명한다. 참고로, 본 명세서에 있어서 「클러스터 이온」이란, 2종 이상의 원자가 복수 집합하여 덩어리가 된 클러스터이며, 양(陽) 또는 음(陰)의 전하를 갖는 것을 의미한다. 또한, 본 명세서에 있어서 「클러스터 사이즈」란, 1개의 클러스터를 구성하는 원자의 개수를 의미한다.

[0026] 도 2의 (A)를 참조하여, 이온 조사 장치(70)는, 이온원(20)과, 전단(前段) 가속 기구(30)와, 질량 분석 기구(40)와, 후단(後段) 가속 기구(50)와, 조사(照射) 챔버(60)를 가진다. 우선, 이온원(20)에서 클러스터 이온을 생성하고, 이것을 이온 빔으로서 추출(取出)하여, 전단 가속 기구(30)로 보낸다. 그런 다음, 전단 가속 기구(30)에서, 클러스터 이온을 가속(전단 가속)시켜, 이온 빔으로서 추출하여, 질량 분석 기구(40)로 보낸다. 그런 다음, 질량 분석 기구(40)에서, 자기장(磁場)에 의한 질량 분석을 실시하여, 소정의 질량을 갖는 클러스터 이온만을 이온 빔으로서 추출하여, 후단 가속 기구(50)로 보낸다. 그런 다음, 후단 가속 기구(50)에서, 클러스터 이온을 더욱 가속(후단 가속)시켜, 이온 빔으로서 추출하여, 조사 챔버(60)로 보낸다. 그런 다음, 조사 챔버(60)에서, 웨이퍼 고정대에 재치(載置: 올려 놓음) 및 고정된 실리콘 웨이퍼(10)에 대해, 이온 빔을 조사한다. 참고로, 이온 빔이란, 클러스터 이온이 집속(集束)되어, 다발 형상(束狀)으로 병진(竝進)하는 빔이며, 도 2의 (A)에 있어서의 화살표는 이온 빔을 나타낸다.

[0027] 도 2의 (A)에 나타낸 이온원(20)으로서는, 버누스형 이온원 또는 IHC(Indirectly Heated Cathode)형 이온원을 이용할 수 있다. 이하에서는, 도 2의 (B), (C)를 참조하여, 버누스형 이온원 또는 IHC형 이온원을 이용하여, 클러스터 이온을 생성하는 방법을 각각 설명한다.

[0028] 도 2의 (B)를 참조하여, 버누스형 이온원(20)은, 아크 챔버(21)와, 원료 가스 도입구(22)와, 이온 추출구(23)와, U자형의 필라멘트(24)와, 리플렉터(25)와, 전류 전압 인가(印加) 장치(26)와, 자기장 발생 장치(27)와, 진공 펌프(28)를 가진다. 아크 챔버(21)는, 이온 생성 챔버를 구획하는 챔버이다. 원료 가스 도입구(22)는, 아크 챔버(21)에 설치되어 있으며, 그곳으로부터 원료 가스를 아크 챔버(21) 내로 도입한다. 이온 추출구(23)는, 아크 챔버(21)에, 바람직하게는 원료 가스 도입구(22)에 대향(對向)하는 위치에 설치되어 있으며, 아크 챔버(21) 내에서 생성된 클러스터 이온은, 전단 가속 기구(30)에 의해 가속된다. 필라멘트(24) 및 리플렉터(25)는, 아크 챔버(21) 내에 서로 대향하는 위치에 설치되어 있다. 전류 전압 인가 장치(26)는, 아크 챔버(21)의 외부에 설치되어 있으며, 아크 챔버(21)와 필라멘트(24)에 접속되어 있다. 자기장 발생 장치(27)는, 아크 챔버(21)의 외부에 서로 대향되도록 설치되어 있다. 진공 펌프(28)는, 아크 챔버(21)에 접속되어 있다.

[0029] 버누스형 이온원(20)에서는, 이하의 방법에 의해 클러스터 이온을 생성한다. 우선, 진공 펌프(28)에 의해, 아크 챔버(21) 내를 감압(減壓)한다. 그런 다음, 원료 가스 도입구(22)로부터 아크 챔버(21) 내로 원료 가스를 도입한다. 그런 다음, 전류 전압 인가 장치(26)에 의해, 아크 챔버(21)에 양의 전압을 인가하는 동시에, 필라멘트(24)에 음의 전압을 인가한다. 그런 다음, 자기장 발생 장치(27)에 의해, 아크 챔버(21) 내에 자기장을 발생시킨다. 그런 다음, 전류 전압 인가 장치(26)에 의해 필라멘트(24)에 전류를 흘려서, 필라멘트(24)를 가열한다. 이에 의해, 필라멘트(24)로부터 방출된 열전자(e-)가, 전기장(電場)과 자기장의 영향을 받아, 필라멘트(24)와 리플렉터(25)와의 사이를 왕복 운동하여, 원료 가스와 높은 확률로 충돌한다. 그 결과, 원료 가스가 높은 효율로 전리(電離)되어, 밀도가 높은 원료 가스의 플라즈마가 생성된다. 그런 다음, 생성된 플라즈마에 포함되는 원료 가스의 클러스터 이온을 이온 빔으로서 이온 추출구(23)로부터 추출한다.

[0030] 도 2의 (C)를 참조하면, IHC형 이온원은, 버누스형 이온원과는 달리, 필라멘트(24)가, 플라즈마에 직접 노출되지 않도록 아크 챔버(21)의 외부에 설치되어 있다. 또한, 캐소드(29)가 필라멘트(24)에 대향되도록, 아크 챔버(21)의 벽에 설치되어 있고, 캐소드(29)에도 전류 전압 인가 장치(26)가 접속되어 있다. 또한 기타의 구성은, 도 2의 (B)를 참조하여 설명한 버누스형 이온원과 마찬가지이다.

[0031] IHC형 이온원(20)에서는, 이하의 방법에 의해 클러스터 이온을 생성한다. 우선, 진공 펌프(28)에 의해, 아크 챔버(21) 내를 감압한다. 그런 다음, 원료 가스 도입구(22)로부터 아크 챔버(21) 내로 원료 가스를 도입한다. 그런 다음, 전류 전압 인가 장치(26)에 의해, 아크 챔버(21)와 필라멘트(24)에 양의 전압을 인가하는 동시에, 캐소드(29)에 음의 전압을 인가한다. 그런 다음, 자기장 발생 장치(27)에 의해, 아크 챔버(21) 내에 자기장을 발생시킨다. 그런 다음, 전류 전압 인가 장치(26)에 의해 필라멘트(24)에 전류를 흘려서, 필라멘트(24)를 가열한다. 이에 의해, 필라멘트(24)로부터 방출된 열전자(e-)가, 캐소드(29)에 충돌하여, 캐소드(29)를 가열시킨다. 그러면, 캐소드(29)로부터 추가적인 열전자(e-)가 발생하고, 이 열전자(e-)가 전기장과 자기장의 영향을 받아, 캐소드(29)와 리플렉터(25) 사이를 왕복 운동하여, 원료 가스와 높은 확률로 충돌한다. 그 결과, 원료 가스가 높은 효율로 전리되어, 밀도가 높은 원료 가스의 플라즈마가 생성된다. 그런 다음, 생성된 플라즈마에 포함되는 원료 가스의 클러스터 이온을 이온 빔으로서 이온 추출구(23)로부터 추출한다.

[0032] 또한, IHC형 이온원은, 버누스형 이온원에 비해, 고밀도의 플라즈마 형성에 대해 제어성이 좋기 때문에, 높은 빔 전류치를 확보하기가 용이하며, 또한, 필라멘트(24)가 직접 플라즈마에 노출되지 않기 때문에 수명이 길다.

[0033] 원료 가스는, 2-메틸펜탄이나 2,4-디메틸펜탄 등을 들 수 있다. 2-메틸펜탄이나 2,4-디메틸펜탄은, 분자 구조 중에 CH계를 가지고 있어, 이온원(20)에 있어서의 열전자(e-)에 의해 C=C 결합이 절단된다. 그 결과, CnHm(n=1 또는 2, m=1, 2, 3, 4 또는 5)와 같은 클러스터 사이즈가 작은 클러스터 이온이 얻어진다. 제1 공정에서는, CnHm(n=1 또는 2, m=1, 2, 3, 4 또는 5)의 클러스터 이온을 단독으로, 또는 2종 이상을 조합하여 조사해도 되지만, CH3를 조사하는 것이 특히 바람직하다. CH3는, 탄소에 대한 수소의 농도비가 커서, 보다 많은 수소를 주입할 수 있으므로, 패시베이션 효과에 의해 계면 준위에 기인하는 화이트 스팟 결함을 보다 억제할 수 있기 때문이다. 또한, 이러한 특정 종류의 클러스터 이온은, 도 2의 (A)에 나타낸 질량 분석 기구(40)에서, 공지 또는 임의의 방법으로 질량 분석을 행함으로써 추출할 수 있다.

[0034] 또한, 원료 가스로서, 디에틸에테르나 2-프로판올이나 2-메틸-2-프로판올이나 테트라히드로피란과 같이 산소를 포함하는 가스를 이용해도 된다. 산소를 포함하면, 아크 챔버(21) 내부나 필라멘트(24)에 퇴적된 탄소에 기인하는 퇴적물이 산소 이온에 의해 스퍼터링(sputtering)되므로, 이온원의 수명과 성능을 향상시킬 수 있기 때문이다. 또한, 산소에 대한 탄소의 조성비는 2배 이상으로 하는 것이 바람직하다. 예컨대, 탄소와 산소의 조성비가 1:1과 같이 산소의 비율이 높으면, 산소 이온이 필라멘트(24)를 과잉되게 스퍼터링해 버려, 열전자가 발생되기 어려워질 우려가 있기 때문이다.

[0035] 아크 챔버(21) 내의 압력은 5.0×10-2Pa 이하로 하는 것이 바람직하다.

[0036] 아크 챔버(21) 내의 전압(아크 전압)은 45V 이상 90V 이하로 하는 것이 바람직하며, 아크 챔버(21) 내의 전류(아크 전류)는 100mA 이상 5000mA 이하로 하는 것이 바람직하다. 이러한 전압 및 전류의 범위이면, 170㎂ 이상의 빔 전류를 실현할 수 있다.

[0037] 자기장 발생 장치(27)에 의해 발생시키는 외부 자기장은 0.5A/m 이상 1.5A/m 이하로 하는 것이 바람직하다.

[0038] 원료 가스의 유량은, 3cc/min 이상 5cc/min 이하로 하는 것이 바람직하다. 3cc/min 이상이면, CnHm(n=1 또는 2, m=1, 2, 3, 4 또는 5)과 같은 클러스터 사이즈가 작은 클러스터 이온이라 하더라도 170㎂ 이상의 빔 전류치를 확보할 수 있고, 5cc/min 이하이면, 탄화 퇴적물의 영향으로 인한 빔 전류치 저하의 우려가 적기 때문이다.

[0039] 또한, 필라멘트(24)의 재료는, 일반적인 텅스텐을 이용할 수 있다. 원료 가스에 포함되고, 또한 전리되어 있지 않은 탄화수소 화합물과 필라멘트(24) 재료와의 반응 생성물이 필라멘트(24)에 형성되는 것을 억제함으로써, 이온원(20)의 수명을 장기화하는 관점에서, 탄탈을 이용하는 것이 더욱 바람직하다.

[0040] 이러한 버누스형 이온원이나 IHC형 이온원은, 종래에, 이산화탄소나 포스핀을 원료로 하여 탄소 이온이나 인 이온 등의 모노머 이온을 생성하기 위한 장치로서 이용되고 있으며, 원료 가스의 분자 결합을 완전히 절단하여 원자 이온을 생성하는 것을 목적으로 한 장치이기 때문에, 원료 가스의 전리 효율이 매우 높다. 본 실시형태는, 이와 같이 전리 효율이 매우 높은 버누스형 이온원이나 IHC형 이온원을, 클러스터 이온을 생성하기 위한 장치로서 이용한다. 즉, 이들 이온원에 클러스터 이온을 생성하기 위한 원료 가스를 도입하므로, 예컨대 종래의 CnHm(3≤n≤16, 3≤m≤10)과 같은 클러스터 이온보다 클러스터 사이즈가 작은 클러스터 이온을 170㎂ 이상이라는 높은 빔 전류치로 생성할 수 있다. 이 때문에, 종래와 동일한 조사 에너지로 비교하였을 경우에, 개질층(14)에 있어서의 탄소 및 수소의 깊이 방향의 농도 프로파일의 피크를 종래보다 깊은 위치, 구체적으로는, 실리콘 웨이퍼의 표면(10A)으로부터 150㎚를 초과하는 위치에 형성할 수 있다. 그 결과, 높은 게터링 능력을 가지면서, 이면조사형 고체 촬상 소자에 있어서의 화이트 스팟 결함을 보다 억제할 수 있는 에피택셜 실리콘 웨이퍼를 얻을 수 있다. 또한, 본 명세서에 있어서 「농도 프로파일」이란, 2차 이온 질량 분석법(SIMS:Secondary Ion Mass Spectrometry)에 의한 측정으로 얻어진 깊이 방향의 농도 분포를 의미한다. 이에 반해, 특허문헌 1에 기재된 기술은, 바람직하게는 근접 게터링을 가능하게 하는 기술이며, 실제로는 표면조사형 고체 촬상 소자에 적절한 게터링 기술이다. 이 때문에, 특허문헌 1에 기재된 이온원은, 본래, CnHm(3≤n≤16, 3≤m≤10)과 같은 클러스터 사이즈가 큰 클러스터 이온을 생성하는 것을 목적으로 한 장치이며, 이온원의 챔버 내에서는 플라즈마가 발생하지 않는다. 따라서, 클러스터 사이즈가 작은 클러스터 이온을 높은 빔 전류치로 생성하는 것은 기술적으로 곤란하다.

[0041] 클러스터 이온의 가속 에너지는, 전단 가속 기구(30)에서는 30keV/Cluster 이상 40keV/Cluster 이하로 하는 것이 바람직하다. 후단 가속 기구(50)에서는, 40keV/Cluster 이상 970keV/Cluster 이하로 하는 것이 바람직하다. 전단 가속 기구(30) 및 후단 가속 기구(50)에 의한 가속 에너지가 합계로 70keV/Cluster 이상이면, 탄소 및 수소의 농도 프로파일의 피크를 실리콘 웨이퍼 표면(10A)으로부터 깊이 150㎚ 이상에 각각 위치시킬 수 있고, 970keV/Cluster 이하이면, 개질층(14)에 있어서의 탄소 및 수소의 깊이 방향의 농도 프로파일의 피크를, 실리콘 웨이퍼의 표면(10A)으로부터의 깊이가 2000㎚ 이내인 범위에 각각 위치시킬 수 있기 때문이다. 또한, 본 실시형태에서는, 후단 가속 기구(50)의 통과 후의 가속 에너지가 실리콘 웨이퍼(10)에 대한 클러스터 이온의 조사 에너지가 된다.

[0042] 클러스터 이온의 도스량은, 이하의 범위가 되도록, 빔 전류치나 이온 조사 시간을 제어함으로써 조정할 수 있다. 본 실시형태에서는, 이온원(20)에서 170㎂ 이상이라는 높은 빔 전류치가 얻어지므로, 이온 조사 시간은, 종래의 클러스터 이온의 조사에 비해 짧게 설정할 수 있다. 예컨대, 도스량을 1.0×1015atoms/㎝2로 하여, CH3의 클러스터 이온을 조사하는 경우, 이온 조사 시간은 180s∼2120s의 범위로부터 조정할 수 있다. 그 때문에, 클러스터 이온 조사에 수반하는, 실리콘 웨이퍼의 표면(10A)의 데미지를 억제할 수 있으며, 사이즈 150㎚ 이상의 에피택셜 결함을 10개/웨이퍼 이하로 억제할 수 있다. 도스량은 1×1013atoms/㎝2 이상 1×1016atoms/㎝2 이하로 하는 것이 바람직하고, 5×1013atoms/㎝2 이하로 하는 것이 더욱 바람직하다. 1×1013atoms/㎝2 이상이면, 탄소 및 수소의 깊이 방향의 농도 프로파일의 피크 농도를 모두 1×1016atoms/㎝3 이상으로 할 수가 있으므로, 보다 높은 게터링 능력을 얻을 수 있고, 1×1016atoms/㎝2 이하이면, 에피택셜 결함이 발생할 우려가 없기 때문이다.

[0043] 클러스터 이온의 조사에 있어서는, 실리콘 웨이퍼의 표면(10A)의 법선(法線)과 이온 빔이 이루는 각도로 정의되는 틸트(tile)각을 0°로 하는 것이 바람직하며, 실리콘 웨이퍼(10)를 그 중심 주위에 기준 위치(노치)로부터 회전시킨 각도로 정의되는 트위스트각을 0°로 하는 것이 바람직하다. 클러스터 이온의 조사에 수반하는 실리콘 웨이퍼의 표면(10A)의 데미지를 억제할 수 있으므로, 에피택셜 결함을 10개/웨이퍼 이하로 억제할 수 있기 때문이다.

[0044] [제2 공정]

도 1의 (B), (C)를 참조하여, 제2 공정에서는, 화학 기상 성장(CVD:chemical vapor deposition)법에 의해, 실리콘 웨이퍼(10)의 표면 중 개질층을 형성한 측의 표면(10A)(즉, 클러스터 이온(12)을 조사한 측의 표면) 상에 실리콘 에피택셜층(16)을 일반적인 조건으로 형성한다. 예컨대, 수소를 캐리어 가스로 하여, 디클로로실란, 트리클로로실란 등의 원료 가스를 챔버 내에 도입하고, 1000℃ 이상 1150℃이하에서, 실리콘 에피택셜층(16)을 에피택셜 성장시킨다. 실리콘 에피택셜층(16)의 두께는, 1㎛ 이상 10㎛ 이하로 하는 것이 바람직하다. 1㎛ 이상이면, 실리콘 웨이퍼로부터 바깥쪽(外方)으로 확산된 도펀트에 의해, 실리콘 에피택셜층의 저항율이 변화할 우려도 없고, 10㎛ 이하이면, 고체 촬상 소자의 분광 감도 특성에 영향이 생길 우려가 없기 때문이다. 특히, 실리콘 에피택셜층(16)의 일부를, 이면조사형 고체 촬상 소자를 제조하기 위한 디바이스 형성 영역으로 하는 경우에는, 실리콘 에피택셜층(16)의 두께는 3㎛ 이상 6㎛ 이하로 하는 것이 더욱 바람직하다.

[0045] 이상, 본 실시형태를 예로 하여 본 발명의 에피택셜 실리콘 웨이퍼의 제조 방법을 설명하였지만, 본 발명은, 상기의 실시형태로 한정되지 않으며, 특허청구의 범위 내에서 적절히 변경을 가할 수 있다.

[0046] 예컨대, 제1 공정과 제2 공정의 사이에, 실리콘 웨이퍼의 표면(10A)을 SC-1 세정(예컨대, 체적비로 H2O:H2O2:NH4OH=5:1:1인 용액)이나 SC-2 세정(예컨대, 체적비로 H2O:H2O2:HCl=6:1:1인 용액)을 행하는 공정을 가져도 된다. 이에 의해 표면(10A)의 파티클이나 중금속을 제거할 수 있기 때문이다.

[0047] (에피택셜 실리콘 웨이퍼)

도 1의 (C)를 참조하여, 상기 제조 방법에 의해 얻어지는 에피택셜 실리콘 웨이퍼(100)에 대해 설명한다. 에피택셜 실리콘 웨이퍼(100)는, 실리콘 웨이퍼(10)와, 실리콘 웨이퍼(10) 내에 형성된, 탄소 및 수소가 고용되어 이루어지는 개질층(14)과, 개질층(14) 상에 형성된 실리콘 에피택셜층(16)을 가진다. 또한, 실리콘 웨이퍼의 표면(10A)으로부터의 깊이가 150㎚ 초과 2000㎚ 이내인 범위에, 개질층(14)에 있어서의 탄소 및 수소의 깊이 방향의 농도 프로파일의 피크가 각각 위치하는 것을 특징으로 한다.

[0048] 에피택셜 실리콘 웨이퍼(100)에 의하면, 이하의 작용 효과를 얻을 수 있다. 즉, 에피택셜 실리콘 웨이퍼(100)는, 클러스터 이온(12)의 구성 원소인 탄소 및 수소의 석출을 국소적 영역에서 고농도로 할 수가 있으므로, 높은 게터링 능력을 가진다. 또한, 에피택셜 실리콘 웨이퍼(100)는, 실리콘 웨이퍼의 표면(10A)으로부터의 깊이가 150㎚ 초과 2000㎚ 이내인 범위에, 개질층(14)에 있어서의 탄소 및 수소의 깊이 방향의 농도 프로파일의 피크가 각각 위치한다. 이 때문에, 이면조사형 고체 촬상 소자에 있어서의 화이트 스팟 결함을 보다 억제할 수 있다.

[0049] 개질층(14)은, CnHm(n=1 또는 2, m=1, 2, 3, 4 또는 5)의 클러스터 이온의 구성 원소가 고용되어 있으므로, 클러스터 이온을 구성하는 원소종(種), 및 원자 개수로부터, 탄소의 깊이 방향의 농도 프로파일의 피크 위치와 수소의 깊이 방향의 농도 프로파일의 피크 위치의 차를 1000㎚ 이내로 할 수 있다.

[0050] 보다 높은 게터링 능력을 얻는 관점에서 보면, 탄소의 깊이 방향의 농도 프로파일의 피크 농도와 수소의 깊이 방향의 농도 프로파일의 피크 농도가 모두 1×1016atoms/㎝3 이상인 것이 바람직하다.

[0051] 이상, 본 실시형태를 예로 하여 본 발명의 에피택셜 실리콘 웨이퍼를 설명하였지만, 본 발명은, 상기의 실시형태로 한정되지 않으며, 특허청구의 범위 내에서 적절히 변경을 가할 수가 있다.

[0052] (고체 촬상 소자의 제조 방법)

본 발명의 하나의 실시형태에 따른 이면조사형 고체 촬상 소자의 제조 방법은, 상기 에피택셜 실리콘 웨이퍼의 제조 방법으로 제조된 에피택셜 실리콘 웨이퍼 또는 상기 에피택셜 실리콘 웨이퍼, 즉 에피택셜 실리콘 웨이퍼(100)의 표면에 위치하는 실리콘 에피택셜층(16)에, 고체 촬상 소자를 형성하는 것을 특징으로 한다. 이 제조 방법에 의해 얻어지는 고체 촬상 소자는, 종래에 비해 화이트 스팟 결함의 발생을 더욱 억제할 수 있다.

실시예

[0053] (발명예)

[클러스터 이온의 생성]

원료 가스를 2-메틸펜탄으로 하고, 도 2의 (C)에 나타낸 IHC형 이온원(NISSIN ION EQUIPMENT CO. LTD. 제조, 제품 번호:IMPHEAT)을 이용하여, 이온을 생성하였다. 아크 챔버 내의 압력을 2.2×10-2Pa, 아크 챔버의 전압을 76V로 하고, 전류를 2200mA로 하고, 외부 자기장을 0.6A/m로 하고, 원료 가스의 유량을 4.0cc/min으로 하였다.

[0054] 여기서, 도 2의 (A)에 나타낸 질량 분석 기구를 이용하여, IHC형 이온원으로 생성한 이온의 질량을 분석하였다. 분석 결과를 도 4에 나타낸다. 도 4에 나타낸 매스값(AMU) 15에 해당하는 단편(fragment)이 CH3의 클러스터 이온이며, 매스값(AMU) 26에 해당하는 단편(fragment)이 C2H2의 클러스터 이온이다. CH3의 빔 전류치는 325㎂이고, C2H2의 빔 전류치는 250㎂였다. 따라서, IHC형 이온원을 이용하여, 종래보다 클러스터 사이즈가 작은 클러스터 이온을 170㎂ 이상이라는 높은 빔 전류치로 생성할 수 있음을 확인하였다. 또한, 도 4에 나타낸 CH3나 C2H2 이외의 단편(fragment)은, 수소나 탄소의 원자 이온 또는 단원자(單原子)나 분자 이온 등이다.

[0055] [에피택셜 실리콘 웨이퍼의 제작]

상기의 조건으로 생성한 이온 중에서 CH3의 클러스터 이온을 추출하여, 이것을 p형 실리콘 웨이퍼(10)(두께:725㎛, 도펀트:붕소, 도펀트 농도:8.5×1018atoms/㎝3)의 표면에 조사하여(도 1의 (A)), 실리콘 웨이퍼 내에, 클러스터 이온의 구성 원소인 탄소 및 수소가 고용되어 이루어지는 개질층(14)을 형성하였다(도 1의 (B)). 도스량은 1×1015atoms/㎝2로 하고, 전단 가속 및 후단 가속을 합계한 조사 에너지는 80keV/Cluster로 하고, 틸트각은 0°로 하고, 트위스트각은 0°로 하였다.

[0056] 다음으로, 실리콘 웨이퍼를 개별 처리 방식(枚葉式)의 에피택셜 성장 장치(Applied Materials, Inc. 제조) 내로 반송하고, 장치 내에서 1120℃의 온도로 30초의 수소 베이크 처리를 실시한 후, 수소를 캐리어 가스로 하고 디클로로실란을 소스 가스로 하여 1150℃로 CVD법에 의해, 실리콘 웨이퍼의 표면 중 개질층을 형성한 측의 표면 상에 실리콘 에피택셜층(두께:6㎛, 도펀트:붕소, 도펀트 농도:1.0×1015atoms/㎝3)을 에피택셜 성장시켜, 본 발명에 따른 에피택셜 실리콘 웨이퍼(100)를 제작하였다(도 1의 (C)).

[0057] (비교예)

[클러스터 이온의 생성]

원료 가스를 시클로헥산으로 하고, 클러스터 이온 발생 장치(NISSIN ION EQUIPMENT CO. LTD. 제조, 제품 번호:CLARIS)를 이용하여, C3H5의 클러스터 이온을 생성하였다. 또한, 클러스터 이온의 빔 전류치는 850㎂였다.

[0058] [에피택셜 실리콘 웨이퍼의 제작]

이 클러스터 이온을 p형 실리콘 웨이퍼(두께:725㎛, 도펀트:붕소, 도펀트 농도:8.5×1018atoms/㎝3)의 표면에 조사하여, 실리콘 웨이퍼의 표면에, 클러스터 이온의 구성 원소인 탄소 및 수소가 고용되어 이루어지는 개질층을 형성하였다. 도스량은 1×1015atoms/㎝2로 하고, 조사 에너지는 80keV/Cluster로 하고, 틸트각은 0°로 하고, 트위스트각은 0°로 하였다.

[0059] 다음으로, 실리콘 웨이퍼를 개별 처리 방식(枚葉式)의 에피택셜 성장 장치(Applied Materials, Inc. 제조) 내로 반송하고, 장치 내에서 1120℃의 온도로 30초의 수소 베이크 처리를 실시한 후, 수소를 캐리어 가스로 하고 디클로로실란을 소스 가스로 하여 1150℃로 CVD법에 의해, 실리콘 웨이퍼의 표면 중 개질층을 형성한 측의 표면 상에 실리콘 에피택셜층(두께:6㎛, 도펀트:붕소, 도펀트 농도:1.0×1015atoms/㎝3)을 에피택셜 성장시켜, 에피택셜 실리콘 웨이퍼를 제작하였다.

[0060] (평가 방법 및 평가 결과)

우선, 각 발명예 및 비교예에 대해, 2차 이온 질량 분석법(SIMS)에 의해 측정을 행하여, 조사(照射) 원소인 탄소 및 수소의 깊이 방향의 농도 프로파일을 얻었다. 평가 결과를 도 5의 (A), (B) 및 도 6의 (A), (B)에 나타낸다.

[0061] 발명예에서는, 도 5의 (A), (B)에 나타낸 바와 같이, 탄소의 농도 프로파일의 피크는, 실리콘 에피택셜층과 실리콘 웨이퍼 간의 계면(즉, 실리콘 웨이퍼의 표면 중 클러스터 이온을 조사한 측의 표면)으로부터 167㎚의 위치에 있으며, 피크 농도는 5.37×1019atoms/㎝3였다. 또한, 수소의 농도 프로파일의 피크는, 실리콘 에피택셜층과 실리콘 웨이퍼 간의 계면으로부터 167㎚의 위치에 있으며, 피크 농도는 7.36×1017atoms/㎝3였다. 한편, 비교예에서는, 도 6의 (A), (B)에 나타낸 바와 같이, 탄소의 농도 프로파일의 피크는, 실리콘 에피택셜층과 실리콘 웨이퍼 간의 계면으로부터 80㎚의 위치에 있으며, 피크 농도는 8.65×1019atoms/㎝3였다. 또한, 수소의 농도 프로파일의 피크는, 실리콘 에피택셜층과 실리콘 웨이퍼 간의 계면으로부터, 80㎚의 위치에 있으며, 피크 농도는 1.35×1018atoms/㎝3였다. 따라서, 발명예는 피크 위치를 비교예보다 깊은 위치에 형성하는 것이 가능하였다.

[0062] 다음으로, 각 발명예 및 비교예의 실리콘 에피택셜층의 표면을 Ni 오염액(1.0×1013atoms/㎝2)으로 스핀 코트 오염법에 의해 고의로 오염시킨 후에, 질소 분위기하에서 900℃, 30분의 열처리를 실시하였다. 이후, 2차 이온 질량 분석법(SIMS)에 의해 측정을 행하여, Ni의 깊이 방향의 농도 프로파일을 얻었다. 평가 결과를 도 7에 나타낸다.

[0063] 도 7에 나타낸 바와 같이, 각 발명예 및 비교예 모두, 개질층이 게터링 사이트로서 기능함으로써, 높은 게터링 능력을 발휘하는 것을 확인할 수 있었다. 나아가, 발명예에서는, 탄소 및 수소의 피크 위치가 비교예보다 깊은 위치에 존재하고 있었던 것에 기인하여, Ni의 농도 프로파일의 끝자락의 실리콘 에피택셜층으로의 확산을 비교예보다 억제하는 것이 가능하였다. 이것으로부터, 발명예에 따른 에피택셜 실리콘 웨이퍼를 이용하여 이면조사형 고체 촬상 소자를 제작하면, 화이트 스팟 결함을 비교예보다 억제할 수 있음을 알 수 있다.

[0064] 본 발명에 의하면, 높은 게터링 능력을 가지면서, 이면조사형 고체 촬상 소자에 있어서의 화이트 스팟 결함을 보다 억제할 수 있는 에피택셜 실리콘 웨이퍼를 얻을 수 있다.

100

에피택셜 실리콘 웨이퍼

10 실리콘 웨이퍼

10A 실리콘 웨이퍼의 표면

12 클러스터 이온

14 개질층

16 실리콘 에피택셜층

20 이온원

21 아크 챔버

22 원료 가스 도입구

23 이온 추출구

24 필라멘트

25 리플렉터

26 전류 전압 인가 장치

27 자기장 발생 장치

28 진공 펌프

29 캐소드

30 전단 가속 기구

40 질량 분석 기구

50 후단 가속 기구

60 조사 챔버

70 이온 조사 장치

10 실리콘 웨이퍼

10A 실리콘 웨이퍼의 표면

12 클러스터 이온

14 개질층

16 실리콘 에피택셜층

20 이온원

21 아크 챔버

22 원료 가스 도입구

23 이온 추출구

24 필라멘트

25 리플렉터

26 전류 전압 인가 장치

27 자기장 발생 장치

28 진공 펌프

29 캐소드

30 전단 가속 기구

40 질량 분석 기구

50 후단 가속 기구

60 조사 챔버

70 이온 조사 장치

Claims (8)

- 실리콘 웨이퍼의 표면에, 버누스형 이온원 또는 IHC형 이온원을 이용하여 생성한 CnHm(n=1 또는 2, m=1, 2, 3, 4 또는 5)의 클러스터 이온을 조사하여, 상기 실리콘 웨이퍼 내에, 상기 클러스터 이온의 구성 원소인 탄소 및 수소가 고용되어 이루어지는 개질층을 형성하는 제1 공정과,

상기 제1 공정 후에, 상기 표면 상에 실리콘 에피택셜층을 형성하는 제2 공정을 갖고,

상기 제1 공정에서는, 상기 개질층에 있어서의 상기 탄소 및 상기 수소의 깊이 방향의 농도 프로파일의 피크를, 상기 실리콘 웨이퍼의 상기 표면으로부터의 깊이가 150㎚ 초과 2000㎚ 이내인 범위에 각각 위치시키는 것을 특징으로 하는 에피택셜 실리콘 웨이퍼의 제조 방법. - 제1항에 있어서,

상기 제1 공정에서는, 상기 클러스터 이온을 170㎂ 이상의 빔 전류치로 조사하는, 에피택셜 실리콘 웨이퍼의 제조 방법. - 제1항 또는 제2항에 있어서,

상기 제1 공정에서는, 상기 실리콘 웨이퍼의 틸트각 및 트위스트각이 모두 0°가 되도록, 상기 클러스터 이온의 조사를 행하는, 에피택셜 실리콘 웨이퍼의 제조 방법. - 제1항 내지 제3항 중 어느 한 항에 있어서,

상기 제1 공정과 상기 제2 공정의 사이에, 상기 실리콘 웨이퍼의 표면을 세정하는 공정을 더 갖는, 에피택셜 실리콘 웨이퍼의 제조 방법. - 실리콘 웨이퍼와, 상기 실리콘 웨이퍼 내에 형성된, 탄소 및 수소가 고용되어 이루어지는 개질층과, 상기 개질층 상에 형성된 실리콘 에피택셜층을 갖고,

상기 실리콘 웨이퍼의 표면으로부터의 깊이가 150㎚ 초과 2000㎚ 이내인 범위에, 상기 개질층에 있어서의 상기 탄소 및 상기 수소의 깊이 방향의 농도 프로파일의 피크가 각각 위치하는 것을 특징으로 하는 에피택셜 실리콘 웨이퍼. - 제5항에 있어서,

상기 탄소의 깊이 방향의 농도 프로파일의 피크 위치와 상기 수소의 깊이 방향의 농도 프로파일의 피크 위치의 차(差)가 1000㎚ 이내인, 에피택셜 실리콘 웨이퍼. - 제5항 또는 제6항에 있어서,

상기 탄소의 깊이 방향의 농도 프로파일의 피크 농도와 상기 수소의 깊이 방향의 농도 프로파일의 피크 농도가 모두 1×1016atoms/㎝3 이상인, 에피택셜 실리콘 웨이퍼. - 제1항 내지 제4항 중 어느 한 항에 기재된 에피택셜 실리콘 웨이퍼의 제조 방법으로 제조된 에피택셜 실리콘 웨이퍼 또는 제5항 내지 제7항 중 어느 한 항에 기재된 에피택셜 실리콘 웨이퍼의 실리콘 에피택셜층에, 고체 촬상 소자를 형성하는 것을 특징으로 하는 고체 촬상 소자의 제조 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017249862A JP6812962B2 (ja) | 2017-12-26 | 2017-12-26 | エピタキシャルシリコンウェーハの製造方法 |

| JPJP-P-2017-249862 | 2017-12-26 | ||

| PCT/JP2018/031435 WO2019130653A1 (ja) | 2017-12-26 | 2018-08-24 | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、及び固体撮像素子の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20200044930A true KR20200044930A (ko) | 2020-04-29 |

| KR102393269B1 KR102393269B1 (ko) | 2022-04-29 |

Family

ID=67066804

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020207009158A KR102393269B1 (ko) | 2017-12-26 | 2018-08-24 | 에피택셜 실리콘 웨이퍼의 제조 방법, 에피택셜 실리콘 웨이퍼, 및 고체 촬상 소자의 제조 방법 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US11245014B2 (ko) |

| JP (1) | JP6812962B2 (ko) |

| KR (1) | KR102393269B1 (ko) |

| CN (1) | CN111771265B (ko) |

| TW (1) | TWI700734B (ko) |

| WO (1) | WO2019130653A1 (ko) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6988843B2 (ja) * | 2019-02-22 | 2022-01-05 | 株式会社Sumco | 半導体エピタキシャルウェーハ及びその製造方法 |

| US11271079B2 (en) * | 2020-01-15 | 2022-03-08 | Globalfoundries U.S. Inc. | Wafer with crystalline silicon and trap rich polysilicon layer |

| CN113249684B (zh) * | 2021-04-16 | 2023-05-16 | 杭州电子科技大学 | 一种高密度功能团簇材料及其制备方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050269520A1 (en) * | 1999-12-13 | 2005-12-08 | Semequip Inc. | Icon implantation ion source, system and method |

| KR20100040673A (ko) * | 2008-10-10 | 2010-04-20 | 소니 주식회사 | Soi 기판과 그 제조 방법, 고체 촬상 장치와 그 제조 방법, 및 촬상 장치 |

| WO2012157162A1 (ja) | 2011-05-13 | 2012-11-22 | 株式会社Sumco | 半導体エピタキシャルウェーハの製造方法、半導体エピタキシャルウェーハ、および固体撮像素子の製造方法 |

| KR20170041229A (ko) * | 2014-08-28 | 2017-04-14 | 가부시키가이샤 사무코 | 반도체 에피택셜 웨이퍼 및 그 제조 방법, 및, 고체 촬상 소자의 제조 방법 |

| KR20170101833A (ko) * | 2016-02-29 | 2017-09-06 | 가부시키가이샤 사무코 | 반도체 에피택셜 웨이퍼 및 그 제조 방법 및 고체 촬상 소자의 제조 방법 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5159005B2 (ja) * | 2000-01-20 | 2013-03-06 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US20090124065A1 (en) * | 2007-11-13 | 2009-05-14 | Varian Semiconductor Equipment Associates, Inc. | Particle beam assisted modification of thin film materials |

| JP2009200231A (ja) * | 2008-02-21 | 2009-09-03 | Sumco Corp | エピタキシャルウェーハ及びその製造方法 |

| US8330118B2 (en) | 2008-05-16 | 2012-12-11 | Semequip, Inc. | Multi mode ion source |

| SG161151A1 (en) * | 2008-10-22 | 2010-05-27 | Semiconductor Energy Lab | Soi substrate and method for manufacturing the same |

| US20130341761A1 (en) * | 2012-06-20 | 2013-12-26 | Ashwini K. Sinha | Methods for extending ion source life and improving ion source performance during carbon implantation |

| JP6442817B2 (ja) * | 2013-08-20 | 2018-12-26 | 株式会社Sumco | エピタキシャルウェーハの製造方法およびエピタキシャルウェーハ |

| JP6516957B2 (ja) | 2013-09-04 | 2019-05-22 | 株式会社Sumco | エピタキシャルウェーハの製造方法及び貼り合わせウェーハの製造方法 |

| JP6493104B2 (ja) * | 2015-09-03 | 2019-04-03 | 株式会社Sumco | 半導体エピタキシャルウェーハの製造方法、品質予測方法および品質評価方法 |

| JP6459948B2 (ja) | 2015-12-15 | 2019-01-30 | 株式会社Sumco | 半導体エピタキシャルウェーハの製造方法および固体撮像素子の製造方法 |

| JP6508030B2 (ja) | 2015-12-17 | 2019-05-08 | 株式会社Sumco | シリコンエピタキシャルウェーハの製造方法および固体撮像素子の製造方法 |

-

2017

- 2017-12-26 JP JP2017249862A patent/JP6812962B2/ja active Active

-

2018

- 2018-08-24 WO PCT/JP2018/031435 patent/WO2019130653A1/ja active Application Filing

- 2018-08-24 KR KR1020207009158A patent/KR102393269B1/ko active IP Right Grant

- 2018-08-24 CN CN201880083648.6A patent/CN111771265B/zh active Active

- 2018-08-24 US US16/956,232 patent/US11245014B2/en active Active

- 2018-09-07 TW TW107131603A patent/TWI700734B/zh active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050269520A1 (en) * | 1999-12-13 | 2005-12-08 | Semequip Inc. | Icon implantation ion source, system and method |

| KR20100040673A (ko) * | 2008-10-10 | 2010-04-20 | 소니 주식회사 | Soi 기판과 그 제조 방법, 고체 촬상 장치와 그 제조 방법, 및 촬상 장치 |

| WO2012157162A1 (ja) | 2011-05-13 | 2012-11-22 | 株式会社Sumco | 半導体エピタキシャルウェーハの製造方法、半導体エピタキシャルウェーハ、および固体撮像素子の製造方法 |

| KR20170041229A (ko) * | 2014-08-28 | 2017-04-14 | 가부시키가이샤 사무코 | 반도체 에피택셜 웨이퍼 및 그 제조 방법, 및, 고체 촬상 소자의 제조 방법 |

| KR20170101833A (ko) * | 2016-02-29 | 2017-09-06 | 가부시키가이샤 사무코 | 반도체 에피택셜 웨이퍼 및 그 제조 방법 및 고체 촬상 소자의 제조 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW201929053A (zh) | 2019-07-16 |

| KR102393269B1 (ko) | 2022-04-29 |

| JP6812962B2 (ja) | 2021-01-13 |

| WO2019130653A1 (ja) | 2019-07-04 |

| CN111771265A (zh) | 2020-10-13 |

| CN111771265B (zh) | 2024-02-02 |

| US11245014B2 (en) | 2022-02-08 |

| US20210083058A1 (en) | 2021-03-18 |

| TWI700734B (zh) | 2020-08-01 |

| JP2019117832A (ja) | 2019-07-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9847370B2 (en) | Method of producing semiconductor epitaxial wafer, semiconductor epitaxial wafer, and method of producing solid-state image sensing device | |

| US20200127043A1 (en) | Method of producing semiconductor epitaxial wafer, semiconductor epitaxial wafer, and method of producing solid-state image sensing device | |

| KR101837454B1 (ko) | 반도체 에피텍셜 웨이퍼의 제조 방법, 반도체 에피텍셜 웨이퍼, 및 고체 촬상 소자의 제조 방법 | |

| US20200127044A1 (en) | Method for producing semiconductor epitaxial wafer, semiconductor epitaxial wafer, and method of producing solid-state image sensing device | |

| KR102393269B1 (ko) | 에피택셜 실리콘 웨이퍼의 제조 방법, 에피택셜 실리콘 웨이퍼, 및 고체 촬상 소자의 제조 방법 | |

| TWI611482B (zh) | 半導體磊晶晶圓的製造方法及固體攝像元件的製造方法 | |

| CN111108583B (zh) | 半导体外延晶片及其制造方法、以及固体摄像元件的制造方法 | |

| CN111902911A (zh) | 半导体外延晶片的制造方法以及半导体器件的制造方法 | |

| CN110223907B (zh) | 半导体外延晶片的制造方法 | |

| JP7095725B2 (ja) | エピタキシャルシリコンウェーハ | |

| CN113454756B (zh) | 半导体外延晶片及其制造方法 | |

| JP6930459B2 (ja) | 半導体エピタキシャルウェーハの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |