KR20160145801A - 관통-유리 비아의 제조를 위한 본딩 재료의 엣칭 백 공정 - Google Patents

관통-유리 비아의 제조를 위한 본딩 재료의 엣칭 백 공정 Download PDFInfo

- Publication number

- KR20160145801A KR20160145801A KR1020167032591A KR20167032591A KR20160145801A KR 20160145801 A KR20160145801 A KR 20160145801A KR 1020167032591 A KR1020167032591 A KR 1020167032591A KR 20167032591 A KR20167032591 A KR 20167032591A KR 20160145801 A KR20160145801 A KR 20160145801A

- Authority

- KR

- South Korea

- Prior art keywords

- substrate

- bonding layer

- holes

- vias

- carrier

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 85

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 15

- 239000000463 material Substances 0.000 title claims description 10

- 239000000758 substrate Substances 0.000 claims abstract description 148

- 239000011521 glass Substances 0.000 claims abstract description 146

- 239000004020 conductor Substances 0.000 claims abstract description 34

- 238000005530 etching Methods 0.000 claims abstract description 31

- 239000000853 adhesive Substances 0.000 claims description 34

- 230000001070 adhesive effect Effects 0.000 claims description 34

- 239000002904 solvent Substances 0.000 claims description 10

- 238000001312 dry etching Methods 0.000 claims description 7

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 claims description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 5

- 229910052802 copper Inorganic materials 0.000 claims description 5

- 239000010949 copper Substances 0.000 claims description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 claims description 4

- 229910052786 argon Inorganic materials 0.000 claims description 2

- 239000007789 gas Substances 0.000 claims description 2

- 238000001039 wet etching Methods 0.000 claims description 2

- 238000005553 drilling Methods 0.000 claims 1

- 239000010410 layer Substances 0.000 description 81

- 238000005429 filling process Methods 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- 238000001465 metallisation Methods 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- 239000011800 void material Substances 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000003750 conditioning effect Effects 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 235000001674 Agaricus brunnescens Nutrition 0.000 description 1

- 229910000881 Cu alloy Inorganic materials 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 239000012790 adhesive layer Substances 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- LDDQLRUQCUTJBB-UHFFFAOYSA-N ammonium fluoride Chemical compound [NH4+].[F-] LDDQLRUQCUTJBB-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 238000007772 electroless plating Methods 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 239000003365 glass fiber Substances 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- LSGOVYNHVSXFFJ-UHFFFAOYSA-N vanadate(3-) Chemical compound [O-][V]([O-])([O-])=O LSGOVYNHVSXFFJ-UHFFFAOYSA-N 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/486—Via connections through the substrate with or without pins

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C15/00—Surface treatment of glass, not in the form of fibres or filaments, by etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6835—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/14—Mountings, e.g. non-detachable insulating substrates characterised by the material or its electrical properties

- H01L23/15—Ceramic or glass substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49866—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers characterised by the materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49866—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers characterised by the materials

- H01L23/49894—Materials of the insulating layers or coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/68318—Auxiliary support including means facilitating the separation of a device or wafer from the auxiliary support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/68345—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support used as a support during the manufacture of self supporting substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/68359—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support used as a support during manufacture of interconnect decals or build up layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/68381—Details of chemical or physical process used for separating the auxiliary support from a device or wafer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Materials Engineering (AREA)

- Life Sciences & Earth Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Geochemistry & Mineralogy (AREA)

- Organic Chemistry (AREA)

- Geometry (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

- Surface Treatment Of Glass (AREA)

- Drying Of Semiconductors (AREA)

- Weting (AREA)

Abstract

유리 기판에 비아를 제조하는 방법은 복수의 구멍을 포함한 상기 유리 기판의 제1 면을, 본딩 층을 통해 유리 캐리어의 제1 면에 본딩하는 단계를 포함한다. 본딩 층은 유리 기판의 제1 면과 유리 캐리어의 제1 면 사이의 두께(t)를 갖고, 그리고 상기 유리 기판의 상기 제1 면으로부터 깊이(h)까지 복수의 구멍 중 적어도 수개의 구멍으로 뻗어있다. 본 방법은 유리 기판의 복수의 구멍을 통해 깊이(d)로 본딩 층을 엣칭 백하는 단계를 포함한다. 깊이(d)는 두께(t) 및 깊이(h)의 합보다 더 작다. 본 방법은 전기 전도성 재료로써 복수의 구멍을 충전하는 단계와, 본딩 층 및 유리 캐리어로부터 유리 기판을 디-본딩하는 단계를 포함할 수 있다.

Description

본 발명은 2014년 04월 30일에 미국특허청에 35 U.S.C. § 119하에서 출원된 미국 특허 가출원번호 제61/986,370호를 우선권 주장하고 있으며, 이 특허문헌은 참조를 위해 본 명세서에 모두 통합되어 있다.

본 발명은 일반적으로 유리 비아를 통한 제조에 관한 것이며, 더욱 상세하게는 유리 비아를 통한 제조에 사용되는 엣칭 공정에 관한 것이다.

관통-기판 비아는 물리적인 전기 회로나 또는 칩에서 층 사이에 전기 접속부를 제공한다. 예를 들면, 3 차원 스택된 집적 회로에 있어서, 관통-기판 비아는 전자 부품을 수직으로 그리고 수평으로 모두 집적할 수 있게 한다. 전통적으로, 관통-기판 비아는 실리콘 기판을 사용한다. 그러나, 유리가 실리콘보다 덜 비싸기 때문에, 유리 기판은 전자 장치에서 더욱 널리 확대되고 있다.

감소된 비용, 가변(flexible) 열 팽창 계수, 및 유리 고유의 단열 특성이 매력적인 옵션으로서, 기판과 같은 유리의 선택을 만드는 한편으로, 유리의 사용은 여러 도전을 나타낸다. 특히, 유리 기판의 사용에 있어 하나의 도전은 제조 공정 동안에 유리의 적당하게 얇은 부분의 조정/처리(handling)이다. 다른 한 도전은 진입 구멍에서 유리에 크랙이 없이 그리고 비아의 금속화에 악 영향을 미치지 않으면서 고 속도로 유리 기판에 구멍을 형성하는 것이다.

이에 따라, 제조가능성을 향상시키고 비아의 신뢰가능한 금속화를 달성시키는 관통-유리 비아를 성형하는 대안적인 방법이 요구되고 있다.

일 실시예에 따라, 기판에 복수의 비아를 제조하는 방법은 캐리어의 제1 면에 복수의 구멍을 포함한 기판의 제1 면을 본딩 층을 사용하여 본딩하는 단계를 포함한다. 본딩 층은 기판의 제1 면과 캐리어의 제1 면 사이의 두께(t)를 갖고, 그리고 유리 기판의 제1 면으로부터 깊이(h)까지 적어도 수개의 복수의 구멍으로 뻗어있다. 본 방법은 또한 기판에서의 복수의 구멍을 통해 깊이(d)까지 본딩 층을 엣칭하는 단계를 포함한다. 깊이(d)는 두께(t)와 깊이(h)의 합보다 더 작다. 본 방법은 또한 복수의 비아를 형성하기 위해 재료로써 복수의 구멍을 충전하는 단계를 포함한다.

다른 일 실시예에 있어서, 기판에 복수의 비아를 제조하는 방법은 캐리어의 제1 면에, 복수의 구멍을 포함한 기판의 제1 면을 본딩하는 단계, 습식 엣칭 공정을 사용하여 상기 기판의 복수의 구멍을 통해 깊이(d)로 본딩 층을 엣칭하는 단계, 상기 기판에 복수의 비아를 형성하도록 전기 전도성 재료로써 복수의 구멍을 충전하는 단계, 그리고 상기 캐리어 및 상기 본딩 층으로부터 복수의 비아를 포함한 상기 유리 기판을 디-본딩하는 단계;를 포함한다. 기판의 제1 면은 본딩 층을 통해 유리 캐리어에 본딩된다. 본딩 층은 기판의 제1 면과 캐리어의 제1 면 사이의 두께(t)를 갖고, 그리고 깊이(d)는 상기 기판의 상기 제1 면으로부터 측정된다. 깊이(d)는 두께(t)보다 더 작다. 전기 전도성 재료는, 기판이 본딩 층 및 캐리어로부터 디-본딩될 때, 상기 전기 전도성 재료가 상기 기판의 제1 면으로부터 돌출하도록, 깊이(d)까지 본딩 층으로 뻗어있다.

다른 일 실시예에 있어서, 기판에 복수의 비아를 제조하는 방법은 복수의 구멍을 포함한 기판의 제1 면을 본딩 층을 통해 캐리어의 제1 면에 본딩하는 단계, 건식 엣칭 공정을 사용하여 깊이(d)까지 상기 본딩 층을 에칭하는 단계, 상기 기판에 복수의 비아를 형성하도록 전기 전도성 재료로 복수의 구멍을 충전하는 단계, 및 상기 캐리어와 상기 본딩 층으로부터 복수의 비아를 포함한 기판을 디-본딩하는 단계를 포함한다. 본딩 층은 기판의 제1 면과 캐리어의 제1 면 사이의 두께(t)를 갖는다. 깊이(d)는 기판의 제1 면으로부터 측정되고, 두께(t)와 동일하다. 캐리어의 제1 면은 건식 엣칭 공정을 위한 정지 층이다. 기판이 본딩 층 및 캐리어로부터 디-본딩될 때, 전기 전도성 재료는 상기 기판의 제1 면으로부터 길이(l)로 뻗어있는 기둥(pillar)을 형성하며, 이 경우 상기 길이(l)는 본딩 층의 두께(t)와 동일하다.

부가적인 특징과 장점이 아래 상세한 설명에 설명될 것이고, 당업자라면 적어도 바람직한 실시예로부터 용이하게 파악될 수 있으며, 또는 아래 기재된 청구범위 뿐만 아니라 첨부된 도면을 포함하여, 본 명세서에 기재된 바와 같은 실시예를 실시함으로 알 수 있을 것이다.

상기 일반적인 설명과 아래 상세한 설명 모두는 단지 예시적이고, 청구범위의 특징과 특성의 전반적인 또는 개괄적인 이해를 돕기 위한 것임을 알 수 있을 것이다. 첨부된 도면은, 본 발명의 이해를 더욱 돕기 위한 것으로서, 본 명세서의 일부를 이루도록 통합되어 있다. 도면은 하나 이상의 실시예를 나타내고 있고, 그리고 발명의 상세한 설명과 함께 다양한 실시예의 원리와 작동을 설명하도록 사용된다.

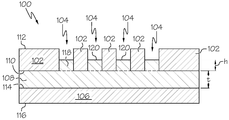

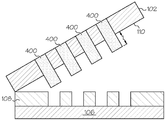

도 1은 하나 이상의 실시예에 따라 본딩 층을 통해 유리 캐리어에 본딩된, 복수의 구멍을 포함한 유리 기판의 개략적인 도면이고;

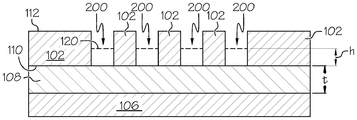

도 2는 하나 이상의 실시예에 따라 도 1에 도시된 유리 기판의 복수의 구멍을 통해 본딩 층을 엣칭 백하는 공정을 단면으로 개략적으로 나타낸 도면이고;

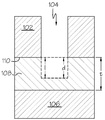

도 3a는 하나 이상의 실시예에 따른 유리 기판의 복수의 구멍 내에서 본딩 층의 원위 면의 높이(h)와 동일한 깊이(d)로 본딩 층을 엣칭 백하는 공정을 단면으로 개략적으로 나타낸 도면이고;

도 3b는 하나 이상의 실시예에 따른 본딩 층으로 길이(l)로 뻗어있는 깊이(d)로 본딩 층을 엣칭 백하는 공정을 단면으로 개략적으로 나타낸 도면이고;

도 3c는 하나 이상의 실시예에 따라 본딩 층으로의 길이(l)로 그리고 유리 기판의 복수의 구멍 내의 본딩 층의 원위 면의 높이(h)의 합과 동일한 깊이(d)로 본딩 층을 엣칭 백하는 공정을 단면으로 개략적으로 나타낸 도면이고;

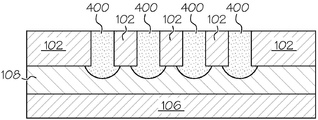

도 4a는 하나 이상의 실시예에 따른 버섯 형상을 갖는 복수의 비아를 전기 전도성 재료가 형성하는 금속 충전 공정을 단면으로 개략적으로 나타낸 도면이고;

도 4b는 하나 이상의 실시예에 따른 기둥 형상을 갖는 복수의 비아를 전기 전도성 재료가 형성하는 금속 충전 공정을 단면으로 개략적으로 나타낸 도면이고;

도 4c는 하나 이상의 실시예에 따른 기둥 형상을 갖는 복수의 비아를 전기 전도성 재료가 형성하는 금속 충전 공정을 단면으로 개략적으로 나타낸 도면이고;

도 5a는 도 4a에 도시된 실시예에 따른 복수의 버섯-형상의 비아를 구비한 유리 기판의 디-본딩 공정을 단면으로 개략적으로 나타낸 도면이고;

도 5b는 도 4b에 도시된 실시예에 따른 복수의 기둥-형상의 비아를 구비한 유리 기판의 디-본딩 공정을 단면으로 개략적으로 나타낸 도면이며; 그리고

도 5c는 도 4c에 도시된 실시예에 따른 복수의 기둥-형상의 비아를 구비한 유리 기판의 디-본딩 공정을 단면으로 개략적으로 나타낸 도면이다.

도 2는 하나 이상의 실시예에 따라 도 1에 도시된 유리 기판의 복수의 구멍을 통해 본딩 층을 엣칭 백하는 공정을 단면으로 개략적으로 나타낸 도면이고;

도 3a는 하나 이상의 실시예에 따른 유리 기판의 복수의 구멍 내에서 본딩 층의 원위 면의 높이(h)와 동일한 깊이(d)로 본딩 층을 엣칭 백하는 공정을 단면으로 개략적으로 나타낸 도면이고;

도 3b는 하나 이상의 실시예에 따른 본딩 층으로 길이(l)로 뻗어있는 깊이(d)로 본딩 층을 엣칭 백하는 공정을 단면으로 개략적으로 나타낸 도면이고;

도 3c는 하나 이상의 실시예에 따라 본딩 층으로의 길이(l)로 그리고 유리 기판의 복수의 구멍 내의 본딩 층의 원위 면의 높이(h)의 합과 동일한 깊이(d)로 본딩 층을 엣칭 백하는 공정을 단면으로 개략적으로 나타낸 도면이고;

도 4a는 하나 이상의 실시예에 따른 버섯 형상을 갖는 복수의 비아를 전기 전도성 재료가 형성하는 금속 충전 공정을 단면으로 개략적으로 나타낸 도면이고;

도 4b는 하나 이상의 실시예에 따른 기둥 형상을 갖는 복수의 비아를 전기 전도성 재료가 형성하는 금속 충전 공정을 단면으로 개략적으로 나타낸 도면이고;

도 4c는 하나 이상의 실시예에 따른 기둥 형상을 갖는 복수의 비아를 전기 전도성 재료가 형성하는 금속 충전 공정을 단면으로 개략적으로 나타낸 도면이고;

도 5a는 도 4a에 도시된 실시예에 따른 복수의 버섯-형상의 비아를 구비한 유리 기판의 디-본딩 공정을 단면으로 개략적으로 나타낸 도면이고;

도 5b는 도 4b에 도시된 실시예에 따른 복수의 기둥-형상의 비아를 구비한 유리 기판의 디-본딩 공정을 단면으로 개략적으로 나타낸 도면이며; 그리고

도 5c는 도 4c에 도시된 실시예에 따른 복수의 기둥-형상의 비아를 구비한 유리 기판의 디-본딩 공정을 단면으로 개략적으로 나타낸 도면이다.

첨부된 도면에 도시된 예시적인 실시예에 대한 상세한 사항을 참조하기 바란다. 가능하다면, 동일한 부재 번호는 동일하거나 비슷한 부품을 지시하도록 도면 내내 사용될 것이다. 본 발명의 방법에 사용된 구성요소의 일 실시예가 도 1에 도시되어 있고, 그리고 부재 번호 100으로써 도면에 전반적으로 지시되어 있다. 구성요소는 일반적으로 본딩 층을 통해 유리 캐리어에 본딩된, 복수의 구멍을 포함한 유리 기판을 포함할 수 있다. 본딩 층은 전기 전도성 재료로 충전된 복수의 구멍을 통해 에칭될 수 있고, 그리고 유리 기판은 유리 캐리어로부터 디-본딩될 수 있다.

본 발명의 방법은 유리 기판의 조정/처리와 관련된 도전에도 불구하고 상기 유리 기판에 관통-유리 비아가 제조될 수 있게 한다. 예를 들면, 유리 기판을 유리 캐리어에 본딩시킴으로써, 얇은 유리 기판의 조정/처리와 관련된 도전은 경감(alleviate)될 수 있다. 더욱이, 다양한 실시예는 더욱 효과적인 금속화를 초래하는 한편으로, 현 반도체 공정과 공정 흐름에 레버리지(leverage)를 도입할 수 있다.

도 1에 도시된 실시예에 있어서, 복수의 구멍(104)을 포함한 유리 기판(102)이 본딩 층(108)을 통해 유리 캐리어(106)에 본딩된다. 유리 기판(102)은 예를 들면, 3-차원 칩 내에 전기 접속부를 제공하기 위한 개재기(interposer)로서 사용될 수 있다. 유리 기판(102)은 제1 면(110)과, 상기 제1 면(110) 반대쪽 제2 면(112)을 포함한다. 이와 비슷하게, 유리 캐리어(106)는 제1 면(114)과, 상기 제1 면(114) 반대쪽 제2 면(116)을 포함한다. 유리 캐리어(106)는 제조자가 그 현 제조 공정이나 또는 설비를 변경하지 않고도 유리 기판(102)의 두께를 감소시킬 수 있게 한다. 비아가 유리 기판(102) 내에 형성된 이후에, 상기 유리 기판(102)은 유리 캐리어(106)로부터 분리되고 그리고 상기 유리 캐리어(106)는 차후의 유리 기판의 조정/처리에 버려질 수 있거나 재사용될 수 있다. 유리 기판(102)의 제1 면(110)은 본딩 층(108)의 두께(r) 만큼 유리 캐리어(106)의 제1 면(114)으로부터 분리된다.

유리 기판(102)의 조성과 치수는 특별하게 한정되지 않으며, 상기 유리 기판(102)의 요구되는 최종 사용에 기초하여 선택된다. 유리 기판(102)은 예를 들면, Corning, Inc.가 제조하는 Code 2318 유리, Eagle XG 유리 등일 수 있다. 부가적으로, 유리 기판(102)은 예를 들면, 4 inch, 6 inch, 8 inch, 또는 12 inch 직경을 갖는 웨이퍼의 형상을 취할 수 있다. 대안적으로, 유리 기판(102)은 그 최종 사용에 적당한 임의의 치수를 갖는 형태를 취할 수 있다. 유리 기판(102)의 두께는 또한 그 최종 사용에 따라 변할 수 있다. 예를 들면, 유리 기판(102)은 대략 30 ㎛ 내지 대략 1000 ㎛, 대략 40 ㎛ 내지 대략 500 ㎛, 대략 50 ㎛ 내지 대략 200 ㎛, 또는 대략 100 ㎛의 두께를 가질 수 있다. 다양한 실시예에 있어서, 유리 기판(102)은 대략 100 ㎛ 이하의 두께를 갖는다. 여러 실시예에 있어서, 유리 기판(102)은 100 ㎛ 보다 작은 두께를 갖는다. 임의의 적당한 두께의 유리 기판이 사용될 수 있다는 것을 알 수 있을 것이다.

복수의 구멍(104)은 임의의 적당한 방법에 의해 유리 기판(102)에 형성될 수 있다. 예를 들면, 다양한 실시예에 있어서, 복수의 구멍(104)이 펄스 레이저 빔을 사용하여 유리 기판(102)에 드릴링 가공된다. 레이저 빔은 희생(sacrificial) 커버 층 및 유리 기판(102)을 드릴링할 수 있는 광학 특성을 갖는 어느 한 레이저 빔일 수 있다(예를 들면, 대략 355 nm의 파장을 방출하는, 주파수 3배화된(frequency tripled) Nd:YVO4(neodymium dopes yttrium orthovanadate) 레이저인 UV(자외선) 레이저 빔). 레이저 빔은 유리 기판(102)에 복수의 구멍(104) 중 각각의 구멍을 형성하도록 사전결정된 위치에 펄스(pulse)될 수 있다. 복수의 구멍은 또한 여러 실시예에서 기계적으로 기계가공될 수 있다.

도 1에 도시된 바와 같이, 유리 기판(102)은 유리 캐리어(106)에 본딩된다. 유리 기판(102) 및 유리 캐리어(106)는 다양한 접착제 재료를 사용하여 본딩될 수 있고, 그리고 UV-경화가능한 접착제일 수 있거나 또는 아닐 수도 있다. 본딩 층은 TOK, BS, 3M, 또는 DuPont가 만드는 상업적으로 이용가능한 접착제일 수 있으며, 단지 예를 들자면, 이들 접착제에는 3M UV-경화가능한 접착제 LC-3200, 3M UV-경화가능한 접착제 LC-4200, 또는 3M UV-경화가능한 접착제 LC-5200가 포함된다. 다양한 실시예에 있어서, 접착제는 유리 기판(102)의 제1 면(110) 및 유리 캐리어(106)의 제1 면(114) 중 한면 또는 양면에 도포된다. 유리 기판(102)의 제1 면(110)은 유리 캐리어(106)의 제1 면(114)과 접촉하게 된다. 예를 들면, 접착제 층은 유리 기판의 제1 면(110) 및 유리 캐리어(106)의 제1 면(114) 중 한면이나 양면에 스핀-코팅(spin-coat)될 수 있다. 압력 및/또는 열이 본딩 층(108)을 통해 유리 기판(102) 및 유리 캐리어(106)를 본딩하도록 상기 유리 기판(102)과 상기 유리 캐리어(106)에 가해질 수 있다.

다양한 실시예에 있어서, 본딩처리 동안에 유리 기판(102) 및 유리 캐리어(106)에 압력이 가해지면, 본딩 층(108)이 적어도 수개의 복수의 구멍(104)으로 확장되어, 접착제 플러그(118)를 형성한다. 도 1에 도시된 바와 같이, 접착제 플러그(118)는 유리 기판(102)의 제1 면(110)으로부터 접착제 플러그(118)의 원위 면(120)까지 측정된 바와 같은 높이(h)로 복수의 구멍(104)으로 뻗어있다. 이에 따라, 본딩 층(108)은 접착제 플러그(118)의 원위 면(120)으로부터 유리 캐리어(106)의 제1 면(114)까지 측정된 바와 같이, 복수의 구멍(104) 내측의 높이(h)에 더하여 두께(t) 및 유리 기판의 제1 면(110)과 유리 캐리어(106)의 제1 면(114) 사이의 두께(t)를 가질 수 있다.

유리 기판(102)이 유리 캐리어(106)에 본딩된 이후에, 엣칭-백 공정은 접착제 플러그(118)를 제거하도록 사용된다. 복수의 구멍(104)으로부터의 접착제 플러그(118)의 제거는 유리 섬유 및 수지를 제거함으로써, 상기 복수의 구멍(104)을 더욱 형성하도록 사용되어, 상기 복수의 구멍이 전기 전도성 재료로 충전될 때, 상기 전기 전도성 재료가 상기 구멍의 내부를 매끈하게 그리고 완전하게 코팅할 수 있고, 이에 따라 상기 유리 기판의 어느 한 측에서 층 사이에 효과적인 연결부를 형성한다.

도 2에 도시된 바와 같이, 엣칭액(200)은 유리 기판(102)의 제2 면(112)에서 복수의 구멍(105)을 통해 안내된다. 엣칭 공정은 특별하게 한정되지 않으며, 습식 엣칭 공정이나 또는 건식 엣칭 공정을 포함할 수 있다.

다양한 실시예에 있어서, 습식 엣칭 공정은 본딩 층(108)을 엣칭 백하도록 사용된다. 이러한 실시예에 있어서, 엣칭액(200)은 엣칭 솔벤트일 수 있다. 본딩 층(108)은 복수의 구멍(104)을 통해 엣칭 솔벤트에 노출될 수 있다. 유리 기판(102)은 엣칭 공정용 경질의 마스크로 기능한다. 예를 들면, 각각의 접착제 플러그(118) 및 상기 접착제 플러그(118)로부터 유리 캐리어(106)의 제1 면(114)까지 뻗어있는 본딩 층(108)의 부분이 엣칭액(200)에 노출될 수 있는 한편으로, 유리 기판(102)의 제1 면(110)과 상기 유리 캐리어(106)의 상기 제1 면(114) 사이의 상기 본딩 층(108)의 부분이 엣칭액(200)에 노출되지 않을 수 있으며, 상기 부분에 구멍이 존재하지 않는다. 이에 따라, 접착제 플러그(118)와 유리 캐리어(106)의 제1 면(114) 사이에 그리고 (접착제 플러그(118)를 이루는) 복수의 구멍(104)으로 뻗어있는 본딩 층(108)의 일부는 엣칭될 수 있는 한편으로, 상기 본딩 층(108)의 다른 부분이 유지된다.

엣칭 솔벤트는 플루오르화 수소산, 불화 암모니아, 질산, 아세트산, 아세톤 중 적어도 하나를 포함할 수 있거나 또는 이들의 조합을 포함할 수 있지만, 이들로만 한정되는 것은 아니다. 다양한 실시예에 있어서, 엣칭 솔벤트는 버퍼된 옥사이드 엣칭(즉, BOE(buffered oxide etch), 버퍼된 HF, 또는 BHF) 또는 아세톤을 포함할 수 있다. 다른 엣칭 솔벤트가 유리 캐리어(106) 및 유리 기판(102)의 특별한 유리 조성과 본딩 층에서의 특별한 접착제 재료에 따라, 사용될 수 있다. 특히, 적당한 엣칭 솔벤트는 유리 캐리어(106) 및 유리 기판(102)의 유리와 본딩 층(108) 사이에 높은 선택성을 갖는다. 엣칭 솔벤트는 유리 기판(102)에 분무될 수 있거나 또는 구성요소(100)가 엣칭 솔벤트에 침지될 수 있다.

다른 실시예에 있어서, 건식 엣칭 공정은 본딩 층(108)을 엣칭 백하도록 사용된다. 이러한 실시예에 있어서, 플라즈마 엣칭기(etcher)는 O2 또는 아르곤-함유 가스로부터 발생된 플라즈마를 사용해 본딩 층(108)을 엣칭 백하도록 사용될 수 있다. 다른 건식 엣칭 공정이 사용될 수 있다. 건식 엣칭 공정은 시간으로 제어될 수 있거나 또는 엣칭이 유리 캐리어(106)에 도달할 때 멈춰질 수 있다.

엣칭이 습식 엣칭 공정을 사용하여 실행되거나 건식 엣칭 공정을 사용하여 실행되던 간에, 도 2에 도시된 바와 같이, 복수의 구멍(104) 내의 본딩 층(108)은, 접착제 플러그(118)가 제거되도록, 상기 접착제 플러그(118)의 원위 면(120)을 통해 엣칭 백된다. 엣칭 공정의 기간은 한정되지 않으며, 엣칭 백의 요구되는 깊이와 엣칭 율에 기초하여 결정될 수 있다.

도 3a - 도 3c에 도시된 바와 같이, 다양한 실시예에 있어서, 본딩 층(108)은 복수의 구멍(104)을 통해 깊이(d)까지 엣칭 백된다. 본 발명에서 사용된 바와 같이, 깊이(d)는 접착제 플러그(118)의 원위 면(120)으로부터 측정된 본딩 층(108)으로의 깊이를 나타낸다(예를 들면, 두께(t)의 적어도 일부를 더한 깊이(h)의 합). 예를 들면, 엣칭 백 공정이 접착제 플러그(118)를 이루는 접착제 만을 엣칭 백하도록 사용될 때 그리고 유리 기판(102)의 제1 면(110)을 지나 본딩 층(108)의 접착제 재료를 엣칭하지 않을 때, 깊이(d)는 도 3a에 도시된 바와 같이, 접착제 플러그(118)의 높이(h)와 동일하다. 여러 실시예에 있어서, 예를 들면, 본딩 층(108)이 복수의 구멍(104)으로 뻗어있지 않은 곳에서, 깊이(d)는 도 3b에 도시된 바와 같이, 본딩 층(108)의 두께(t)보다 더 작거나 동일하다. 도 3c에 도시된 바와 같이, 엣칭 백 공정이 접착제 플러그(118)를 엣칭 백하도록 사용될 때 그리고 본딩 층(108)의 두께(t)를 통해 적어도 부분적으로 더욱 엣칭될 때, 깊이(d)는 상기 두께(t)의 일부를 더한 높이(h)의 합과 동일하다. 다양한 실시예에 있어서, 길이(l)는 유리 기판(102)의 제1 면(110)으로부터 측정된 바와 같이, 엣칭이 뻗어있는 본딩 층(108)으로의 길이를 나타낸다. 예를 들면, 도 3b에 있어서, 길이(l)는, 접착제 플러그가 없기 때문에(예를 들면, 높이(h)가 0과 같음), 깊이(d)와 동일하다. 도 3c에 있어서, 길이(l)는 깊이(d)와 높이(h)의 차이와 동일하다. 이에 따라, 깊이(d)가 존재한다면, 이는 접착제 플러그의 높이(h)와 길이(l)의 합과 동일하다.

엣칭 공정이 일단 완료되면, 복수의 구멍(104)은 전기 전도성 재료로 충전된다. 전기 전도성 재료는 구리, 은, 알루미늄, 니켈, 이들의 합금, 및 이들의 조합일 수 있으며, 이들은 단지 예시적인 것으로서 이들로만 한정되는 것은 아니다. 여러 실시예에 있어서, 복수의 구멍(104)은 구리 합금과 같은 구리-함유 재료로 충전된다.

충전 공정은 복수의 구멍으로 땜납 페이스트를 물리적으로 배치시키는 웨이브 납땜 공정, 진공 솔더 기술, 또는 기술 상 알려지거나 사용되는 임의의 여러 금속 충전 기술을 포함하는 임의의 적당한 금속 충전 공정일 수 있지만, 이들로만 한정되는 것은 아니다. 여러 실시예에 있어서, PVD(physical vapor deposition, 즉 스퍼터링) 또는 화학 증착 공정은 전기 전도성 재료로써 복수의 구멍(104)을 충전하기 이전에 전기 전도성 층을 형성하도록, 상기 전기 전도성 재료로써 복수의 구멍(104)의 내부 벽부를 코팅하도록 사용될 수 있다. 다른 실시예에 있어서, 전기 전도성 층의 증착은 무전해 도금 공정을 포함하거나 또는 전해 도금 공정을 포함할 수 있다. 이러한 실시예에 있어서, 시드 층은 전기 전도성 재료가 놓이기 이전에 복수의 구멍(104)의 내부 벽부에 형성될 수 있다. 예를 들면, 시드 층이 증착될 수 있으며, 이어서 복수의 구멍(104)의 내부 벽부에 전기 전도성 층이 형성되도록, 구리 증착 공정이 뒤따른다. 여러 충전 공정이 복수의 구멍(104)을 충전하기 이전에 전기 전도성 층의 형성부를 포함할 수 있을지라도, 전기 전도성 층의 형성부는 여러 실시예에서 필수적이지 않을 수 있다. 예를 들면, 진공 방법이 복수의 구멍(104)을 충전하도록 사용될 수 있을 때, 전기 전도성 층의 도금이 제거될 수 있다.

도 4a - 도 4c는 전기 전도성 재료로써 복수의 구멍(104)을 충전하는 공정을 단면으로 개략적으로 나타낸 도면이다. 복수의 구멍(104)이 전기 전도성 재료로 충전될 때, 상기 전기 전도성 재료는 복수의 구멍(104)과 엣칭 백되는 본딩 층(108)의 부분을 완전하게 충전할 수 있다. 전기 전도성 재료의 적어도 일부가 본딩 층(108)으로부터 뻗어있는, 유리 기판(102)의 제1 면(11)으로부터 길이(l)로 돌출할 수 있도록, 복수의 비아(400)를 유리 기판(102)에 형성한다. 도 4a에 도시된 바와 같이, 여러 실시예에 있어서, 습식-엣칭 공정이 사용될 때처럼, 전기 전도성 재료는, 비아(400)가 유리 기판(102)의 제1 면(110)으로부터 돌출하는 전기 전도성 재료의 한 부분을 포함하도록, 엣칭 공정에 의해 만들어진 버섯-형상의 보이드를 충전할 수 있다.

다른 실시예에 있어서, 도 4b 및 도 4c에 도시된 실시예에서 처럼, 엣칭 공정은 일 방향성 보이드를 형성할 수 있다. 예를 들면, 건식-엣칭 공정이 사용될 때, 본딩 층은, 유리 기판(102)의 제1 면(110)을 넘어 측방향으로 뻗어있지 않도록, 하나의 방향으로 단지 엣칭될 수 있다. 이에 따라, 전기 전도성 재료는, 도 4b 및 도 4c에 도시된 바와 같이, 기둥-형상의 비아(400)를 초래하는 기둥-형상의 보이드를 형성할 수 있다. 달리 말하자면, 비아(400)는 유리 기판(102)의 제1 면(110)과 실질적으로 수직인 방향으로 상기 유리 기판(102)의 제1 면(110)으로부터 뻗어있는 실질적으로 평행한 면을 구비한 실린더 형상을 구비할 수 있다. 건식-엣칭 공정이 정지 층처럼 유리 캐리어(106)의 제1 면(114)을 사용하는 실시예에 있어서, 본딩 층(108)은 도 4b에 도시된 바와 같이, 상기 본딩 층(108)의 두께(t)와 동일한 길이(l)로 엣칭되고 그리고 기둥-형상의 비아(400)가 유리 기판(102)의 제1 면(100)으로부터 길이(l)로 뻗어있을 수 있다. 건식-엣칭 공정이 시간 제어될 때, 본딩 층(108)은 도 4c에 도시된 바와 같이, 상기 본딩 층(108)으로의 길이(l)로 엣칭 백될 수 있고, 상기 본딩 층에서 길이(l)가 상기 본딩 층(108)의 두께(t)보다 더 작으며, 그리고 기둥-형상의 비아(400)가 유리 기판(102)의 제1 면(100)으로부터 길이(l)로 뻗어있을 수 있다.

복수의 구멍(104)이 일단 전기 전도성 재료(400)로 충전된다면, 도 5a - 도 5c에 도시된 바와 같이, 유리 기판(102)은 본딩 층(108) 및 유리 캐리어(106)로부터 디-본딩될 수 있다. 디-본딩은 임의의 적당한 공정을 사용하여 실행될 수 있다. 예를 들면, 본딩 층(108)이 UV-경화된 접착제를 포함하는 실시예에 있어서, 레이저는 접착제와 유리 기판(102) 사이의 본딩부를 부수도록 사용될 수 있다. 다른 레이저 및 베이킹 방법이 유리 기판(102)으로부터 본딩 층(108)을 분리하도록 사용될 수 있다. 대안적으로 또는 부가적으로, 다이싱(dicing) 테이프는 유리 캐리어(106)로부터 유리 기판(102)을 디-본딩하도록, 레이저를 사용하기 이전에 디-본딩 공정 동안에 상기 유리 기판에 적용될 수 있다. 여러 실시예에 있어서, 유리 캐리어(106)는 먼저 본딩 층(108)으로부터 디-본딩될 수 있고, 그리고 이후에 상기 본딩 층(108)은 복수의 비아(400)를 포함한 유리 기판(102)으로부터 제거될 수 있다.

다양한 실시예에 있어서, 디-본딩 공정은 복수의 비아(400)를 포함한 유리 기판(102) 상에 실질적으로 접착제 잔류물을 남기지 않는다. 예를 들면, 디-본딩 공정은 디-테이핑(de-taping) 테이프(3M가 제조)가 유리 기판(102)의 제1 면(110)으로부터 접착제를 벗겨내도록 사용되는 단계를 포함할 수 있다.

도 5a는 디-본딩 공정 동안의 도 4a의 실시예를 나타내고 있다. 특히, 복수의 비아(400)은, 유리 기판(102)이 디-본딩될 때, 상기 유리 기판(102)의 제1 면(110)으로부터 돌출한다. 본딩 층(108)이 길이(l)로 엣칭된 실시예에 있어서, 전기 전도성 재료는 유리 기판(102)의 제1 면(110)으로부터 길이(l)로 돌출한다. 이와 비슷하게, 도 5b 및 도 5c는 디-본딩 공정 동안의, 도 4b 및 도 4c 각각의 실시예를 나타내고 있다. 도 5b 및 도 5c에 있어서, 복수의 비아(400)가 기둥 형상을 취하고, 그리고 유리 기판(102)의 제1 면(100)으로부터 뻗어있다. 본딩 층(108)이 상기 본딩 층(108)으로 길이(l)로 엣칭되는 실시예에 있어서, 기둥은 유리 기판(102)의 제1 면(110)으로부터 길이(l)로 뻗어있다. 예를 들면, 도 5b에 있어서, 길이(l)는 본딩 층의 두께(t)와 동일하다. 도 5c에 있어서, 길이(l)는 본딩 층의 두께(t) 보다 작다.

본 발명의 실시예에 의하면 반도체 산업에서의 현 제조 공정에 레버리지를 도입하면서 얇은 유리 기판에 관통-유리 비아가 형성될 수 있다는 것을 알 수 있을 것이다. 특히, 다양한 실시예에 의해, 유리 기판이 조정/처리되도록 유리 캐리어에 제거가능하게 결합될 수 있다. 다양한 실시예에 있어서, 본딩 층의 엣칭 백은 또한 유리 기판 및 유리 캐리어에 레버리지를 도입하여 부가적인 마스크 및/또는 정지 층의 필요성을 감소시킴으로써 또는 심지어 상기 필요성을 없게 함으로써 엣칭 공정을 간략하게 한다.

당업자라면 청구범위의 범주 및 사상 내에서 본 명세서에 기재된 실시예에 대한 다양한 변경 및 수정이 행해질 수 있음을 알 수 있을 것이다. 따라서, 본 명세서에 기재된 다양한 실시예에 대한 여러 변경 및 수정이 행해진다면, 이러한 변경 및 수정은 첨부된 청구범위의 범주 내에서 행해진 것임을 알 수 있을 것이다.

Claims (20)

- 기판에 복수의 비아를 제조하는 방법으로서,

본딩 층으로써 캐리어의 제1 면에 복수의 구멍을 포함한 상기 기판의 제1 면을 본딩하는 단계; 및

상기 기판에서의 복수의 구멍을 통해 깊이(d)로 본딩 층을 엣칭하는 단계; 및

복수의 비아를 형성하도록 재료로써 복수의 구멍을 충전하는 단계;를 포함하고,

상기 본딩 층은 상기 기판의 제1 면과 상기 캐리어의 상기 제1 면 사이의 두께(t)를 갖고 그리고 복수의 구멍 중 적어도 수개의 구멍으로 뻗어있어 유리 기판의 상기 제1 면으로부터 높이(h)를 갖는 접착제 플러그를 형성하고,

상기 깊이(d)는 상기 두께(t)와 상기 높이(h)의 합보다 작거나 상기 합과 동일한, 기판에 복수의 비아를 제조하는 방법. - 청구항 1에 있어서,

펄스 레이저 빔을 사용하여 드릴링함으로써, 상기 기판에 복수의 구멍을 형성하는 단계를 더 포함하는, 기판에 복수의 비아를 제조하는 방법. - 청구항 1 또는 2에 있어서,

본딩 층을 엣칭하는 단계는 습식 엣칭 공정을 사용하는 단계를 포함하는, 기판에 복수의 비아를 제조하는 방법. - 청구항 1 또는 2에 있어서,

상기 본딩 층을 엣칭하는 단계는 건식 엣칭 공정을 사용하는 단계를 포함하는, 기판에 복수의 비아를 제조하는 방법. - 청구항 1 내지 4 중 어느 한 항에 있어서,

상기 재료는 상기 본딩 층으로 길이(l)로 뻗어있는 전기 전도성 재료이고, 상기 길이(l)는 상기 깊이(d)와 상기 높이(h)의 차이와 동일하며, 그리고

상기 기판에 복수의 비아를 제조하는 방법은 상기 캐리어 및 상기 본딩 층으로부터 복수의 비아를 포함한 상기 기판을 디-본딩하는 단계를 더 포함하며, 상기 복수의 비아를 형성하는 전기 전도성 재료의 일부가 상기 기판의 상기 제1 면으로부터 돌출하는, 기판에 복수의 비아를 제조하는 방법. - 청구항 5에 있어서,

상기 깊이(d)는, 상기 길이(l)가 상기 두께(t)와 동일하도록, 상기 본딩 층의 두께(t) 및 상기 높이(h)의 합과 동일한, 기판에 복수의 비아를 제조하는 방법. - 기판에 복수의 비아를 제조하는 방법으로서,

본딩 층을 갖는 캐리어의 제1 면에, 복수의 구멍을 포함한 상기 기판의 제1 면을 본딩하는 단계;

습식 엣칭 공정을 사용하여, 상기 기판의 복수의 구멍을 통해 깊이(d)로 상기 본딩 층을 엣칭하는 단계;

복수의 비아를 유리에 형성하도록 전기 전도성 재료로써 복수의 구멍을 충전하는 단계; 및

상기 캐리어 및 상기 본딩 층으로부터 복수의 비아를 포함한 상기 기판을 디-본딩하는 단계;를 포함하고,

상기 본딩 층은 상기 캐리어의 상기 제1 면과 상기 기판의 상기 제1 면 사이의 두께(t)를 갖고,

상기 전기 전도성 재료는 길이(l) 만큼 상기 본딩 층으로 뻗어있고, 그리고 상기 길이(l)는 상기 두께(t)보다 더 작으며,

상기 전기 전도성 재료는 상기 기판의 상기 제1 면으로부터 돌출하는, 기판에 복수의 비아를 제조하는 방법. - 청구항 7에 있어서,

상기 기판은 100 um 이하의 두께를 갖는, 기판에 복수의 비아를 제조하는 방법. - 청구항 8에 있어서,

상기 기판의 상기 두께는 100 um 보다 작은, 기판에 복수의 비아를 제조하는 방법. - 청구항 7 내지 9 중 어느 한 항에 있어서,

상기 습식 엣칭 공정은 HF 및 아세톤으로부터 선택된 솔벤트에 상기 본딩 층을 노출시키는 단계를 포함하는, 기판에 복수의 비아를 제조하는 방법. - 청구항 10에 있어서,

상기 본딩 층은, 상기 기판이 상기 엣칭 공정용 경질의 마스크이도록, 상기 기판을 통해 솔벤트에 노출되는, 기판에 복수의 비아를 제조하는 방법. - 청구항 11에 있어서,

상기 기판은 100 um 이하의 두께를 갖는, 기판에 복수의 비아를 제조하는 방법. - 청구항 7 내지 12 중 어느 한 항에 있어서,

상기 전기 전도성 재료는 구리 재료를 포함하는, 기판에 복수의 비아를 제조하는 방법. - 청구항 7 내지 13 중 어느 한 항에 있어서,

3차원 스택된 집적 회로에 복수의 비아를 포함한 상기 기판을 통합하는 단계를 더 포함하는, 기판에 복수의 비아를 제조하는 방법. - 기판에 복수의 비아를 제조하는 방법으로서,

본딩 층을 사용하여 캐리어의 제1 면에, 복수의 구멍을 포함한 상기 기판의 제1 면을 본딩하는 단계;

건식 엣칭 공정을 사용하여, 상기 기판의 복수의 구멍을 통해 깊이(d)로 상기 본딩 층을 엣칭하는 단계;

상기 기판에 복수의 비아를 형성하도록 전기 전도성 재료로써 복수의 구멍을 충전하는 단계; 및

상기 캐리어 및 상기 본딩 층으로부터 복수의 비아를 포함한 상기 기판을 디-본딩하는 단계;를 포함하고,

상기 본딩 층은 상기 캐리어의 상기 제1 면과 상기 기판의 상기 제1 면 사이의 두께(t)를 갖고,

상기 깊이(d)는 엣칭이 상기 기판의 상기 제1 면으로부터 상기 본딩 층으로 뻗어있는 길이(l)와, 복수의 구멍 중 적어도 수개의 구멍으로 뻗어있는 본딩 층에 의해 형성된 접착제 플러그의 높이(h)의 합과 동일하며, 상기 길이(l)는 상기 두께(t)와 동일하고, 상기 캐리어의 상기 제1 면은 상기 건식 엣칭 공정을 위한 정지 층이고,

상기 전기 전도성 재료는 상기 본딩 층을 통해 상기 캐리어의 상기 제1 면으로 뻗어있고,

상기 전기 전도성 재료는 유리 기판의 상기 제1 면으로부터 상기 길이(l)로 뻗어있는 기둥을 형성하는, 기판에 복수의 비아를 제조하는 방법. - 청구항 15에 있어서,

상기 건식 엣칭 공정은 O2 또는 아르곤-함유 가스 중 어느 하나로부터 발생된 플라즈마에 상기 본딩 층을 노출시키는 단계를 포함하는, 기판에 복수의 비아를 제조하는 방법. - 청구항 15 또는 16에 있어서,

상기 전기 전도성 재료는 구리를 포함하는, 기판에 복수의 비아를 제조하는 방법. - 청구항 15 내지 17 중 어느 한 항에 있어서,

상기 기둥 중 각각의 기둥은 상기 기판의 상기 제1 면으로부터 뻗어있는 실린더를 포함하고, 그리고 상기 기판의 상기 제1 면과 실질적으로 수직인 방향으로 뻗어있는, 기판에 복수의 비아를 제조하는 방법. - 청구항 15 내지 18 중 어느 한 항에 있어서,

상기 기판은 100 um 이하의 두께를 갖는, 기판에 복수의 비아를 제조하는 방법. - 청구항 19에 있어서,

상기 기판의 상기 두께는 100 um 보다 작은, 기판에 복수의 비아를 제조하는 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201461986370P | 2014-04-30 | 2014-04-30 | |

| US61/986,370 | 2014-04-30 | ||

| PCT/US2015/028200 WO2015168236A1 (en) | 2014-04-30 | 2015-04-29 | Etch back processes of bonding material for the manufacture of through-glass vias |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20160145801A true KR20160145801A (ko) | 2016-12-20 |

Family

ID=53177892

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020167032591A KR20160145801A (ko) | 2014-04-30 | 2015-04-29 | 관통-유리 비아의 제조를 위한 본딩 재료의 엣칭 백 공정 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US9263300B2 (ko) |

| EP (1) | EP3138120B1 (ko) |

| JP (1) | JP2017520906A (ko) |

| KR (1) | KR20160145801A (ko) |

| CN (1) | CN106470953B (ko) |

| TW (1) | TWI659002B (ko) |

| WO (1) | WO2015168236A1 (ko) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106470953B (zh) * | 2014-04-30 | 2019-03-12 | 康宁股份有限公司 | 用于制造穿通玻璃通孔的接合材料的回蚀工艺 |

| US10410883B2 (en) | 2016-06-01 | 2019-09-10 | Corning Incorporated | Articles and methods of forming vias in substrates |

| US10134657B2 (en) | 2016-06-29 | 2018-11-20 | Corning Incorporated | Inorganic wafer having through-holes attached to semiconductor wafer |

| US10794679B2 (en) | 2016-06-29 | 2020-10-06 | Corning Incorporated | Method and system for measuring geometric parameters of through holes |

| CN108231646A (zh) * | 2016-12-13 | 2018-06-29 | 中芯国际集成电路制造(上海)有限公司 | 一种半导体器件的制造方法 |

| US10580725B2 (en) | 2017-05-25 | 2020-03-03 | Corning Incorporated | Articles having vias with geometry attributes and methods for fabricating the same |

| US11078112B2 (en) | 2017-05-25 | 2021-08-03 | Corning Incorporated | Silica-containing substrates with vias having an axially variable sidewall taper and methods for forming the same |

| US11554984B2 (en) | 2018-02-22 | 2023-01-17 | Corning Incorporated | Alkali-free borosilicate glasses with low post-HF etch roughness |

| US11148935B2 (en) | 2019-02-22 | 2021-10-19 | Menlo Microsystems, Inc. | Full symmetric multi-throw switch using conformal pinched through via |

| WO2021167787A1 (en) * | 2020-02-18 | 2021-08-26 | Corning Incorporated | Etching of glass surfaces to reduce electrostatic charging during processing |

| CN117747504B (zh) * | 2023-12-20 | 2024-07-19 | 西安赛富乐斯半导体科技有限公司 | 粘合胶层厚度调整方法 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006161124A (ja) * | 2004-12-09 | 2006-06-22 | Canon Inc | 貫通電極の形成方法 |

| US7425507B2 (en) | 2005-06-28 | 2008-09-16 | Micron Technology, Inc. | Semiconductor substrates including vias of nonuniform cross section, methods of forming and associated structures |

| JP4889974B2 (ja) * | 2005-08-01 | 2012-03-07 | 新光電気工業株式会社 | 電子部品実装構造体及びその製造方法 |

| US7429529B2 (en) * | 2005-08-05 | 2008-09-30 | Farnworth Warren M | Methods of forming through-wafer interconnects and structures resulting therefrom |

| JP2007067031A (ja) * | 2005-08-30 | 2007-03-15 | Tdk Corp | 配線基板の製造方法 |

| US8455357B2 (en) * | 2008-10-10 | 2013-06-04 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method of plating through wafer vias in a wafer for 3D packaging |

| JP5201048B2 (ja) * | 2009-03-25 | 2013-06-05 | 富士通株式会社 | 半導体装置とその製造方法 |

| US20110229687A1 (en) | 2010-03-19 | 2011-09-22 | Qualcomm Incorporated | Through Glass Via Manufacturing Process |

| US8411459B2 (en) | 2010-06-10 | 2013-04-02 | Taiwan Semiconductor Manufacturing Company, Ltd | Interposer-on-glass package structures |

| JP5729932B2 (ja) * | 2010-07-22 | 2015-06-03 | キヤノン株式会社 | 基板貫通孔内への金属充填方法 |

| CN106425129B (zh) | 2010-11-30 | 2018-07-17 | 康宁股份有限公司 | 在玻璃中形成高密度孔阵列的方法 |

| TWI547454B (zh) | 2011-05-31 | 2016-09-01 | 康寧公司 | 於玻璃中高速製造微孔洞的方法 |

| KR101485140B1 (ko) * | 2011-07-14 | 2015-01-22 | 시마쯔 코포레이션 | 플라즈마 처리 장치 |

| JP6176253B2 (ja) | 2012-09-07 | 2017-08-09 | 旭硝子株式会社 | インターポーザ用の中間品を製造する方法およびインターポーザ用の中間品 |

| CN105228788A (zh) | 2012-11-29 | 2016-01-06 | 康宁股份有限公司 | 用于激光钻孔基材的牺牲覆盖层及其方法 |

| US9425125B2 (en) * | 2014-02-20 | 2016-08-23 | Altera Corporation | Silicon-glass hybrid interposer circuitry |

| CN106470953B (zh) * | 2014-04-30 | 2019-03-12 | 康宁股份有限公司 | 用于制造穿通玻璃通孔的接合材料的回蚀工艺 |

-

2015

- 2015-04-29 CN CN201580036200.5A patent/CN106470953B/zh not_active Expired - Fee Related

- 2015-04-29 US US14/699,393 patent/US9263300B2/en not_active Expired - Fee Related

- 2015-04-29 JP JP2016565202A patent/JP2017520906A/ja active Pending

- 2015-04-29 KR KR1020167032591A patent/KR20160145801A/ko unknown

- 2015-04-29 WO PCT/US2015/028200 patent/WO2015168236A1/en active Application Filing

- 2015-04-29 EP EP15722629.1A patent/EP3138120B1/en not_active Not-in-force

- 2015-04-30 TW TW104113956A patent/TWI659002B/zh not_active IP Right Cessation

-

2016

- 2016-02-02 US US15/013,241 patent/US20160155696A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| EP3138120A1 (en) | 2017-03-08 |

| CN106470953B (zh) | 2019-03-12 |

| TW201600484A (zh) | 2016-01-01 |

| WO2015168236A1 (en) | 2015-11-05 |

| CN106470953A (zh) | 2017-03-01 |

| EP3138120B1 (en) | 2018-04-18 |

| TWI659002B (zh) | 2019-05-11 |

| US9263300B2 (en) | 2016-02-16 |

| US20160155696A1 (en) | 2016-06-02 |

| US20150318187A1 (en) | 2015-11-05 |

| JP2017520906A (ja) | 2017-07-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20160145801A (ko) | 관통-유리 비아의 제조를 위한 본딩 재료의 엣칭 백 공정 | |

| US7833895B2 (en) | TSVS having chemically exposed TSV tips for integrated circuit devices | |

| JP4919984B2 (ja) | 電子デバイスパッケージとその形成方法 | |

| US20160079149A1 (en) | Wiring board provided with through electrode, method for manufacturing same and semiconductor device | |

| JP2007053149A (ja) | 半導体ウエハ及びその製造方法 | |

| US20100044873A1 (en) | Semiconductor device and method of manufacturing the same | |

| JP2004158705A (ja) | 微細孔への金属充填方法及びその方法により形成された金属が充填した微細孔を備えたワーク | |

| JP6261733B2 (ja) | オプトエレクトロニクス部品およびその製造方法 | |

| JP2005129888A (ja) | センサ装置、センサシステム、センサ装置の製造方法及びセンサシステムの製造方法 | |

| JP4020367B2 (ja) | 半導体装置の製造方法 | |

| JP2009117771A (ja) | 半導体パッケージの製造方法 | |

| WO2019167918A1 (ja) | 複合基板、および圧電素子 | |

| EP3039710B1 (en) | Wafer dicing method for improving die packaging quality | |

| JP2009259876A (ja) | 半導体装置および半導体装置の製造方法 | |

| US9530692B2 (en) | Method of forming through wiring | |

| JP6585526B2 (ja) | 配線基板の製造方法 | |

| JP2005039078A (ja) | 薄板基板構造形成用ウエーハ基板、この製造方法およびmems素子の製造方法 | |

| TWI594342B (zh) | 製造半導體封裝的方法 | |

| JP2009111433A (ja) | 貫通電極付き半導体基板の製造方法、貫通電極付き半導体デバイスの製造方法 | |

| JP2019153902A (ja) | 複合基板の製造方法 | |

| US20230372970A1 (en) | Transducer device and method of manufacture | |

| US20230381815A1 (en) | Transducer device and method of manufacture | |

| JP2005072489A (ja) | 半導体装置の製造方法および半導体装置 | |

| JP2011009781A (ja) | 貫通電極付き半導体デバイスの製造方法 | |

| KR20200124623A (ko) | 용융 본딩 및 본딩 분리를 위한 저밀도 실리콘 산화물에 대한 방법 및 구조물 |