KR20160052329A - 선택 성장 방법 및 기판 처리 장치 - Google Patents

선택 성장 방법 및 기판 처리 장치 Download PDFInfo

- Publication number

- KR20160052329A KR20160052329A KR1020150147154A KR20150147154A KR20160052329A KR 20160052329 A KR20160052329 A KR 20160052329A KR 1020150147154 A KR1020150147154 A KR 1020150147154A KR 20150147154 A KR20150147154 A KR 20150147154A KR 20160052329 A KR20160052329 A KR 20160052329A

- Authority

- KR

- South Korea

- Prior art keywords

- film

- gas

- metal

- thinned

- selective growth

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 70

- 239000000758 substrate Substances 0.000 title claims abstract description 24

- 229910052751 metal Inorganic materials 0.000 claims abstract description 36

- 239000002184 metal Substances 0.000 claims abstract description 36

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims abstract description 18

- 238000002485 combustion reaction Methods 0.000 claims abstract description 15

- 229910052814 silicon oxide Inorganic materials 0.000 claims abstract description 12

- 239000010409 thin film Substances 0.000 claims abstract description 6

- 239000003054 catalyst Substances 0.000 claims abstract description 3

- 239000010408 film Substances 0.000 claims description 193

- 239000007789 gas Substances 0.000 claims description 101

- 229910052799 carbon Inorganic materials 0.000 claims description 52

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 50

- 230000008569 process Effects 0.000 claims description 27

- 229930195733 hydrocarbon Natural products 0.000 claims description 18

- 150000002430 hydrocarbons Chemical class 0.000 claims description 18

- 230000007246 mechanism Effects 0.000 claims description 18

- 229910052710 silicon Inorganic materials 0.000 claims description 18

- 239000004215 Carbon black (E152) Substances 0.000 claims description 17

- 229910052736 halogen Inorganic materials 0.000 claims description 17

- 150000002367 halogens Chemical class 0.000 claims description 17

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 16

- 239000010703 silicon Substances 0.000 claims description 16

- 238000010438 heat treatment Methods 0.000 claims description 10

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 9

- 150000008282 halocarbons Chemical class 0.000 claims description 9

- 229910052760 oxygen Inorganic materials 0.000 claims description 9

- 239000001301 oxygen Substances 0.000 claims description 9

- 229910052707 ruthenium Inorganic materials 0.000 claims description 5

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 claims description 3

- 239000002994 raw material Substances 0.000 claims description 3

- 229910052804 chromium Inorganic materials 0.000 claims description 2

- 229910052802 copper Inorganic materials 0.000 claims description 2

- 238000000354 decomposition reaction Methods 0.000 claims description 2

- 229910052733 gallium Inorganic materials 0.000 claims description 2

- 229910052732 germanium Inorganic materials 0.000 claims description 2

- 229910052737 gold Inorganic materials 0.000 claims description 2

- 229910052735 hafnium Inorganic materials 0.000 claims description 2

- 229910052738 indium Inorganic materials 0.000 claims description 2

- 229910052741 iridium Inorganic materials 0.000 claims description 2

- 229910052742 iron Inorganic materials 0.000 claims description 2

- 229910052748 manganese Inorganic materials 0.000 claims description 2

- 229910052759 nickel Inorganic materials 0.000 claims description 2

- 229910052762 osmium Inorganic materials 0.000 claims description 2

- 229910052763 palladium Inorganic materials 0.000 claims description 2

- 229910052697 platinum Inorganic materials 0.000 claims description 2

- 229910052703 rhodium Inorganic materials 0.000 claims description 2

- 229910052713 technetium Inorganic materials 0.000 claims description 2

- 229910052718 tin Inorganic materials 0.000 claims description 2

- 229910052719 titanium Inorganic materials 0.000 claims description 2

- 229910052720 vanadium Inorganic materials 0.000 claims description 2

- 229910052725 zinc Inorganic materials 0.000 claims description 2

- 229910052726 zirconium Inorganic materials 0.000 claims description 2

- 239000003463 adsorbent Substances 0.000 claims 1

- 229910052750 molybdenum Inorganic materials 0.000 claims 1

- 229910052758 niobium Inorganic materials 0.000 claims 1

- 239000004065 semiconductor Substances 0.000 abstract description 8

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 35

- 229910052721 tungsten Inorganic materials 0.000 description 35

- 239000010937 tungsten Substances 0.000 description 35

- 229910004298 SiO 2 Inorganic materials 0.000 description 33

- 239000000460 chlorine Substances 0.000 description 18

- 235000012431 wafers Nutrition 0.000 description 15

- 238000006243 chemical reaction Methods 0.000 description 9

- 239000011261 inert gas Substances 0.000 description 8

- 239000006185 dispersion Substances 0.000 description 7

- 238000011534 incubation Methods 0.000 description 6

- 238000003860 storage Methods 0.000 description 6

- 229910017052 cobalt Inorganic materials 0.000 description 5

- 239000010941 cobalt Substances 0.000 description 5

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 5

- 235000012239 silicon dioxide Nutrition 0.000 description 5

- 229910003481 amorphous carbon Inorganic materials 0.000 description 4

- 239000010453 quartz Substances 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- KAKZBPTYRLMSJV-UHFFFAOYSA-N Butadiene Chemical compound C=CC=C KAKZBPTYRLMSJV-UHFFFAOYSA-N 0.000 description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 2

- 239000010953 base metal Substances 0.000 description 2

- 238000006555 catalytic reaction Methods 0.000 description 2

- 229910052801 chlorine Inorganic materials 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- XREKLQOUFWBSFH-UHFFFAOYSA-N dimethyl 2-acetylbutanedioate Chemical compound COC(=O)CC(C(C)=O)C(=O)OC XREKLQOUFWBSFH-UHFFFAOYSA-N 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- ZCYVEMRRCGMTRW-UHFFFAOYSA-N 7553-56-2 Chemical compound [I] ZCYVEMRRCGMTRW-UHFFFAOYSA-N 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000006978 adaptation Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000003197 catalytic effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 229910052681 coesite Inorganic materials 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229910052906 cristobalite Inorganic materials 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- 125000005842 heteroatom Chemical group 0.000 description 1

- 239000011630 iodine Substances 0.000 description 1

- 229910052740 iodine Inorganic materials 0.000 description 1

- 239000011553 magnetic fluid Substances 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- OOXOBWDOWJBZHX-UHFFFAOYSA-N n-(dimethylaminosilyl)-n-methylmethanamine Chemical compound CN(C)[SiH2]N(C)C OOXOBWDOWJBZHX-UHFFFAOYSA-N 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000001737 promoting effect Effects 0.000 description 1

- 229910052702 rhenium Inorganic materials 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- FZHAPNGMFPVSLP-UHFFFAOYSA-N silanamine Chemical compound [SiH3]N FZHAPNGMFPVSLP-UHFFFAOYSA-N 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 229910052682 stishovite Inorganic materials 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- 229910052905 tridymite Inorganic materials 0.000 description 1

- 238000003466 welding Methods 0.000 description 1

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

- C30B25/18—Epitaxial-layer growth characterised by the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

-

- H01L21/2018—

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/04—Coating on selected surface areas, e.g. using masks

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/26—Deposition of carbon only

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/30—Deposition of compounds, mixtures or solid solutions, e.g. borides, carbides, nitrides

- C23C16/40—Oxides

- C23C16/401—Oxides containing silicon

- C23C16/402—Silicon dioxide

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/52—Controlling or regulating the coating process

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/56—After-treatment

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

- C30B25/16—Controlling or regulating

- C30B25/165—Controlling or regulating the flow of the reactive gases

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02115—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material being carbon, e.g. alpha-C, diamond or hydrogen doped carbon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02205—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition

- H01L21/02208—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si

- H01L21/02211—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound being a silane, e.g. disilane, methylsilane or chlorosilane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02299—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment

- H01L21/02304—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment formation of intermediate layers, e.g. buffer layers, layers to improve adhesion, lattice match or diffusion barriers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02299—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment

- H01L21/02312—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment treatment by exposure to a gas or vapour

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02527—Carbon, e.g. diamond-like carbon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02551—Group 12/16 materials

- H01L21/02554—Oxides

-

- H01L21/205—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28568—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table the conductive layers comprising transition metals

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Mechanical Engineering (AREA)

- Inorganic Chemistry (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical Vapour Deposition (AREA)

- Formation Of Insulating Films (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

본 발명은 보다 미세한 반도체 장치 구조에의 적응이 가능한 선택 성장 방법을 제공한다. 절연막과 금속이 노출되어 있는 하지 위에 박막을 선택적으로 성장시키는 선택 성장 방법은, 하지의 금속을 촉매로 사용하여, 하지의 금속 위에 연소에 의해 감막하는 막을 선택적으로 성장시키는 공정(스텝 1)과, 연소에 의해 감막하는 막을 연소시키면서, 하지의 절연막 위에, 실리콘 산화물 막을 선택적으로 성장시키는 공정(스텝 2)을 구비한다.

Description

본 발명은 선택 성장 방법 및 기판 처리 장치에 관한 것이다.

하지 위에 박막을 선택적으로 성장시키는 선택 성장 방법으로서는, 하지 결정면의 면 방위를 이용한 단결정의 호모 에피택셜 성장법 및 헤테로 에피택셜 성장법이 알려져 있다. 예를 들어, 특허문헌 1에는, 하지인 단결정 실리콘막 위에 실리콘 에피택셜층을 성장시키는 호모 에피택셜 성장법이 기재되어 있다.

또한, 예를 들어 특허문헌 2에는, 하지인 단결정 실리콘막 위에 실리콘 게르마늄 에피택셜층을 성장시키는 헤테로 에피택셜 성장법이 기재되어 있다.

그러나, 현재의 호모 에피택셜 성장법이나 헤테로 에피택셜 성장법에서는, 선택 성장시키는 하지가 한정되는 것, 계면의 청정화가 필요한 것, 고온 프로세스가 필요한 것과 같은 제약이 있어, 현재 요구되고 있는 보다 미세한 반도체 장치 구조에의 적응은 곤란하다는 사정이 있다.

본 발명은 보다 미세한 반도체 장치 구조에의 적응이 가능한 선택 성장 방법 및 그 선택 성장 방법을 실시하는 것이 가능한 기판 처리 장치를 제공한다.

본 발명의 제1 형태에 관한 선택 성장 방법은, 절연막과 금속막이 노출되어 있는 하지 위에, 박막을 선택적으로 성장시키는 선택 성장 방법으로서, 상기 하지의 금속을 촉매로 사용하여, 상기 하지의 금속막 위에, 연소에 의해 감막하는 막을 선택적으로 성장시키는 제1 공정과, 상기 연소에 의해 감막하는 막을 연소시키면서, 상기 하지의 절연막 위에, 실리콘 산화물 막을 선택적으로 성장시키는 제2 공정을 포함한다.

본 발명의 제2 형태에 관한 기판 처리 장치는, 피처리체의, 절연막과 금속막이 노출되어 있는 피처리면 위에 박막을 선택적으로 성장시키는 기판 처리 장치로서, 상기 피처리체를 수용하는 처리실과, 상기 처리실 내에, 탄화수소 가스, 할로겐 가스 또는 할로겐화 탄화수소 가스, 실리콘을 포함하는 가스 및 산소를 포함하는 가스를 적어도 공급하는 가스 공급 기구와, 상기 처리실 내를 가열하는 가열 장치와, 상기 처리실 내를 배기하는 배기 기구와, 상기 가스 공급 기구, 상기 가열 장치, 상기 배기 기구를 제어하는 컨트롤러를 포함하고, 상기 컨트롤러가, 상기 처리실 내에서, 제1 형태에 관한 선택 성장 방법이 상기 피처리체에 대하여 실시되도록, 상기 가스 공급 기구, 상기 가열 장치, 상기 배기 기구를 제어한다.

본 발명에 의하면, 보다 미세한 반도체 장치 구조에의 적응이 가능한 선택 성장 방법 및 그 선택 성장 방법을 실시하는 것이 가능한 기판 처리 장치를 제공할 수 있다.

도 1은 본 발명의 제1 실시 형태에 따른 선택 성장 방법의 일례를 나타내는 흐름도이다.

도 2a 내지 도 2e는 도 1에 도시하는 시퀀스 중의 피처리체의 상태를 개략적으로 도시하는 단면도이다.

도 3은 처리 시간과 카본막의 막 두께와의 관계를 도시하는 도면이다.

도 4는 카본막을 제거한 상태를 도시하는 단면도이다.

도 5는 본 발명의 제2 실시 형태에 따른 선택 성장 방법의 일례를 나타내는 흐름도이다.

도 6a 내지 도 6h는 도 5에 도시하는 시퀀스 중의 피처리체의 상태를 개략적으로 도시하는 단면도이다.

도 7은 카본막을 제거한 상태를 도시하는 단면도이다.

도 8은 본 발명의 제3 실시 형태에 따른 선택 성장 방법의 일례를 나타내는 흐름도이다.

도 9a 내지 도 9j는 도 8에 도시하는 시퀀스 중의 피처리체의 상태를 개략적으로 도시하는 단면도이다.

도 10은 카본막을 제거한 상태를 도시하는 단면도이다.

도 11은 본 발명의 제4 실시 형태에 따른 기판 처리 장치의 일례를 개략적으로 도시하는 종단면도이다.

도 2a 내지 도 2e는 도 1에 도시하는 시퀀스 중의 피처리체의 상태를 개략적으로 도시하는 단면도이다.

도 3은 처리 시간과 카본막의 막 두께와의 관계를 도시하는 도면이다.

도 4는 카본막을 제거한 상태를 도시하는 단면도이다.

도 5는 본 발명의 제2 실시 형태에 따른 선택 성장 방법의 일례를 나타내는 흐름도이다.

도 6a 내지 도 6h는 도 5에 도시하는 시퀀스 중의 피처리체의 상태를 개략적으로 도시하는 단면도이다.

도 7은 카본막을 제거한 상태를 도시하는 단면도이다.

도 8은 본 발명의 제3 실시 형태에 따른 선택 성장 방법의 일례를 나타내는 흐름도이다.

도 9a 내지 도 9j는 도 8에 도시하는 시퀀스 중의 피처리체의 상태를 개략적으로 도시하는 단면도이다.

도 10은 카본막을 제거한 상태를 도시하는 단면도이다.

도 11은 본 발명의 제4 실시 형태에 따른 기판 처리 장치의 일례를 개략적으로 도시하는 종단면도이다.

이하, 본 발명의 실시 형태의 몇 가지를, 도면을 참조하여 설명한다. 또한, 전 도면에 걸쳐, 공통 부분에는 공통의 참조 부호를 붙인다.

(제1 실시 형태)

<선택 성장 방법>

도 1은 본 발명의 제1 실시 형태에 따른 선택 성장 방법의 일례를 나타내는 흐름도, 도 2a 내지 도 2e는 도 1에 도시하는 시퀀스 중의 피처리체의 상태를 개략적으로 도시하는 단면도이다.

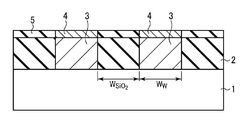

먼저, 도 2a에 도시한 바와 같이, 피처리체로서, 예를 들어 실리콘 웨이퍼(이하, 웨이퍼라고 함)(1)를 준비한다. 웨이퍼(1)의 표면 위에는, 절연막에 의한 구조체와 금속막에 의한 구조체가 형성되어 있다. 도 2a에 도시하는 구조체는, 반도체 집적 회로 장치의 제조 중에 있어서의 구조체를 모방한 것이며, 절연막은, 예를 들어 실리콘 산화물 막, 금속막은, 예를 들어 텅스텐막(3)이다. 실리콘 산화물 막의 일례는, 예를 들어 SiO2막(2)이다. 도 2a에는, SiO2막(2)과 텅스텐막(3)이 교대로 출현하는 패턴이 도시되어 있다. SiO2막(2) 및 텅스텐막(3)의 노출면은 웨이퍼(1)의 피처리면이며, 피처리면은, 박막이 선택적으로 성장되는 하지로 되어 있다.

이어서, 도 1 중의 스텝 1 및 도 2b에 도시한 바와 같이, 하지의 금속, 본 예에서는 텅스텐막(3) 위에, 연소에 의해 감막하는 막을 선택적으로 성장시킨다. 연소에 의해 감막하는 막은, 예를 들어 카본막(4)이며, 카본막(4)은 하지의 금속, 본 예에서는 텅스텐을 촉매로 사용하여, 텅스텐막(3) 위에 선택적으로 성장된다.

도 3은, 처리 시간과 카본막(4)의 막 두께와의 관계를 도시하는 도면이다. 도 3에는, 카본막(4)을 저온에서 SiO2막(2) 위에 성막한 경우(△: LT-Carbon on SiO2)와, 동일하게 카본막(4)을 저온에서 텅스텐막(3) 위에 성막한 경우(●: LT-Carbon on W)가 도시되어 있다. 또한, 카본막(4)의 원료 가스로는, 탄화수소 가스와, 할로겐 가스를 사용하였다. 본 예에서는 탄화수소 가스로서 부타디엔(C4H6) 가스, 할로겐 가스로서 염소(Cl2) 가스를 사용하였다.

도 3에 도시한 바와 같이, C4H6 가스 및 Cl2 가스를 원료 가스로서 사용하여, 카본막(4)을 저온, 예를 들어 350℃의 처리 온도에서 SiO2막(2) 위에 성막한 경우, SiO2막(2) 위에 카본막(4)이 성막되기 시작하는 처리 시간은 약 170 내지 180min 경과 후가 되었다. 이에 반해, 카본막(4)을 350℃의 처리 온도에서 텅스텐막(3) 위에 성막한 경우에는, 처리 시간이 약 30min 경과한 단계에서 카본막(4)이 텅스텐막(3) 위에 성막되기 시작하였다. 즉, 본 예와 같은 카본 성막 처리에서는, 카본막(4)의 SiO2막(2) 위에서의 인큐베이션 시간과, 동일하게 텅스텐막(3) 위에서의 인큐베이션 시간과의 사이에 약 140 내지 150min의 큰 차가 생기는 것으로 판명되었다.

인큐베이션 시간에 큰 차가 생기는 이유의 하나로서, 텅스텐막(3)에는 촉매 작용이 있어, C4H6 가스 중의 C4H6의 흡착과, Cl2 가스의 Cl2 분자의 분해를 촉진시키고 있다고 생각할 수 있다.

텅스텐막(3) 위에서는, 이하의 반응에 의해 아몰퍼스의 카본막이 퇴적된다.

C4H6→ C4H5+H

… (1)

Cl2→2Cl

… (2)

C4H5+Cl → C4H5Cl

… (3)

C4H5Cl +C4H6→아몰퍼스의 카본

… (4)

이에 반해, SiO2막(2) 위에서는, 이하의 반응에 의해 아몰퍼스의 카본막이 퇴적된다.

C4H6+Cl2→ C4H5Cl +HCl

… (5)

C4H5Cl +C4H6→아몰퍼스의 카본

… (6)

상기 반응 중,

(1)+(2)+(3)의 반응은, (5)의 반응과 비교해서 매우 빠르다.

((1)+(2)+(3)>>(5))

(4)의 반응은, (6)의 반응과 동일하다.

((4)=(6))

즉, (1)+(2)+(3)의 반응은, (5)의 반응과 비교해서 매우 빠르기 때문에, SiO2막(2) 위와 텅스텐막(3) 위는, 카본막(4)의 인큐베이션 시간에 차가 발생한다.

따라서, 도 2b에 도시한 바와 같이, 연소에 의해 감막하는 막, 예를 들어 카본막(4)을 텅스텐막(3) 위에 선택적으로 성장시킬 수 있다.

이러한 카본막(4)을 텅스텐막(3) 위에 선택적으로 성장시키는 스텝 1의 처리 조건의 일례는,

C4H6 가스 유량: 200sccm

Cl2 가스 유량: 50sccm

처리 시간: 30 내지 180min

처리 온도: 350℃

처리 압력: 800Pa(약 6Torr)

이다. 또한, C4H6 가스 유량은 100 내지 400sccm의 범위에서 선택되는 것, Cl2 가스 유량은 1 내지 100sccm의 범위에서 선택되는 것, 처리 압력은 1 내지 20Torr(133.3Pa 내지 2666Pa)의 범위에서 선택되는 것이, 실용적인 관점에서 바람직하다.

또한, 스텝 1에서의 처리 시간으로서는, 텅스텐막(3) 위에의 카본막(4)의 인큐베이션 시간 이상, SiO2막(2) 위에의 카본막(4)의 인큐베이션 시간 이하로 설정되는 것이 바람직하다.

이어서, 도 1 중의 스텝 2와 도 2c 및 도 2d에 도시한 바와 같이, 연소에 의해 감막하는 막, 본 예에서는 카본막(4)을 연소시키면서, 하지의 절연막, 본 예에서는 SiO2막(2) 위에 실리콘 산화물 막, 예를 들어 SiO2막(5)을 선택적으로 성장(퇴적)시킨다. SiO2막(5)의 원료 가스의 일례는 아미노실란계 가스, 예를 들어 비스(디메틸아미노)실란(2DMAS), 산화제 가스의 일례는 오존(O3)이다.

스텝 2의 처리 조건의 일례는,

2DMAS 가스 유량: 200sccm

O3 가스 유량: 1000sccm

처리 시간: 30 내지 180min

처리 온도: 350℃

처리 압력: 133.3Pa(1Torr)

이다.

스텝 2에서는, 카본막(4)은 연소에 의해, 그 막 두께를 서서히 감소시켜 가지만, SiO2막(5)은 퇴적에 의해, 그 막 두께를 서서히 증가시켜 간다(도 2c 및 도 2d참조).

또한, 스텝 2에서의 처리 시간으로서는, 서서히 감막하는 카본막(4)의 막 두께와, 서서히 증막하는 SiO2막(5)의 막 두께가, 거의 균형을 이루는 시간으로 설정되는 것이 바람직하다.

이러한 스텝 1, 스텝 2를 구비한 제1 실시 형태에 의하면, 카본막(4) 및 SiO2막(5)을 선택적으로 성장시킬 수 있다. 이 때문에, 도 2e에 도시한 바와 같이, 하지의 텅스텐막(3)의 패턴에 자기 정합한 카본막(4)과, 동일하게 하지의 SiO2막(2)의 패턴에 자기 정합한 SiO2막(5)을 얻을 수 있다.

또한, 제1 실시 형태에 의하면, 카본막(4) 및 SiO2막(5)을 선택 성장시키므로, 리소그래피 공정의 필요가 없다. 이 때문에, 텅스텐막(3)의 폭(Ww) 및 SiO2막(2)의 폭 WSiO2의 양쪽이, 리소그래피의 해상도 한계 이하로 미세화되어 있었다고 해도, 텅스텐막(3) 및 SiO2막(2)의 각각의 위에 카본막(4) 및 SiO2막(5)을 성막할 수 있다.

또한, 카본막(4) 및 SiO2막(5)을 선택 성장시킬 때의 처리 온도는, 예를 들어 350℃와 같이 저온이면 된다.

또한, 카본막(4)은 도 4에 도시하는 바와 같이 제거하는 것도 가능하다. 카본막(4)의 제거에는, 예를 들어 SiO2막(5)의 선택 성장 시에 사용한 산화제 가스를 이용할 수 있다. 카본막(4)을 제거한 경우에는, 하지의 텅스텐막(3) 위에, 텅스텐막(3)의 패턴에 자기 정합한 개공(6)이 얻어진다는 이점을 얻을 수 있다.

또한, 텅스텐막(3)과 같이 금속막 위에 선택적으로 성장시키는 것이 가능하고, 또한 연소에 의해 감막하는 재료로서는, 루테늄을 들 수 있다. 이 때문에, 카본막(4)은, 예를 들어 루테늄막으로 치환하도록 해도 된다.

또한, 카본막(4)을 선택 성장시킬 때 사용되는 할로겐 가스로서는, 염소(Cl2) 가스 외에, 요오드(I2) 가스도 유효하다. 또한, 할로겐 단체가 아니어도, 할로겐화 탄화수소 가스를 사용할 수도 있다.

이렇게 제1 실시 형태에 의하면, 보다 미세한 반도체 장치 구조에의 적응이 가능한 선택 성장 방법을 얻을 수 있다.

(제2 실시 형태)

<다른 선택 성장 방법>

제1 실시 형태에서는, 카본막(4)의 선택 성장 및 SiO2막(5)의 선택 성장을, 각각 1회로 하였다. 그러나, 카본막(4)의 선택 성장 및 SiO2막(5)의 선택 성장은, 1회에 한정되지 않는다. 2회 이상 행하여, 카본막(4) 및 SiO2막(5)의 막 두께를 설계된 막 두께까지 두껍게 적층하는 것도 가능하다. 제2 실시 형태는, 그러한 일례이다.

도 5는 본 발명의 제2 실시 형태에 따른 선택 성장 방법의 일례를 도시하는 흐름도, 도 6a 내지 도 6h는 도 5에 도시하는 시퀀스 중의 피처리체의 상태를 개략적으로 도시하는 단면도이다.

먼저, 도 5 중의 스텝 1 및 스텝 2와 도 6a 내지 도 6d에 도시한 바와 같이, 제1 실시 형태에 따라, 도 6d에 도시한 바와 같은 구조체를 얻는다.

이어서, 도 5 중의 스텝 3 및 도 6e에 도시한 바와 같이, 연소에 의해 감막하는 막, 본 예에서는 카본막(4) 위에 새로운 연소에 의해 감막하는 막, 본 예에서는 카본막(4-1)을 선택적으로 성장시킨다.

스텝 3의 처리 조건의 일례는,

C4H6 가스 유량: 200sccm

Cl2 가스 유량: 50sccm

처리 시간: 180min

처리 온도: 350℃

처리 압력: 800Pa(약 6Torr)

이다. 스텝 3의 처리 조건은, 스텝 1의 처리 조건과 동일해도 되지만, 선택 성장시키는 하지가 텅스텐막(3)으로부터 카본막(4)으로 바뀌었기 때문에, 적절히 변경되어도 된다.

이어서, 도 5 중의 스텝 4와 도 6f 및 도 6g에 도시한 바와 같이, 새로운 연소에 의해 감막하는 막, 본 예에서는 카본막(4-1)을 연소시키면서, 하지의 SiO2막(5) 위에 새로운 실리콘 산화물 막, 예를 들어 SiO2막(5-1)을 선택적으로 성장시킨다.

스텝 4의 처리 조건의 일례는,

2DMAS 가스 유량: 200sccm

O3 가스 유량: 1000sccm

처리 시간: 30min

처리 온도: 350℃

처리 압력: 133.3Pa(1Torr)

이다. 스텝 4의 처리 조건은, 스텝 2의 처리 조건과 동일해도 된다.

이어서, 도 5 중의 스텝 5에 나타낸 바와 같이, 스텝 3 및 스텝 4의 횟수가 설정된 횟수인지 여부를 판단한다. 설정된 횟수에 달했다("예")고 판단된 경우에는, 처리를 종료한다. 반대로 설정된 횟수에 달하지 못했다("아니오")고 판단된 경우에는, 스텝 3으로 돌아가서, 다시 스텝 3 및 스텝 4를 반복한다.

이러한 스텝 3 및 스텝 4를 1회 이상 행함으로써, 도 6h에 도시한 바와 같이, 최종적인 구조로서, 반도체 집적 회로 장치로서 필요한 설계된 막 두께(t)를 갖는 카본막(4) 및 SiO2막(5)을 얻을 수도 있다.

또한, 제2 실시 형태에서도, 카본막(4)은 도 7에 도시한 바와 같이 제거할 수 있다. 해당 제거 처리에 의해서, 하지의 텅스텐막(3) 위에 텅스텐막(3)의 패턴에 자기 정합한, 제1 실시 형태보다도 더 깊은 개공(6')이 얻어진다는 이점을 얻을 수 있다.

(제3 실시 형태)

<선택 성장 방법>

제1, 제2 실시 형태에서는, 카본막(4)의 하지가 텅스텐이었다. 텅스텐막(3)과 같은 촉매 작용이 있는 금속으로서는, 텅스텐(W) 외에, Ti, V, Cr, Mn, Fe, Co, Ni, Cu, Zn, Ga, Ge, Si, Zr, Nb, Mo, Tc, Ru, Rh, Pd, In, Sn, Hf, Ta, Re, Os, Ir, Pt, Au 등을 들 수 있다.

그러나, 상기 금속에서는, 탄화수소 가스 중의 탄화수소를 흡착하여, 할로겐 가스 또는 할로겐화 탄화수소 가스의 분자를 분해시키는 반응이, 낮은 온도에서는 일어나기 어려운 것도 있다.

그러한 경우에는, 하지의 금속막의 노출면에는, 하지의 금속막의 내부에 존재하는 금속보다도 저온의 상태에서, 탄화수소 가스 중의 탄화수소의 흡착과, 할로겐 가스 또는 할로겐화 탄화수소 가스의 분자의 분해를 촉진시키는 별도의 금속으로 이루어진 별도의 금속막을 형성하도록 해도 된다. 제3 실시 형태는, 그러한 일례이다.

도 8은 본 발명의 제3 실시 형태에 따른 선택 성장 방법의 일례를 도시하는 흐름도, 도 9a 내지 도 9j는 도 8에 도시하는 시퀀스 중의 피처리체의 상태를 개략적으로 도시하는 단면도이다.

먼저, 도 8 중의 스텝 6과 도 9a 및 도 9b에 도시한 바와 같이, 하지의 금속막, 본 예에서는 코발트막(7) 위에 실리콘막(8)을 선택적으로 성장시킨다.

스텝 6의 처리 조건의 일례는,

SiH4 가스 유량: 200sccm

처리 시간: 60min

처리 온도: 350℃

처리 압력: 133.3Pa(1Torr)

이다.

이어서, 도 8 중의 스텝 7 및 도 9c에 도시한 바와 같이, 실리콘막(8)을 촉매 작용을 촉진시키는 별도의 금속막으로 치환한다. 본 예에서는, 실리콘막(8)을 해당 별도의 금속막으로서의 텅스텐막(9)으로 치환하였다.

스텝 7의 처리 조건의 일례는,

WF6 가스 유량: 200sccm

처리 시간: 30min

처리 온도: 350℃

처리 압력: 133.3Pa(1Torr)

이다.

이 후, 도 8 중의 스텝 1 내지 스텝 5, 및 도 9d 내지 9i에 도시한 바와 같이, 예를 들어 제2 실시 형태에 따라서 처리를 진행시킨다.

이와 같이, 하지의 금속막의 금속이, 예를 들어 저온에서는 촉매 반응이 일어나기 어려운 것이었던 경우에는, 하지의 금속막의 노출면 위에, 보다 저온에서도 촉매 반응이 일어나는 별도의 금속막을 형성해도 된다.

이렇게 하지의 금속막의 노출면 위에 보다 저온에서도 촉매 반응이 일어나는 금속으로 이루어진 별도의 금속막, 본 예에서는 텅스텐막(9)을 형성한 경우의 최종 형상은, 예를 들어 도 9j에 도시한 바와 같이, 하지의 금속막, 본 예에서는 코발트막(7)과 카본막(4)의 사이에, 텅스텐막(9)이 개재된 것으로 된다.

또한, 제3 실시 형태에서도, 카본막(4) 및 텅스텐막(9)은 도 10에 도시하는 바와 같이 제거할 수 있다. 카본막(4) 및 텅스텐막(9)을 제거한 경우에는, 제2 실시 형태에서 설명한 바와 같이, 하지의 코발트막(7) 위에 코발트막(7)의 패턴에 자기 정합한, 제1 실시 형태보다도 더 깊은 개공(6'')이 얻어진다는 이점을 얻을 수 있다.

(제4 실시 형태)

제4 실시 형태는, 상기 제1 내지 제3 실시 형태에 따른 선택 성장 방법을 실시하는 것이 가능한 기판 처리 장치의 일례에 관한 것이다.

도 11은 본 발명의 제4 실시 형태에 따른 기판 처리 장치의 일례를 개략적으로 도시하는 종단면도이다.

도 11에 도시한 바와 같이, 기판 처리 장치(100)는, 하단이 개구된 천장이 있는 원통체 형상의 처리실(101)을 갖고 있다. 처리실(101)의 전체는, 예를 들어 석영에 의해 형성되어 있다. 처리실(101) 내의 천장에는, 석영제의 천장판(102)이 설치되어 있다. 처리실(101)의 하단 개구부에는, 예를 들어 스테인레스 스틸에 의해 원통체 형상으로 성형된 매니폴드(103)가 O링 등의 시일 부재(104)를 개재해서 연결되어 있다.

매니폴드(103)는 처리실(101)의 하단을 지지하고 있다. 매니폴드(103)의 하방으로부터는, 피처리체로서 복수매, 예를 들어 50 내지 100매의 반도체 웨이퍼, 본 예에서는, 실리콘 웨이퍼(1)를 다단으로 적재 가능한 석영제의 웨이퍼 보트(105)가 처리실(101) 내에 삽입 가능하게 되어 있다. 웨이퍼 보트(105)는 복수개의 지주(106)를 갖고, 지주(106)에 형성된 홈에 의해 복수매의 웨이퍼(1)가 지지되도록 되어 있다.

웨이퍼 보트(105)는, 석영제의 보온통(107)을 개재해서 테이블(108) 위에 적재되어 있다. 테이블(108)은 매니폴드(103)의 하단 개구부를 개폐하는, 예를 들어 스테인레스 스틸제의 덮개부(109)를 관통하는 회전축(110) 위에 지지된다. 회전축(110)의 관통부에는, 예를 들어 자성 유체 시일(111)이 설치되어, 회전축(110)을 기밀하게 시일하면서 회전 가능하게 지지하고 있다. 덮개부(109)의 주변부와 매니폴드(103)의 하단부의 사이에는, 예를 들어 O링으로 이루어지는 시일 부재(112)가 설치되어 있다. 이에 의해 처리실(101) 내의 시일성이 유지되어 있다. 회전축(110)은, 예를 들어 보트 엘리베이터 등의 승강 기구(도시하지 않음)에 지지된 아암(113)의 선단에 설치되어 있다. 이에 의해, 웨이퍼 보트(105) 및 덮개부(109) 등은, 일체적으로 승강되어서 처리실(101) 내에 대하여 삽입 분리된다.

기판 처리 장치(100)는, 처리실(101) 내에, 처리에 사용하는 가스를 공급하는 처리 가스 공급 기구(114)와, 처리실(101) 내에, 불활성 가스를 공급하는 불활성 가스 공급 기구(115)를 갖고 있다.

처리 가스 공급 기구(114)는, 탄화수소 가스 공급원(117a), 할로겐 가스 공급원(117b), 실리콘을 포함하는 가스 공급원(117c) 및 산소를 포함하는 가스 공급원(117d)을 포함하여 구성되어 있다.

본 예에서는, 탄화수소 가스 공급원(117a)은, 탄화수소 가스로서 C4H6 가스를, 할로겐 가스 공급원(117b)은, 할로겐 가스로서 Cl2 가스를, 실리콘을 포함하는 처리 가스 공급원(117c)은, 실리콘을 포함하는 가스로서 2DMAS 가스를, 산소를 포함하는 가스 공급원(117d)은, 산소를 포함하는 가스로서 O3 가스를, 각각 처리실(101) 내에 공급한다.

불활성 가스 공급 기구(115)는, 불활성 가스 공급원(120)을 포함하여 구성되어 있다. 불활성 가스 공급원(120)은 불활성 가스로서 N2 가스를, 처리실(101) 내에 공급한다.

또한, 할로겐 가스 공급원(117b)은, 할로겐 가스 외에, 할로겐화 탄화수소 가스를 공급하도록 해도 된다.

탄화수소 가스 공급원(117a)은, 유량 제어기(121a) 및 개폐 밸브(122a)를 통해서, 분산 노즐(123a)에 접속되어 있다. 마찬가지로, 할로겐 가스 공급원(117b)은, 유량 제어기(121b) 및 개폐 밸브(122b)를 통해서 도시하지 않은 분산 노즐(123b)에, 마찬가지로, 실리콘을 포함하는 가스 공급원(117c)은 유량 제어기(121c) 및 개폐 밸브(122c)를 통해서 도시하지 않은 분산 노즐(123c)에, 산소를 포함하는 가스 공급원(117d)은 유량 제어기(121d) 및 개폐 밸브(122d)를 통해서 분산 노즐(123d)에, 각각 접속되어 있다.

분산 노즐(123a 내지 123d)은 석영관으로 이루어지며, 매니폴드(103)의 측벽을 내측으로 관통해서 상측 방향으로 굴곡되어 수직으로 연장된다. 분산 노즐(123a 내지 123d)의 수직 부분에는, 복수의 가스 토출 구멍(124a 내지 124d)이 소정의 간격을 두고 형성되어 있다. 탄화수소 가스, 할로겐 가스, 실리콘을 포함하는 가스, 산소를 포함하는 가스는 각각, 가스 토출 구멍(124a 내지 124d)으로부터 처리실(101) 내를 향해서 수평 방향으로 대략 균일하게 토출된다.

불활성 가스 공급원(120)은, 유량 제어기(121e) 및 개폐 밸브(122e)를 통해서 노즐(128)에 접속되어 있다. 노즐(128)은 매니폴드(103)의 측벽을 관통하여, 그 선단으로부터 불활성 가스를 처리실(101) 내에 수평 방향을 향해서 토출시킨다.

처리실(101) 내의, 분산 노즐(123a 내지 123d)과 반대측의 부분에는, 처리실(101) 내를 배기하기 위한 배기구(129)가 형성되어 있다. 배기구(129)는, 처리실(101)의 측벽을 상하 방향으로 깎아냄으로써 가늘고 길게 형성되어 있다. 처리실(101)의 배기구(129)에 대응하는 부분에는, 배기구(129)를 덮도록 단면이 역 ㄷ자 형상으로 성형된 배기구 커버 부재(130)가 용접에 의해 설치되어 있다. 배기구 커버 부재(130)는, 처리실(101)의 측벽을 따라 상방으로 연장되어 있고, 처리실(101)의 상방에 가스 출구(131)를 규정하고 있다. 가스 출구(131)에는, 진공 펌프 등을 포함하는 배기 기구(132)가 접속된다. 배기 기구(132)는, 처리실(101) 내를 배기함으로써 처리에 사용한 처리 가스의 배기 및 처리실(101) 내의 압력을 처리에 따른 처리 압력으로 한다.

처리실(101)의 외주에는 통체 형상의 가열 장치(133)가 설치되어 있다. 가열 장치(133)는, 처리실(101) 내에 공급된 처리 가스를 활성화함과 함께, 처리실(101) 내에 수용된 피처리체, 본 예에서는 웨이퍼(1)를 가열한다.

기판 처리 장치(100)의 각 부의 제어는, 예를 들어 마이크로프로세서(컴퓨터)로 이루어지는 컨트롤러(150)에 의해 행하여진다. 컨트롤러(150)에는, 유저 인터페이스(151)가 접속되어 있다. 유저 인터페이스(151)는, 오퍼레이터가 기판 처리 장치(100)를 관리하기 위해서, 커맨드의 입력 조작 등을 행하기 위한 터치 패널 디스플레이나 키보드 등을 포함하는 입력부 및 기판 처리 장치(100)의 가동 상황을 가시화해서 표시하는 디스플레이 등을 포함하는 표시부가 구비되어 있다.

컨트롤러(150)에는 기억부(152)가 접속되어 있다. 기억부(152)는, 기판 처리 장치(100)에서 실시되는 각종 처리를 컨트롤러(150)의 제어로 실현하기 위한 제어 프로그램이나, 처리 조건에 따라서 기판 처리 장치(100)의 각 구성부에 처리를 실시시키기 위한 프로그램, 즉 레시피가 저장된다. 레시피는, 예를 들어 기억부(152) 중 기억 매체에 기억된다. 기억 매체는, 하드 디스크나 반도체 메모리이어도 되고, CD-ROM, DVD, 플래시 메모리 등의 가반성인 것이어도 된다. 또한, 다른 장치로부터, 예를 들어 전용 회선을 통해서 레시피를 적절히 전송시키도록 해도 된다. 레시피는, 필요에 따라, 유저 인터페이스(151)로부터의 지시 등으로 기억부(152)로부터 판독되어, 판독된 레시피에 따른 처리를 컨트롤러(150)가 실시함으로써, 기판 처리 장치(100)는 컨트롤러(150)의 제어 하에 원하는 처리가 실시된다.

본 예에서는, 컨트롤러(150)의 제어 하에, 상기 제1 내지 제3 실시 형태에 따른 선택 성장 방법을 실시한다. 상기 제1 내지 제3 실시 형태에 따른 선택 성장 방법은, 도 11에 도시하는 바와 같은 기판 처리 장치(100)에 의해 실시할 수 있다.

이상, 본 발명을 제1 내지 제4 실시 형태에 따라서 설명했지만, 본 발명은 상기 제1 내지 제4 실시 형태에 한정되지 않고, 그 취지를 일탈하지 않는 범위에서 다양하게 변형 가능하다.

예를 들어, 상기 실시 형태에서는 처리 조건을 구체적으로 예시했지만, 처리 조건은, 상기 구체적인 예시에 한정되는 것은 아니다. 처리 조건은, 예를 들어 피처리체를 수용하는 처리실의 용적이나, 처리 압력의 변경 등에 따라서 변경하는 것이 가능하다.

그 밖에, 본 발명은 그 요지를 일탈하지 않는 범위에서 다양하게 변형될 수 있다.

1 : 실리콘 웨이퍼

2 : SiO2막

3 : 텅스텐막 4 : 카본막

5 : SiO2막 6 : 개공

7 : 코발트막 8 : 실리콘막

9 : 텅스텐막

3 : 텅스텐막 4 : 카본막

5 : SiO2막 6 : 개공

7 : 코발트막 8 : 실리콘막

9 : 텅스텐막

Claims (11)

- 절연막과 금속막이 노출되어 있는 하지 위에 박막을 선택적으로 성장시키는 선택 성장 방법으로서,

상기 하지의 금속을 촉매로 사용하여, 상기 하지의 금속막 위에 연소에 의해 감막하는 막을 선택적으로 성장시키는 제1 공정과,

상기 연소에 의해 감막하는 막을 연소시키면서, 상기 하지의 절연막 위에 실리콘 산화물 막을 선택적으로 성장시키는 제2 공정

을 포함하는 선택 성장 방법. - 제1항에 있어서,

상기 제2 공정 후,

잔존하고 있는 상기 연소에 의해 감막하는 막 위에, 새로운 연소에 의해 감막하는 막을 선택적으로 성장시키는 제3 공정과,

상기 새로운 연소에 의해 감막하는 막을 연소시키면서, 상기 실리콘 산화물 막 위에, 새로운 실리콘 산화물 막을 선택적으로 성장시키는 제4 공정

을 더 포함하고,

상기 제3 공정 및 제4 공정을 1회, 또는 설정된 횟수까지 반복해서 행하는, 선택 성장 방법. - 제1항에 있어서,

상기 제2 공정 후,

상기 실리콘 산화물 막을 마스크로 사용하여, 상기 연소에 의해 감막하는 막을 제거하는 제5 공정

을 더 포함하는, 선택 성장 방법. - 제2항에 있어서,

상기 제4 공정 후,

상기 새로운 실리콘 산화물 막을 마스크로 사용하여, 상기 새로운 연소에 의해 감막하는 막 및 상기 연소에 의해 감막하는 막을 제거하는 제6 공정

을 더 포함하는, 선택 성장 방법. - 제1항 내지 제4항 중 어느 한 항에 있어서,

상기 연소에 의해 감막하는 막은, 카본막 또는 루테늄막인, 선택 성장 방법. - 제5항에 있어서,

상기 연소에 의해 감막하는 막이 카본막일 때,

상기 카본막의 원료 가스는, 탄화수소 가스와, 할로겐 가스 또는 할로겐화 탄화수소 가스를 포함하고,

상기 금속은, 상기 탄화수소 가스 중의 탄화수소를 흡착하여, 상기 할로겐 가스 또는 할로겐화 탄화수소 가스의 분자를 분해시키는, 선택 성장 방법. - 제6항에 있어서,

상기 할로겐은, Cl 및 I 중 어느 하나인, 선택 성장 방법. - 제1항 내지 제4항 중 어느 한 항에 있어서,

상기 실리콘 산화물 막의 원료 가스는, 실리콘을 포함하는 가스와, 산소를 포함하는 가스를 포함하는, 선택 성장 방법. - 제6항에 있어서,

상기 하지의 금속막의 노출면에는, 상기 하지의 금속막의 내부에 존재하는 금속보다도 저온인 상태에서, 상기 탄화수소 가스 중의 탄화수소의 흡착과, 상기 할로겐 가스 또는 할로겐화 탄화수소 가스의 분자의 분해를 촉진시키는 별도의 금속으로 이루어진 별도의 금속막이 형성되어 있는, 선택 성장 방법. - 제1항 내지 제4항 중 어느 한 항에 있어서,

상기 금속은,

Ti, V, Cr, Mn, Fe, Co, Ni, Cu, Zn, Ga, Ge, Si, Zr, Nb, Mo, Tc, Ru, Rh, Pd, In, Sn, Hf, Ta, W, Re, Os, Ir, Pt, Au

중 어느 하나를 포함하는, 선택 성장 방법. - 피처리체의, 절연막과 금속막이 노출되어 있는 피처리면 위에 박막을 선택적으로 성장시키는 기판 처리 장치로서,

상기 피처리체를 수용하는 처리실과,

상기 처리실 내에, 탄화수소 가스, 할로겐 가스 또는 할로겐화 탄화수소 가스, 실리콘을 포함하는 가스 및 산소를 포함하는 가스를 적어도 공급하는 가스 공급 기구와,

상기 처리실 내를 가열하는 가열 장치와,

상기 처리실 내를 배기하는 배기 기구와,

상기 가스 공급 기구, 상기 가열 장치, 상기 배기 기구를 제어하는 컨트롤러를 포함하고,

상기 컨트롤러가, 상기 처리실 내에서, 제1항 내지 제4항 중 어느 한 항에 기재된 선택 성장 방법이 상기 피처리체에 대하여 실시되도록, 상기 가스 공급 기구, 상기 가열 장치, 상기 배기 기구를 제어하는 기판 처리 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JPJP-P-2014-220157 | 2014-10-29 | ||

| JP2014220157A JP6317232B2 (ja) | 2014-10-29 | 2014-10-29 | 選択成長方法および基板処理装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20160052329A true KR20160052329A (ko) | 2016-05-12 |

| KR101892337B1 KR101892337B1 (ko) | 2018-08-27 |

Family

ID=55853466

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020150147154A KR101892337B1 (ko) | 2014-10-29 | 2015-10-22 | 선택 성장 방법 및 기판 처리 장치 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9512541B2 (ko) |

| JP (1) | JP6317232B2 (ko) |

| KR (1) | KR101892337B1 (ko) |

| TW (1) | TWI625787B (ko) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20180111537A (ko) * | 2017-03-30 | 2018-10-11 | 도쿄엘렉트론가부시키가이샤 | 선택 성장 방법 |

| KR20190127578A (ko) * | 2018-05-02 | 2019-11-13 | 에이에스엠 아이피 홀딩 비.브이. | 증착 및 제거를 이용한 선택적 층 형성 |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017212294A (ja) * | 2016-05-24 | 2017-11-30 | 東京エレクトロン株式会社 | カーボン膜の成膜方法および成膜装置 |

| US10176984B2 (en) * | 2017-02-14 | 2019-01-08 | Lam Research Corporation | Selective deposition of silicon oxide |

| US10242866B2 (en) | 2017-03-08 | 2019-03-26 | Lam Research Corporation | Selective deposition of silicon nitride on silicon oxide using catalytic control |

| US10043656B1 (en) | 2017-03-10 | 2018-08-07 | Lam Research Corporation | Selective growth of silicon oxide or silicon nitride on silicon surfaces in the presence of silicon oxide |

| US9911595B1 (en) | 2017-03-17 | 2018-03-06 | Lam Research Corporation | Selective growth of silicon nitride |

| US10453681B2 (en) * | 2017-04-12 | 2019-10-22 | Tokyo Electron Limited | Method of selective vertical growth of a dielectric material on a dielectric substrate |

| US10559461B2 (en) | 2017-04-19 | 2020-02-11 | Lam Research Corporation | Selective deposition with atomic layer etch reset |

| US10490411B2 (en) | 2017-05-19 | 2019-11-26 | Applied Materials, Inc. | Method for enabling self-aligned lithography on metal contacts and selective deposition using free-standing vertical carbon structures |

| DE102017121245B3 (de) | 2017-09-13 | 2018-12-20 | Westfälische Wilhelms-Universität Münster | Strukturierung von OLED-Schichten und entsprechend strukturierte OLEDs |

| JP2019062142A (ja) | 2017-09-28 | 2019-04-18 | 東京エレクトロン株式会社 | 選択成膜方法および半導体装置の製造方法 |

| US10460930B2 (en) | 2017-11-22 | 2019-10-29 | Lam Research Corporation | Selective growth of SiO2 on dielectric surfaces in the presence of copper |

| CN112005343A (zh) | 2018-03-02 | 2020-11-27 | 朗姆研究公司 | 使用水解的选择性沉积 |

| TWI757659B (zh) * | 2018-11-23 | 2022-03-11 | 美商應用材料股份有限公司 | 碳膜的選擇性沉積及其用途 |

| US20200347493A1 (en) * | 2019-05-05 | 2020-11-05 | Applied Materials, Inc. | Reverse Selective Deposition |

| TWI837391B (zh) | 2019-06-26 | 2024-04-01 | 美商蘭姆研究公司 | 利用鹵化物化學品的光阻顯影 |

| TWI819233B (zh) | 2019-08-15 | 2023-10-21 | 美商應用材料股份有限公司 | 非共形膜的選擇性蝕刻臨界尺寸控制 |

| JP2021040159A (ja) * | 2020-11-30 | 2021-03-11 | 東京エレクトロン株式会社 | 選択成長方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60249334A (ja) * | 1984-05-25 | 1985-12-10 | Hitachi Ltd | 薄膜形成方法 |

| JPS62291913A (ja) * | 1986-06-12 | 1987-12-18 | Matsushita Electric Ind Co Ltd | 薄膜の形成方法 |

| JP2009231836A (ja) | 2008-03-20 | 2009-10-08 | Siltronic Ag | ヘテロエピタキシャル層を備えた半導体ウェハ及び前記ウェハの製造方法 |

| JP2011190156A (ja) * | 2010-03-16 | 2011-09-29 | Nagoya Univ | カーボンナノウォールの選択成長方法、およびカーボンナノウォールを用いた電子デバイス |

| JP2014033186A (ja) * | 2012-07-09 | 2014-02-20 | Tokyo Electron Ltd | カーボン膜の成膜方法および成膜装置 |

| JP2014175337A (ja) | 2013-03-06 | 2014-09-22 | Tokyo Electron Ltd | 選択エピタキシャル成長法および成膜装置 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050274996A1 (en) * | 2004-06-14 | 2005-12-15 | Matsushita Electric Industrial Co., Ltd. | Solid-state imaging device and method for manufacturing the same |

| US20080299780A1 (en) * | 2007-06-01 | 2008-12-04 | Uv Tech Systems, Inc. | Method and apparatus for laser oxidation and reduction |

| JP4476313B2 (ja) * | 2007-07-25 | 2010-06-09 | 東京エレクトロン株式会社 | 成膜方法、成膜装置、および記憶媒体 |

| JP2009094279A (ja) * | 2007-10-09 | 2009-04-30 | Elpida Memory Inc | ホールパターンの形成方法および半導体装置の製造方法 |

| JP5238775B2 (ja) * | 2010-08-25 | 2013-07-17 | 株式会社東芝 | カーボンナノチューブ配線の製造方法 |

| JP2012199520A (ja) * | 2011-03-10 | 2012-10-18 | Toshiba Corp | 半導体装置およびその製造方法 |

-

2014

- 2014-10-29 JP JP2014220157A patent/JP6317232B2/ja active Active

-

2015

- 2015-10-20 US US14/887,685 patent/US9512541B2/en active Active

- 2015-10-22 KR KR1020150147154A patent/KR101892337B1/ko active IP Right Grant

- 2015-10-26 TW TW104135017A patent/TWI625787B/zh active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60249334A (ja) * | 1984-05-25 | 1985-12-10 | Hitachi Ltd | 薄膜形成方法 |

| JPS62291913A (ja) * | 1986-06-12 | 1987-12-18 | Matsushita Electric Ind Co Ltd | 薄膜の形成方法 |

| JP2009231836A (ja) | 2008-03-20 | 2009-10-08 | Siltronic Ag | ヘテロエピタキシャル層を備えた半導体ウェハ及び前記ウェハの製造方法 |

| JP2011190156A (ja) * | 2010-03-16 | 2011-09-29 | Nagoya Univ | カーボンナノウォールの選択成長方法、およびカーボンナノウォールを用いた電子デバイス |

| JP2014033186A (ja) * | 2012-07-09 | 2014-02-20 | Tokyo Electron Ltd | カーボン膜の成膜方法および成膜装置 |

| JP2014175337A (ja) | 2013-03-06 | 2014-09-22 | Tokyo Electron Ltd | 選択エピタキシャル成長法および成膜装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20180111537A (ko) * | 2017-03-30 | 2018-10-11 | 도쿄엘렉트론가부시키가이샤 | 선택 성장 방법 |

| KR20190127578A (ko) * | 2018-05-02 | 2019-11-13 | 에이에스엠 아이피 홀딩 비.브이. | 증착 및 제거를 이용한 선택적 층 형성 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20160126106A1 (en) | 2016-05-05 |

| TW201633400A (zh) | 2016-09-16 |

| JP6317232B2 (ja) | 2018-04-25 |

| TWI625787B (zh) | 2018-06-01 |

| KR101892337B1 (ko) | 2018-08-27 |

| US9512541B2 (en) | 2016-12-06 |

| JP2016086145A (ja) | 2016-05-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101892337B1 (ko) | 선택 성장 방법 및 기판 처리 장치 | |

| KR101759157B1 (ko) | 산화 실리콘막의 성막 방법 | |

| JP5514162B2 (ja) | アモルファスシリコン膜の成膜方法および成膜装置 | |

| US8431494B2 (en) | Film formation method and film formation apparatus | |

| US8501629B2 (en) | Smooth SiConi etch for silicon-containing films | |

| KR101813312B1 (ko) | 실리콘막의 성막 방법, 박막의 성막 방법 및 단면 형상 제어 방법 | |

| KR101682747B1 (ko) | 시드층의 형성 방법, 실리콘막의 성막 방법 및 성막 장치 | |

| JP5541223B2 (ja) | 成膜方法及び成膜装置 | |

| KR20160002613A (ko) | 질화 실리콘막의 성막 방법 및 성막 장치 | |

| KR101475557B1 (ko) | 카본막 상으로의 산화물막의 성막 방법 및 성막 장치 | |

| KR20180025819A (ko) | 그래핀의 생성 방법 | |

| US9460913B2 (en) | Film-forming method for forming silicon oxide film on tungsten film or tungsten oxide film | |

| US9466476B2 (en) | Film-forming method for forming silicon oxide film on tungsten film or tungsten oxide film | |

| JP6010161B2 (ja) | アモルファスシリコン膜の成膜方法および成膜装置 | |

| JP5710819B2 (ja) | アモルファスシリコン膜の成膜方法および成膜装置 | |

| JP2013199673A (ja) | 酸化ルテニウム膜の成膜方法および酸化ルテニウム膜成膜用処理容器のクリーニング方法 | |

| KR20240056552A (ko) | 기판 처리 방법, 반도체 장치의 제조 방법, 기판 처리 장치 및 프로그램 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |