KR20140097990A - 반도체 장치 및 그 제작 방법 - Google Patents

반도체 장치 및 그 제작 방법 Download PDFInfo

- Publication number

- KR20140097990A KR20140097990A KR1020140009394A KR20140009394A KR20140097990A KR 20140097990 A KR20140097990 A KR 20140097990A KR 1020140009394 A KR1020140009394 A KR 1020140009394A KR 20140009394 A KR20140009394 A KR 20140009394A KR 20140097990 A KR20140097990 A KR 20140097990A

- Authority

- KR

- South Korea

- Prior art keywords

- film

- oxide semiconductor

- oxide

- transistor

- semiconductor film

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 389

- 238000000034 method Methods 0.000 title claims abstract description 62

- 238000004519 manufacturing process Methods 0.000 title claims description 30

- 239000011248 coating agent Substances 0.000 claims description 38

- 238000000576 coating method Methods 0.000 claims description 38

- 238000012545 processing Methods 0.000 claims description 20

- 238000010894 electron beam technology Methods 0.000 claims description 17

- 239000007788 liquid Substances 0.000 claims description 11

- 238000007654 immersion Methods 0.000 claims description 10

- 229910052721 tungsten Inorganic materials 0.000 claims description 9

- 229910052719 titanium Inorganic materials 0.000 claims description 8

- 229910052738 indium Inorganic materials 0.000 claims description 7

- 229910052750 molybdenum Inorganic materials 0.000 claims description 5

- 229910052715 tantalum Inorganic materials 0.000 claims description 5

- 229910052733 gallium Inorganic materials 0.000 claims description 4

- 230000008569 process Effects 0.000 abstract description 10

- 229910052760 oxygen Inorganic materials 0.000 description 78

- 239000001301 oxygen Substances 0.000 description 74

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 72

- 239000000758 substrate Substances 0.000 description 60

- 238000010438 heat treatment Methods 0.000 description 48

- 125000004429 atom Chemical group 0.000 description 46

- 239000000463 material Substances 0.000 description 44

- 239000011701 zinc Substances 0.000 description 39

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 34

- 238000004544 sputter deposition Methods 0.000 description 33

- 229910052710 silicon Inorganic materials 0.000 description 32

- 239000010703 silicon Substances 0.000 description 32

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 32

- 239000013078 crystal Substances 0.000 description 31

- 239000012535 impurity Substances 0.000 description 31

- 229910052814 silicon oxide Inorganic materials 0.000 description 31

- 239000003990 capacitor Substances 0.000 description 25

- 239000007789 gas Substances 0.000 description 25

- 239000010410 layer Substances 0.000 description 23

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 22

- 229910052581 Si3N4 Inorganic materials 0.000 description 22

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 22

- 238000005530 etching Methods 0.000 description 21

- 229910052739 hydrogen Inorganic materials 0.000 description 20

- 239000001257 hydrogen Substances 0.000 description 20

- 206010021143 Hypoxia Diseases 0.000 description 19

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 17

- 229910052751 metal Inorganic materials 0.000 description 16

- 239000000523 sample Substances 0.000 description 16

- 230000007547 defect Effects 0.000 description 13

- 238000006243 chemical reaction Methods 0.000 description 12

- 239000004020 conductor Substances 0.000 description 11

- 239000002184 metal Substances 0.000 description 11

- 229910052757 nitrogen Inorganic materials 0.000 description 11

- 238000003860 storage Methods 0.000 description 11

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 10

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 10

- 238000004380 ashing Methods 0.000 description 10

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 9

- 229910052799 carbon Inorganic materials 0.000 description 9

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 9

- 229910001868 water Inorganic materials 0.000 description 9

- 238000004458 analytical method Methods 0.000 description 8

- 230000006870 function Effects 0.000 description 8

- 238000005259 measurement Methods 0.000 description 8

- 238000010521 absorption reaction Methods 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 238000001514 detection method Methods 0.000 description 7

- 238000010586 diagram Methods 0.000 description 7

- 150000002431 hydrogen Chemical class 0.000 description 7

- 238000002955 isolation Methods 0.000 description 7

- 230000002093 peripheral effect Effects 0.000 description 7

- 229910052725 zinc Inorganic materials 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 6

- 239000002585 base Substances 0.000 description 6

- 229910052732 germanium Inorganic materials 0.000 description 6

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 6

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 6

- 230000003287 optical effect Effects 0.000 description 6

- 239000002245 particle Substances 0.000 description 6

- 229910052786 argon Inorganic materials 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 5

- 230000005669 field effect Effects 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 230000010354 integration Effects 0.000 description 5

- 230000003647 oxidation Effects 0.000 description 5

- 238000007254 oxidation reaction Methods 0.000 description 5

- 239000000843 powder Substances 0.000 description 5

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 5

- 239000002356 single layer Substances 0.000 description 5

- 239000011787 zinc oxide Substances 0.000 description 5

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 4

- 238000004435 EPR spectroscopy Methods 0.000 description 4

- HBBGRARXTFLTSG-UHFFFAOYSA-N Lithium ion Chemical compound [Li+] HBBGRARXTFLTSG-UHFFFAOYSA-N 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 239000011261 inert gas Substances 0.000 description 4

- 238000005468 ion implantation Methods 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 4

- 229910001416 lithium ion Inorganic materials 0.000 description 4

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 4

- 230000001590 oxidative effect Effects 0.000 description 4

- 125000004430 oxygen atom Chemical group O* 0.000 description 4

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 4

- 238000001878 scanning electron micrograph Methods 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 229910052726 zirconium Inorganic materials 0.000 description 4

- 229910052684 Cerium Inorganic materials 0.000 description 3

- 229910052779 Neodymium Inorganic materials 0.000 description 3

- OUUQCZGPVNCOIJ-UHFFFAOYSA-M Superoxide Chemical compound [O-][O] OUUQCZGPVNCOIJ-UHFFFAOYSA-M 0.000 description 3

- 238000011161 development Methods 0.000 description 3

- 230000018109 developmental process Effects 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 3

- 229910001195 gallium oxide Inorganic materials 0.000 description 3

- 229910052735 hafnium Inorganic materials 0.000 description 3

- 229910052746 lanthanum Inorganic materials 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- 239000000779 smoke Substances 0.000 description 3

- 238000005477 sputtering target Methods 0.000 description 3

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 2

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- 229910007541 Zn O Inorganic materials 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 230000002159 abnormal effect Effects 0.000 description 2

- 230000001133 acceleration Effects 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- -1 at least one of Ti Chemical class 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 230000000052 comparative effect Effects 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 229910021419 crystalline silicon Inorganic materials 0.000 description 2

- 238000002425 crystallisation Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 2

- 230000001788 irregular Effects 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 2

- 239000000395 magnesium oxide Substances 0.000 description 2

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 238000013508 migration Methods 0.000 description 2

- 230000005012 migration Effects 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 2

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 2

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 229910001928 zirconium oxide Inorganic materials 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 235000015842 Hesperis Nutrition 0.000 description 1

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 description 1

- 235000012633 Iberis amara Nutrition 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 241001591005 Siga Species 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 239000006117 anti-reflective coating Substances 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000002485 combustion reaction Methods 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000003795 desorption Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000003623 enhancer Substances 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 238000000671 immersion lithography Methods 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 229910000765 intermetallic Inorganic materials 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 239000002159 nanocrystal Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000003208 petroleum Substances 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 238000004321 preservation Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical group [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66969—Multistep manufacturing processes of devices having semiconductor bodies not comprising group 14 or group 13/15 materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

- H01L29/78693—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate the semiconducting oxide being amorphous

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Thin Film Transistor (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Dram (AREA)

Abstract

본 발명은 높은 전기 특성을 갖는 미세한 트랜지스터를 수율 좋게 제공한다. 또한, 상기 트랜지스터를 포함하는 반도체 장치에서도 고성능화, 고신뢰성화, 및 고생산화를 달성한다.

산화물 반도체막을 섬 형상으로 미세 가공할 때, 하드 마스크를 사용함으로써 산화물 반도체막 단부의 요철을 억제할 수 있다. 구체적으로는 산화물 반도체막 위에 하드 마스크를 형성하고, 하드 마스크 위에 레지스트를 형성하고, 노광하여 레지스트 마스크를 형성하고, 레지스트 마스크를 마스크로 하여 하드 마스크를 가공하고, 가공된 하드 마스크를 마스크로 하여 산화물 반도체막을 가공하고, 레지스트 마스크 및 가공된 하드 마스크를 제거하고, 가공된 산화물 반도체막에 접하는 소스 전극 및 드레인 전극을 형성하고, 소스 전극 및 드레인 전극 위에 게이트 절연막을 형성하고, 게이트 절연막 위에 있고 산화물 반도체막과 중첩되는 위치에 게이트 전극을 형성한다.

산화물 반도체막을 섬 형상으로 미세 가공할 때, 하드 마스크를 사용함으로써 산화물 반도체막 단부의 요철을 억제할 수 있다. 구체적으로는 산화물 반도체막 위에 하드 마스크를 형성하고, 하드 마스크 위에 레지스트를 형성하고, 노광하여 레지스트 마스크를 형성하고, 레지스트 마스크를 마스크로 하여 하드 마스크를 가공하고, 가공된 하드 마스크를 마스크로 하여 산화물 반도체막을 가공하고, 레지스트 마스크 및 가공된 하드 마스크를 제거하고, 가공된 산화물 반도체막에 접하는 소스 전극 및 드레인 전극을 형성하고, 소스 전극 및 드레인 전극 위에 게이트 절연막을 형성하고, 게이트 절연막 위에 있고 산화물 반도체막과 중첩되는 위치에 게이트 전극을 형성한다.

Description

본 발명은 물건(product: 기계(machine), 제품(manufacture), 조성물(composition of matter)을 포함함), 및 방법(process: 단순 방법 및 생산 방법을 포함함)에 관한 것이다. 특히, 본 발명의 일 형태는 반도체 장치, 표시 장치, 발광 장치, 축전 장치, 이들의 구동 방법, 또는 이들의 제조 방법에 관한 것이다. 특히, 본 발명의 일 형태는 산화물 반도체를 갖는 반도체 장치, 표시 장치, 또는 발광 장치에 관한 것이다.

액정 표시 장치나 발광 표시 장치로 대표되는 플랫 패널 디스플레이의 대부분에 사용되고 있는 트랜지스터는 유리 기판 위에 형성된 어모퍼스 실리콘, 단결정 실리콘, 또는 다결정 실리콘 등의 실리콘 반도체로 구성된다. 또한, 상기 실리콘 반도체를 사용한 트랜지스터는 집적 회로(IC) 등에도 이용되고 있다.

근년에 들어, 실리콘 반도체 대신에 반도체 특성을 나타내는 금속 산화물을 트랜지스터에 사용하는 기술이 주목을 받고 있다. 또한, 본 명세서 중에서는 반도체 특성을 나타내는 금속 산화물을 산화물 반도체라고 부르기로 한다.

예를 들어, 산화물 반도체로서 산화 아연 또는 In-Ga-Zn계 산화물을 사용한 트랜지스터가 개시(開示)되어 있다(특허 문헌 1 참조).

그런데, 트랜지스터 동작의 고속화, 트랜지스터의 저소비 전력화, 고집적화 등을 달성하기 위해서는 트랜지스터의 미세화가 필수적이다.

그러나, 트랜지스터의 미세화에 따라, 제작 공정에서의 수율의 저하가 우려된다. 예를 들어, 채널이 되는 산화물 반도체막을 섬 형상으로 미세 가공할 때, 산화물 반도체막 단부에 요철이 생김으로써 산화물 반도체막의 형상 편차가 커지고, 트랜지스터의 전기 특성이나 신뢰성에도 영향을 미칠 수 있다.

따라서, 본 발명의 일 형태는 미세한 구조라도 높은 전기 특성을 갖는 트랜지스터 등을 수율 좋게 제공하는 것을 목적 중 하나로 한다.

또는, 상기 트랜지스터를 포함한 반도체 장치 등에서도 고성능화, 고신뢰성화, 및 고생산화를 달성하는 것을 목적 중 하나로 한다.

또는, 본 발명의 일 형태는 신규 반도체 장치 등을 제공하는 것을 과제로 한다. 또는, 본 발명의 일 형태는 신규 반도체 장치 등의 제조 방법을 제공하는 것을 과제로 한다. 또한, 이들 과제의 기재는 다른 과제의 존재를 방해하는 것이 아니다. 또한, 본 발명의 일 형태는 상술한 과제 모두를 해결할 필요는 없는 것으로 한다. 또한, 이들 외의 과제는 명세서, 도면, 청구항 등의 기재로부터 저절로 명확해지는 것이며 명세서, 도면, 청구항 등의 기재로부터 이들 외의 과제를 추출할 수 있다.

본 발명의 일 형태는 산화물 반도체막을 섬 형상으로 미세 가공할 때, 하드 마스크를 사용함으로써 산화물 반도체막 단부의 요철을 억제할 수 있다. 또한, 전자 빔 또는 액침 노광 등을 사용하여 레지스트를 노광함으로써 형성된 선폭이 작은 레지스트 마스크를 사용함으로써 채널 길이를 짧게 할 수 있다. 구체적인 구성 및 제작 방법은 이하와 같다.

본 발명의 일 형태는 절연 표면 위의 산화물 반도체막과, 산화물 반도체막에 접하는 소스 전극 및 드레인 전극과, 소스 전극 및 드레인 전극 위의 게이트 절연막과, 게이트 절연막 위의, 산화물 반도체막과 중첩되는 위치에 게이트 전극을 갖고, 소스 전극과 드레인 전극 사이의 거리는 1nm 이상 30nm 이하이고, 산화물 반도체막의 라인 에지 거칠기(Line Edge Roughness: LER)의 표준 편차는 4nm 이하인 것을 특징으로 하는 반도체 장치다.

또한, 상술한 구성에서, 산화물 반도체막을 끼운 제 1 산화물막 및 제 2 산화물막을 갖고, 제 1 산화물막 및 제 2 산화물막은 전도대 하단의 에너지가 산화물 반도체막보다 0.05eV 이상 2eV 이하의 범위에서 진공 준위에 가까운 것을 특징으로 하는 반도체 장치다.

또한, 상술한 구성에서, 산화물 반도체막과 소스 전극 사이에 제공된 제 1 저저항 영역과, 산화물 반도체막과 드레인 전극 사이에 제공된 제 2 저저항 영역을 갖는다.

또한, 본 발명의 다른 일 형태는 절연 표면 위에 산화물 반도체막을 형성하고, 산화물 반도체막 위에 하드 마스크를 형성하고, 하드 마스크 위에 레지스트를 형성하고, 노광하여 레지스트 마스크를 형성하고, 레지스트 마스크를 마스크로 하여 하드 마스크를 가공하고, 레지스트 마스크를 제거하고, 가공된 하드 마스크를 마스크로 하여 산화물 반도체막을 가공하고, 가공된 하드 마스크를 제거하고, 가공된 산화물 반도체막에 접하는 소스 전극 및 드레인 전극을 형성하고, 소스 전극 및 드레인 전극 위에 게이트 절연막을 형성하고, 게이트 절연막 위에 있고 산화물 반도체막과 중첩되는 위치에 게이트 전극을 형성하는 것을 특징으로 하는 반도체 장치의 제작 방법이다.

또한, 본 발명의 다른 일 형태는 절연 표면 위에 산화물 반도체막을 형성하고, 산화물 반도체막 위에 하드 마스크를 형성하고, 하드 마스크 위에 유기 도포막을 형성하고, 유기 도포막 위에 레지스트를 형성하고, 노광하여 레지스트 마스크를 형성하고, 레지스트 마스크를 마스크로 하여 유기 도포막 및 하드 마스크를 가공하고, 레지스트 마스크와 가공된 유기 도포막을 제거하고, 가공된 하드 마스크를 마스크로 하여 산화물 반도체막을 가공하고, 가공된 하드 마스크를 제거하고, 가공된 산화물 반도체막에 접하는 소스 전극 및 드레인 전극을 형성하고, 소스 전극 및 드레인 전극 위에 게이트 절연막을 형성하고, 게이트 절연막 위에 있고 산화물 반도체막과 중첩되는 위치에 게이트 전극을 형성하는 것을 특징으로 하는 반도체 장치의 제작 방법이다.

또한, 상기 제작 방법에서, 노광은 전자 빔 노광 또는 액침 노광인 것을 특징으로 하는 반도체 장치의 제작 방법이다.

또한, 본 명세서에서 "하드 마스크"란 레지스트 재료 외의 재료(금속 재료나 절연 재료)를 사용하여 제작된 마스크를 말한다.

또한, 본 명세서에서 "라인 에지 거칠기"란 레지스트 단부가 직선으로부터 요철로 어긋난 정도를 말한다.

상술한 구성으로 함으로써 미세한 구조라도 높은 전기 특성을 갖는 트랜지스터를 수율 좋게 제공할 수 있다.

또한, 상술한 구성으로 함으로써 상기 트랜지스터를 포함하는 반도체 장치에서도 고성능화, 고신뢰성화, 및 고생산화를 달성할 수 있다.

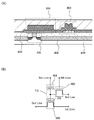

도 1은 본 발명의 일 형태에 따른 반도체 장치를 도시한 평면도 및 단면도.

도 2는 본 발명의 일 형태에 따른 반도체 장치의 제작 방법을 도시한 단면도.

도 3은 본 발명의 일 형태에 따른 반도체 장치의 제작 방법을 도시한 단면도.

도 4는 본 발명의 일 형태에 따른 반도체 장치를 도시한 평면도 및 단면도.

도 5는 본 발명의 일 형태에 따른 반도체 장치의 제작 방법을 도시한 단면도.

도 6은 본 발명의 일 형태에 따른 반도체 장치의 제작 방법을 도시한 단면도.

도 7은 본 발명의 일 형태에 따른 반도체 장치를 도시한 단면도.

도 8은 반도체 장치의 단면도 및 회로도.

도 9는 반도체 장치의 회로도 및 사시도.

도 10은 반도체 장치의 블록도.

도 11은 반도체 장치의 단면도.

도 12는 반도체 장치의 블록도.

도 13은 반도체 장치를 적용할 수 있는 전자 기기를 설명하기 위한 도면.

도 14는 실시예에서 제작한 시료의 SEM상을 설명하기 위한 도면.

도 15는 액침 노광 장치를 설명하기 위한 도면.

도 16은 렌즈의 개구각을 설명하기 위한 도면.

도 2는 본 발명의 일 형태에 따른 반도체 장치의 제작 방법을 도시한 단면도.

도 3은 본 발명의 일 형태에 따른 반도체 장치의 제작 방법을 도시한 단면도.

도 4는 본 발명의 일 형태에 따른 반도체 장치를 도시한 평면도 및 단면도.

도 5는 본 발명의 일 형태에 따른 반도체 장치의 제작 방법을 도시한 단면도.

도 6은 본 발명의 일 형태에 따른 반도체 장치의 제작 방법을 도시한 단면도.

도 7은 본 발명의 일 형태에 따른 반도체 장치를 도시한 단면도.

도 8은 반도체 장치의 단면도 및 회로도.

도 9는 반도체 장치의 회로도 및 사시도.

도 10은 반도체 장치의 블록도.

도 11은 반도체 장치의 단면도.

도 12는 반도체 장치의 블록도.

도 13은 반도체 장치를 적용할 수 있는 전자 기기를 설명하기 위한 도면.

도 14는 실시예에서 제작한 시료의 SEM상을 설명하기 위한 도면.

도 15는 액침 노광 장치를 설명하기 위한 도면.

도 16은 렌즈의 개구각을 설명하기 위한 도면.

실시형태에 대하여 도면을 사용하여 자세히 설명한다. 다만, 본 발명은 이하의 설명에 한정되지 않고, 본 발명의 취지 및 그 범위에서 벗어남이 없이 그 형태 및 자세한 사항을 다양하게 변경할 수 있는 것은 당업자라면 쉽게 이해할 수 있다. 따라서, 본 발명은 이하에 기재된 실시형태의 내용에 한정하여 해석되는 것이 아니다. 또한, 이하에서 설명하는 발명의 구성에서, 동일 부분 또는 같은 기능을 갖는 부분에는 동일한 부호를 상이한 도면간에서 공통적으로 사용하고, 그 반복 설명은 생략할 수 있다.

또한, 트랜지스터의 "소스"나 "드레인"의 기능은 상이한 극성을 갖는 트랜지스터가 적용되는 경우나, 또는 회로 동작에서 전류 방향이 변화하는 경우 등에, 서로 바뀔 수 있다. 따라서, 본 명세서에서, "소스"나 "드레인"이라는 용어는 서로 바꿔 사용할 수 있다.

본 명세서에서, "평행"이란, 2개의 직선이 -10° 이상 10° 이하의 각도로 배치된 상태를 말한다. 따라서, -5° 이상 5° 이하의 경우도 그 범주에 포함된다. 또한, "수직"이란, 2개의 직선이 80° 이상 100° 이하의 각도로 배치된 상태를 말한다. 따라서, 85° 이상 95° 이하의 경우도 그 범주에 포함된다.

또한, 본 명세서에서, 삼방정 또는 능면체정은 육방정계에 포함된다.

(실시형태 1)

본 실시형태는 본 발명의 일 형태에 따른 반도체 장치인 트랜지스터에 대하여 도면을 사용하여 설명한다.

도 1은 본 발명의 일 형태에 따른 트랜지스터(150)의 상면도 및 단면도다. 도 1의 (A)는 상면도이고, 도 1의 (A) 중 일점 쇄선 A1-A2를 따라 자른 단면도가 도 1의 (B)에 상당한다. 또한, 도 1의 (A)에 도시된 상면도에서는 도면을 명료화하기 위하여 요소를 일부 생략하여 도시하였다.

도 1에 도시된 트랜지스터(150)는 기판(100) 위의 하지 절연막(102)과, 하지 절연막(102) 위의 산화물 반도체막(104)과, 산화물 반도체막(104) 위의 저저항 영역(105a) 및 저저항 영역(105b)과, 저저항 영역(105a)에 접하는 소스 전극(106a)과, 저저항 영역(105b)에 접하는 드레인 전극(106b)과, 산화물 반도체막(104), 소스 전극(106a), 및 드레인 전극(106b) 위의 게이트 절연막(108)과, 게이트 절연막(108) 위의 게이트 전극(110)을 갖는다. 또한, 게이트 절연막(108) 및 게이트 전극(110) 위에 절연막(112)이 제공되어도 좋다. 절연막(112)은 필요에 따라 제공하면 좋고, 이 상부에 상이한 절연막을 더 제공하여도 좋다.

기판(100)에 큰 제한은 없다. 예를 들어, 유리 기판, 세라믹 기판, 석영 기판, 사파이어 기판 등을 기판(100)으로서 사용하여도 좋다. 또한 실리콘이나 탄화 실리콘으로 이루어지는 단결정 반도체 기판, 다결정 반도체 기판, 실리콘 게르마늄으로 이루어지는 화합물 반도체 기판, SOI(Silicon On Insulator) 기판 등을 적용할 수도 있고, 이들 기판 위에 반도체 소자가 제공된 것을 기판(100)으로서 사용하여도 좋다.

또한, 기판(100)으로서 제 5 세대(1000mm×1200mm 또는 1300mm×1500mm), 제 6 세대(1500mm×1800mm), 제 7 세대(1870mm×2200mm), 제 8 세대(2200mm×2500mm), 제 9 세대(2400mm×2800mm), 제 10 세대(2880mm×3130mm) 등의 대형 유리 기판을 사용하는 경우에는, 반도체 장치의 제작 공정에서의 가열 처리 등으로 인하여 생기는 기판(100)의 수축에 의하여, 미세 가공하기 어려워지는 경우가 있다. 그러므로, 상술한 바와 같은 대형 유리 기판을 기판(100)으로서 사용하는 경우, 가열 처리로 인하여 그다지 수축되지 않는 것을 사용하는 것이 바람직하다. 예를 들어, 400℃, 바람직하게는 450℃, 더 바람직하게는 500℃의 온도로 1시간 동안 가열 처리한 후의 수축량이 10ppm 이하, 바람직하게는 5ppm 이하, 더 바람직하게는 3ppm 이하인 대형 유리 기판을 기판(100)으로서 사용하면 좋다.

또한, 기판(100)으로서 가요성 기판을 사용하여도 좋다. 또한 가요성 기판 위에 트랜지스터를 제공하는 방법으로서는 비가요성 기판 위에 트랜지스터를 제작한 후, 트랜지스터를 박리하고, 가요성 기판인 기판(100)에 전치(轉置)하는 방법도 있다. 이 경우에는 비가요성 기판과 트랜지스터 사이에 박리층을 제공하면 좋다.

하지 절연막(102)은 기판(100)으로부터의 불순물 확산을 방지하는 역할에 더하여, 가열 처리를 수행함으로써 산소를 방출하여 산화물 반도체막에 산소를 공급하는 역할을 가질 수도 있기 때문에, 산소를 포함하는 절연막인 것이 바람직하고, 과잉 산소를 포함하는 절연막이 더 바람직하다. 또한, 상술한 바와 같이 기판(100)을 다른 디바이스가 형성된 기판으로 하는 경우, 하지 절연막(102)은 층간 절연막으로서도 기능한다. 이 경우, 표면이 평탄하게 되도록 CMP(Chemical Mechanical Polishing)법 등으로 평탄화 처리를 수행하는 것이 바람직하다.

하지 절연막(102)은 산화 실리콘막, 산화 갈륨막, 산화 아연막, 산화 알루미늄막, 갈륨 아연 산화물막, 질화 실리콘막, 산화 질화 실리콘막, 산화 질화 알루미늄막, 또는 질화 산화 실리콘막 중으로부터 선택된 한 층 또는 이들을 적층한 막을 사용할 수 있다.

여기서 가열 처리에 의하여 산소를 방출하는 막은, 막의 표면 온도가 100℃ 이상 700℃ 이하, 바람직하게는 100℃ 이상 500℃ 이하의 가열 처리로 수행되는 승온 이탈 가스(TDS: Thermal Desorption Spectroscopy) 분석에 의하여 1×1018atoms/cm3 이상, 1×1019atoms/cm3 이상, 또는 1×1020atoms/cm3 이상의 산소(산소 원자수로 환산)를 방출할 수도 있다.

또한, 가열 처리에 의하여 산소를 방출하는 막은, 과산화 라디칼을 포함한다. 구체적으로는 과산화 라디칼에 기인한 스핀 밀도가 5×1017spins/cm3 이상이다. 또한, 과산화 라디칼을 포함하는 막을 전자 스핀 공명(ESR: Electron Spin Resonance)으로 측정하면 g값이 2.01의 신호 근방에 비대칭의 신호를 가질 수도 있다.

또한, 과잉 산소를 포함하는 절연막은 산소가 과잉으로 포함된 산화 실리콘(SiOX(X>2))이라도 좋다. 산소가 과잉으로 포함된 산화 실리콘(SiOX(X>2))은 실리콘 원자수의 2배보다 많은 산소 원자를 단위 체적당 포함하는 것이다. 단위 체적당 실리콘 원자수 및 산소 원자수는 러더퍼드 후방 산란 분광법(RBS: Rutherford Backscattering Spectrometry)에 의하여 측정한 값이다.

산화물 반도체막(104)은 적어도 인듐을 포함하는 산화물 반도체막이다. 예를 들어, 인듐 외에 아연을 포함하여도 좋다.

산화물 반도체막(104)의 실리콘 농도에 대하여 이하에서 설명한다. 또한, 트랜지스터의 전기 특성을 안정하게 하기 위하여 산화물 반도체막(104) 중의 불순물 농도를 저감하여, 산화물 반도체막(104)을 진성 또는 실질적으로 진성으로 하는 것이 유효하다. 구체적으로 말하면 산화물 반도체막의 캐리어 밀도를 1×1017/cm3 미만, 1×1015/cm3 미만, 또는 1×1013/cm3 미만으로 하면 좋다. 또한, 산화물 반도체막에서 주성분 외(1atomic% 미만)의 경원소, 반금속 원소, 금속 원소 등은 불순물이 된다. 예를 들어, 수소, 질소, 탄소, 실리콘, 게르마늄은 산화물 반도체막 중에서 불순물이 된다.

또한, 산화물 반도체막(104) 중에서 수소 및 질소는 도너 준위를 형성하고 캐리어 밀도를 증대시킨다. 이차 이온 질량 분석법(SIMS: Secondary Ion Mass Spectrometry)에 의하여 측정하였을 때의 산화물 반도체막(104) 중의 수소 농도는 2×1020atoms/cm3 이하, 바람직하게는 5×1019atoms/cm3 이하, 더 바람직하게는 1×1019atoms/cm3 이하, 더욱 바람직하게는 5×1018atoms/cm3 이하로 한다. 또한, SIMS에 의하여 측정하였을 때의 산화물 반도체막(104) 중의 질소 농도는 5×1019atoms/cm3 미만, 바람직하게는 5×1018atoms/cm3 이하, 더 바람직하게는 1×1018atoms/cm3 이하, 더욱 바람직하게는 5×1017atoms/cm3 이하로 한다.

또한, 산화물 반도체막(104) 중의 수소 농도 및 질소 농도를 저감시키기 위하여 산화물 반도체막(104)에 근접하는 게이트 절연막(108) 중의 수소 농도 및 질소 농도를 저감하면 바람직하다.

또한, SIMS에 의하여 측정하였을 때의 산화물 반도체막(104) 중의 알칼리 금속 또는 알칼리 토금속의 농도는 1×1018atoms/cm3 이하, 바람직하게는 2×1016atoms/cm3 이하로 한다. 알칼리 금속 및 알칼리 토금속은 산화물 반도체와 결합하면 캐리어를 생성하는 경우가 있고, 트랜지스터의 오프 전류를 증대시킬 수 있다.

또한, 상술한 바와 같이 고순도화된 산화물 반도체막을 채널 형성 영역에 사용한 트랜지스터의 오프 전류는 매우 낮고, 트랜지스터의 채널 폭으로 정규화된 오프 전류는 수yA/μm~수zA/μm까지 저감할 수 있다.

또한, 산화물 반도체막을 미세 가공할 때는, 먼저, 산화물 반도체막 위에 하드 마스크, 유기 도포막, 및 레지스트를 형성하고 전자 빔 노광을 수행하여 유기 도포막 위에 레지스트 마스크를 형성하고, 하드 마스크 및 유기 도포막을 에칭한 후, 레지스트 마스크 및 하드 마스크를 마스크로 하여 산화물 반도체막을 에칭한다. 이와 같이 함으로써 산화물 반도체막의 라인 에지 거칠기를 저감할 수 있다. 또한, 전자 빔 노광에 한정되지 않고 ArF 엑시머 레이저를 광원으로 하는 액침 노광이나 EUV(Extreme Ultraviolet) 노광을 사용하여도 좋다.

상술한 바와 같이, 레지스트 마스크와 하드 마스크 사이에 유기 도포막을 제공함으로써 레지스트 마스크와 유기 도포막의 밀착성을 향상시킬 수 있다. 또한, 레지스트 마스크와 하드 마스크의 밀착성이 충분한 경우에는 유기 도포막을 제공하지 않아도 좋다. 또한, 산화물 반도체막의 미세 가공에 대한 자세한 사항은 나중에 기재한다.

산화물 반도체막은 단결정 산화물 반도체막 및 비단결정 산화물 반도체막으로 대별된다. 비단결정 산화물 반도체막이란, 비정질 산화물 반도체막, 미결정 산화물 반도체막, 다결정 산화물 반도체막, CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)막 등을 말한다.

비정질 산화물 반도체막은 막 중에서의 원자 배열이 불규칙하고, 결정 성분을 갖지 않는 산화물 반도체막이다. 미소 영역에서도 결정부를 갖지 않고, 막 전체가 완전한 비정질 구조인 산화물 반도체막이 전형적이다.

미결정 산화물 반도체막은 예를 들어, 크기가 1nm 이상 10nm 미만의 미결정(나노 결정이라고도 함)을 포함한다. 따라서, 미결정 산화물 반도체막은 비정질 산화물 반도체막보다 원자 배열의 규칙성이 높다. 그러므로 미결정 산화물 반도체막은 비정질 산화물 반도체막보다 결함 준위 밀도가 낮다는 특징을 갖는다.

CAAC-OS막은 복수의 결정부를 갖는 산화물 반도체막의 하나이며, 결정부의 대부분은 하나의 변이 100nm 미만인 입방체 내에 들어가는 크기다. 따라서, CAAC-OS막에 포함되는 결정부는 하나의 변이 10nm 미만, 5nm 미만, 또는 3nm 미만인 입방체 내에 들어가는 크기인 경우도 포함된다. CAAC-OS막은 미결정 산화물 반도체막보다 결함 준위 밀도가 낮다는 특징을 갖는다. 이하에서는, CAAC-OS막에 대하여 자세히 설명한다.

CAAC-OS막을 투과형 전자 현미경(TEM: Transmission Electron Microscope)에 의하여 관찰하면, 결정부들끼리의 명확한 경계, 즉, 결정 입계(그레인 바운더리라고도 함)는 확인되지 않는다. 따라서, CAAC-OS막은 결정 입계에 기인하는 전자 이동도의 저하가 일어나기 어렵다고 할 수 있다.

CAAC-OS막을 시료면에 대략 평행한 방향으로부터 TEM에 의하여 관찰(단면 TEM 관찰)하면, 결정부에서 금속 원자가 층상으로 배열되어 있는 것을 확인할 수 있다. 금속 원자의 각층은 CAAC-OS막이 형성되는 면(피형성면이라고도 함) 또는 CAAC-OS막의 상면의 요철이 반영된 형상이며 CAAC-OS막의 피형성면 또는 상면에 평행하게 배열된다.

한편, CAAC-OS막을 시료면에 대략 수직인 방향으로부터 TEM에 의하여 관찰(평면 TEM 관찰)하면, 결정부에서 금속 원자가 삼각형 또는 육각형으로 배열되어 있는 것을 확인할 수 있다. 그러나, 상이한 결정부들간에서 금속 원자의 배열에는 규칙성이 보이지 않는다.

단면 TEM 관찰 및 평면 TEM 관찰로부터, CAAC-OS막의 결정부는 배향성을 갖는 것을 알 수 있다.

CAAC-OS막에 대하여 X선 회절(XRD: X-Ray Diffraction) 장치를 사용하여 구조 해석을 수행하면, 예를 들어, InGaZnO4의 결정을 갖는 CAAC-OS막의 out-of-plane법에 의한 해석에서는, 회절각(2θ)이 31° 근방일 때 피크가 나타나는 경우가 있다. 이 피크는, InGaZnO4의 결정의 (009)면에 귀속되기 때문에, CAAC-OS막의 결정이 c축 배향성을 갖고, c축이 피형성면 또는 상면에 대략 수직인 방향으로 배향하는 것을 확인할 수 있다.

한편, CAAC-OS막에 대하여 c축에 대략 수직인 방향으로부터 X선을 입사시키는 in-plane법에 의한 해석에서는, 2θ가 56° 근방일 때 피크가 나타나는 경우가 있다. 이 피크는 InGaZnO4의 결정의 (110)면에 귀속된다. InGaZnO4의 단결정 산화물 반도체막의 경우에는, 2θ를 56° 근방에 고정하고, 시료면의 법선 벡터를 축(φ축)으로 하여 시료를 회전시키면서 분석(φ 스캔)을 수행하면, (110)면과 등가인 결정면에 귀속되는 6개의 피크가 관찰된다. 한편, CAAC-OS막의 경우에는, 2θ를 56° 근방에 고정하고 φ 스캔을 수행하여도 명료한 피크가 나타나지 않는다.

상술한 것으로부터, CAAC-OS막에서는, 상이한 결정부들간에서는 a축 및 b축의 배향이 불규칙하지만, c축 배향성을 가지며 c축이 피형성면 또는 상면의 법선 벡터에 평행한 방향으로 배향하는 것을 알 수 있다. 따라서, 상술한 단면 TEM 관찰로 확인된 층상으로 배열된 금속 원자의 각층은, 결정의 ab면에 평행한 면이다.

또한, 결정부는 CAAC-OS막을 형성하였을 때, 또는 가열 처리 등의 결정화 처리를 수행하였을 때에 형성된다. 상술한 바와 같이, 결정의 c축은 CAAC-OS막의 피형성면 또는 상면의 법선 벡터에 평행한 방향으로 배향한다. 따라서, 예를 들어 CAAC-OS막의 형상을 에칭 등에 의하여 변화시킨 경우, 결정의 c축이 CAAC-OS막의 피형성면 또는 상면의 법선 벡터에 평행하게 배향하지 않는 경우도 있다.

또한, CAAC-OS막 중의 결정화도가 균일하지 않아도 좋다. 예를 들어, CAAC-OS막의 결정부가 CAAC-OS막의 상면 근방으로부터의 결정 성장에 의하여 형성되는 경우에는, 상면 근방의 영역은 피형성면 근방의 영역보다 결정화도가 높게 되는 경우가 있다. 또한, CAAC-OS막에 불순물을 첨가하는 경우에는, 불순물이 첨가된 영역의 결정화도가 변화되어, 부분적으로 결정화도가 상이한 영역이 형성될 수도 있다.

또한, InGaZnO4의 결정을 갖는 CAAC-OS막의 out-of-plane법에 의한 해석에서는, 2θ가 31° 근방일 때 나타나는 피크에 더하여, 2θ가 36° 근방일 때도 피크가 나타나는 경우가 있다. 2θ가 36° 근방일 때 나타나는 피크는 CAAC-OS막 중의 일부에, c축 배향성을 갖지 않는 결정이 포함되는 것을 가리킨다. CAAC-OS막은 2θ가 31° 근방일 때 피크가 나타나고, 2θ가 36° 근방일 때 피크가 나타나지 않는 것이 바람직하다.

CAAC-OS막을 사용한 트랜지스터는, 가시광이나 자외광의 조사에 의한 전기 특성의 변동이 작다. 따라서, 상기 트랜지스터는 신뢰성이 높다.

또한, 산화물 반도체막은 예를 들어 비정질 산화물 반도체막, 미결정 산화물 반도체막, CAAC-OS막 중 2종류 이상을 갖는 적층막이라도 좋다.

CAAC-OS막은 예를 들어, 다결정인 산화물 반도체 스퍼터링용 타깃을 사용하여 스퍼터링법에 의하여 형성할 수 있다. 상기 스퍼터링용 타깃에 이온이 충돌되면, 스퍼터링용 타깃에 포함되는 결정 영역이 a-b면으로부터 벽개(劈開)하여 a-b면에 평행한 면을 갖는 평판 형상, 또는 펠릿(pellet) 형상의 스퍼터링 입자로서 박리될 수 있다. 이 경우, 상기 평판 형상의 스퍼터링 입자가 결정 상태를 유지한 채로 기판에 도달됨으로써 CAAC-OS막을 형성할 수 있다.

또한, CAAC-OS막을 형성하기 위하여 이하의 조건을 적용하는 것이 바람직하다.

성막 시의 불순물 혼입을 저감함으로써, 불순물로 인하여 결정 상태가 무너지는 것을 억제할 수 있다. 예를 들어, 성막실 중에 존재하는 불순물(수소, 물, 이산화탄소, 및 질소 등)을 저감하면 좋다. 또한, 성막 가스 중의 불순물을 저감하면 좋다. 구체적으로는, 이슬 점이 -80℃ 이하, 바람직하게는 -100℃ 이하, 더 바람직하게는 -120℃ 이하인 성막 가스를 사용한다.

또한, 성막 시의 기판 가열 온도를 높게 함으로써, 스퍼터링 입자가 기판에 도달한 후에 스퍼터링 입자의 마이그레이션(migration)이 일어난다. 구체적으로는, 기판 가열 온도를 100℃ 이상 740℃ 이하, 바람직하게는 200℃ 이상 500℃ 이하로 하여 성막한다. 성막 시의 기판 가열 온도를 높게 함으로써, 평판 형상의 스퍼터링 입자가 기판에 도달한 경우에, 기판 위에서 마이그레이션이 일어나 스퍼터링 입자의 평평한 면이 기판에 부착된다.

또한, 성막 가스 중의 산소 비율을 높여 전력을 최적화시킴으로써 성막 시의 플라즈마 대미지를 경감시키면 바람직하다. 성막 가스 중의 산소 비율은 30체적% 이상, 바람직하게는 100체적%로 한다.

스퍼터링용 타깃의 일례로서, In-Ga-Zn-O 화합물 타깃에 대해서 이하에 기재한다.

InOX 분말, GaOY 분말, 및 ZnOZ 분말을 소정의 mol수비로 혼합하고 가압 처리를 한 후, 1000℃ 이상 1500℃ 이하의 온도로 가열 처리함으로써 다결정인 In-Ga-Zn-O 화합물 타깃으로 한다. 또한, X, Y, 및 Z는 임의의 양수다. 여기서, 분말의 종류 및 이들을 혼합하는 mol수비는, 제작하는 스퍼터링용 타깃에 따라 적절히 변경하면 좋다.

또한 산화물 반도체막(104)에 실리콘 및 탄소가 높은 농도로 포함됨으로써 산화물 반도체막(104)의 결정성을 저하시킬 수 있다. 산화물 반도체막(104)의 결정성을 저하시키지 않기 위해서는 산화물 반도체막(104) 중의 실리콘 농도를 1×1019atoms/cm3 미만, 바람직하게는 5×1018atoms/cm3 미만, 더 바람직하게는 2×1018atoms/cm3 미만으로 하면 좋다. 또한, 산화물 반도체막(104)의 결정성을 저하시키지 않기 위해서는 산화물 반도체막(104) 중의 탄소 농도를 1×1019atoms/cm3 미만, 바람직하게는 5×1018atoms/cm3 미만, 더 바람직하게는 2×1018atoms/cm3 미만으로 하면 좋다.

이와 같이, 채널이 형성되는 산화물 반도체막(104)이 높은 결정성을 가지며, 불순물이나 결함 등에 기인하는 준위 밀도가 낮은 경우, 산화물 반도체막(104)을 사용한 트랜지스터는 안정된 전기 특성을 갖는다.

소스 전극(106a) 및 드레인 전극(106b)은 산화물 반도체막을 구성하는 금속 원소보다 산소와 결합하기 쉬운 도전 재료를 사용할 수 있다. 예를 들어, Al, Cr, Cu, Ta, Mo, W, Ti 등을 사용할 수 있다. 나중의 프로세스 온도를 비교적 높게 할 수 있는 등의 이유로, 융점이 높은 W을 사용하는 것이 특히 바람직하다. 또한, 산소와 결합하기 쉬운 도전 재료에는 산소가 확산되기 쉬운 재료도 포함된다. 또한, W 위에 Cu 등 상술한 재료를 복수로 적층하여도 좋다.

소스 전극 및 드레인 전극이 되는 도전막의 재료가 산화물 반도체막을 구성하는 금속 원소보다 산소와 결합하기 쉬운 도전 재료이기 때문에 산화물 반도체막(104) 중의 산소가 도전 재료와 결합한다. 이 결합에 의하여 산화물 반도체막(104) 중 도전막과의 계면 근방의 영역에 산소 결손이 생긴다. 또는, 산화물 반도체막(104) 위에 형성되는 도전막을 형성할 때, 산화물 반도체막(104) 상면에 대한 대미지(산소 결손)가 생긴다. 이 산소 결손과 수소에 의하여 저저항화된 영역, 즉, 저저항 영역(105a) 및 저저항 영역(105b)이 형성되고 산화물 반도체막과 소스 전극 또는 드레인 전극과의 접촉 저항이 저감된다. 또한, 가열 처리를 수행함으로써 도전막의 재료가 산화물 반도체막 중에 확산되기 쉬운 도전 재료인 경우라도 저저항 영역(105a) 및 저저항 영역(105b)이 형성된다.

따라서, 저저항 영역(105a)과 저저항 영역(105b) 사이의 산화물 반도체막(104) 중의 영역(A)과, 소스 전극(106a)과 접하지 않는 위치에 있는 저저항 영역(105a)의 영역 및 드레인 전극(106b)과 접하지 않는 위치에 있는 저저항 영역(105b)의 영역을 합친 영역(A1)(도시되지 않았음)이 트랜지스터(150)의 채널 형성 영역이 된다. 트랜지스터(150)의 채널 형성 영역은 저저항화(n형화라고도 함)되기 때문에 산화물 반도체막(104) 중의 불순물 농도를 저감하여 고순도 진성화할 필요가 있다. 고순도 진성화란, 산화물 반도체막을 진성 또는 실질적으로 진성으로 하는 것을 말한다. 또한, 실질적으로 진성이라고 하는 경우, 산화물 반도체막 중의 캐리어 밀도는 1×1017cm3 미만, 바람직하게는 1×1015cm3 미만, 더 바람직하게는 1×1013cm3 미만이다.

트랜지스터(150)의 채널 형성 영역을 고순도 진성화하기 위해서는 산화물 반도체막(104)의 영역(A) 및 영역(A1)에 대하여 산소를 첨가하면 좋다. 이와 같이 함으로써 산소 결손량을 저감할 수 있어 고순도 진성인 영역을 형성할 수 있다. 따라서 자기 정합적으로 고순도 진성인 영역과 저저항 영역을 형성할 수 있다.

또한, 가열 처리함으로써 하지 절연막(102) 및 절연막(112)으로부터 과잉 산소를 방출하기 쉽게 하여 산화물 반도체막(104) 중의 산소 결손을 저감할 수 있다. 따라서 산화물 반도체막(104) 중의 채널 형성 영역은 산소 결손량이 더욱 저감되어 고순도 진성화될 수 있다.

게이트 절연막(108)은 산화 알루미늄, 산화 마그네슘, 산화 실리콘, 산화 질화 실리콘, 질화 산화 실리콘, 질화 실리콘, 산화 갈륨, 산화 게르마늄, 산화 이트륨, 산화 지르코늄, 산화 란타넘, 산화 네오디뮴, 산화 하프늄, 및 산화 탄탈럼을 1종류 이상 포함하는 절연막을 단층 또는 적층으로 사용하면 좋다.

게이트 절연막(108)은 예를 들어, 산화 실리콘막을 사용하면 좋다. 산화 실리콘막은 결함 밀도가 작은 산화 실리콘막을 사용하면 바람직하다. 구체적으로는 ESR로 측정하면, g값이 2.001의 신호에서 유래하는 스핀 밀도가 3×1017spins/cm3 이하, 바람직하게는 5×1016spins/cm3 이하인 산화 실리콘막을 사용한다. 산화 실리콘막은 과잉 산소를 포함하는 산화 실리콘막을 사용하면 바람직하다.

게이트 전극(110)은 Al, Ti, Cr, Co, Ni, Cu, Y, Zr, Mo, Ru, Ag, Ta, 및 W 등의 도전막을 사용할 수 있다. 또한, 게이트 전극(110)은 상술한 재료의 적층이라도 좋다.

절연막(112)은 산화 알루미늄, 산화 마그네슘, 산화 실리콘, 산화 질화 실리콘, 질화 산화 실리콘, 질화 실리콘, 산화 갈륨, 산화 게르마늄, 산화 이트륨, 산화 지르코늄, 산화 란타넘, 산화 네오디뮴, 산화 하프늄, 및 산화 탄탈럼을 1종류 이상 포함하는 절연막을 단층 또는 적층으로 사용하면 좋다.

절연막(112)은 예를 들어, 첫 번째 층을 산화 실리콘막으로 하고, 두 번째 층을 질화 실리콘막으로 한 적층막으로 하면 좋다. 이 경우 산화 실리콘막을 산화 질화 실리콘막으로 하여도 좋다. 또한, 질화 실리콘막은 질화 산화 실리콘막으로 하여도 좋다. 산화 실리콘막은 결함 밀도가 작은 산화 실리콘막을 사용하면 바람직하다. 구체적으로는 ESR로 측정하면 g값이 2.001의 신호에서 유래하는 스핀 밀도가 3×1017spins/cm3 이하, 바람직하게는 5×1016spins/cm3 이하인 산화 실리콘막을 사용한다. 질화 실리콘막은 수소 가스 및 암모니아 가스의 방출량이 적은 질화 실리콘막을 사용한다. 수소 가스 및 암모니아 가스의 방출량은 승온 TDS 분석에 의하여 측정하면 좋다. 또한, 질화 실리콘막은 수소, 물, 및 산소를 투과시키지 않는 질화 실리콘막, 또는 거의 투과시키지 않는 질화 실리콘막을 사용한다.

또한, 절연막(112)은 예를 들어, 첫 번째 층을 제 1 산화 실리콘막으로 하고, 두 번째 층을 제 2 산화 실리콘막으로 하고, 세 번째 층을 질화 실리콘막으로 한 적층막으로 하면 좋다. 이 경우 제 1 산화 실리콘막 및 제 2 산화 실리콘막 중 한쪽 또는 양쪽을 산화 질화 실리콘막으로 하여도 좋다. 또한, 질화 실리콘막은 질화 산화 실리콘막으로 하여도 좋다. 제 1 산화 실리콘막은 결함 밀도가 작은 산화 실리콘막을 사용하면 바람직하다. 구체적으로는 ESR로 측정하면, g값이 2.001의 신호에서 유래하는 스핀 밀도가 3×1017spins/cm3 이하, 바람직하게는 5×1016spins/cm3 이하인 산화 실리콘막을 사용한다. 제 2 산화 실리콘막은 과잉 산소를 포함하는 산화 실리콘막을 사용한다. 질화 실리콘막은 수소 가스 및 암모니아 가스의 방출량이 적은 질화 실리콘막을 사용한다. 수소 가스 및 암모니아 가스의 방출량은 TDS 분석에 의하여 측정하면 좋다. 또한, 질화 실리콘막은 수소, 물, 및 산소를 투과시키지 않는 질화 실리콘막, 또는 거의 투과시키지 않는 질화 실리콘막을 사용한다.

게이트 절연막(108) 및 절연막(112) 중 적어도 한쪽이 과잉 산소를 포함하는 절연막을 포함하는 경우, 산화물 반도체막(104)의 산소 결손이 저감되고 트랜지스터에 안정된 전기 특성을 부여할 수 있다.

다음에 트랜지스터(150)의 제작 방법에 대하여 도 2 및 도 3을 사용하여 설명한다.

먼저, 기판(100)을 준비한다.

다음에, 하지 절연막(102)을 형성한다. 그 후, 하지 절연막(102) 위에 산화물 반도체막(103)을 형성한다(도 2의 (A) 참조). 하지 절연막은 기판(100) 측으로부터의 불순물 침입을 억제하는 기능을 갖는다. 하지 절연막은 플라즈마 CVD(Chemical Vapor Deposition)법 또는 스퍼터링법 등에 의하여 형성할 수 있다.

산화물 반도체막(103)은 스퍼터링법, CVD법, MBE법, ALD법 또는 PLD법을 사용하여 형성하면 좋다.

스퍼터링법을 사용하여 산화물 반도체막(103)을 형성하는 경우, 플라즈마를 발생시키기 위한 전원 장치는 RF 전원 장치, AC 전원 장치, DC 전원 장치 등을 적절히 사용할 수 있다.

스퍼터링 가스는 희가스(대표적으로는 아르곤) 분위기, 산소 분위기, 희가스 및 산소의 혼합 가스를 적절히 사용한다. 또한, 희가스 및 산소의 혼합 가스의 경우, 희가스에 대하여 산소의 가스 비율을 높이는 것이 바람직하다.

또한, 타깃은 형성하는 산화물 반도체막(103)의 조성에 맞추어 적절히 선택하면 좋다.

스퍼터링법을 사용하는 경우, 적어도 산화물 반도체막(103)을 다음과 같이 형성함으로써 CAAC-OS를 형성할 수 있다. 구체적으로는 기판 온도를 150℃ 이상 500℃ 이하, 바람직하게는 150℃ 이상 450℃ 이하, 더 바람직하게는 200℃ 이상 350℃ 이하로 하여 가열하면서 산화물 반도체막(103)을 형성한다.

다음에 제 1 가열 처리를 수행하는 것이 바람직하다. 제 1 가열 처리는 250℃ 이상 650℃ 이하, 바람직하게는 300℃ 이상 500℃ 이하로 수행하면 좋다. 제 1 가열 처리의 분위기는 불활성 가스 분위기, 산화성 가스를 10ppm 이상, 바람직하게는 1% 이상, 더 바람직하게는 10% 이상 포함하는 분위기, 또는 감압 상태에서 수행한다. 또는 제 1 가열 처리의 분위기는 불활성 가스 분위기에서 가열 처리한 후에 이탈된 산소를 보전하기 위하여 산화성 가스를 10ppm 이상, 바람직하게는 1% 이상, 더 바람직하게는 10% 이상 포함하는 분위기에서 가열 처리를 수행하여도 좋다. 제 1 가열 처리를 수행함으로써 산화물 반도체막(103)의 결정성을 높이면서, 산화물 반도체막으로부터 물, 수소, 질소, 및 탄소 등의 불순물을 제거할 수 있다.

다음에 산화물 반도체막(103) 위에 하드 마스크(120), 하드 마스크(120) 위에 유기 도포막(122)을 형성하고, 유기 도포막(122) 위에 레지스트를 형성하고, 상기 레지스트에 대하여 전자 빔을 사용한 노광을 수행하여 레지스트 마스크(124)를 형성한다(도 2의 (B) 참조).

하드 마스크(120)는 Ti, Mo, Ta, 및 W 중 한 종류 이상 포함하는, 단체나, 질화물, 또는 합금을 단층 또는 적층으로 하여 사용하면 좋다. 또는, 산화 실리콘 등의 산화물 절연막이나 질화 실리콘 등의 질화물 절연막을 사용하여도 좋다. 또는 적어도 In 및 Zn을 포함하는 산화물 또는 산질화물을 사용하여도 좋다. 예를 들어, In-Ga-Zn-O-N계 재료 등을 사용하면 좋다.

상술한 바와 같이, 레지스트 마스크(124)와 하드 마스크(120) 사이에 유기 도포막(122)을 제공함으로써 레지스트 마스크(124)와 유기 도포막(122)의 밀착성을 향상시킬 수 있다. 또한, 레지스트 마스크(124)와 하드 마스크(120)의 밀착성이 충분한 경우에는 유기 도포막(122)은 제공하지 않아도 좋지만, 유기 도포막(122)을 제공함으로써 하드 마스크(120), 유기 도포막(122), 및 레지스트 사이의 밀착성을 향상시킬 수 있고 생산성 및 신뢰성을 향상시킬 수 있다.

유기 도포막(122)은 반사 방지막(BARC: Bottom Anti Reflective Coating), 예를 들어, SWK-T7(TOKYO OHKA KOGYO CO., LTD제)이나 밀착 증강제, 예를 들어, AZ AD프로모터(AZ ELECTRONIC MATERIALS제) 등을 사용할 수 있다.

전자 빔을 조사할 수 있는 전자 빔 묘화 장치에서 예를 들어, 가속 전압은 5kV~50kV인 것이 바람직하다. 또한, 전류 강도는 5×10-12A 이상 1×10-11A 이하인 것이 바람직하다. 또한, 최소 빔 직경은 2nm 이하인 것이 바람직하다. 또한, 제작할 수 있는 패턴의 최소 선폭이 8nm 이하인 것이 바람직하다.

상술한 조건을 사용함으로써 예를 들어, 레지스트 마스크(124)의 폭을 1nm 이상 30nm 이하, 바람직하게는 20nm 이하, 더 바람직하게는 8nm 이하로 할 수 있다.

또한, 전자 빔을 사용한 노광에서는 미세한 선폭을 갖는 레지스트 마스크(124)로 하기 위하여 가능한 한 레지스트 마스크(124)는 얇은 것이 바람직하다. 레지스트 마스크(124)를 얇게 하는 경우에는 피형성면의 요철을 가능한 한 평탄하게 하는 것이 바람직하다. 본 실시형태에 따른 반도체 장치의 제작 방법에서는 하지 절연막(102) 등에 CMP 처리 등의 연마 처리, 에칭(드라이 에칭, 웨트 에칭) 처리나, 플라즈마 처리 등의 평탄화 처리를 수행함으로써 하지 절연막(102) 등에 기인한 요철이 저감되기 때문에 레지스트 마스크를 얇게 할 수 있다. 이로써, 전자 빔을 사용한 노광을 쉽게 할 수 있다.

또한, 트랜지스터(150)의 채널 길이는 트랜지스터 내의 어디에서나 균일한 것이 바람직하다. 트랜지스터의 채널 형성 영역의 형상에 곡선이 포함되는 경우에, 전자 빔을 사용한 노광에 의하여 상기 곡선을 완만하게 하고, 또한 선폭을 균일하게 형성하는 것이 바람직하다. 또한 "채널 길이"란, 트랜지스터의 소스 전극과 드레인 전극 사이의 거리를 말한다.

선폭이 균일하고 완만한 곡선을 전자 빔을 사용한 노광에 의하여 제작하기 위해서는 예를 들어, 기판이 실려 있는 스테이지를 회전시킴으로써 곡선을 노광하는 방법 등이 있다. 또한, 직선상으로 이동하는 스테이지를 사용하더라도, 전자 빔에 의한 묘화 영역을 분할하는 도형 사이즈나 방향을 전자 빔의 패턴에 맞추어 최적화시키는 방법이나, 패턴의 노광량이 일정하게 되도록 도형을 균일한 폭으로 어긋나게 하여 겹쳐 그리는 다중 묘화법 등을 적용함으로써, 트랜지스터의 채널 길이가 균일하게 되도록 레지스트 마스크를 패터닝할 수 있다. 상술한 방법 등을 사용하여 레지스트 마스크의 선폭을 균일하게 형성하여 트랜지스터(150)의 채널 길이를 균일하게 하는 것이 바람직하다.

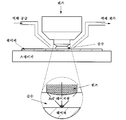

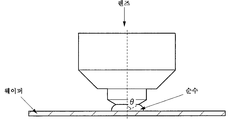

또한, 노광에는 ArF 엑시머 레이저를 광원으로 하는 액침 노광이나 EUV 노광을 사용하여도 좋다. 여기서 ArF 엑시머 레이저를 광원으로 하는 액침 노광에 대하여 도 15 및 도 16을 사용하여 설명한다.

먼저, 노광 장치의 해상도에 대하여 설명한다. 노광 선폭은 이하의 Rayleigh의 식을 사용하여 산출된다.

[수학식 1]

여기서, R은 노광 선폭, k는 레지스트 재료와 노광 방식으로 결정되는 비례상수, λ는 노광 파장, NA는 투영 렌즈의 밝기(개구수)다. 또한, NA는 이하의 식으로 산출된다.

[수학식 2]

여기서, n은 렌즈-레지스트 사이의 굴절률, θ는 도 16에 도시된 렌즈의 개구각이다.

노광 선폭(R)을 작게 하여 고해상도화하기 위해서는 광원의 단파장화나 NA를 크게 할 필요가 있다. 그래서 NA를 크게 하기 위하여 도 15에 도시된 바와 같이 노광 장치의 투영 렌즈와 웨이퍼 사이에 액체(순수, n=1.44)를 채운다.

투영 렌즈와 웨이퍼 사이에 액체(순수)를 채움으로써 렌즈-레지스트 사이의 굴절률(n)이 커지고, 이에 따라 NA도 커지기 때문에 결과적으로 노광 선폭(R)이 작게 되어 해상도를 높게 할 수 있다.

또한, NA를 지나치게 크게 하면 노광광이 임계각을 넘어 렌즈의 계면에서 전반사가 일어난다. 임계각은 이하의 식으로 산출된다.

[수학식 3]

여기서, CA는 임계각, n1은 입사 광선의 굴절률, n2는 반사 광선의 굴절률이다.

예를 들어, n1을 1.5로 하였을 때, 투영 렌즈와 웨이퍼 사이에 아무것도 없는(공기뿐, n=1.0) 경우의 임계각은 42°이지만, 액침 기술을 사용하는 경우(액체가 순수인 경우)의 임계각은 73°가 된다. 따라서 액침 기술을 사용함으로써 입사 가능 각도를 넓게 하고 NA를 크게 할 수 있다.

다음에 레지스트 마스크(124)를 마스크로 하여 유기 도포막(122) 및 하드 마스크(120)를 선택적으로 에칭함으로써 유기 도포막(123) 및 하드 마스크(121)를 형성한다(도 2의 (C) 참조).

또한, 하드 마스크(121)에는 레지스트 마스크(124)에 대한 에칭 선택 비율이 높고 레지스트 마스크(124)가 얇더라도 패턴을 쉽게 형성할 수 있는 것을 사용하는 것이 바람직하다. 또한, 하드 마스크(121)는 산화물 반도체막(103)을 에칭할 때에 마스크로서 사용하기 때문에 산화물 반도체막(103)을 에칭하는 조건에서 에칭되기 어려운 막인 것이 바람직하다.

다음에 레지스트 마스크(124) 및 하드 마스크(121)를 마스크로 하여 산화물 반도체막(103)을 선택적으로 에칭하여 산화물 반도체막(104)을 형성한다(도 2의 (D) 참조).

다음에, 산화물 반도체막(104) 위의, 하드 마스크(121), 유기 도포막(123), 및 레지스트 마스크(124)를 제거한다(도 3의 (A) 참조). 제거 처리에 특별히 한정은 없고 예를 들어, 에칭이나 산소 플라즈마에 의한 애싱 등을 수행하면 좋다.

또한, 산화물 반도체막(103)을 에칭하기 전에 유기 도포막(123) 및 레지스트 마스크(124)를 산소 플라즈마에 의한 애싱으로 제거하고, 이 후, 산화물 반도체막(103)을 에칭하여 산화물 반도체막(104)을 형성하고 나서 하드 마스크(121)를 제거하여도 좋다.

다음에 하지 절연막(102) 및 산화물 반도체막(104) 위에 소스 전극(106a) 및 드레인 전극(106b)이 되는 도전막을 형성하고, 도전막의 일부를 가공하여 소스 전극(106a) 및 드레인 전극(106b)을 형성한다(도 3의 (B) 참조). 이 때, 소스 전극(106a) 및 드레인 전극(106b)의 단부는 도시된 바와 같이, 계단 형상으로 형성한다. 상기 단부의 가공은 애싱에 의하여 레지스트 마스크를 축소시키는 공정과 에칭 공정을 교대로 여러 번 수행함으로써 형성할 수 있다. 도전막은 상술한 소스 전극(106a) 및 드레인 전극(106b)의 재료를 사용하여 스퍼터링법, CVD법, MBE법, ALD법, 또는 PLD법을 사용하여 형성하면 좋다.

또한, 소스 전극(106a) 및 드레인 전극(106b)이 되는 도전막의 재료는 산화물 반도체막을 구성하는 금속 원소보다 산소와 결합하기 쉬운 도전 재료를 사용한다. 이 때, 도전막의 재료가 산소와 결합하기 쉬운 도전 재료이기 때문에 산화물 반도체막(104) 중의 산소가 도전 재료(도전막)와 결합한다. 이 결합에 의하여 산화물 반도체막(104) 중 도전막과의 계면 근방의 영역에 산소 결손이 생긴다. 또는, 산화물 반도체막(104) 위에 형성되는 도전막을 형성할 때, 산화물 반도체막(104) 상면에 대한 대미지(산소 결손)가 생긴다. 이들 산소 결손에 의하여 저저항 영역(105)이 형성된다. 또한, 본 실시형태에서는 저저항 영역(105)은 산화물 반도체막(104)과 도전막의 계면으로부터 산화물 반도체막(104)의 깊이 방향으로 0nm 보다 크고 15nm 이하, 바람직하게는 10nm 미만, 더 바람직하게는 3nm 미만의 영역에 있다.

저저항 영역(105)이 형성됨으로써 나중에 형성되는 소스 전극 또는 드레인 전극과 산화물 반도체막(104)과의 접촉 저항을 저감할 수 있어 트랜지스터(150)의 고속 동작을 구현할 수 있다.

또한, 상술한 애싱에 의하여 레지스트 마스크를 축소시키는 공정과 에칭 공정을 교대로 여러 번 수행함으로써, 소스 전극(106a) 및 드레인 전극(106b)의 단부는 나중에 형성되는 저저항 영역(105a) 및 저저항 영역(105b) 위에 제공된다.

이로써 산화물 반도체막 중의 상술한 영역(A)을 포함하는, 저저항 영역(105) 중 소스 전극(106a) 및 드레인 전극(106b)과 접하지 않는 영역(B)(=영역(A)+영역(A1))이 트랜지스터(150)의 채널 형성 영역이 된다. 트랜지스터(150)의 채널 형성 영역은 n형화되기 때문에 산화물 반도체막(104) 중의 불순물 농도를 저감하여 고순도 진성화할 필요가 있다.

다음에 게이트 절연막(108)을 형성한다(도 3의 (C) 참조). 게이트 절연막(108)은 상술한 게이트 절연막(108)의 재료를 사용하여 스퍼터링법, CVD법, MBE법, ALD법, 또는 PLD법을 사용하여 형성하면 좋다.

다음에 산화물 반도체막의 채널 형성 영역이 되는 영역(B)에 대하여 산소를 첨가하여 저저항 영역(105a) 및 저저항 영역(105b)을 형성한다.

산화물 반도체막의 영역(B)에 산소를 첨가하는 방법으로서, 이온 도핑법 또는 이온 주입법을 사용할 수 있다. 또는, 산소를 첨가하는 방법으로서, 플라즈마 잠입 이온 주입법을 사용하여도 좋다. 또한, 산소의 첨가는 이온 도핑법 또는 이온 주입법 등에 의한 주입 방법 외의 방법으로도 수행할 수 있다. 예를 들어, 산소 분위기에서 플라즈마를 발생시켜, 영역(B)에 대하여 플라즈마 처리를 수행함으로써 산소를 첨가할 수 있다. 상술한 플라즈마를 발생시키는 장치로서는 드라이 에칭 장치나 플라즈마 CVD 장치, 고밀도 플라즈마 CVD 장치 등을 사용할 수 있다.

산화물 반도체막의 영역(B)에 첨가하는 산소는, 산소 라디칼, 산소 원자, 및 산소 이온 중 하나 이상이다. 또한, 산소는 영역(B) 중 적어도 일부, 대표적으로는 영역(B)의 산화물 반도체막의 표면, 영역(B)의 산화물 반도체막 중, 및 영역(B)의 산화물 반도체막과 하지 절연막(102)의 계면 중 어느 하나에 첨가되면 좋다.

이온 도핑법 또는 이온 주입법을 사용하여 산소를 산화물 반도체막의 영역(B)에 첨가할 때의 산소 첨가량은, 5×1019/cm3 이상 5×1021/cm3 이하다. 이 때, 산소의 에너지가 높으면, 산화물 반도체막의 영역(B)에 대미지가 생겨, 물리적으로 결함이 생기기 때문에, 산화물 반도체막에 대미지가 생기지 않을 정도의 산소의 에너지로 하는 것이 바람직하다. 또한, 산화물 반도체막의 영역(B)은 표층으로부터 산화물 반도체막의 깊이 방향으로 산소의 함유량이 서서히 많아지는 영역을 갖는다.

또한, 저저항 영역(105a)은 모두가 소스 전극과 중첩될 필요는 없고, 저저항 영역(105b) 측으로 연장되어 소스 전극과 중첩되지 않는 영역이 있어도 좋다. 또한, 저저항 영역(105b)은 모두가 드레인 전극과 중첩될 필요는 없고, 저저항 영역(105a) 측으로 연장되어 드레인 전극과 중첩되지 않는 영역이 있어도 좋다. 또한, 저저항 영역(105a) 및 저저항 영역(105b)의 막 두께는 균일하지 않아도 좋다. 예를 들어, 소스 전극과 중첩되지 않는 측의 저저항 영역(105a)의 단부는 저저항 영역(105a)의 저면으로부터 표면으로 향하여 완만하게 넓어져도 좋다. 마찬가지로 예를 들어, 드레인 전극과 중첩되지 않는 측의 저저항 영역(105b)의 단부는 저저항 영역(105b)의 저면으로부터 표면으로 향하여 완만하게 넓어져도 좋다. 또한, 소스 전극(106a)과 드레인 전극(106b) 사이의 거리와, 저저항 영역(105a)과 저저항 영역(105b) 사이의 거리의 차이는 소스 전극(106a)과 드레인 전극(106b) 사이의 거리의 30% 미만, 바람직하게는 10% 미만, 더 바람직하게는 3% 미만이다.

다음에, 제 2 가열 처리를 수행하는 것이 바람직하다. 제 2 가열 처리는 제 1 가열 처리와 마찬가지의 조건에서 수행할 수 있다. 제 2 가열 처리에 의하여 산화물 반도체막(104)으로부터 수소나 물 등의 불순물을 더 제거할 수 있다.

다음에 게이트 절연막(108) 위에 게이트 전극(110)이 되는 도전막을 형성하고, 도전막의 일부를 가공함으로써 게이트 전극(110)을 형성한다. 도전막은 상술한 게이트 전극(110)의 재료를 사용하여 스퍼터링법, CVD법, MBE법, ALD법, 또는 PLD법을 사용하여 형성하면 좋다.

다음에 소스 전극(106a), 드레인 전극(106b), 및 게이트 전극(110) 위에 절연막(112)을 형성한다(도 3의 (D) 참조). 절연막(112)은 플라즈마 CVD법 또는 스퍼터링법 등에 의하여 형성할 수 있다.

다음에, 제 3 가열 처리를 수행하는 것이 바람직하다. 제 3 가열 처리는 제 1 가열 처리와 마찬가지의 조건에서 수행할 수 있다. 산소가 과잉으로 포함되는 하지 절연막(102)이나 절연막(112)의 경우, 제 3 가열 처리를 수행함으로써 하지 절연막(102)이나 절연막(112)으로부터 과잉 산소가 방출되기 쉬워져 산화물 반도체막(104)의 산소 결손을 저감할 수 있다. 따라서 산화물 반도체막(104) 중의 채널 형성 영역은 산소 결손량이 더욱 저감되고 고순도 진성화된다.

상술한 공정을 거쳐 트랜지스터(150)를 제작할 수 있다.

이와 같은 제작 방법을 사용함으로써 산화물 반도체막을 섬 형상으로 미세 가공할 때에 산화물 반도체막 단부의 요철을 억제할 수 있다. 따라서 미세한 구조라도 높은 전기 특성을 갖는 트랜지스터를 수율 좋게 제공할 수 있다. 또한, 상기 트랜지스터를 포함하는 반도체 장치에서도 고성능화, 고신뢰성화, 및 고생산화를 달성할 수 있다.

또한, 본 실시형태는 본 명세서에 기재된 다른 실시형태와 적절히 조합할 수 있다.

(실시형태 2)

본 실시형태에서는 실시형태 1에서 설명한 트랜지스터와 상이한 구조를 갖는 트랜지스터에 대하여 설명한다.

도 4는 본 발명의 일 형태에 따른 트랜지스터(250)의 상면도 및 단면도다. 도 4의 (A)는 상면도이고, 도 4의 (A) 중 일점 쇄선 A1-A2를 따라 자른 단면도가 도 4의 (B)에 상당한다. 또한, 도 4의 (C)는 도 4의 (B)에 도시된 파선 동그라미표로 둘러싼 영역을 확대한 도면이다. 또한, 도 4의 (A)에 도시된 상면도에서는 도면을 명료화하기 위하여 요소를 일부 생략하여 도시하였다.

도 4에 도시된 트랜지스터(250)는 기판(100) 위의 하지 절연막(102)과, 하지 절연막(102) 위의 산화물막(204a)과, 산화물막(204a) 위의 산화물 반도체막(204b)과, 산화물 반도체막(204b) 위의 산화물막(204c)과, 산화물막(204c)에 접하는 소스 전극(106a) 및 드레인 전극(106b)과, 산화물막(204c), 소스 전극(106a), 및 드레인 전극(106b) 위의 게이트 절연막(108)과, 게이트 절연막(108) 위의 게이트 전극(110)을 갖는다. 또한, 게이트 절연막(108) 및 게이트 전극(110) 위에 절연막(112)이 제공되어도 좋다. 절연막(112)은 필요에 따라 제공하면 좋고, 이 상부에 상이한 절연막을 더 제공하여도 좋다.

또한, 산화물막(204a), 산화물 반도체막(204b), 및 산화물막(204c)에 사용하는 재료에 따라서는 산화물막(204a) 및 산화물 반도체막(204b)의 경계, 및 산화물 반도체막(204b) 및 산화물막(204c)의 경계를 명확히 확인할 수 없는 경우가 있다. 그래서 도면에서 산화물막(204a), 산화물 반도체막(204b), 및 산화물막(204c)의 경계는 파선으로 나타내었다.

실시형태 1에 기재된 트랜지스터(150)와 도 4에 도시된 트랜지스터(250)의 차이는 산화물 반도체막 위아래에 산화물막을 갖는지 여부다. 그 외의 구성에 대해서는 실시형태 1을 참조할 수 있다.

산화물막(204a), 산화물 반도체막(204b), 및 산화물막(204c)은 In 및 Ga 중 한쪽 또는 양쪽을 포함한다. 대표적으로는 In-Ga 산화물(In과 Ga을 포함하는 산화물), In-Zn 산화물(In과 Zn을 포함하는 산화물), 및 In-M-Zn 산화물(In과, 원소 M과, Zn을 포함하는 산화물, 원소 M은 Al, Ti, Ga, Y, Zr, La, Ce, Nd, 또는 Hf으로부터 선택된 1종류 이상의 원소)이 있다.

산화물막(204a) 및 산화물막(204c)은 산화물 반도체막(204b)을 구성하는 금속 원소 중 같은 금속 원소를 1종류 이상 포함하는 재료를 사용함으로써 형성되는 것이 바람직하다. 이와 같은 재료를 사용함으로써 산화물 반도체막(204b)과, 산화물막(204a) 및 산화물막(204c)의 계면에 계면 준위가 생기기 어렵게 할 수 있다. 따라서, 계면에서의 캐리어의 산란이나 포획이 발생되기 어렵고 트랜지스터의 전계 효과 이동도를 향상시킬 수 있다. 또한, 트랜지스터의 문턱 전압의 편차를 저감시킬 수 있다. 또한, 산화물막(204a), 산화물 반도체막(204b), 및 산화물막(204c)을 합쳐서 다층막이라고 하는 경우가 있다.

또한, 산화물막(204a) 및 산화물막(204c)은 전도대 하단의 에너지가 산화물 반도체막(204b)보다 0.05eV, 0.07eV, 0.1eV, 0.15eV 중 어느 하나 이상이며, 2eV, 1eV, 0.5eV, 0.4eV 중 어느 하나 이하의 범위에서 진공 준위에 가까운 산화물 반도체로 형성하는 것이 바람직하다.

이와 같은 구조에서, 게이트 전극(110)에 전계를 인가하면, 다층막 중 전도대 하단의 에너지가 가장 작은 산화물 반도체막(204b)에 채널이 형성된다. 즉, 산화물 반도체막(204b)과 게이트 절연막(108) 사이에 산화물막(204c)이 형성됨으로써, 트랜지스터의 채널을 게이트 절연막과 접하지 않는 구조로 할 수 있다.

또한, 산화물막(204a), 산화물 반도체막(204b), 및 산화물막(204c)에 사용하는 재료에 따라서는 산화물막(204a) 및 산화물 반도체막(204b)의 경계, 및 산화물 반도체막(204b) 및 산화물막(204c)의 경계를 명확히 확인할 수 없는 경우가 있다. 그래서 도면에서는 산화물 반도체막(204b)을 산화물막(204a) 및 산화물막(204c)과 상이한 해칭으로 도시하였다.

산화물막(204a)의 두께는 3nm 이상 50nm 이하, 바람직하게는 3nm 이상 20nm 이하로 한다. 산화물 반도체막(204b)의 두께는 3nm 이상 200nm 이하, 바람직하게는 3nm 이상 100nm 이하, 더 바람직하게는 3nm 이상 50nm 이하로 한다. 산화물막(204c)의 두께는 3nm 이상 100nm 이하, 바람직하게는 3nm 이상 50nm 이하로 한다.

또한, 산화물 반도체막(204b) 및 산화물막(204a) 양쪽이 In-M-Zn 산화물일 때 산화물막(204a)을 In:M:Zn=x1:y1:z1[원자수비], 산화물 반도체막(204b)을 In:M:Zn=x2:y2:z2[원자수비]로 하면 y1/x1이 y2/x2보다 크게 되는 산화물 반도체막(204b) 및 산화물막(204a)을 선택한다. 또한, 원소 M은 In보다 산소와의 결합력이 강한 금속 원소이고, 예를 들어, Al, Ti, Ga, Y, Zr, Sn, La, Ce, Nd, 또는 Hf 등을 들 수 있다. 바람직하게는 y1/x1이 y2/x2보다 1.5배 이상 크게 되는 산화물 반도체막(204b) 및 산화물막(204a)을 선택한다. 더 바람직하게는 y1/x1이 y2/x2보다 2배 이상 크게 되는 산화물 반도체막(204b) 및 산화물막(204a)을 선택한다. 더욱 바람직하게는 y1/x1이 y2/x2보다 3배 이상 크게 되는 산화물 반도체막(204b) 및 산화물막(204a)을 선택한다. 이 때 산화물 반도체막(204b)에서 y1이 x1 이상이라면, 트랜지스터에 안정된 전기 특성을 부여할 수 있어 바람직하다. 다만, y1이 x1의 3배 이상이 되면 트랜지스터의 전계 효과 이동도가 저하되기 때문에 y1은 x1의 3배 미만인 것이 바람직하다. 산화물막(204a)을 상술한 구성으로 함으로써, 산화물막(204a)을 산화물 반도체막(204b)보다 산소 결손이 생기기 어려운 막으로 할 수 있다.

또한, 산화물 반도체막(204b)이 In-M-Zn 산화물일 때, Zn 및 O를 제외하였을 때의 In과 M의 원자수비는 바람직하게는 In이 25atomic% 이상이고, M이 75atomic% 미만, 더 바람직하게는 In이 34atomic% 이상이고, M이 66atomic% 미만으로 한다. 또한, 산화물막(204a)이 In-M-Zn 산화물일 때, Zn 및 O를 제외하였을 때의 In과 M의 원자수비는 바람직하게는 In이 50atomic% 미만이고, M이 50atomic% 이상, 더 바람직하게는 In이 25atomic% 미만이고 M이 75atomic% 이상으로 한다.

예를 들어, 산화물 반도체막(204b)으로서 In:Ga:Zn=1:1:1 또는 3:1:2의 원자수비를 갖는 In-Ga-Zn 산화물을 사용할 수 있고, 산화물막(204a)으로서 In:Ga:Zn=1:3:4, 1:3:2, 1:6:2, 1:6:4, 1:6:10 , 1:9:6, 또는 1:9:0의 원자수비를 갖는 In-Ga-Zn 산화물을 사용할 수 있다. 또한, 산화물 반도체막(204b) 및 산화물막(204a)의 원자수비는 각각 오차로서 상술한 원자수비의 플러스마이너스 20%의 변동을 포함한다.

또한, 산화물 반도체막(204b) 및 산화물막(204c) 양쪽이 In-M-Zn 산화물일 때 산화물막(204c)을 In:M:Zn=x1:y1:z1[원자수비], 산화물 반도체막(204b)을 In:M:Zn=x2:y2:z2[원자수비]로 하면 y1/x1이 y2/x2보다 크게 되는 산화물 반도체막(204b) 및 산화물막(204c)을 선택한다. 또한, 원소 M은 In보다 산소와의 결합력이 강한 금속 원소이고, 예를 들어, Al, Ti, Ga, Y, Zr, Sn, La, Ce, Nd, 또는 Hf 등을 들 수 있다. 바람직하게는 y1/x1이 y2/x2보다 1.5배 이상 크게 되는 산화물 반도체막(204b) 및 산화물막(204c)을 선택한다. 더 바람직하게는 y1/x1이 y2/x2보다 2배 이상 크게 되는 산화물 반도체막(204b) 및 산화물막(204c)을 선택한다. 더욱 바람직하게는 y1/x1이 y2/x2보다 3배 이상 크게 되는 산화물 반도체막(204b) 및 산화물막(204c)을 선택한다. 이 때 산화물 반도체막(204b)에서 y1이 x1 이상이라면, 트랜지스터에 안정된 전기 특성을 부여할 수 있어 바람직하다. 다만, y1이 x1의 3배 이상이 되면 트랜지스터의 전계 효과 이동도가 저하되기 때문에 y1은 x1의 3배 미만인 것이 바람직하다. 산화물막(204c)을 상술한 구성으로 함으로써, 산화물막(204c)을 산화물 반도체막(204b)보다 산소 결손이 생기기 어려운 막으로 할 수 있다.

또한, 산화물 반도체막(204b)이 In-M-Zn 산화물일 때, Zn 및 O를 제외하였을 때의 In과 M의 원자수비는 바람직하게는 In이 25atomic% 이상이고, M이 75atomic% 미만, 더 바람직하게는 In이 34atomic% 이상이고, M이 66atomic% 미만으로 한다. 또한, 산화물막(204c)이 In-M-Zn 산화물일 때, Zn 및 O를 제외하였을 때의 In과 M의 원자수비는 바람직하게는 In이 50atomic% 미만이고, M이 50atomic% 이상, 더 바람직하게는 In이 25atomic% 미만이고, M이 75atomic% 이상으로 한다.

예를 들어, 산화물 반도체막(204b)으로서 In:Ga:Zn=1:1:1 또는 3:1:2의 원자수비를 갖는 In-Ga-Zn 산화물을 사용할 수 있고, 산화물막(204c)으로서 In:Ga:Zn=1:3:4, 1:3:2, 1:6:2, 1:6:4, 1:6:10 , 1:9:6, 또는 1:9:0의 원자수비를 갖는 In-Ga-Zn 산화물을 사용할 수 있다. 또한, 산화물 반도체막(204b) 및 산화물막(204c)의 원자수비는 각각 오차로서 상술한 원자수비의 플러스마이너스 20%의 변동을 포함한다.

다층막을 사용한 트랜지스터에 안정된 전기 특성을 부여하기 위해서는 산화물 반도체막(204b) 중의 산소 결손 및 불순물 농도를 저감하여 산화물 반도체막(204b)을 진성 또는 실질적으로 진성으로 간주할 수 있는 반도체막으로 하는 것이 바람직하다. 특히, 산화물 반도체막(204b) 중의 채널 형성 영역을 진성 또는 실질적으로 진성으로 간주할 수 있는 것이 바람직하다. 구체적으로는 산화물 반도체막(204b)의 캐리어 밀도를 1×1017/cm3 미만, 1×1015/cm3 미만, 또는 1×1013/cm3 미만으로 한다.

또한, 산화물 반도체막(204b)에서, 수소, 질소, 탄소, 실리콘, 및 주성분 외의 금속 원소는 불순물이다. 산화물 반도체막(204b) 중의 불순물 농도를 저감하기 위해서는 근접하는 산화물막(204a) 및 산화물막(204c) 중의 불순물 농도도 산화물 반도체막(204b)과 같은 정도까지 저감하는 것이 바람직하다.

특히, 산화물 반도체막(204b)에 실리콘이 높은 농도로 포함됨으로써 실리콘에 기인한 불순물 준위가 산화물 반도체막(204b)에 형성된다. 이 불순물 준위는 트랩 준위가 되어 트랜지스터의 전기 특성을 열화시킬 수 있다. 트랜지스터의 전기 특성의 열화를 줄이기 위해서는 산화물 반도체막(204b) 중의 실리콘 농도를 1×1019atoms/cm3 미만, 바람직하게는 5×1018atoms/cm3 미만, 더 바람직하게는 1×1018atoms/cm3 미만으로 하면 좋다. 또한, 산화물 반도체막(204b)과, 산화물막(204a) 및 산화물막(204c)과의 계면의 실리콘 농도도 상기 실리콘 농도의 범위와 마찬가지로 한다.

또한, 트랜지스터의 게이트 절연막으로서는 실리콘을 포함하는 절연막이 많이 사용되기 때문에 상술한 이유로 산화물 반도체막의 채널이 되는 영역은 절연막과 접하지 않는 것이 바람직하다. 또한, 게이트 절연막과 산화물 반도체막의 계면에 채널이 형성되는 경우, 상기 계면에서 캐리어의 산란이 일어나서 트랜지스터의 전계 효과 이동도가 낮게 되는 것이 있다. 이와 같은 관점에서 봐도 산화물 반도체막의 채널이 되는 영역은 게이트 절연막으로부터 떨어뜨리게 하는 것이 바람직하다.

따라서, 다층막을 산화물막(204a), 산화물 반도체막(204b), 및 산화물막(204c)의 적층 구조로 함으로써 트랜지스터의 채널이 형성되는 산화물 반도체막(204b)을 게이트 절연막으로부터 떨어뜨릴 수 있어 높은 전계 효과 이동도를 갖고 안정된 전기 특성을 갖는 트랜지스터를 형성할 수 있다.

또한, 산화물 반도체막(204b) 중에서 수소 및 질소는 도너 준위를 형성하고 캐리어 밀도를 증대시킨다. 산화물 반도체막(204b)을 진성 또는 실질적으로 진성으로 하기 위해서는, SIMS에 의하여 측정하였을 때의 산화물 반도체막(204b) 중의 수소 농도는 2×1020atoms/cm3 이하, 바람직하게는 5×1019atoms/cm3 이하, 더 바람직하게는 1×1019atoms/cm3 이하, 더욱 바람직하게는 5×1018atoms/cm3 이하로 한다. 또한, SIMS에 의하여 측정하였을 때의 산화물 반도체막(204b) 중의 질소 농도는 5×1019atoms/cm3 미만, 바람직하게는 5×1018atoms/cm3 이하, 더 바람직하게는 1×1018atoms/cm3 이하, 더욱 바람직하게는 5×1017atoms/cm3 이하로 한다.

또한 산화물 반도체막(204b)에 실리콘 및 탄소가 높은 농도로 포함됨으로써 산화물 반도체막(204b)의 결정성을 저하시킬 수 있다. 산화물 반도체막(204b)의 결정성을 저하시키지 않기 위해서는 산화물 반도체막(204b) 중의 실리콘 농도를 1×1019atoms/cm3 미만, 바람직하게는 5×1018atoms/cm3 미만, 더 바람직하게는 1×1018atoms/cm3 미만으로 하면 좋다. 또한, 산화물 반도체막(204b)의 결정성을 저하시키지 않기 위해서는 산화물 반도체막(204b) 중의 탄소 농도를 1×1019atoms/cm3 미만, 바람직하게는 5×1018atoms/cm3 미만, 더 바람직하게는 1×1018atoms/cm3 미만으로 하면 좋다.

또한, 산화물 반도체의 밴드 갭은 2eV 이상이므로, 산화물 반도체를 사용한 트랜지스터는, 트랜지스터가 오프 상태일 때의 누설 전류(오프 전류라고도 함)를 매우 작게 할 수 있다.

이하에서는 다층막 중의 국재 준위(局在 準位)에 대하여 설명한다. 다층막 중의 국재 준위 밀도를 저감시킴으로써 다층막을 사용한 트랜지스터에 안정된 전기 특성을 부여할 수 있다. 다층막 중의 국재 준위 밀도는 일정 광전류 측정법(CPM: Constant Photocurrent Method)에 의하여 평가 가능하다.

트랜지스터에 안정된 전기 특성을 부여하기 위해서는 CPM 측정으로 얻어지는 다층막 중의 국재 준위에 의한 흡수 계수를 1×10-3cm-1 미만, 바람직하게는 3×10-4cm-1 미만으로 하면 좋다. 또한, CPM 측정으로 얻어지는 다층막 중의 국재 준위에 의한 흡수 계수를 1×10-3cm-1 미만, 바람직하게는 3×10-4cm-1 미만으로 함으로써 트랜지스터의 전계 효과 이동도를 높일 수 있다. 또한, CPM 측정으로 얻어지는 다층막 중의 국재 준위에 의한 흡수 계수를 1×10-3cm-1 미만, 바람직하게는 3×10-4cm-1 미만으로 하기 위해서는 산화물 반도체막(204b) 중에서 국재 준위를 형성하는 원소인 실리콘, 게르마늄, 탄소 등의 농도를 2×1018atoms/cm3 미만, 바람직하게는 2×1017atoms/cm3 미만으로 하면 좋다.

또한, CPM 측정에서는, 시료인 다층막에 접하도록 제공된 전극 사이에 전압을 인가한 상태에서 단자 사이의 시료면에 조사하는 광량을 광전류값이 일정하게 되도록 조정하고, 조사 광량에 의하여 흡수 계수를 도출하는 것을 각 파장에서 수행하는 측정이다. CPM 측정에서, 시료에 결함이 있을 때 결함이 존재하는 준위에 따른 에너지(파장으로 환산)에서의 흡수 계수가 증가된다. 이 흡수 계수의 증가분에 상수를 곱함으로써 시료의 결함 밀도를 도출할 수 있다.

CPM 측정으로 얻어진 국재 준위는 불순물이나 결함에 기인하는 준위라고 생각된다. 즉, CPM 측정으로 얻어지는 국재 준위에 의한 흡수 계수가 작은 다층막을 사용함으로써 트랜지스터에 안정된 전기 특성을 부여할 수 있다.

다음에 트랜지스터(250)의 제작 방법에 대하여 도 5 및 도 6을 사용하여 설명한다.

먼저, 기판(100)을 준비한다. 다음에, 하지 절연막(102)을 형성한다. 그 후, 하지 절연막(102) 위에 산화물막(203a), 산화물 반도체막(203b), 및 산화물막(203c)을 순차적으로 형성한다(도 5의 (A) 참조).

기판(100) 및 하지 절연막(102)의 재료 및 제작 방법은 실시형태 1을 참조할 수 있다. 산화물막(203a), 산화물 반도체막(203b), 및 산화물막(203c)의 재료는 상술한 재료를 사용할 수 있고, 산화물막(203a), 산화물 반도체막(203b), 및 산화물막(203c)의 제작 방법은 실시형태 1에 기재된 산화물 반도체막(103)을 참조하면 좋다.

다음에 제 1 가열 처리를 수행하는 것이 바람직하다. 제 1 가열 처리는 250℃ 이상 650℃ 이하, 바람직하게는 300℃ 이상 500℃ 이하로 수행하면 좋다. 제 1 가열 처리의 분위기는 불활성 가스 분위기, 산화성 가스를 10ppm 이상, 바람직하게는 1% 이상, 더 바람직하게는 10% 이상 포함하는 분위기, 또는 감압 상태에서 수행한다. 또는 제 1 가열 처리의 분위기는 불활성 가스 분위기에서 가열 처리한 후에 이탈된 산소를 보전하기 위하여 산화성 가스를 10ppm 이상, 바람직하게는 1% 이상, 더 바람직하게는 10% 이상 포함하는 분위기에서 가열 처리를 수행하여도 좋다. 제 1 가열 처리를 수행함으로써 다층막의 결정성을 높이면서, 나중에 형성되는 게이트 절연막 및 다층막으로부터 물, 수소, 질소, 및 탄소 등의 불순물을 제거할 수 있다.

다음에 산화물막(203c) 위에 하드 마스크(120), 하드 마스크(120) 위에 유기 도포막(122)을 형성하고, 유기 도포막(122) 위에 레지스트를 형성하고, 상기 레지스트에 대하여 전자 빔을 사용한 노광을 수행하여 레지스트 마스크(124)를 형성한다(도 5의 (B) 참조).

또한, 노광에는 ArF 엑시머 레이저를 광원으로 하는 액침 노광이나 EUV 노광을 사용하여도 좋다.

하드 마스크(120), 유기 도포막(122), 및 레지스트 마스크(124)의 재료 및 제작 방법은 실시형태 1을 참조할 수 있다.

다음에 레지스트 마스크(124)를 마스크로 하여 유기 도포막(122) 및 하드 마스크(120)를 선택적으로 에칭함으로써 유기 도포막(123) 및 하드 마스크(121)를 형성한다(도 5의 (C) 참조). 에칭 조건 등은 실시형태 1을 참조할 수 있다.

다음에 레지스트 마스크(124) 및 하드 마스크(121)를 마스크로 하여 산화물막(203a), 산화물 반도체막(203b), 및 산화물막(203c)을 선택적으로 에칭함으로써 산화물막(204a), 산화물 반도체막(204b), 및 산화물막(204c)을 형성한다(도 5의 (D) 참조).

다음에, 산화물막(204c) 위의 하드 마스크(121), 유기 도포막(123), 및 레지스트 마스크(124)를 제거한다(도 6의 (A) 참조). 제거 처리에 특별히 한정은 없고 예를 들어, 에칭이나 산소 플라즈마에 의한 애싱 등을 수행하면 좋다.

또한, 산화물막(203a), 산화물 반도체막(203b), 및 산화물막(203c)을 에칭하기 전에 유기 도포막(123) 및 레지스트 마스크(124)를 산소 플라즈마를 사용한 애싱으로 제거하고, 그 후, 산화물막(203a), 산화물 반도체막(203b), 및 산화물막(203c)을 에칭하여 산화물막(204a), 산화물 반도체막(204b), 및 산화물막(204c)을 형성하고 나서 하드 마스크(121)를 제거하여도 좋다.

다음에 하지 절연막(102) 및 산화물막(204c) 위에 소스 전극(106a) 및 드레인 전극(106b)이 되는 도전막을 형성하고, 도전막의 일부를 가공하여 소스 전극(106a) 및 드레인 전극(106b)을 형성한다(도 6의 (B) 참조). 이 때, 소스 전극(106a) 및 드레인 전극(106b)의 단부는 도시된 바와 같이, 계단 형상으로 형성한다. 상기 단부의 가공은 애싱에 의하여 레지스트 마스크를 축소시키는 공정과 에칭 공정을 교대로 여러 번 수행함으로써 형성할 수 있다.

또한, 소스 전극(106a) 및 드레인 전극(106b)이 되는 도전막의 재료는 다층막을 구성하는 금속 원소보다 산소와 결합하기 쉬운 도전 재료를 사용한다. 이 때, 도전막의 재료가 산소와 결합하기 쉬운 도전 재료이기 때문에 다층막 중의 산소가 도전 재료(도전막)와 결합한다. 이 결합에 의하여 다층막 중 도전막과의 계면 근방의 영역에 산소 결손이 생긴다. 또는, 다층막 위에 형성되는 도전막을 형성할 때, 다층막 상면에 대한 대미지(산소 결손)가 생긴다. 이들 산소 결손에 의하여 저저항 영역(105)이 형성된다. 또한 본 실시형태에서는 저저항 영역(105)과 다층막의 경계는 산화물막(204c) 중에 존재하지만 이것에 한정되지 않고 상기 경계는 산화물막(204a) 중, 산화물 반도체막(204b) 중, 산화물막(204a)과 산화물 반도체막(204b)의 계면, 또는 산화물 반도체막(204b)과 산화물막(204c)의 계면에 존재하여도 좋다. 또한, 저저항 영역(105)은 다층막과 도전막의 계면으로부터 다층막의 깊이 방향으로 0nm 보다 크고 15nm 이하, 바람직하게는 10nm 미만, 더 바람직하게는 3nm 미만의 영역에 있다.

저저항 영역(105)이 형성됨으로써 나중에 형성되는 소스 전극 또는 드레인 전극과 다층막과의 접촉 저항을 저감할 수 있어 트랜지스터(250)의 고속 동작을 구현할 수 있다.

또한, 상술한 애싱에 의하여 레지스트 마스크를 축소시키는 공정과 에칭 공정을 교대로 여러 번 수행함으로써, 소스 전극(106a) 및 드레인 전극(106b)의 단부는 나중에 형성되는 저저항 영역(105a) 및 저저항 영역(105b) 위에 제공된다.

이로써, 저저항 영역(105a)과 저저항 영역(105b) 사이의 다층막의 영역(A)을 포함하는, 저저항 영역(105) 중 소스 전극(106a) 및 드레인 전극(106b)과 접하지 않는 영역(B)이 트랜지스터(250)의 채널 형성 영역이 된다. 트랜지스터(250)의 채널 형성 영역은 n형화되기 때문에 다층막 중의 불순물 농도를 저감하여 고순도 진성화할 필요가 있다.

다음에 게이트 절연막(108)을 형성한다(도 6의 (C) 참조). 게이트 절연막(108)의 재료 및 제작 방법은 실시형태 1을 참조할 수 있다.

다음에 다층막의 채널 형성 영역에 대하여 산소를 첨가하여 저저항 영역(105a) 및 저저항 영역(105b)을 형성한다.

다층막의 영역(B)에 산소를 첨가하는 방법으로서는 실시형태 1을 참조할 수 있다.

다음에, 제 2 가열 처리를 수행하는 것이 바람직하다. 제 2 가열 처리는 제 1 가열 처리와 마찬가지의 조건에서 수행할 수 있다. 제 2 가열 처리에 의하여 다층막으로부터 수소나 물 등의 불순물을 더 제거할 수 있다.

다음에 게이트 절연막(108) 위에 게이트 전극(110)이 되는 도전막을 형성하고, 도전막의 일부를 가공함으로써 게이트 전극(110)을 형성한다. 게이트 전극(110)의 재료 및 제작 방법은 실시형태 1을 참조할 수 있다.

다음에 소스 전극(106a), 드레인 전극(106b), 및 게이트 전극(110) 위에 절연막(112)을 형성한다(도 6의 (D) 참조). 절연막(112)의 재료 및 제작 방법은 실시형태 1을 참조할 수 있다.

다음에, 제 3 가열 처리를 수행하는 것이 바람직하다. 제 3 가열 처리는 제 1 가열 처리와 마찬가지의 조건에서 수행할 수 있다. 산소가 과잉으로 포함되는 하지 절연막(102)이나 절연막(112)의 경우, 제 3 가열 처리를 수행함으로써 하지 절연막(102)이나 절연막(112)으로부터 과잉 산소가 방출되기 쉬워져 다층막, 특히, 산화물 반도체막(204b)의 산소 결손을 저감할 수 있다. 따라서 다층막 중의 채널 형성 영역은 산소 결손량이 더욱 저감되어 고순도 진성화된다.

상술한 공정을 거쳐 트랜지스터(250)를 제작할 수 있다.

또한, 트랜지스터의 다른 구성을 도 7에 도시하였다. 도 7에 도시된 트랜지스터(260)는 기판(100) 위의 하지 절연막(102)과, 하지 절연막(102) 위의 산화물막(204a)과, 산화물막(204a) 위의 산화물 반도체막(204b)과, 산화물 반도체막(204b)에 접하는 소스 전극(106a) 및 드레인 전극(106b)과, 소스 전극(106a) 및 드레인 전극(106b) 위의 산화물막(204c)과, 산화물막(204a) 및 산화물 반도체막(204b)으로부터 산소가 추출되어 형성된, 소스 전극(106a)과 접하는 저저항 영역(105a)과, 산화물막(204a) 및 산화물 반도체막(204b)으로부터 산소가 추출되어 형성된, 드레인 전극(106b)과 접하는 저저항 영역(105b)과, 산화물막(204c), 소스 전극(106a), 및 드레인 전극(106b) 위의 게이트 절연막(108)과, 게이트 절연막(108) 위의 게이트 전극(110)을 갖는다. 또한, 게이트 절연막(108) 및 게이트 전극(110) 위에 절연막(112)이 제공되어도 좋다. 절연막(112)은 필요에 따라 제공하면 좋고, 이 상부에 상이한 절연막을 더 제공하여도 좋다.

도 4에 도시된 트랜지스터(250)와, 도 7에 도시된 트랜지스터(260)는 산화물막(204c)이 소스 전극(106a) 및 드레인 전극(106b) 위에 형성되는 점이 상이하지만 이 외의 점은 마찬가지다.

트랜지스터(260)에서는 채널이 형성되는 산화물 반도체막(204b)과 소스 전극(106a) 및 드레인 전극(106b)이 접하기 때문에 산화물 반도체막(204b)에 높은 밀도로 산소 결손이 생성되어 n형화 영역(저저항 영역(105a) 및 저저항 영역(105b))이 형성된다. 따라서 캐리어의 전송에 대한 저항 성분이 적기 때문에 효율 좋게 캐리어를 이동할 수 있다.

또한, 본 실시형태에서 채널이란, 소스 전극 및 드레인 전극 사이의 산화물 반도체막을 말한다. 또한, 채널 형성 영역이란, 소스 전극 및 드레인 전극 사이의 산화물막(204a), 산화물 반도체막(204b), 및 산화물막(204c)을 말한다.

또한, 산화물막(204c)은 소스 전극(106a) 및 드레인 전극(106b)을 형성한 후에 형성하기 때문에 상기 소스 전극(106a) 및 드레인 전극(106b)을 형성할 때, 산화물막(204c)이 오버 에칭되지 않는다. 따라서 채널이 형성되는 산화물 반도체막(204b)을 게이트 절연막(108)으로부터 충분히 떨어뜨릴 수 있고 계면으로부터 불순물이 확산되는 것으로 인한 영향을 억제하는 효과를 높게 할 수 있다.

또한, 산화물막(204c)은, 외부로부터 수소 또는 수소를 포함하는 화합물(물 등)이 산화물 반도체막(204b)으로 침입하는 것을 억제하는 배리어막으로서 기능하기 때문에 트랜지스터의 신뢰성을 향상시킬 수 있다.

이와 같은 제작 방법을 사용함으로써 산화물 반도체막을 섬 형상으로 미세 가공할 때에 산화물 반도체막 단부의 요철을 억제할 수 있다. 따라서 미세한 구조라도 높은 전기 특성을 갖는 트랜지스터를 수율 좋게 제공할 수 있다. 또한, 상기 트랜지스터를 포함하는 반도체 장치에서도 고성능화, 고신뢰성화, 및 고생산화를 달성할 수 있다.

또한, 본 실시형태는 본 명세서에 기재된 다른 실시형태와 적절히 조합할 수 있다.

(실시형태 3)

본 실시형태에서는 본 발명의 일 형태에 따른 트랜지스터를 사용하여, 전력이 공급되지 않는 상황에서도 기억 내용을 유지할 수 있고, 기록 횟수에 대해서도 제한이 없는 반도체 장치(기억 장치)의 일례를 도면을 사용하여 설명한다.

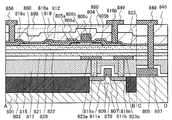

도 8의 (A)는 반도체 장치의 단면도를 도시한 것이고, 도 8의 (B)는 반도체 장치의 회로도를 도시한 것이다.

도 8의 (A) 및 (B)에 도시된 반도체 장치는 제 1 반도체 재료를 사용한 트랜지스터(400)를 하부에 갖고, 제 2 반도체 재료를 사용한 트랜지스터(402) 및 용량 소자(404)를 상부에 갖는다. 또한, 트랜지스터(402)로서는 상술한 실시형태에서 설명한 트랜지스터를 사용할 수 있고, 본 실시형태에서는 실시형태 1에서 제시한 도 1에 도시된 트랜지스터(150)를 적용하는 예에 대하여 설명한다. 또한, 용량 소자(404)의 한쪽 전극에 트랜지스터(402)의 게이트 전극과 같은 재료, 용량 소자(404)의 다른 한쪽 전극에 트랜지스터(402)의 소스 전극 또는 드레인 전극과 같은 재료, 유전체에 트랜지스터(402)의 게이트 절연막(108)과 같은 재료를 사용하는 구조로 함으로써, 트랜지스터(402)와 동시에 용량 소자(404)를 형성할 수 있다.

여기서, 제 1 반도체 재료와 제 2 반도체 재료는 서로 상이한 밴드 갭을 갖는 재료로 하는 것이 바람직하다. 예를 들어, 제 1 반도체 재료를 산화물 반도체 외의 반도체 재료(실리콘 등)로 하고, 제 2 반도체 재료는 실시형태 1에서 설명한 산화물 반도체로 할 수 있다. 산화물 반도체 외의 재료를 사용한 트랜지스터는 고속 동작하기 쉽다. 한편, 산화물 반도체를 사용한 트랜지스터는 오프 전류가 낮다는 전기 특성 때문에 전하를 오랫동안 유지할 수 있게 한다.

또한, 상기 트랜지스터는 모두 n채널형 트랜지스터인 것으로 하여 설명하지만, p채널형 트랜지스터를 사용할 수 있는 것은 말할 나위 없다. 또한, 정보를 유지하기 위하여 산화물 반도체를 사용한 상술한 실시형태에 기재된 바와 같은 트랜지스터가 사용되는 한 반도체 장치에 사용되는 재료나 반도체 장치의 구조 등, 반도체 장치의 구체적인 구성은 여기서 기재된 것으로 한정되지 않는다.

도 8의 (A)에 도시된 트랜지스터(400)는 반도체 재료(예를 들어, 결정성 실리콘 등)를 포함한 기판(410)에 제공된 채널 형성 영역과, 채널 형성 영역을 끼우도록 제공된 불순물 영역과, 불순물 영역과 접하는 금속간 화합물 영역과, 채널 형성 영역 위에 제공된 게이트 절연막과, 게이트 절연막 위에 제공된 게이트 전극을 갖는다. 또한, 도면에는 소스 전극이나 드레인 전극을 명시적으로 도시하지 않은 경우가 있지만, 편의상 이와 같은 형상을 포함하여 트랜지스터라고 부르는 경우가 있다. 또한, 이 경우에는 트랜지스터의 접속 관계를 설명하기 위하여 소스 영역이나 드레인 영역을 포함하여 소스 전극이나 드레인 전극이라고 나타낼 수 있다. 즉, 예를 들어, 본 명세서에서, 소스 전극이라는 기재에는 소스 영역이 포함될 수 있다.

기판(410) 위에는 트랜지스터(400)를 둘러싸도록 소자 분리 절연층(406)이 제공되고, 트랜지스터(400)를 덮도록 절연막(420)이 제공된다. 또한, 소자 분리 절연층(406)은 LOCOS(Local Oxidation of Silicon)나 STI(Shallow Trench Isolation)와 같은 소자 분리 기술을 사용하여 형성할 수 있다.

예를 들어, 결정성 실리콘 기판을 사용한 트랜지스터(400)는 고속 동작이 가능하다. 이로써 상기 트랜지스터를 판독용 트랜지스터로서 사용함으로써 정보의 판독을 고속으로 수행할 수 있다. 트랜지스터(402) 및 용량 소자(404)를 형성하기 전의 처리로서, 트랜지스터(400)를 덮는 절연막(420)에 CMP 처리를 수행하여 절연막(420)을 평탄화함과 동시에 트랜지스터(400)의 게이트 전극의 상면을 노출시킨다.

절연막(420) 위에는 트랜지스터(402)가 제공되고, 그 소스 전극 및 드레인 전극 중 한쪽은 연장되어 용량 소자(404)의 한쪽 전극으로서 작용한다.

도 8의 (A)에 도시된 트랜지스터(402)는 산화물 반도체막에 채널이 형성되는 톱 게이트형 트랜지스터다. 트랜지스터(402)는 오프 전류가 낮으므로, 이를 사용함으로써 기억 내용이 오랫동안 유지될 수 있다. 즉, 리프레시 동작을 수행할 필요가 없게 되거나, 또는 리프레시 동작의 빈도가 매우 적은 반도체 기억 장치로 할 수 있어 소비 전력을 충분히 저감할 수 있다.

또한, 트랜지스터(402)에서 소스 전극 또는 드레인 전극이 접하는 산화물 반도체막 계면 근방의 영역에 저저항 영역이 형성되고, 소스 전극 및 드레인 전극을 마스크로 하여 산소를 산화물 반도체막에 첨가함으로써 채널 형성 영역을 고순도 진성인 영역으로 할 수 있고 자기 정합적으로 고순도 진성인 영역과 저저항 영역을 형성할 수 있다. 상기 트랜지스터는 산화물 반도체막 중의 채널 형성 영역에서의 산소 결손량을 저감할 수 있고, 전기 특성이 양호하기 때문에 신뢰성이 높은 반도체 장치를 제공할 수 있다.

도 8의 (A)에 도시된 바와 같이, 트랜지스터(400)와 트랜지스터(402)는 중첩되도록 형성할 수 있기 때문에 그 점유 면적을 저감할 수 있다. 따라서 반도체 장치의 집적도를 높일 수 있다.

다음에, 도 8의 (A)에 대응하는 회로 구성의 일례를 도 8의 (B)에 도시하였다.

도 8의 (B)에서 제 1 배선(1st Line)과 트랜지스터(400)의 소스 전극은 전기적으로 접속되고, 제 2 배선(2nd Line)과 트랜지스터(400)의 드레인 전극은 전기적으로 접속된다. 또한, 제 3 배선(3rd Line)과 트랜지스터(402)의 소스 전극 및 드레인 전극 중 한쪽은 전기적으로 접속되고, 제 4 배선(4th Line)과 트랜지스터(402)의 게이트 전극은 전기적으로 접속된다. 그리고, 트랜지스터(400)의 게이트 전극과 트랜지스터(402)의 소스 전극 및 드레인 전극 중 한쪽은 용량 소자(404)의 전극 중 한쪽과 전기적으로 접속되고, 제 5 배선(5th Line)과 용량 소자(404)의 전극 중 다른 한쪽은 전기적으로 접속된다.

도 8의 (B)에 도시된 반도체 장치에서는 트랜지스터(400)의 게이트 전극의 전위를 유지할 수 있는 특징을 살림으로써, 다음과 같이 정보의 기록, 유지, 및 판독이 가능하다.

정보의 기록 및 유지에 대하여 설명한다. 먼저, 제 4 배선의 전위를 트랜지스터(402)가 온 상태가 되는 전위로 하여 트랜지스터(402)를 온 상태로 한다. 이로써, 제 3 배선의 전위가 트랜지스터(400)의 게이트 전극 및 용량 소자(404)에 인가된다. 즉, 트랜지스터(400)의 게이트 전극에는 소정의 전하가 인가된다(기록). 여기서는, 상이한 두 가지 전위 레벨을 인가하는 전하(이하 Low 레벨 전하, High 레벨 전하라고 함) 중 어느 하나가 인가되는 것으로 한다. 그 후, 제 4 배선의 전위를 트랜지스터(402)가 오프 상태가 되는 전위로 하여 트랜지스터(402)를 오프 상태로 함으로써 트랜지스터(400)의 게이트 전극에 인가된 전하가 유지된다(유지).

트랜지스터(402)의 오프 전류는 매우 낮기 때문에, 트랜지스터(400)의 게이트 전극의 전하는 오랫동안 유지된다.

다음에, 정보의 판독에 대하여 설명한다. 제 1 배선에 소정의 전위(정전위)를 인가한 상태로 제 5 배선에 적절한 전위(판독 전위)를 인가함으로써, 트랜지스터(400)의 게이트 전극에 유지된 전하량에 따라 제 2 배선의 전위가 변동된다. 일반적으로 트랜지스터(400)를 n채널형 트랜지스터로 하면, 트랜지스터(400)의 게이트 전극에 High 레벨 전하가 인가되는 경우의 외견상 문턱 전압(apparent threshold voltage)(Vth _H)은, 트랜지스터(400)의 게이트 전극에 Low 레벨 전하가 인가되는 경우의 외견상 문턱 전압(Vth _L)보다 낮게 되기 때문이다. 여기서, 외견상 문턱 전압이란, 트랜지스터(400)를 "온 상태"로 하는 데 필요한 제 5 배선의 전위를 말한다. 따라서 제 5 배선의 전위를 Vth _H와 Vth _L 사이의 전위(V0)로 함으로써 트랜지스터(400)의 게이트 전극에 인가된 전하를 판별할 수 있다. 예를 들어, 기록에서 High 레벨 전하가 인가되며 제 5 배선의 전위가 V0(>Vth _H)이 되면 트랜지스터(400)는 "온 상태"가 된다. 또한, 기록에서 Low 레벨 전하가 인가되며 제 5 배선의 전위가 V0(<Vth _L)이 되더라도 트랜지스터(400)는 "오프 상태"인 채다. 이로써 제 2 배선의 전위를 판별함으로써 유지되는 정보를 판독할 수 있다.

또한, 메모리 셀을 어레이 형상으로 배치하여 사용하는 경우에는 원하는 메모리 셀의 정보만을 판독할 수 있어야 한다. 이와 같이, 정보를 판독하지 않는 경우에는, 게이트 전극의 상태에 상관없이 트랜지스터(400)가 "오프 상태"가 되는 전위, 즉, Vth _H보다 작은 전위를 제 5 배선에 인가하면 좋다. 또는, 게이트 전극의 상태에 상관없이 트랜지스터(400)가 "온 상태"가 되는 전위, 즉, Vth _L보다 큰 전위를 제 5 배선에 인가하면 좋다.

본 실시형태에 기재된 반도체 장치에서는 채널 형성 영역에 산화물 반도체를 사용한, 오프 전류가 매우 낮은 트랜지스터를 적용함으로써, 기억 내용을 매우 오랫동안 유지할 수 있다. 즉, 리프레시 동작을 수행할 필요가 없게 되거나, 또는 리프레시 동작의 빈도를 매우 적게 할 수 있기 때문에, 소비 전력을 충분히 저감할 수 있다. 또한, 전력이 공급되지 않는 경우(다만, 전위는 고정되어 있는 것이 바람직함)에도 기억 내용을 오랫동안 유지할 수 있다.

또한, 본 실시형태에 기재된 반도체 장치에서는, 정보를 기록하는 데 높은 전압을 필요하지 않고, 소자가 열화되는 문제도 없다. 예를 들어, 종래의 비휘발성 메모리와 같이, 플로팅 게이트로 전자를 주입하거나, 플로팅 게이트로부터 전자를 추출할 필요가 없기 때문에, 게이트 절연막의 열화 등의 문제가 전혀 생기지 않는다. 즉, 기재된 발명에 따른 반도체 장치에서는 종래의 비휘발성 메모리에서 문제가 되는 재기록 가능 횟수에 대한 제한이 없고, 신뢰성이 비약적으로 향상된다. 또한, 트랜지스터의 온 상태, 오프 상태에 따라 정보가 기록되기 때문에, 고속 동작을 쉽게 구현할 수도 있다.

상술한 바와 같이, 미세화 및 고집적화를 구현하고, 높은 전기적 특성을 갖는 반도체 장치 및 상기 반도체 장치의 제작 방법을 제공할 수 있다.

또한, 본 실시형태는 본 명세서에 기재된 다른 실시형태와 적절히 조합할 수 있다.

(실시형태 4)

본 실시형태에서는 본 발명의 일 형태에 따른 트랜지스터를 사용하여, 전력이 공급되지 않는 상황에서도 기억 내용을 유지할 수 있고 기록 횟수에도 제한이 없는, 실시형태 3에 기재된 구성과 다른 구성을 갖는 반도체 장치에 대하여 설명한다.

도 9의 (A)는 반도체 장치의 회로 구성의 일례를 도시한 것이고, 도 9의 (B)는 반도체 장치의 일례를 도시한 개념도다. 또한, 상기 반도체 장치에 포함되는 트랜지스터(562)로서는 상술한 실시형태에서 설명한 트랜지스터를 사용할 수 있다. 또한, 용량 소자(554)는 실시형태 3에서 설명한 용량 소자(404)와 마찬가지로, 트랜지스터(562)의 제작 공정에서 동시에 제작할 수 있다.

도 9의 (A)에 도시된 반도체 장치에서 비트 라인(BL)과 트랜지스터(562)의 소스 전극은 전기적으로 접속되고, 워드 라인(WL)과 트랜지스터(562)의 게이트 전극은 전기적으로 접속되고, 트랜지스터(562)의 드레인 전극과 용량 소자(554)의 한쪽 단자는 전기적으로 접속된다.

다음에, 도 9의 (A)에 도시된 반도체 장치(메모리 셀(550))에 정보의 기록 및 유지를 수행하는 경우에 대하여 설명한다.

먼저, 워드 라인(WL)의 전위를 트랜지스터(562)가 온 상태가 되는 전위로 하여, 트랜지스터(562)를 온 상태로 한다. 이로써 비트 라인(BL)의 전위가 용량 소자(554)의 한쪽 단자에 인가된다(기록). 그 후, 워드 라인(WL)의 전위를 트랜지스터(562)가 오프 상태가 되는 전위로 하여, 트랜지스터(562)를 오프 상태로 함으로써 용량 소자(554)의 한쪽 단자의 전위가 유지된다(유지).

산화물 반도체를 사용한 트랜지스터(562)는 오프 전류가 매우 낮다는 특징을 갖는다. 이로써 트랜지스터(562)를 오프 상태로 함으로써 용량 소자(554)의 제 1 단자의 전위(또는 용량 소자(554)에 축적된 전하)를 매우 오랫동안 유지할 수 있다.

다음에, 정보의 판독에 대하여 설명한다. 트랜지스터(562)가 온 상태가 되면 용량 소자(554)와 부유 상태인 비트 라인(BL)이 도통하고, 비트 라인(BL)과 용량 소자(554) 사이에서 전하가 다시 분배된다. 이 결과, 비트 라인(BL)의 전위가 변화한다. 비트 라인(BL)의 전위의 변화량은 용량 소자(554)의 제 1 단자의 전위(또는 용량 소자(554)에 축적된 전하)에 따라 상이한 값이 된다.

예를 들어, 용량 소자(554)의 제 1 단자의 전위를 V, 용량 소자(554)의 용량을 C, 비트 라인(BL)이 갖는 용량 성분(이하, 비트 라인 용량이라고도 함)을 CB, 전하가 다시 분배되기 전의 비트 라인(BL)의 전위를 VB0으로 하면, 전하가 다시 분배된 후의 비트 라인(BL)의 전위는 (CB×VB0+C×V)/(CB+C)가 된다. 따라서, 메모리 셀(550)의 상태로서 용량 소자(554)의 제 1 단자의 전위가 V1 및 V0(V1>V0)의 두 가지 상태가 된다고 하면, 전위(V1)를 유지하는 경우의 비트 라인(BL)의 전위(=(CB×VB0+C×V1)/(CB+C))는, 전위(V0)를 유지하는 경우의 비트 라인(BL)의 전위(=(CB×VB0+C×V0)/(CB+C))보다 높게 되는 것을 알 수 있다.

그리고, 비트 라인(BL)의 전위를 소정의 전위와 비교함으로써 정보를 판독할 수 있다.

이와 같이, 도 9의 (A)에 도시된 반도체 장치는 트랜지스터(562)의 오프 전류가 매우 낮다는 특징을 갖기 때문에, 용량 소자(554)에 축적된 전하는 오랫동안 유지될 수 있다. 즉, 리프레시 동작을 수행할 필요가 없게 되거나, 또는 리프레시 동작의 빈도를 매우 적게 할 수 있기 때문에, 소비 전력을 충분히 저감할 수 있다. 또한, 전력이 공급되지 않는 경우에도 기억 내용을 오랫동안 유지할 수 있다.

다음에, 도 9의 (B)에 도시된 반도체 장치에 대하여 설명한다.

도 9의 (B)에 도시된 반도체 장치는, 도 9의 (A)에서 기억 회로로서 도시한 메모리 셀(550)을 복수로 갖는 메모리 셀 어레이(551)(메모리 셀 어레이(551a) 및 메모리 셀 어레이(551b))를 상부에 갖고, 메모리 셀 어레이(551)를 동작시키기 위하여 필요한 주변 회로(553)를 하부에 갖는다. 또한, 주변 회로(553)는 메모리 셀 어레이(551)와 전기적으로 접속된다.

주변 회로(553)에 제공되는 트랜지스터는 트랜지스터(562)와 상이한 반도체 재료를 사용하는 것이 바람직하다. 예를 들어, 실리콘, 게르마늄, 실리콘 게르마늄, 탄화 실리콘, 또는 갈륨 비소 등을 사용할 수 있고, 단결정 반도체를 사용하는 것이 더 바람직하다. 이와 같은 반도체 재료를 사용한 트랜지스터는 충분한 고속 동작이 가능하다. 따라서, 상기 트랜지스터에 의하여, 고속 동작이 요구되는 각종 회로(논리 회로, 구동 회로 등)를 바람직하게 구현할 수 있다.

또한, 도 9의 (B)에 도시된 반도체 장치는 메모리 셀 어레이(551)가 메모리 셀 어레이(551a)와 메모리 셀 어레이(551b)의 적층 구성인 경우를 예시하였지만, 적층되는 메모리 셀 어레이의 개수는 이것에 한정되지 않는다. 3개 이상의 메모리 셀 어레이가 적층된 구성이라도 좋고, 단층이라도 좋다.

트랜지스터(562)는 산화물 반도체를 사용하여 형성되고, 상술한 실시형태에서 설명한 트랜지스터를 사용할 수 있다. 산화물 반도체를 사용한 트랜지스터는 오프 전류가 낮기 때문에 기억 내용이 오랫동안 유지될 수 있다. 즉, 리프레시 동작의 빈도를 매우 적게 할 수 있기 때문에 소비 전력을 충분히 저감할 수 있다.

또한, 산화물 반도체 외의 재료를 사용한 트랜지스터(바꿔 말하면, 충분한 고속 동작이 가능한 트랜지스터)를 사용한 주변 회로와, 산화물 반도체를 사용한 트랜지스터(더 넓은 의미로는 오프 전류가 충분히 낮은 트랜지스터)를 사용한 기억 회로를 일체로 구비함으로써 여태까지 없었던 특징을 갖는 반도체 장치를 구현할 수 있다. 또한, 주변 회로와 기억 회로를 적층 구조로 함으로써 반도체 장치의 집적화를 도모할 수 있다.

상술한 바와 같이, 미세화 및 고집적화를 구현하고, 높은 전기적 특성을 갖는 반도체 장치를 제공할 수 있다.

또한, 본 실시형태는 본 명세서에 기재된 다른 실시형태와 적절히 조합할 수 있다.

(실시형태 5)

본 실시형태에서는 상술한 실시형태에서 설명한 트랜지스터를 사용할 수 있는 전자 기기의 예에 대하여 설명한다.

상술한 실시형태에서 설명한 트랜지스터는 다양한 전자 기기(게임기도 포함함) 및 전기 기기에 적용할 수 있다. 전자 기기 및 전기 기기로서는 텔레비전, 모니터 등의 표시 장치, 조명 장치, 데스크톱 또는 노트북 퍼스널 컴퓨터, 워드 프로세서, DVD(Digital Versatile Disc) 등의 기억 매체에 기억된 정지 화상 또는 동영상을 재생하는 화상 재생 장치, 포터블 CD 플레이어, 라디오, 테이프 레코더, 헤드폰 스테레오, 스테레오, 무선 전화 핸드셋, 트랜시버, 휴대 전화, 자동차 전화, 휴대형 게임기, 계산기, 휴대 정보 단말, 전자 수첩, 전자 사전, 전자 번역기, 음성 입력 기기, 비디오 카메라, 디지털 스틸 카메라, 전기 면도기, IC칩, 전자 레인지 등의 고주파 가열 장치, 전기 밥솥, 전기 세탁기, 전기 청소기, 에어컨디셔너 등의 공기 조절 설비, 식기 세척기, 식기 건조기, 의류 건조기, 이불 건조기, 전기 냉장고, 전기 냉동고, 전기 냉동 냉장고, DNA 보존용 냉동고, 방사선 측정기, 투석 장치 등의 의료 기기 등을 들 수 있다. 또한, 연기 감지기, 가스 경보 장치, 방범 경보 장치 등의 경보 장치도 들 수 있다. 또한, 유도등, 신호기, 벨트 컨베이어, 엘리베이터, 에스컬레이터, 산업용 로봇, 전력 저장 시스템 등의 산업 기기도 들 수 있다. 또한, 석유를 사용한 엔진이나 비수계 이차 전지로부터의 전력을 사용하여 전동기에 의하여 추진하는 이동체, 예를 들어 전기 자동차(EV: Electric Vehicle), 내연 기관과 전동기를 겸비한 하이브리드 차(HEV: Hybrid Electric Vehicle), 플러그인 하이브리드 차(PHEV: Plug-in Hybrid Electric Vehicle), 이들의 타이어 차륜을 무한 궤도로 바꾼 장궤(裝軌) 차량, 전동 어시스트 자전거를 포함하는 원동기가 달린 자전거, 자동 이륜차, 전동 휠체어, 골프용 카트, 소형 또는 대형 선박, 잠수함, 헬리콥터, 항공기, 로켓, 인공 위성, 우주 탐사기나 혹성 탐사기, 우주선 등을 들 수 있다. 이들 전자 기기의 구체적인 예를 도 10 내지 도 13에 도시하였다.

먼저, 경보 장치의 예로서, 화재 경보기의 구성에 대하여 설명한다. 또한, 본 명세서에서 화재 경보기란, 화재 발생을 급보하는 장치 전반을 가리키고, 예를 들어, 주택용 화재 경보기, 자동 화재 경보 설비, 및 상기 자동 화재 경보 설비에 사용되는 화재 감지기 등도 화재 경보기에 포함된다.

도 10에 도시된 경보 장치는 적어도 마이크로 컴퓨터(700)를 갖는다. 여기서, 마이크로 컴퓨터(700)는 경보 장치 내부에 제공된다. 마이크로 컴퓨터(700)는 고전위 전원선(VDD)과 전기적으로 접속된 파워 게이트 컨트롤러(703)와, 고전위 전원선(VDD) 및 파워 게이트 컨트롤러(703)와 전기적으로 접속된 파워 게이트(704)와, 파워 게이트(704)와 전기적으로 접속된 CPU(Central Processing Unit)(705)와, 파워 게이트(704) 및 CPU(705)와 전기적으로 접속된 검출부(709)가 제공된다. 또한, CPU(705)에는 휘발성 기억부(706)와 비휘발성 기억부(707)가 포함된다.

또한, CPU(705)는 인터페이스(708)를 통하여 버스 라인(702)과 전기적으로 접속된다. 인터페이스(708)도 CPU(705)와 마찬가지로 파워 게이트(704)와 전기적으로 접속된다. 인터페이스(708)의 버스 규격으로서는 I2C 버스 등을 사용할 수 있다. 또한, 본 실시형태에 기재된 경보 장치에는 인터페이스(708)를 통하여 파워 게이트(704)와 전기적으로 접속되는 발광 소자(730)가 제공된다.

발광 소자(730)는 지향성이 강한 광을 방출하는 것이 바람직하며, 예를 들어, 유기 EL 소자, 무기 EL 소자, LED(Light Emitting Diode) 등을 사용할 수 있다.

파워 게이트 컨트롤러(703)는 타이머를 갖고, 상기 타이머에 따라 파워 게이트(704)를 제어한다. 파워 게이트(704)는 파워 게이트 컨트롤러(703)의 제어에 따라, CPU(705), 검출부(709), 및 인터페이스(708)에 고전위 전원선(VDD)으로부터 공급되는 전원을 공급 또는 차단한다. 여기서, 파워 게이트(704)로서는, 예를 들어, 트랜지스터 등 스위칭 소자를 사용할 수 있다.

이와 같은 파워 게이트 컨트롤러(703) 및 파워 게이트(704)를 사용함으로써, 광량을 측정하는 기간에 검출부(709), CPU(705), 및 인터페이스(708)에 전원을 공급하고, 측정 기간과 다음 측정 기간 사이에는 검출부(709), CPU(705), 및 인터페이스(708)로의 전원 공급을 차단할 수 있다. 이와 같이 경보 장치를 동작시킴으로써, 상술한 각 구성에 연속적으로 전원을 공급하는 경우보다 소비 전력을 저감할 수 있다.

또한, 파워 게이트(704)로서 트랜지스터를 사용하는 경우, 비휘발성 기억부(707)에 사용되는, 오프 전류가 매우 낮은 트랜지스터, 예를 들어 산화물 반도체를 사용한 트랜지스터를 사용하는 것이 바람직하다. 이와 같은 트랜지스터를 사용함으로써 파워 게이트(704)에 의하여 전원을 차단할 때에 누설 전류를 저감하고 소비 전력을 저감할 수 있다.

본 실시형태에 기재된 경보 장치에 직류 전원(701)을 제공하고, 직류 전원(701)으로부터 고전위 전원선(VDD)에 전원을 공급하여도 좋다. 직류 전원(701)의 고전위 측의 전극은 고전위 전원선(VDD)과 전기적으로 접속되고, 직류 전원(701)의 저전위 측의 전극은 저전위 전원선(VSS)과 전기적으로 접속된다. 저전위 전원선(VSS)은 마이크로 컴퓨터(700)에 전기적으로 접속된다. 여기서, 고전위 전원선(VDD)에는 고전위(H)가 인가된다. 또한 저전위 전원선(VSS)에는, 예를 들어, 접지 전위(GND) 등의 저전위(L)가 인가된다.

직류 전원(701)으로서 전지를 사용하는 경우에는, 예를 들어 고전위 전원선(VDD)과 전기적으로 접속된 전극, 저전위 전원선(VSS)과 전기적으로 접속된 전극, 및 상기 전지를 유지할 수 있는 하우징을 갖는 전지 케이스를 하우징에 제공하는 구성으로 하면 좋다. 또한, 본 실시형태에 기재된 경보 장치에 직류 전원(701)을 반드시 제공할 필요는 없으며, 예를 들어 상기 경보 장치 외부에 제공된 교류 전원으로부터 배선을 통하여 전원을 공급하는 구성으로 하여도 좋다.

또한, 상기 전지로서, 이차 전지, 예를 들어 리튬 이온 이차 전지(리튬 이온 축전지, 리튬 이온 전지, 또는 리튬 이온 배터리라고도 함)를 사용할 수도 있다. 또한, 상기 이차 전지를 충전할 수 있도록 태양 전지를 제공하는 것이 바람직하다.

검출부(709)는 이상 상태에 따른 물리량을 계측하여 계측 값을 CPU(705)로 송신한다. 이상 상태에 따른 물리량은 경보 장치의 용도에 따라 상이하고, 화재 경보기로서 기능하는 경보 장치에서는 화재에 따른 물리량을 계측한다. 그러므로, 검출부(709)는 화재에 따른 물리량으로서 광량을 계측하고 연기의 존재를 감지한다.

검출부(709)는 파워 게이트(704)와 전기적으로 접속된 광 센서(711)와, 파워 게이트(704)와 전기적으로 접속된 증폭기(712)와, 파워 게이트(704) 및 CPU(705)와 전기적으로 접속된 AD 컨버터(713)를 갖는다. 발광 소자(730) 및 검출부(709)에 제공된 광 센서(711), 증폭기(712), 및 AD 컨버터(713)는 파워 게이트(704)가 검출부(709)에 전원을 공급하였을 때 동작한다.

도 11에 경보 장치의 단면의 일부를 도시하였다. 상기 경보 장치는, p형 반도체 기판(801)에 형성된 소자 분리 영역(803)과, 게이트 절연막(807), 게이트 전극(809), n형 불순물 영역(811a), n형 불순물 영역(811b), 절연막(815), 및 절연막(817)을 갖는 n형 트랜지스터(870)를 포함한다. n형 트랜지스터(870)는 단결정 실리콘 등 산화물 반도체와는 상이한 반도체를 사용하여 형성되기 때문에, 충분한 고속 동작이 가능하게 된다. 이로써, 고속 액세스가 가능한 CPU의 휘발성 기억부를 형성할 수 있다.

절연막(815) 및 절연막(817)의 일부를 선택적으로 에칭한 개구부에는 콘택트 플러그(819a) 및 콘택트 플러그(819b)가 형성되고, 절연막(817), 콘택트 플러그(819a), 및 콘택트 플러그(819b) 위에 홈부를 갖는 절연막(821)이 제공된다.

절연막(821)의 홈부에 배선(823a) 및 배선(823b)이 형성되고, 절연막(821), 배선(823a), 및 배선(823b) 위에는 스퍼터링법 또는 CVD법 등에 의하여 형성된 절연막(820)이 제공된다. 또한, 상기 절연막 위에 홈부를 갖는 절연막(822)이 형성된다.

절연막(822) 위에는 스퍼터링법 또는 CVD법 등에 의하여 형성된 절연막(825)이 제공되고, 절연막(825) 위에는 제 2 트랜지스터(880) 및 광전 변환 소자(890)가 제공된다.

제 2 트랜지스터(880)는, 산화물막(806a)과, 산화물 반도체막(806b)과, 산화물막(806c)과, 산화물막(806a), 산화물 반도체막(806b), 및 산화물막(806c)에 접하는 저저항 영역(805a) 및 저저항 영역(805b)과, 저저항 영역(805a) 및 저저항 영역(805b)에 접하는 소스 전극(816a) 및 드레인 전극(816b)과, 게이트 절연막(812)과, 게이트 전극(804)과, 산화물 절연막(818)을 포함한다. 또한, 광전 변환 소자(890)와 제 2 트랜지스터(880)를 덮는 절연막(845)이 제공되고, 절연막(845) 위에, 드레인 전극(816b)에 접하여 배선(849)을 갖는다. 배선(849)은 제 2 트랜지스터(880)의 드레인 전극과 n형 트랜지스터(870)의 게이트 전극(809)을 전기적으로 접속하는 노드로서 기능한다. 또한, 도면에 도시된 단면 C-D는 단면 A-B에 나타낸 트랜지스터(870)의 안 길이 방향의 단면을 도시한 것이다.