KR20140073351A - 발광 소자 - Google Patents

발광 소자 Download PDFInfo

- Publication number

- KR20140073351A KR20140073351A KR1020120141503A KR20120141503A KR20140073351A KR 20140073351 A KR20140073351 A KR 20140073351A KR 1020120141503 A KR1020120141503 A KR 1020120141503A KR 20120141503 A KR20120141503 A KR 20120141503A KR 20140073351 A KR20140073351 A KR 20140073351A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- light emitting

- electrode

- emitting cell

- conductive

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission

- H01L27/153—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission in a repetitive configuration, e.g. LED bars

- H01L27/156—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission in a repetitive configuration, e.g. LED bars two-dimensional arrays

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/10—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a light reflecting structure, e.g. semiconductor Bragg reflector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/14—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure

- H01L33/145—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure with a current-blocking structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

- H01L33/42—Transparent materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/62—Arrangements for conducting electric current to or from the semiconductor body, e.g. lead-frames, wire-bonds or solder balls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/38—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes with a particular shape

- H01L33/385—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes with a particular shape the electrode extending at least partially onto a side surface of the semiconductor body

Abstract

실시예의 발광 소자는 기판과, 기판 위에 수평 방향으로 서로 이격되어 배열되며, 각각은 하부 및 상부 반도체층과 활성층을 갖는 발광 구조물과, 상부 전극 및 하부 전극을 포함하는 복수의 발광 셀과, 이웃하는 복수의 발광 셀 중 하나인 제1 발광 셀의 하부 전극과 다른 하나인 제2 발광 셀의 상부 전극을 전기적으로 연결하는 도전형 상호 연결층 및 제2 발광 셀의 상부 전극과 상부 반도체층 사이로부터 이웃하는 복수의 발광 셀과 도전형 상호 연결층 사이로 연장되어 배치된 전류 차단층을 포함하고, 복수의 발광 셀 각각은 제2 발광 셀의 상부 전극과 전류 차단층 사이로부터 제2 발광 셀의 상부 반도체층 위로 연장되어 배치되어, 제2 발광 셀의 상부 전극과 제2 발광 셀의 상부 반도체층을 전기적으로 연결하는 전도층을 더 포함한다.

Description

실시예는 발광 소자에 관한 것이다.

질화갈륨(GaN)의 금속 유기화학기상 증착법 및 분자선 성장법 등의 발달을 바탕으로 고휘도 및 백색광 구현이 가능한 적색, 녹색 및 청색 발광 다이오드(LED:Light Emitting Diode)가 개발되었다.

이러한 LED는 백열등과 형광등 등의 기존 조명기구에 사용되는 수은(Hg)과 같은 환경 유해물질이 포함되어 있지 않아 우수한 친환경성을 가지며, 긴 수명, 저전력 소비특성 등과 같은 장점이 있기 때문에 기존의 광원들을 대체하고 있다. 이러한 LED 소자의 핵심 경쟁 요소는 고효율 및 고출력 칩 및 패키징 기술에 의한 고휘도의 구현이다.

고휘도를 구현하기 위해서 광 추출 효율을 높이는 것이 중요하다. 광 추출 효율을 높이기 위하여 플립 칩(flip-chip) 구조, 표면 요철 형성(surface texturing), 요철이 형성된 사파이어 기판(PSS:Patterned Sapphire Substrate), 광 결정(photonic crystal) 기술, 및 반사 방지막(anti-reflection layer) 구조 등을 이용한 다양한 방법들이 연구되고 있다.

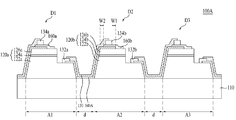

도 1은 일반적인 발광 소자의 단면도를 나타낸다.

도 1을 참조하면, 발광 소자는 복수의 발광 셀(D1, D2)로 구성되고, 각 발광 셀(D1, D2)은 기판(10), 발광 구조물(20, 40), 제1 전극(32, 52), 제2 전극(34, 54), 패시베이션(passivation)층(60) 및 금속 연결층(70)으로 구성된다.

발광 구조물(20, 40)은 기판(10) 상에 배치된 n형 반도체층(22, 42), 활성층(24, 44) 및 p형 반도체층(26, 46)으로 구성된다. 금속 연결층(70)은 인접하는 발광 셀(D1, D2) 중 하나(D1)의 제1 전극(32)과 다른 하나(D2)의 제2 전극(54)을 전기적으로 연결한다. 이때, 패시베이션층(60)은 금속 연결층(70)과 발광 셀(D2)의 발광 구조물(40)을 서로 전기적으로 절연시키고, 인접하는 발광 셀(D1, D2)을 서로 전기적으로 절연시키고, 발광 셀(D1)의 n형 반도체층(22)과 금속 연결층(70)을 서로 전기적으로 절연시킨다.

도 1에 예시된 일반적인 발광 소자의 경우, 패시베이션층(60)을 형성하기 위한 별도의 공정이 추가로 필요하므로, 발광 소자의 제작 시간과 비용이 증가하는 문제점이 있다.

실시예는 제작 시간과 비용이 절감되고 광 추출 효율이 향상되며 외부 조명 장치에 이용될 수 있는 발광 소자를 제공한다.

실시예의 발광 소자는 기판; 상기 기판 위에 수평 방향으로 서로 이격되어 배열되며, 각각은 서로 다른 도전형의 하부 및 상부 반도체층, 상기 하부 및 상부 반도체층 사이에 배치된 활성층을 갖는 발광 구조물과, 상기 상부 반도체층 위에 배치된 상부 전극 및 상기 하부 반도체층 위에 배치된 하부 전극을 포함하는 복수의 발광 셀; 이웃하는 복수의 발광 셀 중 하나인 제1 발광 셀의 하부 전극과 상기 이웃하는 복수의 발광 셀 중 다른 하나인 제2 발광 셀의 상부 전극을 전기적으로 연결하는 도전형 상호 연결층; 및 상기 제2 발광 셀의 상부 전극과 상부 반도체층 사이로부터 상기 이웃하는 복수의 발광 셀과 상기 도전형 상호 연결층 사이로 연장되어 배치된 전류 차단층을 포함하고, 상기 복수의 발광 셀 각각은 상기 제2 발광 셀의 상부 전극과 상기 전류 차단층 사이로부터 상기 제2 발광 셀의 상부 반도체층 위로 연장되어 배치되어, 상기 제2 발광 셀의 상부 전극과 제2 발광 셀의 상부 반도체층을 전기적으로 연결하는 전도층을 더 포함한다.

상기 전류 차단층은 상기 제1 발광 셀의 하부 반도체층과 상기 도전형 상호 연결층의 사이, 상기 기판과 상기 도전형 상호 연결층의 사이, 및 상기 제2 발광 셀의 발광 구조물과 상기 도전형 상호 연결층의 사이에 배치될 수 있다.

상기 제2 발광 셀의 상부 전극은 상기 제2 발광 셀의 상기 상부 반도체층과 대향하는 하부면을 갖고, 상기 제2 발광 셀의 상부 전극과 상부 반도체층 사이에 배치되는 상기 전류 차단층은 상기 상부 전극과 대향하는 상부면을 갖고, 상기 전류 차단층의 상부면의 면적은 상기 상부 전극의 하부면 전체의 면적 이상일 수 있다.

또는, 상기 제2 발광 셀의 상부 전극과 상기 제1 발광 셀의 하부 전극과 상기 도전형 상호 연결층은 일체형 층일 수 있다. 이 경우, 상기 일체형 층은 상기 제2 발광 셀의 상기 상부 반도체층과 대향하는 하부면을 갖고, 상기 일체형 층과 상기 제2 발광 셀의 상부 반도체층의 사이에 배치되는 상기 전류 차단층은 상기 일체형 층과 대향하는 상부면을 갖고, 상기 전류 차단층의 상부면의 면적은 상기 일체형 층의 하부면 전체의 면적 이상일 수 있다.

상기 상부 반도체층 상부에 배치된 상기 전도층의 면적은 상기 상부 반도체층의 상부 면적 이하일 수 있다.

상기 전도층은 ITO(Indium Tin Oxide), TO(Tin Oxide), IZO(Indium Zinc Oxide), IZTO(Indium Zinc Tin Oxide), IAZO(Indium Aluminium Zinc Oxide), IGZO(Indium Gallium Zinc Oxide), IGTO(Indium Gallium Tin Oxide), AZO(Aluminium Zinc Oxide), ATO(Aluminium Tin Oxide), GZO(Gallium Zinc Oxide), IrOx, RuOx, RuOx/ITO, Ni, Ag, Ni/IrOx/Au 또는 Ni/IrOx/Au/ITO 중 적어도 하나를 이용하여 단층 또는 다층으로 배치될 수 있다.

상기 전류 차단층은 분산 브래그 반사층일 수 있다. 상기 분산 브래그 반사층은 굴절률이 서로 다른 제1 및 제2 층이 교대로 적어도 1회 이상 적층된 절연 물질을 포함할 수 있다.

상기 상부 전극은 서로 중첩된 제1 접착층 및 제1 본딩층을 포함하고, 상기 제1 접착층과 상기 제1 본딩층 사이에 반사층이 개재되지 않을 수 있다. 상기 상부 전극은 상기 제1 접착층과 상기 제1 본딩층 사이에 배치된 제1 배리어층을 더 포함할 수 있다.

상기 하부 전극은 서로 중첩된 제2 접착층 및 제2 본딩층을 포함하고, 상기 제2 접착층과 상기 제2 본딩층 사이에 반사층이 개재되지 않을 수 있다. 상기 하부 전극은 상기 제2 접착층과 상기 제2 본딩층 사이에 배치된 제2 배리어층을 더 포함할 수 있다.

상기 복수의 발광 셀은 상기 도전형 상호 연결층에 의해 서로 직렬 연결될 수 있다.

실시예에 따른 발광 소자는 패시베이션층의 역할을 수행하도록 전류 차단층을 배치하므로 패시베이션층을 형성하는 공정이 추가적으로 별도로 수행될 필요가 없어 제작 시간과 비용을 절감시킬 수 있고, 분산 브래그 반사층에 의해 전류 차단층을 구현하여 반사 효율을 증가시킴으로써 광 추출 효율을 개선시킬 수 있고, 상부 및 하부 전극과 도전형 상호 연결층을 반사층없이 구현하여 부식에 강하므로 외부 조명용으로 이용될 수도 있다.

도 1은 일반적인 발광 소자의 단면도를 나타낸다.

도 2는 실시예에 의한 발광 소자의 단면도를 나타낸다.

도 3은 다른 실시예에 의한 발광 소자의 단면도를 나타낸다.

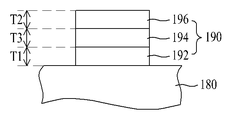

도 4는 도 2 또는 도 3에 예시된 하부 전극, 상부 전극, 도전형 상호 연결층 및 일체형 층 중 적어도 하나의 실시예의 단면도를 나타낸다.

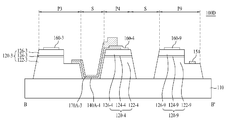

도 5는 또 다른 실시예에 의한 발광 소자의 단면도를 나타낸다.

도 6은 또 다른 실시예에 따른 발광 소자의 평면도를 나타낸다.

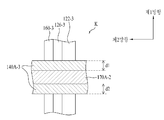

도 7은 도 6에 예시된 'K' 부분을 확대 도시한 도면이다.

도 8은 도 6에 예시된 발광 소자의 A-A'선을 따라 절개한 단면도를 나타낸다.

도 9는 도 6에 도시된 발광 소자의 B-B'선을 따라 절개한 단면도를 나타낸다.

도 10은 도 6에 도시된 발광 소자의 회로도를 나타낸다.

도 11은 또 다른 실시예에 따른 발광 소자의 단면도를 나타낸다.

도 12는 실시 예에 따른 발광 소자에 의해 구현되는 발광 소자 패키지를 포함하는 조명 장치의 분해 사시도이다.

도 13은 실시 예에 따른 발광 소자에 의해 구현되는 발광 소자 패키지를 포함하는 표시 장치를 나타낸다.

도 2는 실시예에 의한 발광 소자의 단면도를 나타낸다.

도 3은 다른 실시예에 의한 발광 소자의 단면도를 나타낸다.

도 4는 도 2 또는 도 3에 예시된 하부 전극, 상부 전극, 도전형 상호 연결층 및 일체형 층 중 적어도 하나의 실시예의 단면도를 나타낸다.

도 5는 또 다른 실시예에 의한 발광 소자의 단면도를 나타낸다.

도 6은 또 다른 실시예에 따른 발광 소자의 평면도를 나타낸다.

도 7은 도 6에 예시된 'K' 부분을 확대 도시한 도면이다.

도 8은 도 6에 예시된 발광 소자의 A-A'선을 따라 절개한 단면도를 나타낸다.

도 9는 도 6에 도시된 발광 소자의 B-B'선을 따라 절개한 단면도를 나타낸다.

도 10은 도 6에 도시된 발광 소자의 회로도를 나타낸다.

도 11은 또 다른 실시예에 따른 발광 소자의 단면도를 나타낸다.

도 12는 실시 예에 따른 발광 소자에 의해 구현되는 발광 소자 패키지를 포함하는 조명 장치의 분해 사시도이다.

도 13은 실시 예에 따른 발광 소자에 의해 구현되는 발광 소자 패키지를 포함하는 표시 장치를 나타낸다.

이하, 본 발명을 구체적으로 설명하기 위해 실시예를 들어 설명하고, 발명에 대한 이해를 돕기 위해 첨부도면을 참조하여 상세하게 설명하기로 한다. 그러나, 본 발명에 따른 실시예들은 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 아래에서 상술하는 실시예들에 한정되는 것으로 해석되지 않아야 한다. 본 발명의 실시예들은 당 업계에서 평균적인 지식을 가진 자에게 본 발명을 보다 완전하게 설명하기 위해서 제공되는 것이다.

본 실시예의 설명에 있어서, 각 구성요소(element)의 "상(위) 또는 하(아래)(on or under)"에 형성되는 것으로 기재되는 경우에 있어, 상(위) 또는 하(아래)(on or under)는 두 개의 구성요소(element)가 서로 직접(directly)접촉되거나 하나 이상의 다른 구성요소(element)가 상기 두 구성요소(element) 사이에 배치되어(indirectly) 형성되는 것을 모두 포함한다.

또한 "상(위)" 또는 "하(아래)(on or under)"로 표현되는 경우 하나의 구성요소(element)를 기준으로 위쪽 방향 뿐만 아니라 아래쪽 방향의 의미도 포함할 수 있다.

도 2는 실시예에 의한 발광 소자(100A)의 단면도를 나타낸다.

도 2에 예시된 발광 소자(100A)는 기판(110), 복수의 발광 셀(D1, D2, D3), 전류 차단층(140A) 및 도전형 상호 연결층(150)을 포함한다.

기판(110)은 반도체 물질 성장에 적합한 물질, 캐리어 웨이퍼로 형성될 수 있다. 또한 기판(110)은 열 전도성이 뛰어난 물질로 형성될 수 있으며, 전도성 기판 또는 절연성 기판일 수 있다. 또한, 기판(110)은 투광성을 갖는 물질로 이루어질 수도 있으며, 발광 셀(D1 ~ D3)의 전체 질화물 발광 구조물(120a, 120b)의 휨을 가져오지 않으면서, 스크라이빙(scribing) 공정 및 브레이킹(breading) 공정을 통해 별개의 칩으로 잘 분리시키기 위한 정도의 기계적 강도를 가질 수 있다. 예를 들어 기판(110)은 사파이어(Al203), GaN, SiC, ZnO, Si, GaP, InP, Ga203, GaAs, Ge 중 적어도 하나를 포함하는 물질일 수 있다. 이러한 기판(110)의 상면에는 요철 패턴 형상을 가질 수 있다. 예를 들어, 비록 도시되지는 않았지만 기판(110)은 PSS(Patterned Sapphire Substrate)일 수 있다.

또한, 기판(110)과 발광 구조물(120a, 120b) 사이에 버퍼층(미도시)이 배치될 수도 있다. 버퍼층은 Ⅲ-Ⅴ족 원소의 화합물 반도체를 이용하여 형성될 수 있다. 버퍼층은 기판(110)과 발광 구조물(120a, 120b) 사이의 격자 상수의 차이를 줄여주는 역할을 한다. 예를 들어, 버퍼층은 AlN을 포함하거나 언 도프드(undoped) 질화물을 포함할 수 있으나, 이에 한정되지는 않는다. 버퍼층은 기판(110)의 종류와 발광 구조물(120a, 120b)의 종류에 따라 생략될 수도 있다.

복수의 발광 셀(D1 ~ D3)은 기판(110) 위에 수평 방향으로 서로 이격되어 배열된다. 여기서, 설명의 편의상 발광 셀(D1 ~ D3)의 개수는 3개인 것으로 도시하였지만, 실시예는 이에 국한되지 않으며 발광 셀이 2개이거나 4개 이상인 경우에도 동일하게 적용될 수 있다.

제1 발광 셀(D1)은 기판(110)의 제1 영역(A1)에 배치되고, 제2 발광 셀(D2)은 기판(110)의 제2 영역(A2)에 배치되고, 제3 발광 셀(D3)은 기판(110)의 제3 영역(A3)에 배치된다. 이웃하는 제1 및 제2 발광 셀(D1, D2)은 일정한 거리(d)만큼 서로 이격되어 배치되고, 제2 및 제3 발광 셀(D2, D3)은 일정한 거리(d)만큼 서로 이격되어 배치된다. 예를 들어, 이격 거리(d)는 2 ㎛ 내지 7 ㎛ 예를 들어 5 ㎛일 수 있다.

발광 셀(D1, D2) 각각은 기판(110) 위에 배치된 발광 구조물(120a, 120b), 하부 전극(132a, 132b), 상부 전극(134a, 134b) 및 전도층(160a, 160b)을 포함한다.

발광 구조물(120a, 120b)은 기판(110)의 상부에 순차적으로 배치된 하부 반도체층(122a, 122b), 활성층(124a, 124b) 및 상부 반도체층(126a, 126b)을 포함한다. 하부 반도체층(122a, 122b)과 상부 반도체층(126a, 126b)은 서로 다른 도전형일 수 있다.

하부 반도체층(122a, 122b)은 기판(110)과 활성층(124a, 124b) 사이에 배치되며, 반도체 화합물을 포함할 수 있으며, Ⅲ-Ⅴ족, Ⅱ-Ⅵ족 등의 화합물 반도체로 구현될 수 있으며, 제1 도전형 도펀트가 도핑될 수 있다. 예를 들어, 햐부 반도체층(122a, 122b)은 AlxInyGa(1-x-y)N (0≤x≤1, 0≤y≤1, 0≤x+y≤1)의 조성식을 갖는 반도체 물질, InAlGaN, AlGaAs, GaP, GaAs, GaAsP, AlGaInP 중 어느 하나 이상을 포함할 수 있다. 하부 반도체층(122a, 122b)은 제1 도전형의 반도체층일 수 있다. 만일, 하부 반도체층(122a, 122b)이 n형 반도체층인 경우, 제1 도전형 도펀트는 Si, Ge, Sn, Se, Te 등과 같은 n형 도펀트를 포함할 수 있다. 하부 반도체층(122a, 122b)은 단층 또는 다층 구조를 가질 수 있으며, 이에 대해 한정하지는 않는다.

활성층(124a, 124b)은 하부 반도체층(122a, 122b)과 상부 반도체층(126a, 126b) 사이에 배치되며, 단일 우물 구조(Double Hetero Structure), 다중 우물 구조, 단일 양자 우물 구조, 다중 양자 우물(MQW:Multi Quantum Well) 구조, 양자점 구조 또는 양자선 구조 중 어느 하나를 포함할 수 있다. 활성층(124a, 124b)은 Ⅲ-Ⅴ족 원소의 화합물 반도체 재료를 이용하여 우물층과 장벽층, 예를 들면 InGaN/GaN, InGaN/InGaN, GaN/AlGaN, InAlGaN/GaN, GaAs(InGaAs),/AlGaAs, GaP(InGaP)/AlGaP 중 어느 하나 이상의 페어 구조를 가질 수 있으나 이에 한정되지는 않는다. 우물층은 장벽층의 에너지 밴드 갭보다 작은 에너지 밴드 갭을 갖는 물질로 이루어질 수 있다.

상부 반도체층(126a, 126b)은 활성층(124a, 124b)의 상부에 배치되며, 반도체 화합물을 포함할 수 있다. 상부 반도체층(126a, 126b)은 Ⅲ-Ⅴ족, Ⅱ-Ⅵ족 등의 화합물 반도체로 구현될 수 있으며, 예를 들어 InxAlyGa1 -x- yN (0≤x≤1, 0≤y≤1, 0≤x+y≤1)의 조성식을 갖는 반도체 물질 또는 AlInN, AlGaAs, GaP, GaAs, GaAsP, AlGaInP 중 어느 하나 이상을 포함할 수 있다.

제1 도전형 반도체층인 하부 반도체층(122a, 122b)과 달리 상부 반도체층(126a, 126b)은 제2 도전형 반도체층일 수 있으며, 제2 도전형 도펀트가 도핑될 수 있다. 상부 반도체층(126a, 126b)이 p형 반도체층인 경우, 제2 도전형 도펀트는 Mg, Zn, Ca, Sr, Ba 등과 같은 p형 도펀트일 수 있다. 상부 반도체층(126a, 126b)은 단층 또는 다층 구조를 가질 수 있으며, 이에 대해 한정하지는 않는다.

하부 반도체층(122a, 122b)은 n형 반도체층이고 상부 반도체층(126a, 126b)은 p형 반도체층으로 구현되거나, 하부 반도체층(122a, 122b)은 p형 반도체층이고 상부 반도체층(126a, 126b)은 n형 반도체층으로 구현될 수 있다. 이에 따라 발광 구조물(120a, 120b)은 N-P 접합, P-N 접합, N-P-N 접합, 및 P-N-P 접합 구조 중 적어도 하나를 포함할 수 있다.

하부 전극(132a, 132b)은 하부 반도체층(122a, 122b) 위에 배치되고, 상부 전극(134a, 134b)은 상부 반도체층(126a, 126b) 위에 배치된다. 하부 전극(132a, 132b)을 하부 반도체층(122a, 122b) 위에 배치하기 위해, 발광 구조물(120a, 120b)은 하부 반도체층(122a, 122b) 일부를 노출할 수 있다. 즉, 상부 반도체층(126a, 126b), 활성층(124a, 124b) 및 하부 반도체층(122a, 122b)의 일부가 메사 식각(mesa etching)에 의하여 식각되어 하부 반도체층(122a, 122b)의 일부를 노출할 수 있다. 이때, 하부 반도체층(122a, 122b)의 노출면은 활성층(124a, 124b)의 하면보다 낮게 위치할 수 있다. 상부 전극(134a, 134b)과 하부 전극(132a, 132b)에 대해서는 도 4를 참조하여 보다 상세히 후술된다.

한편, 전류 차단층(140A)의 일부는 복수의 발광 셀 각각(예를 들어 D2)의 상부 전극(134b)과 상부 반도체층(126b) 사이에 배치된다. 이와 같이 배치된 전류 차단층(140A)은 상부 전극(134b)으로부터 활성층(124b)으로 향하는 캐리어가 보다 잘 확산되도록 하여 활성층(124b)의 광도 향상에 기여할 수 있도록 한다.

만일, 제2 발광 셀(D2)의 상부 전극(132b)은 제2 발광 셀(D2)의 상부 반도체층(126b)과 대향하는 하부면을 갖고, 제2 발광 셀(D2)의 상부 전극(134b)과 상부 반도체층(126b) 사이에 배치되는 전류 차단층(140A)은 상부 전극(134b)과 대향하는 상부면을 갖는다고 하자. 이때, 전류 차단층(140A)이 전술한 바와 같이 캐리어를 확산시키는 역할을 수행하기 위해서는, 상부 반도체층(126b) 위에 배치되는 전류 차단층(140A)의 상부면의 면적은 상부 전극(134b)의 하부면 전체의 면적 이상일 수 있다. 즉, 도 2에 예시된 단면 형상에서, 폭(W1)은 0 이상일 수 있다. 이를 위해, 전류 차단층(140A)은 실리콘 옥사이드(SiO2)와 같은 절연 물질로 형성될 수 있다.

발광 셀(예를 들어 D1, D2) 각각에서, 전도층(160a, 160b)은 상부 전극(134a, 134b)과 전류 차단층(140A) 사이로부터 상부 반도체층(126a, 126b) 위로 연장되어 배치되어, 상부 전극(134a, 134b)과 상부 반도체층(126a, 126b)을 전기적으로 연결한다.

전도층(160a, 160b)은 전반사를 감소시킬 뿐만 아니라, 투광성이 좋기 때문에 활성층(124a, 124b)으로부터 방출되어 상부 반도체층(126a, 126b)을 거친 빛의 추출 효율을 증가시킬 수 있다. 전도층(160a, 160b)은 발광 파장에 대해 투과율이 높은 투명한 산화물계 물질, 예컨대, ITO(Indium Tin Oxide), TO(Tin Oxide), IZO(Indium Zinc Oxide), IZTO(Indium Zinc Tin Oxide), IAZO(Indium Aluminium Zinc Oxide), IGZO(Indium Gallium Zinc Oxide), IGTO(Indium Gallium Tin Oxide), AZO(Aluminium Zinc Oxide), ATO(Aluminium Tin Oxide), GZO(Gallium Zinc Oxide), IrOx, RuOx, RuOx/ITO, Ni, Ag, Ni/IrOx/Au 또는 Ni/IrOx/Au/ITO 중 적어도 하나 이상을 이용하여 단층 또는 다층으로 구현될 수 있다.

상부 반도체층(126a, 126b) 상부에 배치된 전도층(160a, 160b)의 면적은 상부 반도체층(126a, 126b)의 상부 면적 이하일 수 있다. 따라서, 도 2에 예시된 바와 같이, 폭(W2)은 0 이상일 수 있다.

한편, 도전형 상호 연결층(150)은 복수의 발광 셀(D1 ~ D3)에서 인접하는 2개의 발광 셀(예를 들어 D1, D2)을 연결하는 역할을 한다. 즉, 도전형 상호 연결층(150)은 이웃하는 2개의 발광 셀(D1, D2) 중 하나인 제1 발광 셀(D1)의 하부 전극(132a)과 이웃하는 발광 셀(D1, D2) 중 다른 하나인 제2 발광 셀(D2)의 상부 전극(134b)을 전기적으로 연결하는 역할을 한다. 도 2에 예시된 바와 같이, 2개의 발광 셀(D1, D2)은 도전형 상호 연결층(150)에 의해 전기적으로 서로 직렬 연결될 수 있으나, 이에 국한되지 않는다. 즉, 발광 셀(D1, D2)은 도전형 상호 연결층(150)에 의해 전기적으로 서로 병렬로 연결될 수도 있다.

도전형 상호 연결층(150)은 하부 전극(132a, 132b) 및/또는 상부 전극(134a, 134b)과 동일하거나 서로 다른 구성 및 동일하거나 서로 다른 물질로 이루어질 수 있다. 또한, 도전형 상호 연결층(150)의 두께는 하부 전극(132a, 132b) 및/또는 상부 전극(134a, 134b)의 두께와 동일하거나 서로 다를 수 있다. 도전형 상호 연결층(150)은 Cr, Rd, Au, Ni, Ti 또는 Pt 중 적어도 하나를 포함할 수 있으나 이에 국한되지 않는다.

한편, 본 실시예에 의하면, 전류 차단층(140A)은 발광 셀(예를 들어 D2)의 상부 전극(134b)과 상부 반도체층(126b)의 사이로부터 이웃하는 발광 셀(D1, D2)과 도전형 상호 연결층(150) 사이로 연장되어 배치될 수 있다. 즉, 전류 차단층(140A)은 제1 발광 셀(D1)의 하부 반도체층(122a)과 도전형 상호 연결층(150)의 사이, 기판(110)과 도전형 상호 연결층(150)의 사이, 및 제2 발광 셀(D2)의 발광 구조물(120b)과 도전형 상호 연결층(150)의 사이에 배치될 수 있다. 따라서, 도 2에 예시된 전류 차단층(140A)은 도 1에 도시된 패시베이션층(60)의 역할을 수행함을 알 수 있다. 이를 위해, 전술한 바와 같이 전류 차단층(140A)은 절연 물질로 이루어질 수 있다.

전술한 바와 같이, 도 1에 도시된 발광 소자가 별도의 패시베이션층(60)을 마련하는 대신에, 본 실시예에 의한 발광 소자(100A)는 전류 차단층(140A)으로 패시베이션층(60)의 역할을 수행한다. 즉, 전류 차단층(140A)은 전류 차단층 고유의 역할을 수행할 수 있을 뿐만 아니라 패시베이션층(60)의 역할도 수행할 수 있다. 따라서, 제작 단가를 저렴하게 하고, 공정 시간을 단축시킬 수 있다.

도 3은 다른 실시예에 의한 발광 소자(100B)의 단면도를 나타낸다.

도 2에 예시된 발광 소자(100A)에서 전류 차단층(140A)은 단일층으로 구현되어 있다. 반면에, 다른 실시예에 의하면, 도 3에 예시된 바와 같이, 전류 차단층(140B)은 분산 브래그 반사층(DBR:Distributed Bragg Reflector)으로 구현될 수도 있다. 분산 브래그 반사층이란, 굴절율이 서로 다른 둘 이상의 절연층이 교번하여 다수 층으로 적층되어 생성됨에 따라 반사율을 높이는 층을 의미한다. 분산 브래그 반사층(140B)은 90% 이하의 반사율을 갖는 반사층보다 더 높은 반사율 예를 들어, 98%의 반사율을 갖기 때문에 반사층의 역할을 보다 우수하게 수행할 수 있다.

도 3의 경우, 굴절률이 서로 다른 제1 층(142) 및 제2 층(144)이 교대로 1회 적층된 모습을 나타내지만, 1회보다 더 많은 횟수로 적층될 수 있다.

제1 층(142)은 저굴절율층으로서, 예를 들어 1.4의 굴절율을 갖는 실리콘 산화물(SiO2) 또는 1.6의 굴절율을 갖는 알루미늄 산화물(Al2O3)로 이루어질 수 있다. 또한, 제2 층(144)은 고굴절율층으로서, 예를 들어, 2.05 내지 2.25의 굴절율을 갖는 실리콘 질화물(Si3N4), 2 이상의 굴절율을 갖는 티타늄질화물(TiO2), 또는 3 이상의 굴절율을 갖는 Si-H으로 이루어질 수 있다.

또한, 분산 브래그 반사층(140B)에서 제1 층(142)과 제2 층(144) 각각은 λ/(4n)의 두께를 가질 수 있다. 여기서, λ은 활성층(124b)에서 방출된 광의 파장을 나타내고, n은 해당 층의 굴절율을 나타낸다.

또한, 도 2에 예시된 발광 소자(100A)에서 인접하는 발광 셀(예를 들어 D1과 D2) 중 어느 하나인 제1 발광 셀(D1)의 하부 전극(132a)과 인접하는 발광 셀 중 다른 하나인 제2 발광 셀(D2)의 상부 전극(134b) 및 이들(D1, D2)을 전기적으로 연결시키는 도전형 상호 연결층(150)은 각각 별개로 형성되어 있다. 반면에, 다른 실시예에 의하면, 도 3에 예시된 바와 같이, 도전형 상호 연결층(150), 제1 발광 셀(D1)의 하부 전극(132a) 및 제2 발광 셀(D2)의 상부 전극(134b)은 서로 일체형 층(170A)으로 구현될 수도 있다.

만일, 일체형 층(170)이 제2 발광 셀(D2)의 상부에서 상부 반도체층(126b)과 대향하는 하부면을 갖고, 일체형 층(170A)과 상부 반도체층(126b)의 사이에 배치되는 전류 차단층(140B)이 일체형 층(170A)과 대향하는 상부면을 갖는다고 할 때, 전류 차단층(140B)의 상부면의 면적은 일체형 층(170A)의 하부면 전체의 면적 이상일 수 있다. 이는 도 3에 예시된 바와 같이 제2 발광 셀(D2)의 상부 전극(134b)과 도전형 상호 연결층(150)이 일체형 층(170A)으로 구현될 경우, 일체형 층(170A)과 상부 반도체층(126b) 사이에 개재되어 배치된 전류 차단층(140B)이 전술한 바와 같이 일체형 층(170A)으로부터 활성층(124b)으로 공급되는 캐리어를 보다 잘 확산시켜 전류를 차단시키는 역할을 하도록 하기 위함이다.

전술한 도 2와 도 3의 차이점을 제외하면, 도 3에 예시된 발광 소자(100B)는 도 2에 예시된 발광 소자(100A)와 동일하므로, 이에 대한 상세한 설명을 생략한다.

도 4는 도 2 또는 도 3에 예시된 하부 전극(132a, 134b), 상부 전극(134a, 134b), 도전형 상호 연결층(150) 및 일체형 층(170A) 중 적어도 하나의 실시예의 단면도를 나타낸다.

만일, 도 4의 층(190)이 하부 전극(132a, 132b)에 해당한다면 베이스층(180)은 하부 반도체층(122a, 122b)에 해당하고, 층(190)이 상부 전극(134a, 134b)에 해당한다면 베이스층(180)은 전도층(160a, 160b)에 해당하고, 층(190)이 도전형 상호 연결층(150) 또는 일체형 층(170A)에 해당한다면 베이스층(180)은 전류 차단층(140A, 140B)에 해당한다.

도 4를 참조하면, 층(190)은 서로 중첩된 접착층(192) 및 본딩층(196)을 포함할 수 있다. 즉, 접착층(192)은 베이스층(180)의 위에 배치되고, 본딩층(196)은 접착층(192)의 위에 배치될 수 있다. 이때, 접착층(192)과 본딩층(196) 사이에 반사층(미도시)이 개재될 수도 있고 개재되지 않을 수도 있다.

접착층(192)은 베이스층(180)과 오믹 접촉하는 물질을 포함할 수 있다. 예를 들어, 접착층(192)은 Cr, Rd 및 Ti 중 적어도 하나의 재료로, 단층 또는 다층 구조로 형성될 수 있다. 또한, 접착층(192)의 두께(T1)는 적어도 5 ㎚ 내지 15 ㎚일 수 있다. 예를 들어, 접착층(192)은 2 ㎚ 내지 10 ㎛의 두께(T1)를 가질 수 있다.

또한, 본딩층(196)은 접착층(192)에 접하여 배치될 수도 있지만, 도 4에 예시된 바와 같이 배리어층(194)이 개재될 경우 배리어층(194)의 상부에 배치될 수도 있다. 본딩층(196)은 Au을 포함할 수 있고, 100 ㎚ 내지 180 ㎚의 두께(T2) 예를 들어, 140 ㎚의 두께를 가질 수 있다.

층(190)은 접착층(192)과 본딩층(196) 사이에 배치된 배리어층(194)을 더 포함할 수 있지만, 배리어층(194)은 생략될 수도 있다. 배리어층(194)은 접착층(192)과 본딩층(196)에 각각 접하여 배치될 수 있다.

배리어층(194)은 Ni, Cr, Ti 및 Pt 중 적어도 하나를 포함하는 재료로, 단층 또는 다층으로 형성될 수 있다. 예를 들어, 배리어층(194)은 Cr과 Pt의 합금으로 이루어질 수 있다. 또한, 배리어층(194)은 200 ㎚ 내지 300 ㎚ 예를 들어, 250 ㎚의 두께(T3)를 가질 수 있다.

만일, 층(190)이 상부 전극(134a, 134b)일 경우, 접착층(192)과 배리어층(194) 사이에 반사층이 개재될 경우, 반사층은 활성층(124a, 124b)에서 방출된 광을 반사시켜 층(190)의 금속에 의해 흡수되는 광량을 줄일 수 있다. 그러나, 반사층이 접착층(192)과 배리어층(194) 사이에 개재될 경우, Au로 이루어진 본딩층(196)과 Al로 이루어진 반사층이 Ni로 이루어진 배리어층(194)을 사이에 두고 서로 상호 확산(inter-diffusion)될 수도 있다.

또한, 충분한 반사도를 얻기 위해, 반사층은 통상 50 ㎚ 내지 300 ㎚의 두께로 형성될 수 있다. 이러한 두꺼운 반사층의 존재로 인해, 접착층(192)이 예를 들면 2 ㎚ 보다 얇은 두께로 형성되어, 층(190)과 발광 구조물(120a. 120b) 사이에 접착력이 저하될 수 있다.

그러나, 접착층(192)과 본딩층(196) 사이에 반사층이 개재되지 않을 경우, 반사층이 개재되지 않는 두께만큼 접착층(192)을 두껍게 형성할 수 있어, 층(190)과 베이스층(180) 사이의 접착력을 향상시킬 수 있고, 반사층과 본딩층(196) 간의 상호 확산이 발생할 염려도 제거될 수 있다. 이때, 접착층(192)은 2 ㎚ 이상의 두꺼운 두께(T1)를 가질 수 있다.

또한, 전술한 발광 소자(100A, 100B)가 조명용으로 사용될 경우 반사층인 알루미늄이 부식될 수 있다. 따라서, 실시예에서 반사층을 개재하지 않을 경우 이러한 부식의 문제가 사전에 예방될 수 있어, 발광 소자(100A, 100B)가 외부 조명용으로 이용될 수 있다.

도 5는 또 다른 실시예에 의한 발광 소자(100C)의 단면도를 나타낸다.

도 3에 도시된 발광 소자(100B)에서 일체형 층(170A)은 단일층인 반면, 도 5에 예시된 발광 소자(100C)의 일체형 층(170B)은 접착층(172), 배리어층(174) 및 본딩층(176)을 포함할 수 있다. 이를 제외하면, 도 5에 예시된 발광 소자(100C)는 도 3에 예시된 발광 소자(100B)와 동일하므로, 이에 대한 상세한 설명을 생략한다. 도 5에 예시된 접착층(172), 배리어층(174) 및 본딩층(176)은 도 4에 도시된 접착층(192), 배리어층(194) 및 본딩층(196)에 각각 해당하므로 이에 대한 상세한 설명을 생략한다. 도 5의 경우, 일체형 층(170B)에서 배리어층(174)은 생략될 수도 있다.

도 6은 또 다른 실시예에 따른 발광 소자(100D)의 평면도를 나타내고, 도 7은 도 6에 예시된 'K' 부분을 확대 도시한 도면이고, 도 8은 도 6에 예시된 발광 소자(100D)의 A-A'선을 따라 절개한 단면도를 나타내고, 도 9는 도 6에 도시된 발광 소자(100D)의 B-B'선을 따라 절개한 단면도를 나타낸다.

도 6 내지 도 9를 참조하면, 발광 소자(100D)는 M개의 발광 영역들(P1 내지 PM, M>1인 자연수)을 포함한다. 설명의 편의상 도 6 내지 도 9에 예시된 바와 같이 M=9라고 가정하여 설명하지만, M이 9보다 작거나 큰 경우에도, 실시예는 동일하게 적용될 수 있다.

발광 소자(100D)는 기판(110), 복수의 발광 영역(P1 내지 P9)으로 구분되는 발광 구조물(120-1 내지 120-9), 전류 차단층(140A-1 내지 140A-9), 일체형 층(170A-1 내지 170A-8), 제1 전극(152), 제2 전극(154) 및 전도층(160-1 내지 160-9)을 포함한다.

기판(110) 및 발광 구조물(120-1 내지 120-9)은 도 2 또는 도 3의 기판(110) 및 발광 구조물(120a, 120b)에 각각 해당하므로 이들에 대한 상세한 설명을 생략한다. 각 발광 구조물(120-1 내지 120-9)은 도 2 및 도 3에 예시된 하부 반도체층(122a, 122b), 활성층(124a, 124b) 및 상부 반도체층(126a, 126b)에 각각 해당하는 하부 반도체층(122-1 내지 122-9), 활성층(124-1 내지 124-9) 및 상부 반도체층(126-1 내지 126-9)을 포함한다.

이하, 하부 반도체층(122-1 내지 122-9) 각각은 n형 반도체층이고, 상부 반도체층(126-1 내지 126-9) 각각은 p형 반도체층이라고 가정하여 실시예를 설명하지만, 실시예는 이에 국한되지 않는다. 즉, 하부 반도체층(122-1 내지 122-9) 각각은 p형 반도체층이고, 상부 반도체층(126-1 내지 126-9) 각각은 n형 반도체층인 경우에도 본 실시예는 적용될 수 있다.

하나의 칩(single chip)의 발광 구조물(120-1 내지 120-9)은 경계 영역(S)에 의하여 복수 개의 발광 영역(P1 내지 P9)으로 구분될 수 있다. 경계 영역(S)은 발광 영역(P1 내지 P9) 각각의 둘레에 위치하는 영역일 수 있으며, 기판(110)일 수 있다. 복수의 발광 영역(P1 내지 P9) 각각의 면적은 동일할 수 있으나, 이에 한정되는 것은 아니다.

전류 차단층(140A-1 내지 140A-9) 각각은 도 2에 예시된 전류 차단층(140A)과 동일하므로 이에 대한 상세한 설명은 생략한다. 다만, 전류 차단층(140A-1 내지 140A-9) 중 전류 차단층(140A-1)은 패시베이션층(60)의 역할을 수행하지 않으며, 제1 전극(152)으로부터 활성층(124-1)으로 향하는 캐리어가 확산되도록 하여 활성층(124-1)의 광도 향상에 기여할 수 있도록 하는 역할만을 수행한다.

도 6 및 도 8을 참조하면, 제1 전극(152)은 복수의 발광 영역(P1 내지 P9) 중 어느 하나의 발광 영역(예컨대, P1)의 상부 반도체층(126-1) 상에 배치된다. 제1 전극(152)은 전도층(160-1)을 경유하여 상부 반도체층(126-1)과 전기적으로 접촉할 수 있다. 예컨대, 제1 전극(152)은 직렬 연결되는 발광 영역들(P1 내지 P9) 중 첫 번째 발광 영역(예컨대, P1)의 전도층(160-1)과 접촉할 수 있다. 제1 전극(152)은 제1 전원을 제공하기 위한 와이어(미도시)가 본딩될 수 있다.

도 6 및 도 9를 참조하면, 제2 전극(154)은 복수의 발광 영역들(P1 내지 P9) 중 다른 어느 하나의 발광 영역(예컨대, P9)의 하부 반도체층(122-9) 상에 배치되며, 하부 반도체층(122-9)과 접촉할 수 있다. 제2 전극(154)은 제2 전원을 제공하기 위한 와이어(미도시)가 본딩될 수 있다.

일체형 층(170A-1 내지 150-8)은 전류 차단층(140A-2 내지 140A-8) 위에 각각 배치되며, 복수의 발광 영역(P1 내지 P9)을 전기적으로 직렬 연결한다. 예컨대, 일체형 층(170A-1 내지 170A-8)은 제1 전극(152)이 위치하는 제1 발광 영역(P1)을 시점으로 하고, 제2 전극(154)이 위치하는 제9 발광 영역(P9)을 종점으로 하여 복수의 발광 영역들(P1 내지 P9)을 직렬 연결할 수 있다.

일체형 층(170A-1 내지 170A-8)은 각각은 도 3에 예시된 일체형 층(170A)과 동일하므로 이에 대한 상세한 설명은 생략한다. 각 일체형 층(예를 들면 170A-1)은 인접하는 발광 영역들(예컨대, P1 및 P2) 중 어느 하나의 발광 영역(P1)의 하부 반도체층(122-1)과 나머지 다른 하나의 발광 영역(예컨대, P2)의 전도층(160-2)을 서로 전기적으로 연결할 수 있다.

도 6 내지 도 8을 참조하면, 일체형 층(예컨대, 170A-2)과 상부 반도체층(예컨대, 126-3)의 상부면 사이에 배치된 전류 차단층(예컨대, 140A-3)은 일체형 층(170A-2)과 대향하는 상부면을 갖는다고 하자. 또한, 일체형 층(170A-2)은 상부 반도체층(126-3)과 대향하는 하부면을 갖는다고 하자. 이때, 전류 차단층(140A-3)의 상부면의 면적은 일체형 층(170A-2)의 하부면 전체의 면적 이상일 수 있다. 이는, 일체형 층(170A-2)과 상부 반도체층(126-3) 사이에 개재되어 배치된 전류 차단층(140A-3)이 일체형 층(170A-2)으로부터 활성층(124-3)으로 공급되는 캐리어를 확산시켜 전류를 차단시키도록 하기 위함이다. 이때, 전류 차단층(140A-3)의 상부면은 일체형 층(170A-2)의 하부면 보다 더 클 수 있다. 이 경우, 도 7에 예시된 바와 같이 전류 차단층(140A-3)의 폭은 일체형 층(170A-2)의 폭보다 제1 방향으로 d1+d2만큼 더 넓을 수 있고, 도 8에 예시된 바와 같이 제2 방향으로 w1만큼 더 넓을 수 있다.

발광 소자(100D)에 포함되는 서로 직렬 연결되는 복수의 발광 영역(P1 내지 P9)을 순서대로 제1 발광 영역 내지 제9 발광 영역이라 한다. 즉, 제1 전극(152)이 위치하는 발광 영역을 제1 발광 영역(P1)이라 하고, 제2 전극(154)이 위치하는 발광 영역을 제9 발광 영역이라 한다. 여기서 "인접하는 발광 영역"은 제k 발광 영역과 제k+1 발광 영역일 수 있으며, 제k 일체형 층은 제k 발광 영역과 제k+1 발광 영역을 전기적으로 직렬 연결할 수 있고, 1≤k≤(M-1)일 수 있다.

즉, 제k 일체형 층은 제k 발광 영역의 하부 반도체층(122-k)과 제k+1 발광 영역의 전도층(160-(k+1))을 전기적으로 연결할 수 있다. 예컨대, 도 8을 참조하면, 제2 일체형 층(170A-2)은 제2 발광 영역(P2), 제3 발광 영역(P3) 및 그 사이의 경계 영역(S) 상에 위치할 수 있다. 그리고 제2 일체형 층(170A-2)은 제2 발광 영역(P2)의 하부 반도체층(122-2)과 제3 발광 영역(P3)의 전도층(160-3)을 경유하여 상부 반도체층(126-3)을 전기적으로 연결한다.

이때, 제k+1 전류 차단층(140A-(k+1))은 제k 일체형 층(170A-k)과 제k 하부 반도체층(122-k) 사이, 제k 일체형 층(170A-k)과 기판(110) 사이, 제k 일체형 층(170A-k)과 제k+1 하부 반도체층(122-(k+1)) 사이, 제k 일체형 층(170A-k)과 제k+1 활성층(124-(k+1)) 사이, 제k 일체형 층(170-k)과 제k+1 상부 반도체층(126-(k+1)) 사이에 위치하여 서로를 전기적으로 절연시킬 수 있다.

도 8 또는 도 9에 예시된 바와 달리, 전류 차단층(140A-1 내지 140-9)은 도 3에 예시된 바와 같이 분산 브래그 반사층(140B)으로 구현될 수 있다. 이 경우, 제1 전극(152) 및 일체형 층(170A-1 내지 170A-8)으로 빛이 흡수되어 손실되는 것을 차단함으로써, 발광 효율을 향상시킬 수 있다.

도 10은 도 6에 도시된 발광 소자(100D)의 회로도를 나타낸다.

도 6 및 도 10을 참조하면, 발광 소자(100D)는 공통된 하나의 (+) 단자(152)와 공통된 하나의 (-) 단자(154)를 가질 수 있다.

도 11은 또 다른 실시예에 따른 발광 소자(100E)의 단면도를 나타낸다.

도 11을 참조하면, 발광 소자(100E)는 서브 마운트(submount, 204), 제1 금속층(232), 제2 금속층(234), 제1 범프부(210), 제2 범프부(220) 및 발광 소자(240)를 포함한다.

도 11의 발광 소자(100E)는 플립 칩 형태로 구현한 일 례이지만, 실시예는 이에 한정되는 것은 아니며, 다른 실시 예에 따른 발광 소자(100A ~ 100C)가 도 13에 도시된 바와 같은 플립 칩 형태로 구현될 수도 있다.

서브 마운트(204)는 발광 소자(240)를 실장한다. 서브 마운트(204)는 패키지 몸체(package body) 또는 인쇄 회로 기판(Printed Circuit Board) 등으로 구현될 수 있으며, 발광 소자(240)가 플립 칩 본딩(flip chip bonding)될 수 있는 다양한 형태일 수 있다.

발광 소자(240)는 서브 마운트(204) 상에 배치되고, 제1 범프부(210) 및 제2 범프부(220)에 의하여 서브 마운트(204)와 전기적으로 연결된다. 도 11에 도시된 발광 소자(240)는 도 6에 도시된 발광 소자(100D)의 제1 및 제9 발광 영역(P1, P9)과 동일한 단면을 갖는다. 따라서, 동일한 부분에 대해서는 상세한 설명을 생략한다.

서브 마운트(204)는 폴리프탈아미드(PolyPhthal Amide, PPA), 액정 고분자(Liquid Crystal Polymer, LCP), 폴리아미드9T(PolyAmide9T, PA9T), 등과 같은 수지, 금속, 감광성 유리(photo sensitive glass), 사파이어, 세라믹, 인쇄회로기판(Printed Circuit Board) 등을 포함할 수 있다. 그러나 실시 예에 따른 서브 마운트(204)가 이러한 물질로 한정되는 것은 아니다.

제1 금속층(232) 및 제2 금속층(234)은 서브 마운트(204) 상면에 수평 방향으로 서로 이격하여 배치된다. 여기서 서브 마운트(204)의 상면은 발광 소자(240)에 대향하는 면일 수 있다. 제1 금속층(232) 및 제2 금속층(234)은 전도성 금속, 예컨대, 알루미늄(Al) 또는 로듐(Rh)일 수 있다.

제1 범프부(210) 및 제2 범프부(220)는 서브 마운트(204)와 발광 소자(240) 사이에 배치된다. 제1 범프부(210)는 제2 전극(154)와 제1 금속층(232)을 전기적으로 연결할 수 있다. 제2 범프부(220)는 제1 전극(152)과 제2 금속층(234)을 전기적으로 연결할 수 있다.

제1 범프부(210)는 제1 확산 방지 접착층(212), 제1 범퍼(bumper, 214) 및 제2 확산 방지 접착층(216)을 포함한다. 제1 범퍼(214)는 제2 전극(154)과 제1 금속층(232) 사이에 위치한다. 제1 확산 방지 접착층(212)은 제2 전극(154)과 제1 범퍼(214) 사이에 위치하고, 제1 범퍼(214)와 제2 전극(154)을 서로 접합시킨다. 즉, 제1 확산 방지 접착층(212)은 제1 범퍼(214)와 제2 전극(154) 사이의 접착력을 향상시키고, 제1 범퍼(214)에 포함된 이온이 제2 전극(154)을 통하여 발광 구조물(120-9)로 침투 또는 확산하는 것을 방지하는 역할을 한다.

제2 확산 방지 접착층(216)은 제1 범퍼(214)와 제1 금속층(232) 사이에 배치되고, 제1 범퍼(214)와 제1 금속층(232)을 접합시킨다. 제2 확산 방지 접착층(216)은 제1 범퍼(214)와 제1 금속층(232) 사이의 접착력을 향상시키고, 제1 범퍼(214)에 포함된 이온이 제1 금속층(232)을 통하여 서브 마운트(204)로 침투 또는 확산하는 것을 방지하는 역할을 한다.

제2 범프부(220)는 제3 확산 방지 접착층(222), 제2 범퍼(224), 및 제4 확산 방지 접착층(226)을 포함한다. 제2 범퍼(224)는 제1 전극(152)과 제2 금속층(234) 사이에 위치한다.

제3 확산 방지 접착층(222)은 제1 전극(152)과 제2 범퍼(224) 사이에 위치하고, 양자를 서로 접합시킨다. 즉 제3 확산 방지 접착층(222)은 접착력을 향상시키고, 제2 범퍼(224)에 포함된 이온이 제1 전극(152)을 통하여 발광 구조물(120-1)로 침투 또는 확산하는 것을 방지하는 역할을 한다.

제4 확산 방지 접착층(226)은 제2 범퍼(224)와 제2 금속층(234) 사이에 배치되고, 제2 범퍼(224)와 제2 금속층(234)을 접합시킨다. 제4 확산 방지 접착층(226)은 제2 범퍼(224)와 제2 금속층(234) 사이의 접착력을 향상시키고, 제2 범퍼(224)에 포함된 이온이 제2 금속층(234)을 통하여 서브 마운트(204)로 침투 또는 확산하는 것을 방지하는 역할을 한다.

제1 내지 제4 확산 방지 접착층(212, 216, 222, 226)은 Pt, Ti, W/Ti, Au 중 적어도 하나 또는 이들의 합금일 수 있다. 또한 제1 범프(214) 및 제2 범프(224)는 티타늄(Ti), 구리(Cu), 니켈(Ni), 금(Au), 크롬(Cr), 탄탈늄(Ta), 백금(Pt), 및 주석(Sn) 중 적어도 하나를 포함할 수 있다.

전술한 실시예에 따른 발광 소자의 복수 개가 기판 상에 발광 소자 패키지로서 배열될 수 있으며, 발광 소자 패키지의 광 경로 상에 광학 부재인 도광판, 프리즘 시트, 확산 시트 등이 배치될 수 있다. 이러한 발광 소자 패키지, 기판, 광학 부재는 백라이트 유닛으로 기능할 수 있다.

또 다른 실시 예는 상술한 실시 예들에 기재된 발광 소자 또는 발광 소자 패키지를 포함하는 표시 장치, 지시 장치, 조명 시스템으로 구현될 수 있으며, 예를 들어, 조명 시스템은 램프, 가로등을 포함할 수 있다.

도 12는 실시 예에 따른 발광 소자에 의해 구현되는 발광 소자 패키지를 포함하는 조명 장치의 분해 사시도이다. 도 12를 참조하면, 조명 장치는 광을 투사하는 광원(750)과 광원(750)이 내장되는 하우징(700)과 광원(750)의 열을 방출하는 방열부(740) 및 광원(750)과 방열부(740)를 하우징(700)에 결합하는 홀더(760)를 포함한다.

하우징(700)은 전기 소켓(미도시)에 결합되는 소켓 결합부(710)와, 소켓 결합부(710)와 연결되고 광원(750)이 내장되는 몸체부(730)를 포함한다. 몸체부(730)에는 하나의 공기 유동구(720)가 관통하여 형성될 수 있다.

하우징(700)의 몸체부(730) 상에 복수 개의 공기 유동구(720)가 구비되며, 공기 유동구(720)는 하나이거나, 복수 개일 수 있다. 공기 유동구(720)는 몸체부(730)에 방사상으로 배치되거나 다양한 형태로 배치될 수 있다.

광원(750)은 기판(754) 상에 구비되는 복수 개의 발광 소자 패키지(752)를 포함한다. 기판(754)은 하우징(700)의 개구부에 삽입될 수 있는 형상일 수 있으며, 후술하는 바와 같이 방열부(740)로 열을 전달하기 위하여 열전도율이 높은 물질로 이루어질 수 있다. 복수 개의 발광 소자 패키지는 전술한 발광 소자를 포함할 수 있다.

광원(750)의 하부에는 홀더(760)가 구비되며, 홀더(760)는 프레임 및 다른 공기 유동구를 포함할 수 있다. 또한, 도시되지는 않았으나 광원(750)의 하부에는 광학 부재가 구비되어 광원(750)의 발광 소자 패키지(752)에서 투사되는 빛을 확산, 산란 또는 수렴시킬 수 있다.

도 13은 실시 예에 따른 발광 소자에 의해 구현되는 발광 소자 패키지를 포함하는 표시 장치를 나타낸다.

도 13을 참조하면, 표시 장치(800)는 바텀 커버(810)와, 바텀 커버(810) 상에 배치되는 반사판(820)과, 광을 방출하는 발광 모듈(830, 835)과, 반사판(820)의 전방에 배치되며 상기 발광 모듈(830, 835)에서 발산되는 빛을 표시 장치 전방으로 안내하는 도광판(840)과, 도광판(840)의 전방에 배치되는 프리즘 시트들(850, 860)을 포함하는 광학 시트와, 광학 시트 전방에 배치되는 디스플레이 패널(870)과, 디스플레이 패널(870)과 연결되고 디스플레이 패널(870)에 화상 신호를 공급하는 화상 신호 출력 회로(872)와, 디스플레이 패널(870)의 전방에 배치되는 컬러 필터(880)를 포함할 수 있다. 여기서 바텀 커버(810), 반사판(820), 발광 모듈(830, 835), 도광판(840), 및 광학 시트는 백라이트 유닛(Backlight Unit)을 이룰 수 있다.

발광 모듈은 기판(830) 상의 발광 소자 패키지(835)를 포함하여 이루어진다. 여기서, 기판(830)은 PCB 등이 사용될 수 있다. 발광 소자 패키지(835)는 전술한 실시 예에 따른 발광 소자를 포함할 수 있다.

바텀 커버(810)는 표시 장치(800) 내의 구성 요소들을 수납할 수 있다. 그리고, 반사판(820)은 본 도면처럼 별도의 구성요소로 마련될 수도 있으며, 도광판(840)의 후면이나, 바텀 커버(810)의 전면에 반사도가 높은 물질로 코팅되는 형태로 마련되는 것도 가능하다.

여기서, 반사판(820)은 반사율이 높고 초박형으로 사용 가능한 소재를 사용할 수 있고, 폴리에틸렌 테레프탈레이트(PolyEthylene Terephtalate; PET)를 사용할 수 있다.

그리고, 도광판(830)은 폴리메틸메타크릴레이트(PolyMethylMethAcrylate; PMMA), 폴리카보네이트(PolyCarbonate; PC), 또는 폴리에틸렌(PolyEthylene; PE) 등으로 형성될 수 있다.

그리고, 제1 프리즘 시트(850)는 지지 필름의 일면에, 투광성이면서 탄성을 갖는 중합체 재료로 형성될 수 있으며, 중합체는 복수 개의 입체구조가 반복적으로 형성된 프리즘층을 가질 수 있다. 여기서, 복수 개의 패턴은 도시된 바와 같이 마루와 골이 반복적으로 스트라이프 타입으로 구비될 수 있다.

그리고, 제2 프리즘 시트(860)에서 지지 필름 일면의 마루와 골의 방향은, 제1 프리즘 시트(850) 내의 지지필름 일면의 마루와 골의 방향과 수직할 수 있다. 이는 발광 모듈과 반사 시트로부터 전달된 빛을 디스플레이 패널(1870)의 전면으로 고르게 분산하기 위함이다.

그리고, 도시되지는 않았으나, 도광판(840)과 제1 프리즘 시트(850) 사이에 확산 시트가 배치될 수 있다. 확산 시트는 폴리에스터와 폴리카보네이트 계열의 재료로 이루어질 수 있으며, 백라이트 유닛으로부터 입사된 빛을 굴절과 산란을 통하여 광 투사각을 최대로 넓힐 수 있다. 그리고, 확산 시트는 광확산제를 포함하는 지지층과, 광출사면(제1 프리즘 시트 방향)과 광입사면(반사시트 방향)에 형성되며 광확산제를 포함하지 않는 제1 레이어와 제2 레이어를 포함할 수 있다.

실시 예에서 확산 시트, 제1 프리즘시트(850), 및 제2 프리즘시트(860)가 광학 시트를 이루는데, 광학 시트는 다른 조합 예를 들어, 마이크로 렌즈 어레이로 이루어지거나 확산 시트와 마이크로 렌즈 어레이의 조합 또는 하나의 프리즘 시트와 마이크로 렌즈 어레이의 조합 등으로 이루어질 수 있다.

디스플레이 패널(870)은 액정 표시 패널(Liquid crystal display)가 배치될 수 있는데, 액정 표시 패널 외에 광원을 필요로 하는 다른 종류의 표시 장치가 구비될 수 있다.

이상에서 실시예를 중심으로 설명하였으나 이는 단지 예시일 뿐 본 발명을 한정하는 것이 아니며, 본 발명이 속하는 분야의 통상의 지식을 가진 자라면 본 실시예의 본질적인 특성을 벗어나지 않는 범위에서 이상에 예시되지 않은 여러 가지의 변형과 응용이 가능함을 알 수 있을 것이다. 예를 들어, 실시예에 구체적으로 나타난 각 구성 요소는 변형하여 실시할 수 있는 것이다. 그리고 이러한 변형과 응용에 관계된 차이점들은 첨부된 청구 범위에서 규정하는 본 발명의 범위에 포함되는 것으로 해석되어야 할 것이다.

100A, 100B, 100C, 100D, 100E, 240: 발광 소자

110: 기판 120a, 120b, 120-1 ~ 120-9: 발광 구조물

132a, 132b, 134a, 134b, 152, 154: 전극

140A, 140B, 140A-1 ~ 140A-9: 전류 차단층

150: 도전형 상호 연결층 160a, 160b, 160-1 ~ 160-9: 전도층

170A, 170B, 170A-1 ~ 170A-9: 일체형 층

204: 서브 마운트 232, 234: 금속층

210, 220: 범프부 700: 하우징

740: 방열부 750: 광원

760: 홀더 800: 표시 장치

810: 바텀 커버 820: 반사판

830, 835: 발광 모듈 840: 도광판

850, 860: 프리즘 시트 870: 디스플레이 패널

872: 화상 신호 출력 회로 880: 컬러 필터

110: 기판 120a, 120b, 120-1 ~ 120-9: 발광 구조물

132a, 132b, 134a, 134b, 152, 154: 전극

140A, 140B, 140A-1 ~ 140A-9: 전류 차단층

150: 도전형 상호 연결층 160a, 160b, 160-1 ~ 160-9: 전도층

170A, 170B, 170A-1 ~ 170A-9: 일체형 층

204: 서브 마운트 232, 234: 금속층

210, 220: 범프부 700: 하우징

740: 방열부 750: 광원

760: 홀더 800: 표시 장치

810: 바텀 커버 820: 반사판

830, 835: 발광 모듈 840: 도광판

850, 860: 프리즘 시트 870: 디스플레이 패널

872: 화상 신호 출력 회로 880: 컬러 필터

Claims (14)

- 기판;

상기 기판 위에 수평 방향으로 서로 이격되어 배열되며, 각각은 서로 다른 도전형의 하부 및 상부 반도체층, 상기 하부 및 상부 반도체층 사이에 배치된 활성층을 갖는 발광 구조물과, 상기 상부 반도체층 위에 배치된 상부 전극 및 상기 하부 반도체층 위에 배치된 하부 전극을 포함하는 복수의 발광 셀;

이웃하는 복수의 발광 셀 중 하나인 제1 발광 셀의 하부 전극과 상기 이웃하는 복수의 발광 셀 중 다른 하나인 제2 발광 셀의 상부 전극을 전기적으로 연결하는 도전형 상호 연결층; 및

상기 제2 발광 셀의 상부 전극과 상부 반도체층 사이로부터 상기 이웃하는 복수의 발광 셀과 상기 도전형 상호 연결층 사이로 연장되어 배치된 전류 차단층을 포함하고,

상기 복수의 발광 셀 각각은

상기 제2 발광 셀의 상부 전극과 상기 전류 차단층 사이로부터 상기 제2 발광 셀의 상부 반도체층 위로 연장되어 배치되어, 상기 제2 발광 셀의 상부 전극과 제2 발광 셀의 상부 반도체층을 전기적으로 연결하는 전도층을 더 포함하는 발광 소자. - 제1 항에 있어서, 상기 전류 차단층은

상기 제1 발광 셀의 하부 반도체층과 상기 도전형 상호 연결층의 사이, 상기 기판과 상기 도전형 상호 연결층의 사이, 및 상기 제2 발광 셀의 발광 구조물과 상기 도전형 상호 연결층의 사이에 배치되는 발광 소자. - 제1 항에 있어서, 상기 제2 발광 셀의 상부 전극은 상기 제2 발광 셀의 상기 상부 반도체층과 대향하는 하부면을 갖고,

상기 제2 발광 셀의 상부 전극과 상부 반도체층 사이에 배치되는 상기 전류 차단층은 상기 상부 전극과 대향하는 상부면을 갖고,

상기 전류 차단층의 상부면의 면적은 상기 상부 전극의 하부면 전체의 면적 이상인 발광 소자. - 제1 항에 있어서, 상기 제2 발광 셀의 상부 전극과 상기 제1 발광 셀의 하부 전극과 상기 도전형 상호 연결층은 일체형 층인 발광 소자.

- 제4 항에 있어서, 상기 일체형 층은 상기 제2 발광 셀의 상기 상부 반도체층과 대향하는 하부면을 갖고,

상기 일체형 층과 상기 제2 발광 셀의 상부 반도체층의 사이에 배치되는 상기 전류 차단층은 상기 일체형 층과 대향하는 상부면을 갖고,

상기 전류 차단층의 상부면의 면적은 상기 일체형 층의 하부면 전체의 면적 이상인 발광 소자. - 제1 항에 있어서, 상기 상부 반도체층 상부에 배치된 상기 전도층의 면적은 상기 상부 반도체층의 상부 면적 이하인 발광 소자.

- 제1 항에 있어서, 상기 전도층은

ITO(Indium Tin Oxide), TO(Tin Oxide), IZO(Indium Zinc Oxide), IZTO(Indium Zinc Tin Oxide), IAZO(Indium Aluminium Zinc Oxide), IGZO(Indium Gallium Zinc Oxide), IGTO(Indium Gallium Tin Oxide), AZO(Aluminium Zinc Oxide), ATO(Aluminium Tin Oxide), GZO(Gallium Zinc Oxide), IrOx, RuOx, RuOx/ITO, Ni, Ag, Ni/IrOx/Au 또는 Ni/IrOx/Au/ITO 중 적어도 하나를 이용하여 단층 또는 다층으로 배치된 발광 소자. - 제1 항에 있어서, 상기 전류 차단층은 분산 브래그 반사층인 발광 소자.

- 제8 항에 있어서, 상기 분산 브래그 반사층은 굴절률이 서로 다른 제1 및 제2 층이 교대로 적어도 1회 이상 적층된 절연 물질을 포함하는 발광 소자.

- 제1 항에 있어서, 상기 상부 전극은

서로 중첩된 제1 접착층 및 제1 본딩층을 포함하고, 상기 제1 접착층과 상기 제1 본딩층 사이에 반사층이 개재되지 않은 발광 소자. - 제10 항에 있어서, 상기 상부 전극은

상기 제1 접착층과 상기 제1 본딩층 사이에 배치된 제1 배리어층을 더 포함하는 발광 소자. - 제1 항에 있어서, 상기 하부 전극은

서로 중첩된 제2 접착층 및 제2 본딩층을 포함하고, 상기 제2 접착층과 상기 제2 본딩층 사이에 반사층이 개재되지 않은 발광 소자. - 제12 항에 있어서, 상기 하부 전극은

상기 제2 접착층과 상기 제2 본딩층 사이에 배치된 제2 배리어층을 더 포함하는 발광 소자. - 제1 항에 있어서, 상기 복수의 발광 셀은 상기 도전형 상호 연결층에 의해 서로 직렬 연결되는 발광 소자.

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120141503A KR20140073351A (ko) | 2012-12-06 | 2012-12-06 | 발광 소자 |

| US14/096,138 US9337236B2 (en) | 2012-12-06 | 2013-12-04 | Light emitting device having current blocking layer |

| EP13195745.8A EP2741338B1 (en) | 2012-12-06 | 2013-12-04 | Electrode structure for light-emitting diode array |

| CN201310651693.6A CN103855180B (zh) | 2012-12-06 | 2013-12-05 | 发光器件 |

| JP2013251766A JP2014116604A (ja) | 2012-12-06 | 2013-12-05 | 発光素子 |

| US15/092,682 US9735199B2 (en) | 2012-12-06 | 2016-04-07 | Light emitting device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120141503A KR20140073351A (ko) | 2012-12-06 | 2012-12-06 | 발광 소자 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20140073351A true KR20140073351A (ko) | 2014-06-16 |

Family

ID=49683623

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020120141503A KR20140073351A (ko) | 2012-12-06 | 2012-12-06 | 발광 소자 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US9337236B2 (ko) |

| EP (1) | EP2741338B1 (ko) |

| JP (1) | JP2014116604A (ko) |

| KR (1) | KR20140073351A (ko) |

| CN (1) | CN103855180B (ko) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20160002063A (ko) * | 2014-06-30 | 2016-01-07 | 에피스타 코포레이션 | 광전소자와 그 제조방법 |

| KR20170132470A (ko) * | 2016-05-24 | 2017-12-04 | 엘지이노텍 주식회사 | 반도체 소자 |

| KR20180052500A (ko) * | 2016-11-10 | 2018-05-18 | 서울바이오시스 주식회사 | 고효율 발광 다이오드 |

| US10056429B2 (en) | 2014-05-19 | 2018-08-21 | Epistar Corporation | Electrode structure of optoelectronic device |

| WO2018174425A1 (ko) * | 2017-03-21 | 2018-09-27 | 서울바이오시스주식회사 | 분포 브래그 반사기 적층체를 구비하는 발광 다이오드 |

| KR20190094283A (ko) | 2018-02-03 | 2019-08-13 | 김승훈 | 기억 상기 다기능 테이블 |

| CN110690249A (zh) * | 2015-02-13 | 2020-01-14 | 首尔伟傲世有限公司 | 发光元件 |

| WO2024053994A1 (ko) * | 2022-09-06 | 2024-03-14 | 서울반도체 주식회사 | 발광장치 |

Families Citing this family (40)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103840054A (zh) * | 2012-11-20 | 2014-06-04 | 展晶科技(深圳)有限公司 | 发光二极管芯片 |

| KR20140073351A (ko) * | 2012-12-06 | 2014-06-16 | 엘지이노텍 주식회사 | 발광 소자 |

| US9356212B2 (en) | 2012-12-21 | 2016-05-31 | Seoul Viosys Co., Ltd. | Light emitting diode and method of fabricating the same |

| WO2014098510A1 (en) * | 2012-12-21 | 2014-06-26 | Seoul Viosys Co., Ltd. | Light emitting diode and method of fabricating the same |

| CN106910758B (zh) * | 2013-01-09 | 2020-05-15 | 新世纪光电股份有限公司 | 发光装置 |

| KR20150101783A (ko) * | 2014-02-27 | 2015-09-04 | 서울바이오시스 주식회사 | 발광 다이오드 및 그 제조 방법 |

| KR102197082B1 (ko) * | 2014-06-16 | 2020-12-31 | 엘지이노텍 주식회사 | 발광 소자 및 이를 포함하는 발광소자 패키지 |

| FR3023061B1 (fr) * | 2014-06-27 | 2017-12-15 | Commissariat Energie Atomique | Diode de structure mesa a surface de contact sensiblement plane |

| JP6529223B2 (ja) * | 2014-06-30 | 2019-06-12 | 晶元光電股▲ふん▼有限公司Epistar Corporation | 光電部品 |

| CN104218133B (zh) * | 2014-08-26 | 2017-04-26 | 华灿光电股份有限公司 | 一种发光二极管芯片及其制造方法 |

| CN104362236B (zh) * | 2014-11-11 | 2017-03-08 | 杭州士兰明芯科技有限公司 | 一种led结构及其制作方法 |

| TWI620349B (zh) * | 2015-01-05 | 2018-04-01 | 隆達電子股份有限公司 | 覆晶式發光二極體晶片 |

| CN106067497B (zh) | 2015-04-22 | 2019-09-17 | 新世纪光电股份有限公司 | 发光元件及其制造方法 |

| WO2016177333A1 (zh) * | 2015-05-05 | 2016-11-10 | 湘能华磊光电股份有限公司 | Iii族半导体发光器件倒装结构的制作方法 |

| JP2017059752A (ja) * | 2015-09-18 | 2017-03-23 | 豊田合成株式会社 | 発光装置とその製造方法 |

| US9705035B1 (en) | 2015-12-30 | 2017-07-11 | Epistar Corporation | Light emitting device |

| DE102017205639A1 (de) * | 2016-04-18 | 2017-10-19 | Seoul Viosys Co., Ltd | Lumineszenzdiode mit hoher Effizienz |

| CN105762246B (zh) * | 2016-04-25 | 2017-11-28 | 厦门乾照光电股份有限公司 | 一种垂直结构发光二极管及其制作方法 |

| KR20180007025A (ko) | 2016-07-11 | 2018-01-22 | 삼성디스플레이 주식회사 | 초소형 발광 소자를 포함하는 픽셀 구조체, 표시장치 및 그 제조방법 |

| CN106711306A (zh) * | 2016-12-20 | 2017-05-24 | 合肥彩虹蓝光科技有限公司 | 一种高压led芯片制备方法 |

| WO2018137139A1 (en) * | 2017-01-24 | 2018-08-02 | Goertek. Inc | Micro-led device, display apparatus and method for manufacturing a micro-led device |

| US10043941B1 (en) | 2017-01-31 | 2018-08-07 | International Business Machines Corporation | Light emitting diode having improved quantum efficiency at low injection current |

| FR3062953A1 (fr) * | 2017-02-15 | 2018-08-17 | Commissariat A L'energie Atomique Et Aux Energies Alternatives | Dispositif comportant une pluralite de diodes |

| DE102017104135A1 (de) | 2017-02-28 | 2018-08-30 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement und Verfahren zur Herstellung eines optoelektronischen Bauelements |

| CN106941108B (zh) * | 2017-05-23 | 2019-09-17 | 深圳市华星光电技术有限公司 | 微发光二极管显示面板及其制作方法 |

| CN108110107A (zh) * | 2017-12-18 | 2018-06-01 | 湘能华磊光电股份有限公司 | 一种led芯片的制作方法 |

| JP6822429B2 (ja) | 2018-02-19 | 2021-01-27 | 日亜化学工業株式会社 | 発光素子 |

| JP2019149480A (ja) * | 2018-02-27 | 2019-09-05 | 豊田合成株式会社 | 半導体素子、発光装置、および発光装置の製造方法 |

| CN108447955B (zh) | 2018-03-16 | 2019-07-23 | 厦门市三安光电科技有限公司 | 发光二极管芯片结构及其制作方法 |

| CN208385406U (zh) * | 2018-05-25 | 2019-01-15 | 深圳市瑞丰光电子股份有限公司 | 一种led模组 |

| US11282984B2 (en) * | 2018-10-05 | 2022-03-22 | Seoul Viosys Co., Ltd. | Light emitting device |

| WO2020073295A1 (zh) * | 2018-10-11 | 2020-04-16 | 厦门市三安光电科技有限公司 | 一种发光二极管元件及其制作方法 |

| US11515456B2 (en) * | 2019-02-21 | 2022-11-29 | Innolux Corporation | LED with light adjusting layer extending past the LED |

| KR102649029B1 (ko) * | 2019-04-10 | 2024-03-20 | 삼성전자주식회사 | Led 소자, led 소자의 제조 방법 및 led 소자를 포함하는 디스플레이 장치 |

| JP6843916B2 (ja) * | 2019-05-14 | 2021-03-17 | 晶元光電股▲ふん▼有限公司Epistar Corporation | 光電部品 |

| CN110767670B (zh) * | 2019-10-31 | 2022-11-15 | 成都辰显光电有限公司 | 显示面板、显示装置和显示面板的制作方法 |

| CN113036014B (zh) * | 2019-12-25 | 2022-07-05 | 深圳第三代半导体研究院 | 一种垂直集成单元发光二极管 |

| US11901491B2 (en) * | 2020-10-29 | 2024-02-13 | Lumileds Llc | Light emitting diode devices |

| JP7223046B2 (ja) * | 2021-02-24 | 2023-02-15 | 晶元光電股▲ふん▼有限公司 | 光電部品 |

| US20230118125A1 (en) * | 2021-10-18 | 2023-04-20 | Hamamatsu Photonics K.K. | Optical semiconductor element |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3497741B2 (ja) * | 1998-09-25 | 2004-02-16 | 株式会社東芝 | 半導体発光装置及び半導体発光装置の駆動方法 |

| EP1168539B1 (en) * | 1999-03-04 | 2009-12-16 | Nichia Corporation | Nitride semiconductor laser device |

| JP2002026384A (ja) * | 2000-07-05 | 2002-01-25 | Nichia Chem Ind Ltd | 集積型窒化物半導体発光素子 |

| US6630689B2 (en) * | 2001-05-09 | 2003-10-07 | Lumileds Lighting, U.S. Llc | Semiconductor LED flip-chip with high reflectivity dielectric coating on the mesa |

| US7535028B2 (en) * | 2005-02-03 | 2009-05-19 | Ac Led Lighting, L.Lc. | Micro-LED based high voltage AC/DC indicator lamp |

| KR100640496B1 (ko) | 2005-11-23 | 2006-11-01 | 삼성전기주식회사 | 수직구조 질화갈륨계 발광다이오드 소자 |

| EP2458653B1 (en) | 2006-06-23 | 2023-08-30 | LG Electronics Inc. | Light emitting diode having vertical topology |

| JP2009071220A (ja) * | 2007-09-18 | 2009-04-02 | Toyoda Gosei Co Ltd | Iii族窒化物系化合物半導体発光素子 |

| KR101371511B1 (ko) | 2007-10-04 | 2014-03-11 | 엘지이노텍 주식회사 | 수직형 발광 소자 |

| US8536584B2 (en) * | 2007-11-14 | 2013-09-17 | Cree, Inc. | High voltage wire bond free LEDS |

| JP2009302314A (ja) * | 2008-06-13 | 2009-12-24 | Rohm Co Ltd | GaN系半導体装置 |

| JP5217787B2 (ja) * | 2008-08-27 | 2013-06-19 | 日亜化学工業株式会社 | 半導体発光素子 |

| US7939839B2 (en) * | 2008-09-11 | 2011-05-10 | Bridgelux, Inc. | Series connected segmented LED |

| JP5123269B2 (ja) | 2008-09-30 | 2013-01-23 | ソウル オプト デバイス カンパニー リミテッド | 発光素子及びその製造方法 |

| KR20100076083A (ko) | 2008-12-17 | 2010-07-06 | 서울반도체 주식회사 | 복수개의 발광셀들을 갖는 발광 다이오드 및 그것을 제조하는 방법 |

| KR101533817B1 (ko) * | 2008-12-31 | 2015-07-09 | 서울바이오시스 주식회사 | 복수개의 비극성 발광셀들을 갖는 발광 소자 및 그것을 제조하는 방법 |

| US7982409B2 (en) * | 2009-02-26 | 2011-07-19 | Bridgelux, Inc. | Light sources utilizing segmented LEDs to compensate for manufacturing variations in the light output of individual segmented LEDs |

| CN102201426B (zh) * | 2010-03-23 | 2016-05-04 | 展晶科技(深圳)有限公司 | 发光二极管及其制作方法 |

| JP2012028749A (ja) * | 2010-07-22 | 2012-02-09 | Seoul Opto Devices Co Ltd | 発光ダイオード |

| KR20140073351A (ko) * | 2012-12-06 | 2014-06-16 | 엘지이노텍 주식회사 | 발광 소자 |

-

2012

- 2012-12-06 KR KR1020120141503A patent/KR20140073351A/ko not_active Application Discontinuation

-

2013

- 2013-12-04 US US14/096,138 patent/US9337236B2/en active Active

- 2013-12-04 EP EP13195745.8A patent/EP2741338B1/en active Active

- 2013-12-05 JP JP2013251766A patent/JP2014116604A/ja active Pending

- 2013-12-05 CN CN201310651693.6A patent/CN103855180B/zh active Active

-

2016

- 2016-04-07 US US15/092,682 patent/US9735199B2/en active Active

Cited By (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10522588B2 (en) | 2014-05-19 | 2019-12-31 | Epistar Corporation | Optoelectronic units in an optoelectronic device |

| US10056429B2 (en) | 2014-05-19 | 2018-08-21 | Epistar Corporation | Electrode structure of optoelectronic device |

| US10825860B2 (en) | 2014-05-19 | 2020-11-03 | Epistar Corporation | Electrode configuration for an optoelectronic device |

| US11355550B2 (en) | 2014-05-19 | 2022-06-07 | Epistar Corporation | Optoelectronic device having conductor arrangement structures non-overlapped with heat dissipation pads |

| US11705480B2 (en) | 2014-05-19 | 2023-07-18 | Epistar Corporation | Optoelectronic device with electrodes forming an outer boundary beyond an outer boundary of an epitaxial stack |

| KR20160002063A (ko) * | 2014-06-30 | 2016-01-07 | 에피스타 코포레이션 | 광전소자와 그 제조방법 |

| CN110690249A (zh) * | 2015-02-13 | 2020-01-14 | 首尔伟傲世有限公司 | 发光元件 |

| CN110690249B (zh) * | 2015-02-13 | 2024-01-19 | 首尔伟傲世有限公司 | 发光元件 |

| KR20170132470A (ko) * | 2016-05-24 | 2017-12-04 | 엘지이노텍 주식회사 | 반도체 소자 |

| KR20180052500A (ko) * | 2016-11-10 | 2018-05-18 | 서울바이오시스 주식회사 | 고효율 발광 다이오드 |

| WO2018174425A1 (ko) * | 2017-03-21 | 2018-09-27 | 서울바이오시스주식회사 | 분포 브래그 반사기 적층체를 구비하는 발광 다이오드 |

| KR20190094283A (ko) | 2018-02-03 | 2019-08-13 | 김승훈 | 기억 상기 다기능 테이블 |

| WO2024053994A1 (ko) * | 2022-09-06 | 2024-03-14 | 서울반도체 주식회사 | 발광장치 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20160225816A1 (en) | 2016-08-04 |

| US9337236B2 (en) | 2016-05-10 |

| EP2741338A1 (en) | 2014-06-11 |

| JP2014116604A (ja) | 2014-06-26 |

| EP2741338B1 (en) | 2020-05-20 |

| US9735199B2 (en) | 2017-08-15 |

| CN103855180B (zh) | 2019-11-05 |

| CN103855180A (zh) | 2014-06-11 |

| US20140159071A1 (en) | 2014-06-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2741338B1 (en) | Electrode structure for light-emitting diode array | |

| KR102087933B1 (ko) | 발광 소자 및 이를 포함하는 발광 소자 어레이 | |

| KR101888604B1 (ko) | 발광 소자 및 발광 소자 패키지 | |

| JP5414711B2 (ja) | 発光素子 | |

| KR101902392B1 (ko) | 발광 소자 | |

| KR102197082B1 (ko) | 발광 소자 및 이를 포함하는 발광소자 패키지 | |

| KR101871372B1 (ko) | 발광 소자 | |

| US9812626B2 (en) | Light emitting device | |

| US9837577B2 (en) | Light emitting device | |

| KR101830719B1 (ko) | 발광 소자 | |

| KR101827977B1 (ko) | 발광 소자 | |

| KR20140092037A (ko) | 발광 소자 패키지 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E90F | Notification of reason for final refusal | ||

| E601 | Decision to refuse application |