KR20110081318A - 방향성 박리를 사용한 반도체 온 절연체 구조를 생성하기 위한 방법 및 장치 - Google Patents

방향성 박리를 사용한 반도체 온 절연체 구조를 생성하기 위한 방법 및 장치 Download PDFInfo

- Publication number

- KR20110081318A KR20110081318A KR1020117012220A KR20117012220A KR20110081318A KR 20110081318 A KR20110081318 A KR 20110081318A KR 1020117012220 A KR1020117012220 A KR 1020117012220A KR 20117012220 A KR20117012220 A KR 20117012220A KR 20110081318 A KR20110081318 A KR 20110081318A

- Authority

- KR

- South Korea

- Prior art keywords

- semiconductor wafer

- weakened slice

- donor semiconductor

- ion implantation

- density

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 115

- 238000000034 method Methods 0.000 title claims abstract description 76

- 239000012212 insulator Substances 0.000 title claims abstract description 11

- 238000004299 exfoliation Methods 0.000 title claims description 13

- 238000005468 ion implantation Methods 0.000 claims abstract description 52

- 230000008859 change Effects 0.000 claims abstract description 30

- 238000000926 separation method Methods 0.000 claims description 64

- 238000010899 nucleation Methods 0.000 claims description 53

- 230000006911 nucleation Effects 0.000 claims description 53

- 239000001257 hydrogen Substances 0.000 claims description 30

- 229910052739 hydrogen Inorganic materials 0.000 claims description 30

- 238000002513 implantation Methods 0.000 claims description 28

- 239000007943 implant Substances 0.000 claims description 25

- 238000002347 injection Methods 0.000 claims description 22

- 239000007924 injection Substances 0.000 claims description 22

- 238000009826 distribution Methods 0.000 claims description 19

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 17

- 238000005553 drilling Methods 0.000 claims description 3

- 230000005012 migration Effects 0.000 claims description 3

- 238000013508 migration Methods 0.000 claims description 3

- 238000009827 uniform distribution Methods 0.000 claims description 3

- 239000001307 helium Substances 0.000 claims description 2

- 229910052734 helium Inorganic materials 0.000 claims description 2

- 230000000630 rising effect Effects 0.000 claims description 2

- 230000003028 elevating effect Effects 0.000 claims 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 claims 1

- 235000012431 wafers Nutrition 0.000 description 107

- 150000002500 ions Chemical class 0.000 description 49

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 20

- 229910052710 silicon Inorganic materials 0.000 description 20

- 239000010703 silicon Substances 0.000 description 20

- 230000008569 process Effects 0.000 description 16

- 239000000758 substrate Substances 0.000 description 16

- 230000006378 damage Effects 0.000 description 15

- 238000010884 ion-beam technique Methods 0.000 description 15

- -1 oxygen ions Chemical class 0.000 description 15

- 239000000463 material Substances 0.000 description 10

- 125000004429 atom Chemical group 0.000 description 9

- 239000011521 glass Substances 0.000 description 9

- 238000013459 approach Methods 0.000 description 8

- 239000007789 gas Substances 0.000 description 8

- 230000007547 defect Effects 0.000 description 7

- 238000003776 cleavage reaction Methods 0.000 description 6

- 230000007017 scission Effects 0.000 description 6

- YZCKVEUIGOORGS-UHFFFAOYSA-N Hydrogen atom Chemical compound [H] YZCKVEUIGOORGS-UHFFFAOYSA-N 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 230000005855 radiation Effects 0.000 description 5

- 230000008878 coupling Effects 0.000 description 4

- 238000010168 coupling process Methods 0.000 description 4

- 238000005859 coupling reaction Methods 0.000 description 4

- 239000012634 fragment Substances 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- 150000002431 hydrogen Chemical class 0.000 description 4

- 238000011065 in-situ storage Methods 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 230000005465 channeling Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 239000010408 film Substances 0.000 description 3

- 239000002241 glass-ceramic Substances 0.000 description 3

- GPRLSGONYQIRFK-UHFFFAOYSA-N hydron Chemical compound [H+] GPRLSGONYQIRFK-UHFFFAOYSA-N 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 239000007787 solid Substances 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 239000004205 dimethyl polysiloxane Substances 0.000 description 2

- 230000000873 masking effect Effects 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 238000009828 non-uniform distribution Methods 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229920000435 poly(dimethylsiloxane) Polymers 0.000 description 2

- 239000006096 absorbing agent Substances 0.000 description 1

- 238000004026 adhesive bonding Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 238000003486 chemical etching Methods 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000001802 infusion Methods 0.000 description 1

- 230000000977 initiatory effect Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 229920000620 organic polymer Polymers 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 238000003631 wet chemical etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/782—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, each consisting of a single circuit element

- H01L21/786—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, each consisting of a single circuit element the substrate being other than a semiconductor body, e.g. insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Element Separation (AREA)

- Physical Vapour Deposition (AREA)

- Recrystallisation Techniques (AREA)

Abstract

본 발명은 상기 도너 반도체 웨이퍼의 주입 표면에 이온 주입 단계를 실시하여 상기 도너 반도체 웨이퍼의 박리층을 한정하는 단면에 약화된 슬라이스를 형성하는 단계; 및 상기 이온 주입 단계 전에, 중에 또는 그 후에, 상기 도너 반도체 웨이퍼에 공간 변화 단계를 실시하여 상기 약화된 슬라이스의 적어도 하나의 변수가 X- 및 Y-축 방향 중 적어도 한 방향에서 상기 약화된 슬라이스 전체에서 공간적으로 변화하는 단계를 포함하는 반도체-온-절연체(SOI) 구조를 형성하는 방법 및 장치를 제공한다.

Description

관련 출원 상호 참조

본 출원은 2008년 10월 30일에 출원된 미국 출원 12/290,362 및 2008년 10월 30일에 출원된 미국 출원 12/290,384에 대한 우선권의 이익을 주장하고, 그 내용을 참조로 포함한다.

기술분야

본 발명은 반도체-온-절연체(SOI) 구조, 예를 들면 비-원형(non-circular) 단면을 갖는 구조 및/또는 비교적 큰 단면적을 갖는 구조의 제조에 관한 것이다.

반도체-온-절연체 디바이스는 시장 요구가 계속 늘어남에 따라서 점점 더 요구되고 있다. SOI 방법은 고성능 박막 트랜지스터(TFT), 태양전지 및 디스플레이, 예를 들면 활성 매트릭스 디스플레이, 유기 발광 다이오드(OLED) 디스플레이, 액정 디스플레이(LCD), 집적 회로, 광발전 디바이스, 등에서 점점 더 중요해 지고 있다. SOI 구조는 절연 물질 상에 박층 반도체 물질, 예를 들면 실리콘을 포함할 수 있다.

SOI 구조를 얻는 다양한 방법은 격자 정합 기판 상에 실리콘(Si)의 에피택셜 성장 및 또 다른 실리콘 웨이퍼에 단결정 실리콘 웨이퍼의 결합을 포함한다. 또 다른 방법은 수소 또는 산소 이온 중의 하나를 주입하여 산소 이온 주입의 경우에 Si가 상부에 위치하는 실리콘 웨이퍼 내에 매장된 산화물층을 형성하거나, 수소 이온 주입의 경우에서와 같이 얇은 Si층을 분리(박리)하여 산화물층을 갖는 또 다른 Si 웨이퍼에 결합시키는 이온 주입 방법을 포함한다.

미국 특허 7,176,528는 박리 방법을 사용한 SOG(반도체 온 유리) 구조를 제조하는 방법이 기재되어 있다. 이러한 단계는 (i) 실리콘 웨이퍼 표면을 수소 이온 주입에 노출하여 결합 표면을 형성하는 단계; (ii) 상기 웨이퍼의 결합 표면을 유리 기판과 접촉시키는 단계; (iii) 웨이퍼 및 유리 기판에 압력, 온도 및 전압을 인가하여 이들 사이에 결합을 용이하게 하는 단계; 및 (iv) 유리 기판 및 박층 실리콘을 실리콘 웨이퍼와 분리시키는 단계를 포함한다.

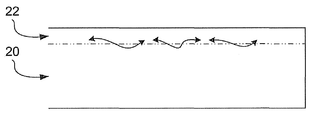

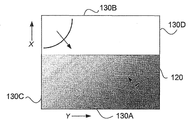

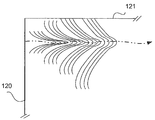

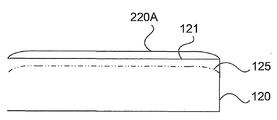

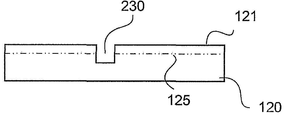

상기 접근방법은 어떠한 환경하에서 및/또는 특정한 적용에서 사용될 때, 바람직하지 않은 영향을 받기 쉽다. 도 1a-1d를 참조하면, 반도체 웨이퍼(20)는 이온 주입량이 반도체 웨이퍼(20) 전역에서 밀도 및 깊이에 대해서 균일하도록 표면(21)을 통해서 이온, 예를 들면 수소 이온을 주입한다.

도 1a를 참조하면, 반도체 물질, 예를 들면 실리콘은 이온, 예를 들면 H이온을 주입하면 손상 부위가 형성된다. 손상 부위의 층은 박리층(22)을 한정하는다. 이들 손상 부위의 일부는 매우 높은 가로세로비를 갖는 단편(platelet)을 핵으로 한다(이들은 매우 큰 효과적인 직경 및 거의 없는 높이를 갖는다). 주입된 이온, 예를 들면 H2에 기인하는 기체는 단편으로 확산하여 상당히 높은 가로세로비의 기포를 형성한다. 이들 기포내에서 기체 압력은 매우 높아서 약 10 kbar만큼 높게 된다고 추정되었다.

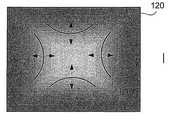

도 1b에서 양방향 화살표로 도시된 바와 같이, 단편 또는 기포는 이들이 서로 충분히 가깝게 될 때까지 효과적인 직경으로 성장하여 잔류하는 실리콘이 너무 약해져서 기체의 고압을 견딜 수 없다. 분리 면의 시작에 대한 바람직한 점은 없기 때문에, 다수의 분리 면은 랜덤하게 형성되고 다수의 균열은 반도체 웨이퍼(20)를 통해서 확장한다.

반도체 웨이퍼(20)의 에지 근방에서 더 큰 주입된 수소 부분은 수소-리치 면으로부터 탈출할 수 있다. 이것은 싱크의 주변(즉, 웨이퍼(20)의 측벽)이기 때문이다. 보다 구체적으로, 주입동안, 이온(예를 들면 수소 양자)은 반도체 웨이퍼(20)(예를 들면 실리콘)의 격자 구조를 통해서 감소하고 이들의 격자점으로부터 일부의 실리콘 원자를 제거하여 결함 면을 형성할 수 있다. 수소 이온이 그 운동에너지를 잃기 때문에, 이들은 원자상 수소가 되고 더욱 원자상 수소면을 한정하는다. 결함 면 및 원자상 수소 면은 실온에서 실리콘 격자에서 안정하지 않다. 따라서, 결함(빈격자점) 및 원자상 수소는 서로를 향해서 이동하고 열적으로 안정한 빈격자-수소종을 형성한다. 다수의 종은 집단으로 수소-리치 면을 형성한다(가열시에 실리콘 격자는 일반적으로 수소-리치 면을 따라서 쪼개진다).

모든 빈격자 및 수소가 수소-빈격자 종으로 붕괴하는 것은 아니다. 일부 원자의 수소종은 빈격자면으로부터 멀리 확산되고 결국 실리콘 웨이퍼(20)를 탈출한다. 따라서, 일부 원자상 수소는 박리층(22)의 쪼개짐에 기여하지 않는다. 실리콘 웨이퍼(20)의 에지 근방에서 수소 원자는 격자로부터 탈출하기 위한 추가의 통로를 갖는다. 따라서, 실리콘 웨이퍼(20)의 에지 영역은 수소 농도가 감소될 수 있다. 수소 농도의 감소는 분리를 지지하기 위한 충분한 힘을 개발하기 위해서 더 높은 온도 또는 더 긴 시간을 필요로 한다.

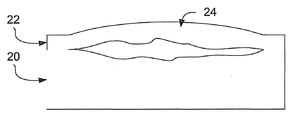

따라서, 분리 공정 동안, 텐트형 구조(24)는 분리되지 않은 에지에 의해서 형성된다. 중심 압력에서, 잔류하는 반도체 물질의 균열은 비교적 약한 면, 예를 들면 {111}면을 따라서 발생하고(도 1c), 반도체 웨이퍼(20)로부터 박리층(22)의 분리가 종료한다(도 1d). 그러나, 에지(22A, 22B)는 손상 부위로 한정된 주요한 쪼개짐 면을 벗어나 있다. 이러한 비-평면 쪼개짐(non-planar cleavage)은 바람직하지 않다. 그외의 분리 특징은, 박리층(22)이 단편 또는 기포가 균열이 발생한 "협곡(canyons)"에 의해 둘러싸인 "메사(mesas)"를 갖는 것으로 기재되어 있는 것을 포함한다. 이들 메사 및 협곡은 이러한 상세도가 도시된 비율에서 재생가능하지 않기 때문에, 도 1d에 정확하게 도시되어 있지 않은 것을 유의한다.

본 발명은 임의의 조작 이론으로 한정되지 않고, 본 출원의 발명자는 분리 시작으로부터 분리가 완료될 때까지의 시간이 상술한 방법을 사용하여 약 수십 마이크로초인 것으로 생각한다. 즉, 분리의 랜덤한 시작 및 확장은 약 3000m/sec이다. 다시, 본 발명은 임의의 조작 이론에 한정되지 않고, 본 출원 발명자는 이러한 분리 속도가 상기 기재된 박리층(22)의 쪼개진 표면의 바람직하지 않은 특성에 기여한다고 생각한다(도 1d).

미국 출원 6,010,579는 "제어된 쪼개짐 면"를 달성하기 위해서, 웨이퍼를, 분리 시작 후 다수의 임펄스 에너지를 주입 깊이 Z0 근방에서 기판(10)의 에지에 도입하는 온도 미만으로 설정한 반도체 기판(10) 내의 균일한 깊이 Z0까지 균일한 이온을 주입하는 방법을 기재한다. 미국 6,010,579는 상기 접근 방법이 표면 조도(surface roughness)에 대해서 소위 "랜덤" 쪼개짐에 대한 개선인 것으로 기재되어 있다. 본 발명은 미국 6,010,579의 "제어된 쪼개짐 면" 접근 방법과 상당히 다르고 "랜덤" 분열 접근 방법과 다른 방향성 분리 접근방법을 취한다.

상술한 반도체 웨이퍼(20)로부터 박리층(22)의 분리에 관련된 도전은 SOI 구조의 크기가 증가함에 따라서, 특히 반도체 웨이퍼의 형상이 직사각형일 때 악화된다. 이러한 직사각형 반도체 웨이퍼는 다수의 반도체 타일이 절연체 기판에 결합된 적용에 사용될 수 있다. 또한, 타일 SOI 구조의 제조에 대한 세부사항은 미국 출원 공개 2007/0117354에 기재되어 있고, 그 내용은 참조로 포함된다.

프리젠테이션을 용이하게 하기 위해서, 하기에 SOI 구조에 대해서 때때로 검토될 것이다. 이러한 특별한 SOI 구조의 형태는 본 발명의 설명을 용이하게 위해서 참조되고 본 발명의 범위를 한정하는 것으로 해석되지 않는다. 본원에서 SOI 약기는 일반적으로 실리콘-온-절연체 구조를 포함하지만 이들로 한정되지 않는 반도체-온-절연체 구조를 칭하는 것으로 사용된다. 유사하게, SOG 약기는 일반적으로 실리콘-온-유리 구조를 포함하지만 이들로 한정되지 않는 반도체-온-유리 구조를 칭하는 것으로 사용된다. SOI 약기는 SOG 구조를 포함한다.

본 발명의 하나 이상의 실시형태에 따라서, 반도체-온-절연체(SOI) 구조를 형성하는 데에 사용되는 방법 및 장치는: 도너 반도체 웨이퍼의 주입 표면에 이온 주입 단계를 실시하여 상기 도너 반도체 웨이퍼의 박리층을 한정하는 단면에 약화된 슬라이스를 형성하는 단계; 및 상기 이온 주입 단계 전에, 중에 또는 그 후에, 상기 도너 반도체 웨이퍼에 공간 변화 단계를 실시하여 상기 약화된 슬라이스의 하나 이상의 변수가 X- 및 Y-축 방향 중 적어도 한 방향에서 웨이퍼 전체에서 공간적으로 변화하는 단계를 포함한다.

상기 공간 변화 단계는 이러한 분리가 방향성 있게 및/또는 일시적으로 제어 가능하도록 도너 반도체 웨이퍼로부터 박리층의 분리 특성을 용이하게 한다.

상기 변수는 하기의 하나 이상을 단독으로 또는 조합하여 포함할 수 있다: (i) 이온 주입 단계에 기인하는 핵형성 부위의 밀도; (ii) 주입 표면(또는 기준면)으로부터 약화된 슬라이스의 깊이; (iii) 상기 약화된 슬라이스까지 적어도 주입 표면을 통해서 인공적으로 형성된 손상 위치(예를 들면 블라인드 홀); 및 (iv) 온도 구배를 사용한 약화된 슬라이스 전체에 결함 부위의 핵형성 및/또는 압력 증가.

상기 방법 및 장치는 상기 약화된 슬라이스의 점, 에지(edge) 및/또는 영역으로부터 약화된 슬라이스에서 분리를 시작하는 데에 충분한 온도까지 도너 반도체 웨이퍼를 상승시키는 단계를 제공한다. 상기 도너 반도체 웨이퍼는 다양한 변수의 함수로서 방향성 있게 약화된 슬라이스를 따라서 실질적으로 분리를 지속하는 데에 충분한 온도에서 실시할 수 있다.

그외의 형태, 특징, 이점 등은 수반한 도면과 함께 본 발명을 설명하는 경우 당업자에게 명백하게 될 것이다.

본 발명은 상기 도너 반도체 웨이퍼의 주입 표면에 이온 주입 단계를 실시하여 상기 도너 반도체 웨이퍼의 박리층을 한정하는 단면에 약화된 슬라이스를 형성하는 단계; 및 상기 이온 주입 단계 전에, 중에 또는 그 후에, 상기 도너 반도체 웨이퍼에 공간 변화 단계를 실시하여 상기 약화된 슬라이스의 적어도 하나의 변수가 X- 및 Y-축 방향 중 적어도 한 방향에서 상기 약화된 슬라이스 전체에서 공간적으로 변화하는 단계를 포함하는 반도체-온-절연체(SOI) 구조를 형성하는 방법 및 장치를 제공한다.

본 발명의 다양한 형태를 설명하기 위해서, 바람직한 형태가 도면에 도시되어 있지만, 본 발명은 도시된 정확한 배열 및 기기로 한정되지 않는 것으로 이해된다.

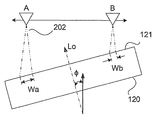

도 1a, 1b, 1c, 및 1d는 종래 기술에 따른 박리 공정을 설명하는 블록도이다.

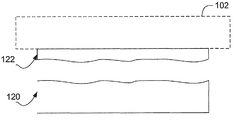

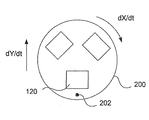

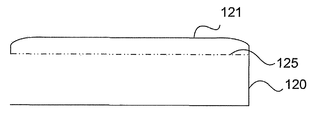

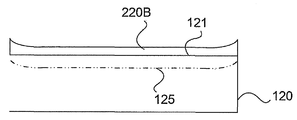

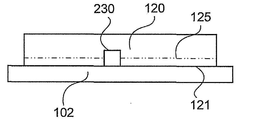

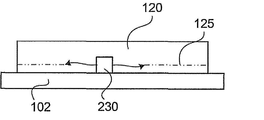

도 2a-2b는 본 발명의 하나 이상의 형태에 따라서 박리 공정을 설명하는 블록도이다.

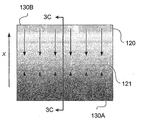

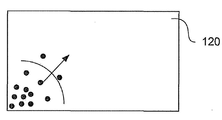

도 3a는 본 발명의 하나 이상의 형태에 따라서 약화된 층 또는 그 안에 슬라이스에 따른 공간적으로 변화하는 변수를 갖는 도너 반도체 웨이퍼의 상면도이다.

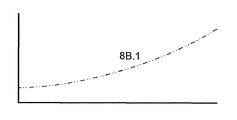

도 3b는 도 3a의 공간적으로 변화하는 변수를 그래프적으로 설명한 플롯이다.

도 3c는 도 3a의 공간적으로 변화하는 변수가 약화된 슬라이스의 깊이인 것을 그래프적으로 설명하는 플롯이다.

도 4a, 4b 및 4c는 본 발명의 하나 이상의 형태에 따른 공간적으로 변화하는 변수를 갖는 각각의 도너 반도체 웨이퍼의 상면도이다.

도 5a, 5b 및 5c는 도너 반도체 웨이퍼의 공간적으로 변화하는 변수를 얻는 데에 적당한 일부 이온 주입 장치의 개략도이다.

도 6a-6b는 도너 반도체 웨이퍼에서 핵형성 부위의 공간적으로 변화하는 밀도를 달성하는 데에 적당한 이온 주입 방법을 설명한다.

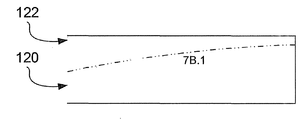

도 7a-7b는 도너 반도체 웨이퍼에서 공간적으로 변화하는 주입 깊이를 달성하는 데에 적당한 이온 주입 방법을 설명한다.

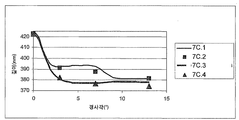

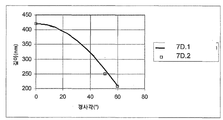

도 7c-7d는 이온 주입물의 경사각 및 주입 깊이 사이의 관계를 도시한 그래프이다.

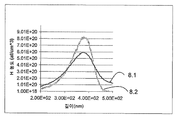

도 8a-8b는 도너 반도체 웨이퍼에서 공간적으로 변화하는 이온 주입 분포 폭을 달성하는 데에 적당한 이온 주입 방법을 설명한다.

도 8c는 이온 주입물의 경사각과 스트래글(straggle) 사이의 관계를 설명하는 그래프이다.

도 9a-9d는 도너 반도체 웨이퍼에서 공간적으로 변화하는 이온 주입 깊이를 달성하는 데에 적당한 이온 주입 방법을 설명한다.

도 10a-10d 및 11는 도너 반도체 웨이퍼에서 결함 부위의 공간적으로 변화하는 분포를 달성하는 데에 적당한 이온 주입 방법을 설명한다.

도 12a-12b는 도너 반도체 웨이퍼에서 공간적으로 변화하는 변수 프로파일을 달성하는 데에 적당한 시간-온도 프로파일 방법을 설명한다.

도 1a, 1b, 1c, 및 1d는 종래 기술에 따른 박리 공정을 설명하는 블록도이다.

도 2a-2b는 본 발명의 하나 이상의 형태에 따라서 박리 공정을 설명하는 블록도이다.

도 3a는 본 발명의 하나 이상의 형태에 따라서 약화된 층 또는 그 안에 슬라이스에 따른 공간적으로 변화하는 변수를 갖는 도너 반도체 웨이퍼의 상면도이다.

도 3b는 도 3a의 공간적으로 변화하는 변수를 그래프적으로 설명한 플롯이다.

도 3c는 도 3a의 공간적으로 변화하는 변수가 약화된 슬라이스의 깊이인 것을 그래프적으로 설명하는 플롯이다.

도 4a, 4b 및 4c는 본 발명의 하나 이상의 형태에 따른 공간적으로 변화하는 변수를 갖는 각각의 도너 반도체 웨이퍼의 상면도이다.

도 5a, 5b 및 5c는 도너 반도체 웨이퍼의 공간적으로 변화하는 변수를 얻는 데에 적당한 일부 이온 주입 장치의 개략도이다.

도 6a-6b는 도너 반도체 웨이퍼에서 핵형성 부위의 공간적으로 변화하는 밀도를 달성하는 데에 적당한 이온 주입 방법을 설명한다.

도 7a-7b는 도너 반도체 웨이퍼에서 공간적으로 변화하는 주입 깊이를 달성하는 데에 적당한 이온 주입 방법을 설명한다.

도 7c-7d는 이온 주입물의 경사각 및 주입 깊이 사이의 관계를 도시한 그래프이다.

도 8a-8b는 도너 반도체 웨이퍼에서 공간적으로 변화하는 이온 주입 분포 폭을 달성하는 데에 적당한 이온 주입 방법을 설명한다.

도 8c는 이온 주입물의 경사각과 스트래글(straggle) 사이의 관계를 설명하는 그래프이다.

도 9a-9d는 도너 반도체 웨이퍼에서 공간적으로 변화하는 이온 주입 깊이를 달성하는 데에 적당한 이온 주입 방법을 설명한다.

도 10a-10d 및 11는 도너 반도체 웨이퍼에서 결함 부위의 공간적으로 변화하는 분포를 달성하는 데에 적당한 이온 주입 방법을 설명한다.

도 12a-12b는 도너 반도체 웨이퍼에서 공간적으로 변화하는 변수 프로파일을 달성하는 데에 적당한 시간-온도 프로파일 방법을 설명한다.

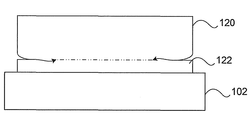

도면을 참조하면, 동일한 부호는 동일한 요소를 나타내고, 도 2a-2b에서 본 발명의 하나 이상의 실시형태에 따른 중간의 SOI 구조(특히, SOG 구조)를 도시한다. 중간의 SOG구조는 절연체 기판, 예를 들면 유리 또는 유리 세라믹 기판(102) 및 도너 반도체 웨이퍼(120)를 포함한다. 유리 또는 유리 세라믹 기판(102) 및 도너 반도체 웨이퍼(120)는 해당 기술 분야에서 승인된 방법, 예를 들면 결합, 용융, 접착 등 중 어느 하나를 사용하여 함께 결합되었다.

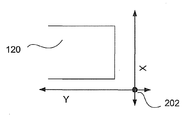

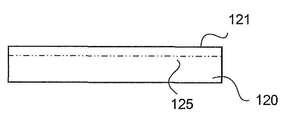

유리 또는 유리 세라믹 기판(102) 및 도너 반도체 웨이퍼(120)를 함께 결합하기 전에, 도너 반도체 웨이퍼(120)는 노출된 주입 표면(121)을 포함한다. 도너 반도체 웨이퍼(120)의 주입 표면(121)은 이온 주입 단계를 실시하여 박리층(122)을 한정하는 단면에서 약화된 슬라이스(125)를 형성한다. 약화된 슬라이스(125)는 X-Y 직교축 방향으로 한정된 기준면(어디에나 있으므로 설명하지 않는다)과 실질적으로 평행하다. X축 방향은 도 2a에서 왼쪽에서 오른쪽으로 도시하고, Y축 방향은 페이지의 X축 방향에 직교한다(따라서 도시하지 않는다).

도너 반도체 웨이퍼(120)는 이온 주입 단계 전, 중 또는 후에 공간 변화 단계를 실시하여 도너 반도체 웨이퍼(120)로부터 박리층(122)의 분리 특성이 방향성 있게 및/또는 일시적으로 제어가능하다. 본 발명은 임의의 조작 이론으로 한정되지 않지만, 이러한 방향성 및/또는 일시적 제어성은 분리 특성을 개선시키는, 예를 들면 박리층(122) 및 도너 반도체 웨이퍼(120)에 노출된 표면을 평탄하게 할 수 있는(후분리(post separation)) 것으로 생각된다. 이러한 방향성 및/또는 일시적 제어성은 에지 특성을 개선시키는, 예를 들면 약화된 슬라이스(125)로 한정된 주요한 쪼개짐 면에 있는 박리층(122) 및 도너 반도체 웨이퍼(120)에 노출된 표면의 에지의 양품률을 향상시킬 수 있다.

도너 반도체 웨이퍼(120)로부터 박리층(122)의 방향성 있게 및/또는 일시적으로 제어가능한 분리 특성은 다수의 방법, 예를 들면 X- 및 Y-축 방향 중 적어도 한 방향에서 약화된 슬라이스(125) 전역에서 하나 이상의 변수를 공간적으로 변화시킴으로써 달성될 수 있다. 변수는 하기의 하나 이상을 단독으로 또는 조합해서 포함할 수 있다: (i)이온 주입 단계에 기인하는 핵형성 부위의 밀도; (ii)주입 표면(121)으로부터 약화된 슬라이스(125)의 깊이(또는 기준면); (iii) 약화된 슬라이스(125) 까지 적어도 주입 표면(121)을 통해서 인공적으로 형성된 손상 위치(예를 들면, 블라인드 홀); 및 (iv) 온도 구배를 사용하는 약화된 슬라이스(125) 전체에 결함 부위의 핵형성 및/또는 압력 증가.

도 2a-2b에서 화살표 A로 도시된 바와 같이, 도너 반도체 웨이퍼(120)로부터 박리층(122)의 방향성 있게 및/또는 일시적으로 제어가능한 분리 특성은 시간의 함수로서 약화된 슬라이스(125)의 한 점, 에지, 및/또는 영역으로부터 그외의 점, 에지, 및/또는 영역까지 분리를 확장시킨다. 이것은 일반적으로 다음과 같이 달성된다: 첫번째로 상기 기재된 바와 같이 약화된 슬라이스(125)에서 공간적으로 하나 이상의 변수를 변화시키고, 두번째로 도너 반도체 웨이퍼(120)를 이러한 점, 에지 및/또는 영역으로부터 약화된 슬라이스(125)에서 분리를 시작하는 데에 충분한 온도까지 상승시킨다. 그 다음에, 도너 반도체 웨이퍼(120)는 약화된 슬라이스(125) 전역에서 변수의 공간 변화의 함수로서 방향성 있게 약화된 슬라이스(125)를 따라서 실질적으로 분리를 지속하는 데에 충분한 온도까지 상승시킨다. 다양한 변수는 상승하는 온도의 시간-온도 프로파일이 약 몇 초이고 약화된 슬라이스(125)를 따라서 분리의 확장이 적어도 1초에 걸쳐서 발생하도록 형성되는 것이 바람직하다.

도 3a-3c를 참조하여, 약화된 슬라이스(125) 전역에서 하나 이상의 변수를 공간적으로 변화시키는 데에 관련된 세부사항을 설명한다. 도 3a는 주입 표면(121)을 통해서 본 도너 반도체 웨이퍼(120)의 상면이다. X축 방향에서 음영의 변화는 상기 변수의 공간 변화를 나타낸다(예를 들면, 핵형성 부위의 밀도, 그 부위내에서 압력, 핵형성 정도, 인공적으로 형성된 손상 부위(홀)의 분포, 주입 깊이, 등). 설명된 예에서, 하나 이상의 변수는 도너 반도체 웨이퍼(120), (따라서 그 약화된 슬라이스(125))의 대면하는 에지(130B)를 향해서 X축 방향에서 또는 그 반대 방향에서 하나의 에지(130A)를 변화시킨다.

도 3b를 참조하면, 분리 변수의 그래프는 단면 프로파일, 예를 들면 X축 방향의 함수로서 약화된 슬라이스(125) 내에 핵형성 부위의 밀도의 단면 프로파일을 설명한다. 또한, 분리 변수는 X축, 공간 메트릭스의 함수로서 핵형성 부위 내의 압력, 핵형성 정도, 인공적으로 형성된 손상 부위(홀)의 분포 중의 하나 이상을 나타낼 수 있다. 도 3c을 참조하면, 분리 변수의 그래프는 단면 프로파일, 예를 들면 X축 방향의 함수로서 약화된 슬라이스(125)의 깊이(예를 들면, 이온 주입 깊이에 상응하는)의 단면 프로파일을 설명한다.

본 발명은 임의의 조작 이론에 의해서 한정되는 것을 의도하지 않지만, 핵형성 부위의 밀도가 에지(130A)에서 비교적 높고 에지(130B)를 향해서 공간 위치에서 핵형성 부위가 더 낮은 밀도로 저감될 때, 에지(130A)로부터 에지(130B)를 향해서 분리 확장(파선 화살표로 표시)이 발생한다고 생각된다. 이 이론은 그외의 변수,예를 들면 핵형성 부위내에서 기체 압력, 분리 전에 핵형성 부위를 합병하는 정도, 및 인공적으로 형성된 손상 부위(홀)의 분포와 관련해서 유지된다고 생각된다. 그러나, 약화된 슬라이스(125)의 깊이에 관련된 변수에 대해서 실질적으로 낮은 깊이가 약화된 슬라이스(125)의 초기의 에지(130B)를 따라서 존재하고 비교적 높은 깊이가 에지(130A)를 향해서 연속적으로 더욱 먼 거리에서 존재할 때, 에지(130B)로부터 에지(130A)를 향해서 분리의 확장(실선 화살표로 도시)은 발생한다고 생각된다.

도 4a-4c를 참조하여, 약화된 슬라이스(125) 전역에서 하나 이상의 변수를 공간적으로 변화하는 것에 관련된 보다 세부사항을 설명한다. 도면은 주입 표면(121)을 통해서 본 도너 반도체 웨이퍼(120)의 상면도를 도시한다. X- 및 Y-축 방향에서 음영의 변화는 상기 변수의 공간 변화, 다시 핵형성 부위의 밀도, 그 부위 내의 압력, 핵형성 정도, 인공적으로 형성된 손상 부위(홀)의 분포, 주입 깊이 등을 나타낸다. 각각 설명된 경우에서, 변수는 X 및 Y축 방향에서 공간적으로 변화된다.

도 4a를 참조하면, 음영은 상기 변수가 2개의 에지(130A, 130D)로부터 그외의 에지(130B, 130C)를 향해서 공간적으로 변화하고 X 및 Y축 방향에서 연속적으로 더욱 먼 거리로 변화한다. 상기의 검토를 유지하면서, 핵형성 부위의 밀도의 변수를 고려하는 경우, 더 높은 밀도가 에지(130A, 130D)에서 시작하면, 분리의 확장(파선 화살표로 도시)는 에지(130A, 130D)의 코너로부터 웨이퍼(120)의 중심 및 그외의 에지(130B, 130C)를 향해서 방사상으로 퍼지는 것으로 생각된다. 이 이론은 그외의 변수, 예를 들면 핵형성 부위내에서 기체 압력, 분리 전에 핵형성 부위의 합병 정도, 및 인공적으로 형성된 손상 부위(홀)의 분포와 연관해서 유지된다고 생각된다. 그러나, 약화된 슬라이스(125)의 깊이에 관련된 변수에 대해서, 분리의 확장(실선 화살표로 도시)은 더 낮은 깊이가 에지(130B, 130C)를 따라서 시작되는 경우, 에지(130B, 130C)의 코너로부터 웨이퍼(120)의 중심 및 그외의 에지(130A, 130D)를 향해서 방사상으로 퍼지는 것으로 생각된다.

도 4B 및 4C를 참조하면, 음영은 변수가 모든 에지(130)로부터 도너 반도체 웨이퍼(120)의 중심을 향해서 또는 그 반대로 공간적으로 변화하는 것을 나타낼 수 있다.

또한, X 및 Y축 중 한 방향 또는 양방향에서 약화된 슬라이스(125) 전체에서 이온 주입에 기인하는 핵형성 부위의 밀도를 공간적으로 변화시키는 특별한 변수에 대한 세부사항을 제공할 것이다. 이러한 공간 변화를 달성하기 위해서 어떠한 방법을 사용하더라도, 핵형성 부위의 최대 밀도는 약 5x105 sites/㎠ 의 약화된 슬라이스(125)의 하나 이상의 에지, 점 또는 영역에서 존재하는 것이 바람직하고 핵형성 부위의 최소 밀도는 약5x104 sites/㎠ 의 약화된 슬라이스(125)에서 이들로부터 떨어져서 존재한다. 또 다른 방법에서 변화를 보면, 핵형성 부위의 최대 밀도 및 핵형성 부위의 최소 밀도 사이의 차이는 약 10배일 수 있다.

본 발명의 하나 이상의 형태에 따라서, 약화된 슬라이스(125) 내에 핵형성 부위의 밀도는 이온 주입 단계의 주입량을 변화시킴으로써 공간적으로 변화될 수 있다. 배경기술로서, 약화된 슬라이스(125)(따라서 박리층(122))는 주입 표면(121)에 하나 이상의 이온 주입 단계를 실시함으로써 형성된다. 이러한 점에서 사용될 수 있는 수많은 이온 주입 방법, 기기 등이 있지만, 하나의 적당한 방법은 도너 반도체 웨이퍼(120)의 주입 표면(121)에 수소 이온 주입 단계를 실시하여 적어도 도너 반도체 웨이퍼(120)내의 박리층(122)의 형성을 시작하는 것을 포함한다.

도 5a를 참조하여, Axcelis NV-10 타입 배치 주입기의 개략도가 설명되고, 이것은 이온 주입량을 변화시킴으로써 약화된 슬라이스(125) 내에서 핵형성 부위의 밀도를 공간적으로 변화시키는데 사용하기 위해서 변경될 수 있다.

다수의 도너 반도체 웨이퍼(120), 이러한 경우에 직사각형 타일은 입사 이온 빔(202)(페이지로 향하는)에 대해서 플라텐(platen)(200) 상에 고정 반경에서 방위각으로 분포될 수 있다. 플라텐(200)의 회전은 슈도 X 스캔(dX/dt)를 제공하는 반면, 전체의 플라텐(200)의 기계적 이동은 Y 스캔(dY/dt)을 제공한다. 작은 반경의 플라텐(200)은 더 큰 반경의 플라텐(200)에 비해서 X 스캔이 약간 더 구부러져 있으므로 이러한 회전 플라텐(200) 상에 직선의 스캔이 바람직하게 얻어지지 않기 때문에 슈도 X스캔이 사용된다. X스캔 속도 및/또는 Y 스캔 속도를 변경하는 것은 주입량의 공간 변화를 일으킬 것이다. 종래에 이온 빔(202)이 플라텐(200)의 중심을 향해서 방사상으로 이동할 때 Y 스캔 속도를 증가시키는 것은 균일한 주입량을 확보하기 위해서 사용되었다. 즉, 종래의 사고는 공간적으로 균일한 주입량을 달성하고 도너 반도체 웨이퍼(120)에 대한 각속도가 플라텐(200)의 중심에 가까울수록 감소되기 때문에, Y 스캔 속도가 상응해서 증가되어야만 한다. 그러나, 본 발명에 따르면, 공간적으로 변화하는 주입량은 종래의 스캔 프로토콜을 따르지 않고 예를 들면 도 3a 및 4a의 패턴을 일으킴으로써 달성될 수 있다. 예를 들면, 이온 빔(202)이 플라텐(200)의 중심을 향해서 방사상으로 이동할 때 Y스캔 속도가 균일하게 된다. 또한, 이것은 이온 빔(202)이 플라텐(200)의 중심을 향해서 방사상으로 이동할 때 Y 스캔 속도를 감소시킬 수 있다. 당업자는 본원에 기재된 것으로부터 그외의 가능성을 인지할 것이다. 또 다른 접근 방법은 스캔 속도 및 위치의 함수로서 빔 에너지를 변화시키는 것이다. 이들 변화는 소프트웨어에서 주입기의 제어 알고리즘에 대한 변경, 제어 소프트웨어와 말단 스테이션 드라이브 사이에서 전자 계면, 또는 그외의 기계적인 변경을 통해서 영향을 받을 수 있다.

도 5b를 참조하여, 하나의 기판 X-Y 주입기의 개략도를 설명하고, 이러한 주입기는 이온의 주입량을 변화시킴으로써 약화된 슬라이스(125) 내에 핵형성 부위의 밀도를 공간적으로 변화시키는 데에 사용하기 위해서 변경될 수 있다. 이 경우에, 전자 빔(202)은 (도 5a)의 기계적 기판 스캔보다 훨씬 빠르게 스캔된다. 다시, 종래의 사고는 공간적으로 균일한 주입량을 달성하는 것이므로 X 및 Y 스캔 속도 및 빔 에너지는 균일한 주입량이 달성되도록 설정된다. 다시, 공간적으로 변화하는 주입량은 종래의 스캔 프로토콜을 따르지 않고 달성될 수 있다. 주입량에서 상당한 공간 변화는 가변 X 및 Y 스캔 속도 및/또는 빔 에너지의 수많은 조합을 통해서 달성될 수 있다. 1차원 또는 2차원 구배는 도 3a, 4a, 4b 및 4c의 패턴을 일으키는 이러한 변화를 통해서 수직 또는 수평으로 생성될 수 있다.

도 5c를 참조하여, 주입기의 개략적인 도면을 이온 샤워 방법에 따라서 설명한다. 리본 빔(204)은 확장된 이온 소스에 기인한다. 종래의 방법에 따라서, 하나의 균일한 속도 스캔(직교 방향에서 균일한 빔에너지에 비례)는 종래의 이상적인, 즉 공간적으로 균일한 주입량을 달성할 수 있다. 그러나, 본 발명의 다양한 형태에 따라서, 1차원 구배(예를 들면, 도 3a가 90°회전된 것)는 리본 빔(204)을 통해서 도너 반도체 웨이퍼(120)의 기계적 스캔 속도의 변화를 통해서 생성될 수 있다. 기계적 스캔 속도의 변화와 함께 리본 빔(204)에 대해서 약간의 각도로 도너 반도체 웨이퍼(120)를 트위스트한 것은 도 4a의 것과 유사한 방법으로 주입량의 공간적인 변화를 생성할 수 있다. 또한, 빔 소스에 따라서 공간적으로 변화하는 빔 전류는 스캔 방향에 직교하는 구배를 제공하고 추가의 자유도를 제공하여 공간적으로 변화하는 주입량을 생성할 것이다.

주입량의 변화를 달성하기 위해서 사용되는 특별한 주입 방법에 관계없이, 및 가장 높은 주입량의 위치에 관계없이 (예를 들면, 하나 이상의 초기 에지, 초기 점 또는 초기의 영역에 따라서), 실질적으로 가장 높은 주입량은 단위 atoms/㎠의 소망의 범위 내에 있고 X 및 Y축 방향 중 적어도 한 방향에서 이들로부터 가장 낮은 주입량은 단위 atoms/㎠의 그외의 소망의 범위 내에 있다. 최대 주입량과 최소 주입량의 차이는 약 3개의 요소의 최대 변화와 함께 약 10-30% 사이일 수 있다. 일부 적용에서, 적어도 약 20%의 차이가 중요하다는 것을 알 수 있었다.

본 발명의 하나 이상의 형태에 따라서, 약화된 슬라이스(125) 내에 핵형성 부위의 밀도는 제 1 이온 종을 실질적으로 균일하게 주입함으로써 공간적으로 변화시켜서 실질적으로 균일한 분포를 갖는 약화된 슬라이스(125)를 형성할 수 있다. 그 다음에, 도너 반도체 웨이퍼(120)는 제 2 이온 종을 실질적으로 비균일하게 주입할 수 있다. 비균일 주입은 제 2 이온 종이 약화된 슬라이스(125)로 원자의 이동을 일으키고 약화된 슬라이스(125) 전역에 핵형성 부위의 공간적으로 변화하는 밀도가 발생하도록 한다.

일례로서, 제 1 이온 종은 수소 이온이고 제 2 이온 종은 헬륨 이온일 수 있다.

비균일 주입은 상기 기재된 방법, 후술된 방법 또는 다른 문헌에서 수집된 방법을 사용하여 발생할 수 있다. 예를 들면, 제 2 이온 종의 주입량은 공간적으로 변화될 수 있다. 제 2 이온 종(예를 들면 He 이온)의 주입량의 변화는 제 1 종의 위치로 제 2 종의 비균일 이동을 일으킴으로써 핵형성 부위의 비균일 밀도를 형성할 것이다. 이 변화는 단편의 압력을 변화시킬 가능성이 있고, 이것은 유리하게 될 수 있다.

또한, 제 2 이온 종의 비균일 주입은 도너 반도체 웨이퍼(120) 전역에 공간적으로 변화하는 깊이에 제 2 이온 종을 주입하는 것을 포함할 수 있다. 균일한 깊이에 이온을 주입하는 임의의 공지된 방법은 본원의 방법에 따라서 당업자에 의해서 변경되어 비균일 깊이 프로파일을 달성할 수 있다. 배경기술로서, He 이온은 H 보다 예를 들면 2배 이상 깊게 주입될 수 있다. 웨이퍼 온도가 증가함에 따라서, 많은 He 이온이 더 얕은 H 이온 주입물의 자리로 이동하고 후분리(later separation)를 위한 기체 압력을 제공할 것이다. 본 발명의 형태에 따르면, 더 깊게 매장된 He에 의한 손상은 더 얕은 H 이온 주입물로부터 먼 도너 반도체 웨이퍼(120)의 깊이에 위치되고, 적은 He 이온은 소정 시간 동안 상기 웨이퍼에 도달할 것이다. 반대편은 덜 깊게 주입된 He 이온이 약화된 슬라이스(125) 전역에서 핵형성 부위의 공간적으로 변화하는 밀도를 일으키는 것이 사실이다.

이론적으로, 핵형성 부위의 공간적으로 변화된 밀도는 제 1 및 제 2 이온 종(예를 들면, 처음 주입된 He 또는 처음 주입된 H)의 순서에 관계없이 달성될 수 있지만, 다수의 이온 주입 단계의 순서는 원하는 결과에 기여할 수 있다. 즉, 이온 종에 따른 주입의 순서는 밀도가 공간적으로 변화하기 때문에 밀도에 전체적인 영향을 줄 수 있다. 많은 당업자에게 반직관적이고 놀랍게도, 처음 주입된 H가 많은 핵형성 부위를 형성하는 것을 알 수 있었다. 소정의 주입량에 대해서, 당업자는 He이 H이온에 비해서 약 10배 정도의 손상을 일으키는 것을 인지한다. 그러나, He이온에 의해 생성된 손상(빈격자 및 격자간 반도체 원자 또는 프랜켈 쌍(Frankel pair)은 스스로 실온에서도 격하게 어닐링하는 것을 유의할 필요가 있다. 따라서, 모두는 아니지만 많은 He 손상이 회복된다. 한편, H 이온은 반도체 원자, 예를 들면 Si 원자와 결합하고(Si-H 결합을 형성), 형성된 손상을 안정화시킨다. He이 주입되기 전에 H가 존재하면 많은 핵형성 부위가 형성된다.

도 6a-6b를 참조하면, 핵형성 부위의 밀도의 공간 변화를 달성하는 데에 적당한 많은 예가 설명된다. 이러한 예에서, 도 6a에 도시된 바와 같이, 핵형성 부위의 밀도의 공간 변화는 이온 주입 단계 중에 이온 빔의 빔각도를 조절함으로써 달성된다. 빔각도가 많은 방법에 의해 조절될 수 있지만, 이러한 접근 방법은 도 6a에 도시된 바와 같이 이온 빔(예를 들면, 도트 빔(202))에 대해서 도너 반도체 웨이퍼(120)를 경사지게 하는 것이다. 도너 반도체 웨이퍼(120)는 폭(페이지에 도시된 왼쪽에서 오른쪽), 깊이(페이지내의) 및 높이(페이지에 도시된 상부에서 하부)를 갖는다. 폭 및 깊이는 X 및 Y 축 방향을 정의하고 높이는 주입 표면(121)에 수직인 장축 Lo을 정의할 수 있다. 도너 반도체 웨이퍼(120)는 장축 Lo가 이온 주입 단계 중에 이온 주입빔의 방향축(실선 화살표로 표시)에 대해서 각도 Φ에 있도록 경사지게 한다. 각도 Φ는 약 1 내지 45°사이일 수 있다.

경사 조건 하에서, 빔소스가 위치 A로부터 위치 B까지 스캔될 때, 빔(202)의 폭 W는 폭 Wa로부터 폭 Wb까지, 또는 그 반대로 도너 반도체 웨이퍼(120)의 주입 표면 (121)에서 변화한다. 폭 W의 변화는 스캔 방향에서 이온 주입에 기인하는 핵형성 부위의 밀도의 변화에 기여한다(X 및 Y 축 방향 중 적어도 한 방향에 따라서 변화하게 설정될 수 있다).

주입빔(202)은 수소 이온을 포함하고, 수소 이온은 동일한 (포지티브) 전하를 갖는다. 동일한 전하를 갖는 입자가 서로 반발하기 때문에, 빔(202)은 이온 소스로부터 더 긴 거리에서 더 넓고(위치 A), 이온 소스로부터 더 짧은 거리에서 더 좁다(위치B). 위치 B에서 더욱 많이 집속된 (더 낮은 폭 Wb)이온 빔은 도너 반도체 웨이퍼(120)의 국소 영역을 위치 A에서 덜 집속된 (더 높은 폭 Wa) 이온 빔보다 더 높은 정도로 가열한다. 더 높은 온도하에서, 많은 수소 이온은 이러한 국소 영역으로부터 확산하고 다른 영역에 비해서 더 낮은 수소 이온의 부분은 잔류한다. 도 6b에 도시된 바와 같이, 이것은 도너 반도체 웨이퍼(120)의 약화된 슬라이스(125)에서 수소의 층상으로 비균일한 분포(따라서 핵형성 부위의 밀도)를 일으킨다.

핵형성 부위의 밀도에서 유사한 공간의 변화는 빔소스의 각도를 조절하거나 이온빔(202)의 시준(collimation)을 조절하기 위해서 공지된 메카니즘의 일부를 포함시킴으로써 달성될 수 있다.

핵형성 부위의 밀도에서 공간의 변화를 달성하는 데에 적당한 방법은 2단계의 이온 주입 단계를 사용하는 것이다. 제 1 이온 주입을 실시하여 제 2 이온 종을 접착하는 효과를 갖는 이온을 주입시킨다. 그 다음에, 제 2 이온 종을 주입한다. 제 1 이온 종은 상술한 또는 후술한 적당한 방법 중 어느 하나를 사용하여 공간적으로 비균일하게 주입된다. 따라서, 제 2 이온 종이 주입되고 제 1 종으로 이동하면, 얻어진 약화된 슬라이스(125)는 핵형성 부위의 비균일 밀도를 나타낸다.

예를 들면, 제 1 이온 종은 도너 반도체 웨이퍼(120)의 물질, 예를 들면 실리콘 도너 반도체 웨이퍼(120)에서 주입용 실리콘 이온을 사용한 물질에 기초한다. 이러한 Si 이온은 제 2 이온 종, 예를 들면 수소 이온을 트랩핑하는 특성을 가질 수 있다. 상기 기재된 바와 같이, H 이온은 일부 반도체 원자, 예를 들면 Si 원자와 결합하여 Si-H 결합을 형성한다. 일례로서, 실리콘 내의 실리콘 주입(silicon-into silicon implantation)은 종래에 공지된 주입량 및 에너지에서 실시될 수 있고, 예를 들면 미국 특허 7,148,124에 기재되어 있고, 그 내용은 참조로 포함되어 있다. 그러나, 종래 기술과 달리, 트랩핑 이온 종의 공간 밀도 분포(이러한 경우에 Si)는 비균일하다(예를 들면, 하나의 에지에서 가장 높고, 도너 반도체 웨이퍼(120)의 반대 에지에서 가장 낮고 또는 본원에 검토된 그외의 변화). 다음에, 제 2 이온 종, 예를 들면 수소가 주입되고, 균일한 분포를 가질 수 있다. 도너 반도체 웨이퍼(120)의 약화된 슬라이스(125)에서 수소의 잔량은 2개의 요소: (1)제 2 종, 수소를 트랩핑할 수 있는 부위의 농도 분포, 및 (2)입수가능한 수소(주입량으로 주입되고 잔류하는 수소)에 따라 다르다.

상기 종의 비균일 공간 분포를 반대로 하여 유사한 결과를 달성할 수 있다. 예를 들면, 제 1 종을 균일하게 주입한 후 제 2 종을 비균일하게 주입할 수 있다. 또한, 양쪽 주입물은 공간적으로 비균일하게 될 수 있다. 약화된 슬라이스(125) 내에 제 2 종(예를 들면, 수소)의 비균일 분포는 가장 높은 수소 농도의 점, 에지 또는 영역을 일으키는데, 이는 이어서 쪼개짐을 시작하기 위한 가장 낮은 온도의 위치이다.

다시, 도 2a-2b를 참조하면, 화살표 A는 도너 반도체 웨이퍼(120)로부터 박리층(122)의 방향성 있게 및/또는 일시적으로 제어가능한 분리 특성을 설명하고, 약화된 슬라이스(125)의 하나의 점, 에지, 및/또는 영역으로부터 그외의 점, 에지 및/또는 영역까지 분리를 확장하는 것은 시간의 함수로서 달성된다. 핵형성 부위에서 밀도의 공간 변화와 관련해서, 도너 반도체 웨이퍼(120)는 가장 높은 밀도의 점, 에지 및/또는 영역으로부터 약화된 슬라이스(125)에서 분리를 시작하는 데에 충분한 온도까지 상승한다. 실리콘 내의 높은 수소 농도는 350℃ 이하만큼 낮은 온도에서 분리하는 반면, 보다 낮은 농도의 수소를 갖는 실리콘은 더 높은 온도, 예를 들면 450℃ 이상에서 분리하는 것을 알 수 있었다. 도너 반도체 웨이퍼(120)는 약화된 슬라이스(125) 전역에서 밀도의 공간 변화의 함수로서 방향성 있게 약화된 슬라이스(125)를 따라서 실질적으로 분리를 지속하는 데에 충분한 온도까지 상승한다.

X축 및 Y축 방향 중 한 방향 또는 양방향에서 이온 주입에 기인하는 약화된 슬라이스(125)의 깊이를 공간적으로 변화하는 특별한 변수에 대한 세부사항이 제공될 것이다. 이러한 공간 변화를 달성하기 위해서 어떠한 방법을 사용하더라도, 실질적으로 낮은 깊이는 약 200-380nm 사이이고, 가장 높은 깊이는 약 400-425 nm 사이인 것이 바람직하다. 또 다른 방법에서 변화를 보면, 최대 깊이와 최소 깊이 사이의 차이는 약 5-200% 사이일 수 있다.

본 발명의 하나 이상의 형태에 따라서, 약화된 슬라이스(125)의 깊이는 이온 주입 단계 중에 이온 빔의 각도를 조절함으로써 공간적으로 변화될 수 있다. 즉, 도 6a-6b에서 기재된 방법은 약화된 슬라이스(125)의 깊이 조절의 적용성을 가질 수 있다(빔 폭의 함수로서 온도를 변화시키는 메카니즘은 약화된 슬라이스(125)의 깊이 변화가 달성되는 이유로 생각되지 않는 것을 유의한다).

도 6a 및 7a-7b를 참조하면, 약화된 슬라이스(125)의 깊이의 공간 변화는: (1)경사각 Φ(도 6a에 대해 도시되고 기재된); 및 (2)이온 주입빔(202)의 방향축에 대해서 도너 반도체 웨이퍼(120)의 장축 Lo에 대해서 트위스트 중 적어도 하나를 변화시킴으로써 달성될 수 있다. 경사 및/또는 트위스트의 조절은 도너 반도체 웨이퍼(120)의 격자 구조를 통해서 채널링 정도를 조절하고, 이러한 채널은 이온 빔(202)이 주입 표면(121) 전역을 스캔할 때, 이온빔(202)으로 정렬하고 정렬하지 않는 경향이 있다. 채널링 정도는 공간적으로 변화할 때, 약화된 슬라이스(125)의 깊이도 변화한다.

각도 Φ는 약 1-10°사이이고 트위스트 각은 약 1-45°일 수 있다.

상기 추론된 바와 같이, 도 7c 및 7d를 참조하면, 주입 깊이는 경사가 커질수록 작아진다. 비교적 작은 각(예를 들면, 0-10°)에 대해서, 주입 깊이와 경사 사이의 관계는 채널링에 의해서 지배된다. 비교적 더 큰 각도에 대해서, 코사인 효과가 지배한다. 즉, 얻어진 박리막 두께는 필수적으로 주입각의 코사인에 비례한다.

또한, 공간 변화 단계는 이온 빔(202)이 도너 반도체 웨이퍼(120)의 주입 표면(121) 전역을 스캔할 때, 주입 표면(121)으로부터 약화된 슬라이스(125)의 깊이가 도너 반도체 웨이퍼(120) 전역에서 공간적으로 변화하도록 이온빔(202)의 에너지 수준의 변화를 포함할 수 있다.

도 7b를 도시된 바와 같이, 상기의 방법은 도너 반도체 웨이퍼(120)의 약화된 슬라이스의 층상으로 비균일한 깊이(또는 주입깊이)를 일으킨다.

도너 반도체 웨이퍼(202)의 경사 조절에 따라서, 공간 변화를 달성하기 위해서 박리될 수 있는 변수는 이온 증착 분포(또는 스트래글)의 폭이다. 도 8a에 도시된 바와 같이, 약화된 슬라이스(125)를 통해서 이온 분포의 폭은 (상부에서 하부)는 도너 반도체 웨이퍼(120)의 경사각(또는 일반적으로 빔각)의 함수로서 변화한다. 따라서, 경사각을 변화시킴으로써, 공간적으로 변화하는 분포폭은 약화된 슬라이스(125)에서 달성될 수 있다(도 8b에 도시됨). 임의의 조작 이론에 의해서 제한되는 것으로 의도되지 않지만, 더 좁은 분포 폭을 갖는 약화된 슬라이스(125)의 부분이 더 넓은 분포폭을 갖는 약화된 슬라이스(125)의 부분보다 낮은 온도에서 분리하는 것으로 생각된다. 따라서, 도너 반도체 웨이퍼(120)로부터 박리층(122)의 방향성 있게 및/또는 일시적으로 제어가능한 분리 특성, 약화된 슬라이스(125)의 하나의 점, 에지 및/또는 영역부터 그외의 점, 에지 및/또는 영역까지의 분리 확장은 시간 및 온도 함수로서 달성될 수 있는 것으로 생각된다.

도 8c를 참조하면, 스트래글에 대한 경사 효과에 대해서 추가의 데이터는 다시 주입 프로파일의 폭에 영향을 준다. 도 8c에 도시된 양쪽의 주입물에서 사용된 주입량이 동일하다. 피크 H 농도가 다르지만, 양쪽의 주입물은 박리한다. 따라서, +/-0.1°및 +/-3°의 경사 변화 사이의 차이는 스트래글에 대해서 중요하다.

도 9a-9d를 참조하면, 약화된 슬라이스(125)의 깊이를 공간적으로 변화하는 방법은 주입 표면(121)으로부터 약화된 슬라이스(125)의 깊이가 도너 반도체 웨이퍼(120) 전역에서 공간적으로 변화하도록 도너 반도체 웨이퍼(120)에 포스트 주입 물질 제거 공정을 실시하는 것을 포함한다. 도 9a에 도시된 바와 같이, 도너 반도체 웨이퍼(120)는 일부 결정적인 연마 공정 또는 플라즈마 증진 화학 에칭(PACE)을 실시할 수 있다. 이들의 방법은 연마 단계에 의해서 제거된 물질의 양의 국소적 제어를 허용한다. 반응성 이온 에칭(RIE), 화학적 기계적 연마(CMP) 및 습윤 화학 에칭을 포함하는 그외의 방법은 규칙적이고 재생가능한 노출 표면 전역에서 비균일 물질을 제거할 수 있다. 하나 이상의 이들의 방법을 사용하여 주입 표면(121)으로부터 약화된 슬라이스(125)의 깊이에서 약간의 변화, 예를 들면 도 3a, 4a, 4b, 4c 등에 도시된 것 중 임의의 하나를 도입할 수 있다. 물질 제거 전에 이온 주입 단계는 공간적으로 균일하거나 비균일할 수 있다.

도 9b 및 9c를 참조하면, 공간 변화 단계는 이온 빔(202)이 주입 표면(121)을 스캔할 때 이온 침투가 다양한 정도로 방해되도록, 공간적으로 비균일하게 도너 반도체 웨이퍼(120)의 주입 표면(121)에 마스크(220A 또는 220B)를 사용하는 것을 포함할 수 있다. 마스킹 필름(220)은 실리콘 디옥사이드, 유기 폴리머, 예를 들면 포토 레지스트 등을 포함할 수 있다. 유망한 증착 방법은 플라즈마 화학 기상성장법(PECVD), 스핀 코팅, 폴리디메틸실록산(PDMS) 스탬핑 등을 포함한다. 마스킹 필름(220) 두께는 약화된 슬라이스(125)의 소망의 깊이에 필적하거나 그보다 적게 될 수 있다. 이온이 주입된 깊이는 입사 이온의 에너지에 의해서 결정되기 때문에, 마스크(220)의 방해 작용은 도너 반도체 웨이퍼(120)에서 주로 주입 종의 깊이에서 공간 변조를 의미할 것이다. 증착된 마스크(220)의 특성에 따라서, 소망의 특성은 이온 통로에 길이를 부가하거나, 이온을 분산하여 채널 정도를 변경하거나 그외의 현상에 의해서 달성될 수 있다.

도 9d에 도시된 바와 같이(약화된 슬라이스(125)의 모든 에지에 더 낮은 깊이 및 그 중심을 향해서 더 높은 깊이를 도시한다), 기판(102)에 결합 후 또는 결합 중에 도너 반도체 웨이퍼(120)는 가장 낮은 깊이의 점, 에지, 및/또는 영역으로부터 약화된 슬라이스(125)에서 분리를 시작하는 데에 충분한 온도까지 상승시킨다. 도너 반도체 웨이퍼(120)는 가장 낮은 깊이부터 가장 높은 깊이까지의 깊이의 공간 변화의 함수로서 방향성 있게 약화된 슬라이스(125)를 따라서 실질적으로 분리를 지속하는 데에 충분한 온도까지 상승한다.

도 10a-10d 및 11를 참조하면, 공간 변화 단계는 약화된 슬라이스(125)에 적어도 주입 표면(121)을 통해서, 바람직하게 약화된 슬라이스(125)를 통해서 하나 이상의 블라인드 홀(230)을 천공하는 것을 포함한다(도 10b). 본 발명은 임의의 조작 이론에 의해서 한정하는 것으로 의도되지 않지만, 기판(102)에 결합 중 또는 결합 후(도 10c), 도너 반도체 웨이퍼(120)를 더 높은 온도까지 상승시킨 것이 이러한 홀이 없는 위치에서 분리되기 전에 블라인드 홀(230)에서 분리를 일으킬 (도 10d) 것으로 생각된다. 도 11에 도시된 바와 같이, 주입 표면(121)을 통해서 블라인드 홀(230)의 배열을 천공하는 것은 이러한 홀의 비균일 공간 분포를 형성할 수 있다. 따라서, 도너 반도체 웨이퍼(120)를 약화된 슬라이스(125)를 따라서 실질적으로 분리를 시작하고 지속하는 데에 충분한 온도까지 상승하는 것은 가장 높은 농도부터 가장 낮은 농도까지 블라인드 홀(230)의 배열 분포의 함수로서 방향성 있게 달성될 수 있다.

도 12a-12b를 참조하면, 공간 변화 단계는 약화된 슬라이스(125) 전체에 각각의 공간 위치에서 핵형성 부위 밀도 또는 압력이 도너 반도체 웨이퍼(120) 전역에서 공간적으로 변화하도록 도너 반도체 웨이퍼(120)에 비균일 시간-온도 프로파일을 실시하는 것을 포함한다. 예를 들면, 도 12a에서 도시된 온도 구배는 웨이퍼(120)의 우측에 비해서 좌측에 더 높은 온도를 적용한다. 온도 구배는 기판(102)에 결합 전 또는 결합 중 인시츄 적용될 수 있다. 시간 경과에 따라서, 상기 공정 시간은 소정의 공정 온도에서 분리 쓰레스홀드 미만으로 유지하면, 결함 부위의 핵형성 및 그 안에 기체 압력 중의 하나가 온도 구배의 함수로서 웨이퍼(120) 전역에서 공간적으로 약화된 슬라이스(125) 전체에서 다양한 정도로 증가한다.(도 12b 참조). 소정 공정 온도에서 분리 쓰레스홀드 시간은 분리 쓰레스홀드 시간이 공정 온도에 지수적으로 역비례하는 아레니우스 관계를 따르는 것으로 예상된다. 이익의 변수는 공정 시간과 공정 온도에서 분리 쓰레스홀드 시간의 비율이다. 본원에서 검토된 상술한 공간적으로 변화하는 변수 프로파일 또는 그외의 바람직한 것은 공정 시간-분리 시간 비율 프로파일을 조절함으로써 달성될 수 있다. 그 다음에, 도너 반도체 웨이퍼(120)는 최대 공정 시간-분리 시간 비율의 점, 에지, 및/또는 영역으로부터 약화된 슬라이스(125)에서 분리를 시작하는 데에 충분한 온도까지 상승한다. 설명된 예에서, 최대 공정 시간-분리 시간 비율은 웨이퍼(120)의 좌측에 있다. 도너 반도체 웨이퍼(120)는 최대 공정 시간-분리 시간 비율부터 최소 공정 시간-분리 시간 비율까지 변화하는 시간-온도 프로파일의 함수로서 방향성 있게 약화된 슬라이스(125)를 따라서 실질적으로 분리를 지속하는 데에 충분한 온도까지 상승한다. 물질 특성, 및 이온 종, 주입량, 및 주입 깊이를 포함하는 그외의 요소에 따라서, 실질적으로 높은 공정 시간-분리 시간 비율은 약 0.9와 0.5 사이이고 가장 낮은 공정 시간-분리 시간 비율은 0과 0.5 사이이다.

다양한 메카니즘이 사전 결합 또는 인-시츄 결합에 사용되어 공간적으로 변화하는 시간-온도 프로파일을 달성할 수 있다. 예를 들면, 하나 이상의 공간적으로 비균일 전도, 대류, 또는 복사 가열 방법(핫플레이트, 레이저 조사, 가시/적외선 램프, 등)이 사용되어 도너 반도체 웨이퍼(120)를 가열할 수 있다. 제어된 시간/온도 구배는 직접적인 또는 간접적인 열 접촉(전도)에 의해 달성되어 임의의 소망의 프로파일을 달성할 수 있다. 처리가능한, 2차원 배열의 핫플레이트 요소가 사용되어 컴퓨터 제어 또는 프로그래밍에 기초한 다른 프로파일을 달성할 수 있다. 예를 들면 급속 열 어닐링(복사)에 사용된 램프를 사용한 국소 적외선 조사가 사용되고, 및/또는 가시광 또는 근적외선 레이저 조사가 사용되어 국소적 및 공간적으로 비균일 가열(조사)을 제공할 수 있다. 또한, 임의의 수단을 통해서 균일 또는 비균일 열 프로파일의 적용 및 공간적으로 비균일 냉각 메카니즘의 적용, 예를 들면 직접적인 접촉(전도) 또는 기체 또는 유체 흐름 제트(전도/대류)가 사용되어 소망의 사간-온도 구배를 달성할 수 있다.

다시, 이들 가열/냉각 방법은 사전 결합 또는 인시츄에 사용될 수 있다. 인시츄 결합 방법에 따라서, 미국 특허 출원 11/417,445, High Temperature anodic bonding apparatus 명칭에 기재된 결합 장치는 전체 내용을 참조로 포함되어 있고 본 발명에 따라서 사용하기 위해서 적응될 수 있다. 결합 장치에서 열 복사 손실의 관리가 제어되고, 박리되어 결합 장치의 주변에 적외선 반사 요소의 혼합을 통해서 시간-온도 구배를 달성하여 복사 손실을 최소화하고 에지 온도를 최대화할 수 있다. 반대로, 결합 장치에서 열 복사 손실의 관리는 냉각된 적외선 흡수재의 혼합을 통해서 제어되어 복사손실을 최대화하고 에지 온도를 최소화한다. 상기 주제의 많은 변수가 사용되어 소망의 시간-온도 구배를 달성할 수 있다.

본 발명은 특별한 실시형태에 대해서 기재되어 있지만, 이들 실시형태는 본 발명의 원리 및 적용을 설명하는 것이 이해된다. 수많은 변경은 설명하는 실시형태에 대해서 행해지고 다른 배열은 첨부된 청구범위로 정의된 본 발명의 정신 및 범위로부터 벗어나지 않고 고안될 수 있다.

Claims (19)

- 도너 반도체 웨이퍼의 주입 표면에 이온 주입 단계를 실시하여 상기 도너 반도체 웨이퍼의 박리층을 한정하는 단면에 약화된 슬라이스를 형성하는 단계; 및

상기 이온 주입 단계 전에, 중에 또는 그 후에, 상기 도너 반도체 웨이퍼에 공간 변화 단계를 실시하여 상기 이온 주입 단계에 기인한 핵형성 부위의 밀도가 X- 및 Y-축 방향 중 적어도 한 방향에서 약화된 슬라이스 전체에서 공간적으로 변화하는 단계를 포함하는 반도체-온-절연체(SOI) 구조를 형성하는 방법. - 청구항 1에 있어서, 핵형성 부위의 최대 국소 밀도는 약 5x105 sites/㎠ 의 약화된 슬라이스의 제 1 영역에 존재하며, 핵형성 부위의 최소 밀도는 약 5x104 sites/㎠ 의 약화된 슬라이스의 제 2 영역에 존재하고, 상기 제 2 영역은 X- 및 Y-축 방향 중 적어도 한 방향에서 제 1 영역으로부터 떨어져 있는 것을 특징으로 하는 방법.

- 청구항 1에 있어서, 상기 약화된 슬라이스의 제 1 영역에서 핵형성 부위의 최대 밀도는 상기 약화된 슬라이스의 제 2 영역에서 핵형성 부위의 최소 밀도의 적어도 10배인 것을 특징으로 하는 방법.

- 청구항 1에 있어서, 상기 방법은 상기 도너 반도체 웨이퍼를 가장 높은 밀도의 핵형성 부위의 점, 에지 및/또는 영역으로부터 상기 약화된 슬라이스에서 분리를 시작하는 데에 충분한 온도까지 상승시키는 단계를 더욱 포함하는 것을 특징으로 하는 방법.

- 청구항 4에 있어서, 상기 방법은 상기 도너 반도체 웨이퍼를 가장 높은 밀도로부터 가장 낮은 밀도로 핵형성 부위의 변화하는 밀도의 함수로서 방향성 있게 상기 약화된 슬라이스를 따라서 실질적으로 분리를 지속하는 데에 충분한 온도까지 상승시키는 단계를 더욱 포함하는 것을 특징으로 하는 방법.

- 청구항 5에 있어서, 상기 상승하는 온도의 시간-온도 프로파일은 대략 수 초이므로 가장 높은 밀도로부터 가장 낮은 밀도까지 상기 약화된 슬라이스를 따라서 분리의 확장이 적어도 1초에 걸쳐서 발생하는 것을 특징으로 하는 방법.

- 청구항 1에 있어서, 상기 공간 변화 단계는 X- 및 Y-축 방향 중 적어도 한 방향에서 이온 주입량을 공간적으로 변화시키는 단계를 포함하는 것을 특징으로 하는 방법.

- 청구항 7에 있어서, 상기 공간 변화 단계는 실질적으로 높은 주입량이 상기 도너 반도체 웨이퍼의 약화된 슬라이스의 초기의 에지, 초기의 점 또는 초기의 영역을 따라서 존재하고 비교적 낮은 주입량이 X- 및 Y-축 방향 중 적어도 한 방향에서 초기의 에지, 초기의 점 또는 초기의 영역으로부터 연속적으로 더욱 먼 거리에 존재하도록 이온 주입량을 공간적으로 변화시키는 단계를 포함하는 것을 특징으로 하는 방법.

- 청구항 8에 있어서, 상기 가장 낮은 주입량은 실질적으로 높은 주입량의 70% 내지 90%, 특정한 실시형태에서 적어도 80%인 것을 특징으로 하는 방법.

- 청구항 8에 있어서, 상기 실질적으로 높은 주입량은 상기 약화된 슬라이스의 하나 이상의 에지를 따라서 초기의 점 또는 영역에서 존재하고 비교적 낮은 주입량은 X- 및 Y-축 방향에서 초기의 점 또는 초기의 영역으로부터 연속적으로 더욱 먼 거리에서 존재하는 것을 특징으로 하는 방법.

- 청구항 7에 있어서, 상기 도너 반도체 웨이퍼는 직사각형이고;

상기 공간 변화 단계는 실질적으로 높은 주입량이 상기 도너 반도체 웨이퍼의 약화된 슬라이스의 적어도 2개의 에지 각각에 존재하고 비교적 낮은 주입량이 상기 약화된 슬라이스의 중심을 향해서 적어도 2개의 에지로부터 연속적으로 더욱 먼 거리에서 존재하도록 이온 주입량을 공간적으로 변화하는 단계를 포함하는 것을 특징으로 하는 방법. - 청구항 11에 있어서, 상기 공간 변화 단계는 실질적으로 높은 주입량이 상기 약화된 슬라이스의 모든 에지에서 존재하고 비교적 낮은 주입량이 상기 약화된 슬라이스의 중심을 향해서 연속적으로 더욱 먼 거리에서 존재하도록 이온 주입량을 공간적으로 변화시키는 단계를 포함하는 것을 특징으로 하는 방법.

- 청구항 7에 있어서, 상기 공간 변화 단계는 상기 이온 주입 단계 중에 발생하고, 상기 이온 주입 단계는:

제 1 이온 종을 실질적으로 균일하게 주입하여 실질적으로 균일한 분포의 약화된 슬라이스를 형성하는 단계; 및

제 2 이온 종을 실질적으로 비균일하게 주입하여 상기 제 2 이온 종이 상기 약화된 슬라이스로의 원자 이동을 일으켜서 상기 약화된 슬라이스 전체에 핵형성 부위의 공간적으로 변화하는 밀도를 발생시키는 단계를 포함하는 것을 특징으로 하는 방법. - 청구항 13에 있어서, 상기 제 1 이온 종은 수소이고, 상기 제 2 이온 종은 헬륨인 것을 특징으로 하는 방법.

- 청구항 13에 있어서, 상기 제 2 이온 종을 실질적으로 비균일하게 주입하는 단계는 상기 제 2 이온 종을 상기 도너 반도체 웨이퍼 전체에서 공간적으로 변화하는 깊이에 주입하는 단계를 포함하는 것을 특징으로 하는 방법.

- 청구항 1에 있어서, 상기 도너 반도체 웨이퍼는 폭, 깊이 및 높이를 갖고, 상기 폭 및 깊이는 X- 및 Y-축 방향을 한정하며 상기 높이는 장축을 한정하고;

상기 공간 변화 단계는 상기 도너 반도체 웨이퍼를 그 장축이 이온 주입 단계 중에 이온 주입 빔의 방향 축에 대해서 비-제로 각도(non-zero angle) Φ에 있도록 경사시켜서 상기 이온 주입단계에 기인하는 핵형성 부위의 밀도가 X- 및 Y- 축 방향 중 어느 한 방향에서 약화된 슬라이스 전체에서 공간적으로 변화하는 단계를 포함하는 것을 특징으로 하는 방법. - 청구항 16에 있어서, 상기 각도 Φ는 약 1 내지 45°의 범위인 것을 특징으로 하는 방법.

- 도너 반도체 웨이퍼의 주입 표면에 이온 주입 단계를 실시하여 도너 반도체 웨이퍼의 박리층을 한정하는 단면에 약화된 슬라이스를 형성하는 단계;

상기 약화된 슬라이스에 적어도 상기 주입 표면을 통해서 블라인드 홀을 천공하는 단계; 및

상기 도너 반도체 웨이퍼를 상기 블라인드 홀에서 분리를 시작하는 데에 충분한 온도까지 상승시키는 단계를 포함하는 반도체-온-절연체(SOI) 구조를 형성하는 방법. - 청구항 18에 있어서, 상기 방법은 상기 약화된 슬라이스에 적어도 상기 주입 표면을 통해서 블라인드 홀의 배열을 천공하여 비균일한 공간 분포를 형성하는 단계; 및

상기 도너 반도체 웨이퍼를 블라인드 홀 배열의 분포의 함수로서 방향성 있게 약화된 슬라이스를 따라서 실질적으로 분리를 지속하는 데에 충분한 온도까지 상승시키는 단계를 더욱 포함하는 것을 특징으로 하는 방법.

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/290,384 | 2008-10-30 | ||

| US12/290,362 | 2008-10-30 | ||

| US12/290,384 US8003491B2 (en) | 2008-10-30 | 2008-10-30 | Methods and apparatus for producing semiconductor on insulator structures using directed exfoliation |

| US12/290,362 US7816225B2 (en) | 2008-10-30 | 2008-10-30 | Methods and apparatus for producing semiconductor on insulator structures using directed exfoliation |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20110081318A true KR20110081318A (ko) | 2011-07-13 |

Family

ID=41559616

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020117012221A KR101568898B1 (ko) | 2008-10-30 | 2009-10-29 | 방향성 박리를 사용한 반도체 온 절연체 구조를 생성하기 위한 방법 및 장치 |

| KR1020117012220A KR20110081318A (ko) | 2008-10-30 | 2009-10-29 | 방향성 박리를 사용한 반도체 온 절연체 구조를 생성하기 위한 방법 및 장치 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020117012221A KR101568898B1 (ko) | 2008-10-30 | 2009-10-29 | 방향성 박리를 사용한 반도체 온 절연체 구조를 생성하기 위한 방법 및 장치 |

Country Status (6)

| Country | Link |

|---|---|

| EP (2) | EP2359400A2 (ko) |

| JP (2) | JP5650653B2 (ko) |

| KR (2) | KR101568898B1 (ko) |

| CN (2) | CN102203934B (ko) |

| TW (2) | TWI451534B (ko) |

| WO (2) | WO2010059361A2 (ko) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5703853B2 (ja) * | 2011-03-04 | 2015-04-22 | 信越半導体株式会社 | 貼り合わせウェーハの製造方法 |

| FR3055063B1 (fr) * | 2016-08-11 | 2018-08-31 | Soitec | Procede de transfert d'une couche utile |

| CN111834205B (zh) * | 2020-07-07 | 2021-12-28 | 中国科学院上海微系统与信息技术研究所 | 一种异质半导体薄膜及其制备方法 |

| CN114975765A (zh) * | 2022-07-19 | 2022-08-30 | 济南晶正电子科技有限公司 | 复合单晶压电薄膜及其制备方法 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2714524B1 (fr) * | 1993-12-23 | 1996-01-26 | Commissariat Energie Atomique | Procede de realisation d'une structure en relief sur un support en materiau semiconducteur |

| US6013563A (en) * | 1997-05-12 | 2000-01-11 | Silicon Genesis Corporation | Controlled cleaning process |

| MY118019A (en) * | 1998-02-18 | 2004-08-30 | Canon Kk | Composite member, its separation method, and preparation method of semiconductor substrate by utilization thereof |

| JP3031904B2 (ja) * | 1998-02-18 | 2000-04-10 | キヤノン株式会社 | 複合部材とその分離方法、及びそれを利用した半導体基体の製造方法 |

| US20010007790A1 (en) * | 1998-06-23 | 2001-07-12 | Henley Francois J. | Pre-semiconductor process implant and post-process film separation |

| US6054370A (en) * | 1998-06-30 | 2000-04-25 | Intel Corporation | Method of delaminating a pre-fabricated transistor layer from a substrate for placement on another wafer |

| FR2811807B1 (fr) * | 2000-07-12 | 2003-07-04 | Commissariat Energie Atomique | Procede de decoupage d'un bloc de materiau et de formation d'un film mince |

| JP2002124652A (ja) * | 2000-10-16 | 2002-04-26 | Seiko Epson Corp | 半導体基板の製造方法、半導体基板、電気光学装置並びに電子機器 |

| FR2830983B1 (fr) | 2001-10-11 | 2004-05-14 | Commissariat Energie Atomique | Procede de fabrication de couches minces contenant des microcomposants |

| FR2847077B1 (fr) * | 2002-11-12 | 2006-02-17 | Soitec Silicon On Insulator | Composants semi-conducteurs, et notamment de type soi mixtes, et procede de realisation |

| EP1429381B1 (en) * | 2002-12-10 | 2011-07-06 | S.O.I.Tec Silicon on Insulator Technologies | A method for manufacturing a material compound |

| US7176528B2 (en) | 2003-02-18 | 2007-02-13 | Corning Incorporated | Glass-based SOI structures |

| DE10318283A1 (de) * | 2003-04-22 | 2004-11-25 | Forschungszentrum Jülich GmbH | Verfahren zur Herstellung einer verspannten Schicht auf einem Substrat und Schichtstruktur |

| US7148124B1 (en) * | 2004-11-18 | 2006-12-12 | Alexander Yuri Usenko | Method for forming a fragile layer inside of a single crystalline substrate preferably for making silicon-on-insulator wafers |

| JP2006324051A (ja) * | 2005-05-17 | 2006-11-30 | Nissin Ion Equipment Co Ltd | 荷電粒子ビーム照射方法および装置 |

| JP4977999B2 (ja) * | 2005-11-21 | 2012-07-18 | 株式会社Sumco | 貼合せ基板の製造方法及びその方法で製造された貼合せ基板 |

| US7691730B2 (en) * | 2005-11-22 | 2010-04-06 | Corning Incorporated | Large area semiconductor on glass insulator |

-

2009

- 2009-10-28 TW TW098136607A patent/TWI451534B/zh not_active IP Right Cessation

- 2009-10-28 TW TW098136605A patent/TWI430338B/zh not_active IP Right Cessation

- 2009-10-29 KR KR1020117012221A patent/KR101568898B1/ko not_active IP Right Cessation

- 2009-10-29 CN CN200980143710.7A patent/CN102203934B/zh not_active Expired - Fee Related

- 2009-10-29 KR KR1020117012220A patent/KR20110081318A/ko active IP Right Grant

- 2009-10-29 JP JP2011534755A patent/JP5650653B2/ja not_active Expired - Fee Related

- 2009-10-29 JP JP2011534746A patent/JP5650652B2/ja not_active Expired - Fee Related

- 2009-10-29 EP EP09744304A patent/EP2359400A2/en not_active Withdrawn

- 2009-10-29 WO PCT/US2009/062504 patent/WO2010059361A2/en active Application Filing

- 2009-10-29 EP EP09744303A patent/EP2356676A2/en not_active Withdrawn

- 2009-10-29 CN CN200980143709.4A patent/CN102203933B/zh not_active Expired - Fee Related

- 2009-10-29 WO PCT/US2009/062531 patent/WO2010059367A2/en active Application Filing

Also Published As

| Publication number | Publication date |

|---|---|

| CN102203934A (zh) | 2011-09-28 |

| WO2010059367A2 (en) | 2010-05-27 |

| JP2012507868A (ja) | 2012-03-29 |

| JP5650652B2 (ja) | 2015-01-07 |

| WO2010059361A2 (en) | 2010-05-27 |

| TWI430338B (zh) | 2014-03-11 |

| JP2012507870A (ja) | 2012-03-29 |

| WO2010059367A3 (en) | 2010-08-05 |

| CN102203934B (zh) | 2014-02-12 |

| WO2010059361A3 (en) | 2010-08-12 |

| CN102203933B (zh) | 2015-12-02 |

| TW201030815A (en) | 2010-08-16 |

| JP5650653B2 (ja) | 2015-01-07 |

| EP2359400A2 (en) | 2011-08-24 |

| KR20110081881A (ko) | 2011-07-14 |

| TW201036112A (en) | 2010-10-01 |

| EP2356676A2 (en) | 2011-08-17 |

| KR101568898B1 (ko) | 2015-11-12 |

| TWI451534B (zh) | 2014-09-01 |

| CN102203933A (zh) | 2011-09-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8338269B2 (en) | Methods and apparatus for producing semiconductor on insulator structures using directed exfoliation | |

| CN101454875B (zh) | 使用辐照退火制造绝缘体上半导体结构的方法 | |

| KR100614860B1 (ko) | 원하는 기판 상에 단결정 물질의 박막을 전달하는 방법 | |

| US6429104B1 (en) | Method for forming cavities in a semiconductor substrate by implanting atoms | |

| CN101405847B (zh) | 处理含氧半导体晶片的方法及半导体元件 | |

| KR100634528B1 (ko) | 단결정 실리콘 필름의 제조방법 | |

| CN103943672A (zh) | 处理含氧半导体晶片的方法及半导体元件 | |

| CN102986020A (zh) | 对绝缘体基材上的硅进行精整的方法 | |

| KR20070085231A (ko) | 공동 주입 및 후속 주입에 의해 박막을 획득하는 방법 | |

| KR101568898B1 (ko) | 방향성 박리를 사용한 반도체 온 절연체 구조를 생성하기 위한 방법 및 장치 | |

| WO2004008514A1 (en) | Process for forming a fragile layer inside of a single crystalline substrate | |

| US8003491B2 (en) | Methods and apparatus for producing semiconductor on insulator structures using directed exfoliation | |

| JP2012507870A5 (ko) | ||

| US6952269B2 (en) | Apparatus and method for adiabatically heating a semiconductor surface | |

| Direction | c12) United States Patent | |

| KR20030076627A (ko) | Soi 재료의 제조 방법 | |

| US20050082549A1 (en) | Light emitting and/or detecting device and method of manufacturing the same | |

| Huang et al. | A nano-thick SOI fabrication method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right |