KR20080098213A - 오픈불량 및 펀치 방지를 위한 반도체소자의 제조 방법 - Google Patents

오픈불량 및 펀치 방지를 위한 반도체소자의 제조 방법 Download PDFInfo

- Publication number

- KR20080098213A KR20080098213A KR1020070043614A KR20070043614A KR20080098213A KR 20080098213 A KR20080098213 A KR 20080098213A KR 1020070043614 A KR1020070043614 A KR 1020070043614A KR 20070043614 A KR20070043614 A KR 20070043614A KR 20080098213 A KR20080098213 A KR 20080098213A

- Authority

- KR

- South Korea

- Prior art keywords

- storage node

- node contact

- semiconductor device

- manufacturing

- etching

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

- H10B12/0335—Making a connection between the transistor and the capacitor, e.g. plug

-

- H10P50/283—

-

- H10P95/062—

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

Description

Claims (13)

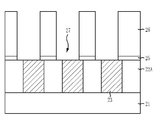

- 기판 상에 스토리지노드콘택홀이 구비된 절연막을 형성하는 단계;상기 스토리지노드콘택홀을 채울때까지 전면에 도전막을 형성하는 단계;상기 도전막을 제1에치백공정으로 식각하여 상기 스토리지노드콘택홀 내부에 스토리지노드콘택플러그를 형성하는 단계;상기 스토리지노드콘택플러그를 포함한 전면에 희생막을 형성하는 단계;상기 희생막의 표면을 평탄화시키는 단계; 및상기 평탄화된 희생막을 제2에치백공정으로 제거하면서 상기 스토리지노드콘택플러그 주변의 절연막을 일부 제거하는 단계를 포함하는 반도체소자의 제조 방법.

- 제1항에 있어서,상기 스토리지노드콘택플러그 주변의 절연막을 일부 제거하는 단계후에,전면에 식각배리어막을 형성하는 단계;상기 식각배리어막 상에 분리절연막을 형성하는 단계;상기 분리절연막을 식각하는 단계; 및상기 식각배리어막을 식각하여 상기 스토리지노드콘택플러그의 표면을 노출시키는 단계를 더 포함하는 반도체소자의 제조 방법.

- 제1항에 있어서,상기 희생막은, 스핀온코팅법으로 형성하는 반도체소자의 제조 방법.

- 제1항에 있어서,상기 희생막과 절연막은 상기 제2에치백공정시 동일한 식각속도를 가지는 물질로 형성하는 반도체소자의 제조 방법.

- 제4항에 있어서,상기 희생막과 절연막은 산화막으로 형성하는 반도체소자의 제조 방법.

- 제5항에 있어서,상기 절연막은, SOG(Spin On Glass)로 형성하는 반도체소자의 제조 방법.

- 제4항에 있어서,상기 제2에치백공정은,TCP(Transformer Coupled Plasma) 장비에서 진행하는 반도체소자의 제조 방법.

- 제7항에 있어서,상기 제2에치백공정은,바이어스파워(Bias power)는 50∼60W로 하고, 압력은 3∼5mTorr로 하며, 온도를 50∼60℃로 하여 진행하는 반도체소자의 제조 방법.

- 제8항에 있어서,상기 제2에치백공정시,식각가스는 불소(Fluorine) 계열 가스를 메인가스로 사용하는 반도체소자의 제조 방법.

- 제9항에 있어서,상기 불소계 가스는 SF6 가스를 100sccm∼500sccm의 유량으로 사용하는 반도체소자의 제조 방법.

- 제9항에 있어서,상기 제2에치백공정시 상기 메인가스에 질소(N2) 가스를 더 첨가하여 진행하는 반도체소자의 제조 방법.

- 제1항에 있어서,상기 희생막 표면을 평탄화시키는 단계는,아르곤 스퍼터링으로 진행하는 반도체소자의 제조 방법.

- 제1항에 있어서,상기 도전막은, 폴리실리콘막으로 형성하는 반도체소자의 제조 방법.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020070043614A KR100936805B1 (ko) | 2007-05-04 | 2007-05-04 | 오픈불량 및 펀치 방지를 위한 반도체소자의 제조 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020070043614A KR100936805B1 (ko) | 2007-05-04 | 2007-05-04 | 오픈불량 및 펀치 방지를 위한 반도체소자의 제조 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20080098213A true KR20080098213A (ko) | 2008-11-07 |

| KR100936805B1 KR100936805B1 (ko) | 2010-01-14 |

Family

ID=40285785

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020070043614A Expired - Fee Related KR100936805B1 (ko) | 2007-05-04 | 2007-05-04 | 오픈불량 및 펀치 방지를 위한 반도체소자의 제조 방법 |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR100936805B1 (ko) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106252218A (zh) * | 2016-09-30 | 2016-12-21 | 上海华虹宏力半导体制造有限公司 | 沟槽型mosfet栅极刻蚀工艺方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3291885B2 (ja) * | 1994-02-01 | 2002-06-17 | ソニー株式会社 | ドライエッチング方法 |

| KR100377163B1 (ko) * | 2000-12-18 | 2003-03-26 | 주식회사 하이닉스반도체 | 반도체소자의 폴리실리콘 플러그 형성 방법 |

| KR101034598B1 (ko) * | 2003-12-30 | 2011-05-12 | 주식회사 하이닉스반도체 | 반도체소자의 랜딩플러그콘택 형성 방법 |

| KR100649350B1 (ko) * | 2004-12-28 | 2006-11-28 | 주식회사 하이닉스반도체 | 반도체 소자의 랜딩 플러그 콘택 형성 방법 |

-

2007

- 2007-05-04 KR KR1020070043614A patent/KR100936805B1/ko not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR100936805B1 (ko) | 2010-01-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100505450B1 (ko) | 다마신 공정을 이용한 반도체소자 제조 방법 | |

| KR100936805B1 (ko) | 오픈불량 및 펀치 방지를 위한 반도체소자의 제조 방법 | |

| KR100680948B1 (ko) | 반도체 소자의 스토리지 노드 콘택 형성방법 | |

| KR20040057405A (ko) | 반도체소자 제조방법 | |

| KR100652793B1 (ko) | 반도체 소자 제조 방법 | |

| JP2011249678A (ja) | 半導体装置及びその製造方法 | |

| KR100643568B1 (ko) | 반도체소자의 깊은 콘택홀 형성 방법 | |

| KR100945225B1 (ko) | 반도체소자 제조 방법 | |

| KR100681207B1 (ko) | 반도체 소자의 콘택 플러그 형성방법 | |

| KR100755141B1 (ko) | 반도체 소자 콘택 플러그 및 그 제조 방법 | |

| KR100835506B1 (ko) | 반도체소자의 제조방법 | |

| KR100701779B1 (ko) | 반도체 소자의 콘택 형성 방법 | |

| KR100745058B1 (ko) | 반도체 소자의 셀프 얼라인 콘택홀 형성방법 | |

| KR100673883B1 (ko) | 반도체소자의 콘택 플러그 형성방법 | |

| KR100784074B1 (ko) | 반도체 소자의 비트 라인 형성 방법 | |

| KR100744002B1 (ko) | 반도체 소자의 제조방법 | |

| KR100843903B1 (ko) | 반도체 소자의 제조방법 | |

| KR20080015253A (ko) | 펀치 방지를 위한 반도체소자의 제조 방법 | |

| KR101043366B1 (ko) | 반도체 소자의 형성 방법 | |

| KR100917639B1 (ko) | 반도체 소자 제조 방법 | |

| KR100431815B1 (ko) | 반도체소자의 제조방법 | |

| KR20010005109A (ko) | 반도체 소자의 콘택 형성방법 | |

| KR20110008477A (ko) | 반도체 소자의 제조방법 | |

| KR20090021962A (ko) | 게이트패턴 제조 방법 | |

| KR20050116665A (ko) | 반도체 소자의 형성 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| A201 | Request for examination | ||

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| D13-X000 | Search requested |

St.27 status event code: A-1-2-D10-D13-srh-X000 |

|

| D14-X000 | Search report completed |

St.27 status event code: A-1-2-D10-D14-srh-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20130107 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20130107 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |