KR101788362B1 - 임프린트 장치, 물품의 제조 방법 및 위치정렬 장치 - Google Patents

임프린트 장치, 물품의 제조 방법 및 위치정렬 장치 Download PDFInfo

- Publication number

- KR101788362B1 KR101788362B1 KR1020140039142A KR20140039142A KR101788362B1 KR 101788362 B1 KR101788362 B1 KR 101788362B1 KR 1020140039142 A KR1020140039142 A KR 1020140039142A KR 20140039142 A KR20140039142 A KR 20140039142A KR 101788362 B1 KR101788362 B1 KR 101788362B1

- Authority

- KR

- South Korea

- Prior art keywords

- detector

- mark

- marks

- shot area

- substrate

- Prior art date

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 15

- 238000001514 detection method Methods 0.000 claims abstract description 20

- 239000000758 substrate Substances 0.000 claims description 83

- 230000007547 defect Effects 0.000 claims description 42

- 238000000034 method Methods 0.000 claims description 36

- 239000000463 material Substances 0.000 claims description 19

- 230000003287 optical effect Effects 0.000 claims description 7

- 238000012545 processing Methods 0.000 claims description 4

- 230000002950 deficient Effects 0.000 claims description 3

- 229920005989 resin Polymers 0.000 description 16

- 239000011347 resin Substances 0.000 description 16

- 238000010586 diagram Methods 0.000 description 14

- 239000004065 semiconductor Substances 0.000 description 5

- 238000012546 transfer Methods 0.000 description 5

- 238000001723 curing Methods 0.000 description 4

- 238000003384 imaging method Methods 0.000 description 3

- 238000000016 photochemical curing Methods 0.000 description 3

- 239000011295 pitch Substances 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 238000005382 thermal cycling Methods 0.000 description 3

- 238000012937 correction Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229920005992 thermoplastic resin Polymers 0.000 description 2

- 230000004075 alteration Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- RKTYLMNFRDHKIL-UHFFFAOYSA-N copper;5,10,15,20-tetraphenylporphyrin-22,24-diide Chemical compound [Cu+2].C1=CC(C(=C2C=CC([N-]2)=C(C=2C=CC=CC=2)C=2C=CC(N=2)=C(C=2C=CC=CC=2)C2=CC=C3[N-]2)C=2C=CC=CC=2)=NC1=C3C1=CC=CC=C1 RKTYLMNFRDHKIL-UHFFFAOYSA-N 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000009477 glass transition Effects 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/0002—Lithographic processes using patterning methods other than those involving the exposure to radiation, e.g. by stamping

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Shaping Of Tube Ends By Bending Or Straightening (AREA)

- Engineering & Computer Science (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Length Measuring Devices By Optical Means (AREA)

- Health & Medical Sciences (AREA)

- Toxicology (AREA)

Abstract

Description

도 1b는 제1 실시 형태의 임프린트 장치의 다른 구성을 도시하는 개략도.

도 2는 몰드 상의 마크의 일례 및 샷 영역 상의 마크의 일례를 도시하는 도면.

도 3은 몰드 상의 마크의 일례 및 샷 영역 상의 마크의 일례를 도시하는 도면.

도 4는 기판 상의 복수의 샷 영역의 배치를 도시하는 도면.

도 5a는 샷 영역에 형성된 마크의 배치예를 도시하는 도면.

도 5b는 샷 영역에 형성된 마크의 배치예를 도시하는 도면.

도 5c는 샷 영역에 형성된 마크의 배치예를 도시하는 도면.

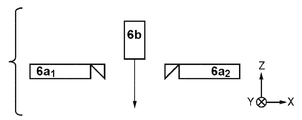

도 6a는 샷 영역에 형성된 마크의 배치예를 도시하는 도면.

도 6b는 샷 영역에 형성된 마크의 배치예를 도시하는 도면.

도 7a는 제1 검출기 및 제2 검출기의 배치예를 도시하는 도면.

도 7b는 제1 검출기 및 제2 검출기의 배치예를 도시하는 도면.

도 7c는 제1 검출기 및 제2 검출기의 배치예를 도시하는 도면.

도 7d는 복수의 제2 검출기의 배치예를 도시하는 도면.

도 8은 샷 영역에 형성된 마크의 배치를 도시하는 도면.

도 9는 복수의 패턴 영역이 형성된 몰드를 도시하는 도면.

Claims (16)

- 몰드를 이용하여 기판의 샷 영역 상의 임프린트 재료의 패턴을 형성하는 임프린트 장치이며,

상기 샷 영역에 형성된 복수의 마크 중 제1 개수의 마크를 포함하는 제1 시야를 가지며, 상기 몰드를 통해서 상기 제1 개수의 마크를 검출하도록 구성된 제1 검출기와,

상기 제1 검출기의 상기 제1 시야보다 넓고, 상기 샷 영역에 형성된 복수의 마크 중 제2 개수의 마크를 포함하는 제2 시야를 가지며, 상기 몰드를 통해서 상기 제1 개수보다 많은 상기 제2 개수의 마크를 검출하도록 구성된 제2 검출기와,

상기 제1 검출기 및 상기 제2 검출기의 검출 결과를 이용하여, 상기 샷 영역과 상기 몰드를 위치정렬하도록 구성된 제어기를 포함하고,

상기 샷 영역은 상기 기판의 외주를 포함하지 않는 칩 영역을 포함하고,

상기 샷 영역에 형성된 복수의 마크의 배치에 따라, 상기 샷 영역의 상기 칩 영역에 형성된 상기 제2 개수의 마크가 상기 제2 검출기에 의해 검출되는 제2 마크로 결정되고, 상기 복수의 마크 중 상기 제2 마크와 상이한 상기 제1 개수의 마크가 상기 제1 검출기에 의해 검출되는 제1 마크로 결정되고,

상기 제어기는, 상기 제1 검출기 및 상기 제2 검출기가 상기 제1 마크 및 상기 제2 마크를 각각 검출하게 하는, 임프린트 장치. - 제1항에 있어서,

복수의 제1 검출기를 더 포함하고,

상기 샷 영역은, 상기 기판의 주변부에 배치된 부분적으로 결함을 가진 샷 영역이며 상기 몰드에 형성된 패턴의 일부가 전사되는 결함 샷 영역을 포함하고,

상기 제어기는, 상기 결함 샷 영역에 형성된 복수의 마크 중, 복수의 상기 제1 검출기가 검출을 동시에 행할 수 있는 거리보다 작은 간격으로 배치되고, 상기 제2 검출기의 상기 제2 시야에 포함되는 상기 제2 개수의 마크를 상기 제2 검출기가 상기 제2 마크로서 검출하게 하고, 상기 제2 검출기의 검출 결과를 이용해서 상기 결함 샷 영역과 상기 몰드를 위치정렬하는, 임프린트 장치. - 제2항에 있어서,

상기 제어기는, 상기 결함 샷 영역에 형성된 복수의 마크 중, 상기 제2 검출기에 의해 검출된 상기 제2 마크와는 상이한 상기 제1 개수의 마크를 상기 제1 마크로서 복수의 상기 제1 검출기가 각각 검출하게 하고, 복수의 상기 제1 검출기의 검출 결과를 이용해서 상기 결함 샷 영역과 상기 몰드를 위치정렬하는, 임프린트 장치. - 제2항에 있어서,

상기 결함 샷 영역은, 상기 기판의 외주를 포함하지 않는 칩 영역을 포함하고,

상기 제2 검출기는, 상기 칩 영역에 제공되는 복수의 마크가 상기 제2 검출기의 상기 제2 시야에 포함되도록 구성되며,

상기 제어기는, 상기 칩 영역에 제공되는 복수의 마크를 상기 제2 마크로서 상기 제2 검출기가 검출하게 하는, 임프린트 장치. - 제2항에 있어서,

상기 제어기는, 상기 결함 샷 영역에 형성된 복수의 마크의 배치에 따라, 상기 결함 샷 영역에 형성된 복수의 마크로부터 상기 제1 마크와 상기 제2 마크를 결정하는, 임프린트 장치. - 제2항에 있어서,

상기 제어기는, 상기 결함 샷 영역이 배치되어 있는 기판 상의 위치에 따라, 상기 결함 샷 영역에 형성된 복수의 마크로부터 상기 제1 마크와 상기 제2 마크를 결정하는, 임프린트 장치. - 제1항에 있어서,

상기 제1 검출기 및 상기 제2 검출기는 각각 기판 면에 평행한 방향으로 이동하도록 구성되고,

상기 제어기는, 상기 제1 마크가 상기 제1 검출기의 상기 제1 시야에 포함되도록 상기 제1 검출기의 이동을 제어하고, 상기 제2 마크가 상기 제2 검출기의 상기 제2 시야에 포함되도록 상기 제2 검출기의 이동을 제어하는, 임프린트 장치. - 제1항에 있어서,

상기 제어기는, 상기 몰드와 상기 임프린트 재료가 서로 접촉하고 있는 상태에서 상기 제1 검출기 및 상기 제2 검출기가 상기 제1 마크 및 상기 제2 마크를 각각 검출하게 하는, 임프린트 장치. - 제1항에 있어서,

상기 임프린트 재료를 경화시키는 광을 발광하도록 구성된 광원과,

상기 제1 검출기와 상기 제2 검출기로부터 발광된 광과, 상기 광원으로부터 발광된 광을 상기 몰드를 통해서 상기 기판으로 유도하도록 구성된 광학 부재를 더 포함하는, 임프린트 장치. - 물품의 제조 방법이며,

임프린트 장치를 이용해서 기판 상에 패턴을 형성하는 단계와,

상기 패턴이 형성된 상기 기판을 가공하여 상기 물품을 제조하는 단계를 포함하고,

상기 물품은 상기 가공된 기판의 적어도 일부를 포함하며,

몰드를 이용하여 상기 기판의 샷 영역 상의 임프린트 재료에 패턴을 형성하는 상기 임프린트 장치는,

상기 샷 영역에 형성된 복수의 마크 중 제1 개수의 마크를 포함하는 제1 시야를 가지며, 상기 몰드를 통해서 상기 제1 개수의 마크를 검출하도록 구성된 제1 검출기와,

상기 제1 검출기의 상기 제1 시야보다 넓고, 상기 샷 영역에 형성된 복수의 마크 중 제2 개수의 마크를 포함하는 제2 시야를 가지며, 상기 몰드를 통해서 상기 제1 개수보다 많은 상기 제2 개수의 마크를 검출하도록 구성된 제2 검출기와,

상기 제1 검출기 및 상기 제2 검출기의 검출 결과를 이용하여, 상기 샷 영역과 상기 몰드를 위치정렬하도록 구성된 제어기를 포함하고,

상기 샷 영역은 상기 기판의 외주를 포함하지 않는 칩 영역을 포함하고,

상기 샷 영역에 형성된 복수의 마크의 배치에 따라, 상기 샷 영역의 상기 칩 영역에 형성된 상기 제2 개수의 마크가 상기 제2 검출기에 의해 검출되는 제2 마크로 결정되고, 상기 복수의 마크 중 상기 결정된 제2 마크와 상이한 상기 제1 개수의 마크가 상기 제1 검출기에 의해 검출되는 제1 마크로 결정되고,

상기 제어기는, 상기 제1 검출기 및 상기 제2 검출기가 상기 제1 마크 및 상기 제2 마크를 각각 검출하게 하는, 물품의 제조 방법. - 기판의 샷 영역을 위치정렬하는 위치정렬 장치이며,

상기 샷 영역에 형성된 복수의 마크 중 제1 개수의 마크를 포함하는 제1 시야를 가지며, 상기 제1 개수의 마크를 검출하도록 구성된 제1 검출기와,

상기 제1 검출기의 상기 제1 시야보다 넓고, 상기 샷 영역에 형성된 복수의 마크 중 제2 개수의 마크를 포함하는 제2 시야를 가지며, 상기 제1 개수보다 많은 상기 제2 개수의 마크를 검출하도록 구성된 제2 검출기와,

상기 제1 검출기 및 상기 제2 검출기의 검출 결과를 이용하여 상기 샷 영역을 위치정렬하도록 구성된 제어기를 포함하고,

상기 샷 영역은 상기 기판의 외주를 포함하지 않는 칩 영역을 포함하고,

상기 복수의 마크의 배치에 따라, 상기 샷 영역의 상기 칩 영역에 형성된 상기 제2 개수의 마크가 상기 제2 검출기에 의해 검출되는 제2 마크로 결정되고, 상기 복수의 마크 중 결정된 상기 제2 마크와 상이한 상기 제1 개수의 마크가 상기 제1 검출기에 의해 검출되는 제1 마크로 결정되고,

상기 제어기는, 상기 제1 검출기 및 상기 제2 검출기가 상기 제1 마크 및 상기 제2 마크를 각각 검출하게 하는, 위치정렬 장치. - 제1항에 있어서,

상기 제1 마크 및 상기 제2 마크는, 상기 제1 검출기 및 상기 제2 검출기에 의한 검출이 동시에 행해질 수 있도록 결정되는, 임프린트 장치. - 제1항에 있어서,

상기 복수의 마크 중 상기 결정된 제2 마크로부터 가장 떨어져 배열된 상기 제1 개수의 마크가 상기 제1 마크로 결정되는, 임프린트 장치. - 제1항에 있어서,

상기 제어기가 상기 제1 마크 및 상기 제2 마크를 결정하는, 임프린트 장치. - 제1항에 있어서,

상기 몰드를 유지하도록 구성된 유지 유닛과, 상기 기판 상의 상기 임프린트 재료를 경화시키는 광을 발광하는 광원을 더 포함하고,

상기 광원으로부터 발광되는 광은 상기 유지 유닛에 제공되는 공간을 통해서 상기 임프린트 재료에 입사하고,

상기 제1 검출기 및 상기 제2 검출기는 상기 공간을 통해서 상기 제1 마크 및 상기 제2 마크를 각각 검출하는, 임프린트 장치. - 제1항에 있어서,

상기 제2 마크는 상기 제1 검출기의 치수보다 작은 간격으로 배치되는, 임프린트 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013078093A JP6188382B2 (ja) | 2013-04-03 | 2013-04-03 | インプリント装置および物品の製造方法 |

| JPJP-P-2013-078093 | 2013-04-03 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20140120844A KR20140120844A (ko) | 2014-10-14 |

| KR101788362B1 true KR101788362B1 (ko) | 2017-10-19 |

Family

ID=51653885

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020140039142A KR101788362B1 (ko) | 2013-04-03 | 2014-04-02 | 임프린트 장치, 물품의 제조 방법 및 위치정렬 장치 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9946156B2 (ko) |

| JP (1) | JP6188382B2 (ko) |

| KR (1) | KR101788362B1 (ko) |

| CN (1) | CN104102090B (ko) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6138189B2 (ja) * | 2015-04-08 | 2017-05-31 | キヤノン株式会社 | インプリント装置および物品の製造方法 |

| CN105182702B (zh) * | 2015-10-30 | 2017-08-11 | 京东方科技集团股份有限公司 | 对位标记搜寻方法、显示基板和显示装置 |

| JP6671160B2 (ja) * | 2015-11-30 | 2020-03-25 | キヤノン株式会社 | インプリント装置、物品製造方法および位置合わせ方法 |

| CN105425478B (zh) | 2016-01-04 | 2019-09-17 | 京东方科技集团股份有限公司 | 一种对盒装置 |

| JP7038562B2 (ja) | 2018-02-13 | 2022-03-18 | キヤノン株式会社 | 検出装置、リソグラフィ装置、および物品の製造方法 |

| JP7116605B2 (ja) * | 2018-06-28 | 2022-08-10 | キヤノン株式会社 | インプリント材のパターンを形成するための方法、インプリント装置、インプリント装置の調整方法、および、物品製造方法 |

| KR102722244B1 (ko) * | 2018-10-22 | 2024-10-25 | 삼성디스플레이 주식회사 | 표시 장치 및 표시 장치의 제조 방법 |

| JP7337670B2 (ja) * | 2019-11-15 | 2023-09-04 | キヤノン株式会社 | インプリント装置、インプリント方法、および、物品の製造方法 |

| CN111016149B (zh) * | 2019-12-27 | 2022-10-04 | 江苏源美竹木业有限责任公司 | 同步对花压印系统及压印方法 |

| JP7603395B2 (ja) | 2020-08-26 | 2024-12-20 | キヤノン株式会社 | インプリント装置、および物品の製造方法 |

| CN119065213A (zh) * | 2024-11-01 | 2024-12-03 | 粤芯半导体技术股份有限公司 | 一种晶圆级标记的曝光方法及装置 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005167030A (ja) | 2003-12-03 | 2005-06-23 | Sony Corp | マスクおよび露光方法 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7292326B2 (en) * | 2004-11-30 | 2007-11-06 | Molecular Imprints, Inc. | Interferometric analysis for the manufacture of nano-scale devices |

| JP2006267191A (ja) * | 2005-03-22 | 2006-10-05 | Pentax Industrial Instruments Co Ltd | 露光装置 |

| JP4185941B2 (ja) | 2006-04-04 | 2008-11-26 | キヤノン株式会社 | ナノインプリント方法及びナノインプリント装置 |

| JP4848832B2 (ja) | 2006-05-09 | 2011-12-28 | 凸版印刷株式会社 | ナノインプリント装置及びナノインプリント方法 |

| JP5096965B2 (ja) * | 2008-02-29 | 2012-12-12 | キヤノン株式会社 | 位置合わせ方法、位置合わせ装置、露光方法及びデバイス製造方法 |

| US8432548B2 (en) | 2008-11-04 | 2013-04-30 | Molecular Imprints, Inc. | Alignment for edge field nano-imprinting |

| CN101833238A (zh) | 2009-03-13 | 2010-09-15 | 鸿富锦精密工业(深圳)有限公司 | 压印模具 |

| NL2005259A (en) * | 2009-09-29 | 2011-03-30 | Asml Netherlands Bv | Imprint lithography. |

| NL2005430A (en) * | 2009-11-24 | 2011-05-25 | Asml Netherlands Bv | Alignment and imprint lithography. |

| JP5697345B2 (ja) * | 2010-02-17 | 2015-04-08 | キヤノン株式会社 | インプリント装置、及び物品の製造方法 |

| NL2005975A (en) * | 2010-03-03 | 2011-09-06 | Asml Netherlands Bv | Imprint lithography. |

| JP5539011B2 (ja) * | 2010-05-14 | 2014-07-02 | キヤノン株式会社 | インプリント装置、検出装置、位置合わせ装置、及び物品の製造方法 |

| JP5597031B2 (ja) | 2010-05-31 | 2014-10-01 | キヤノン株式会社 | リソグラフィ装置及び物品の製造方法 |

| JP2012084732A (ja) * | 2010-10-13 | 2012-04-26 | Canon Inc | インプリント方法及び装置 |

| CN102096348B (zh) * | 2010-12-09 | 2013-01-02 | 西安交通大学 | 提高压印对准过程中莫尔条纹图像质量的数字莫尔条纹方法 |

| JP5637931B2 (ja) * | 2011-05-17 | 2014-12-10 | キヤノン株式会社 | インプリント装置、インプリント方法およびデバイス製造方法 |

| JP5938218B2 (ja) * | 2012-01-16 | 2016-06-22 | キヤノン株式会社 | インプリント装置、物品の製造方法およびインプリント方法 |

| JP6066565B2 (ja) * | 2012-01-31 | 2017-01-25 | キヤノン株式会社 | インプリント装置、および、物品の製造方法 |

| JP6333039B2 (ja) * | 2013-05-16 | 2018-05-30 | キヤノン株式会社 | インプリント装置、デバイス製造方法およびインプリント方法 |

| JP6242099B2 (ja) * | 2013-07-23 | 2017-12-06 | キヤノン株式会社 | インプリント方法、インプリント装置およびデバイス製造方法 |

| JP6097704B2 (ja) * | 2014-01-06 | 2017-03-15 | キヤノン株式会社 | インプリント装置、インプリント方法及び物品の製造方法 |

| JP2015170815A (ja) * | 2014-03-10 | 2015-09-28 | キヤノン株式会社 | インプリント装置、アライメント方法及び物品の製造方法 |

| US10331027B2 (en) * | 2014-09-12 | 2019-06-25 | Canon Kabushiki Kaisha | Imprint apparatus, imprint system, and method of manufacturing article |

| JP2016100366A (ja) * | 2014-11-18 | 2016-05-30 | キヤノン株式会社 | リソグラフィ装置、及び物品の製造方法 |

| JP6570914B2 (ja) * | 2015-08-03 | 2019-09-04 | 東芝メモリ株式会社 | インプリント方法 |

| JP6799397B2 (ja) * | 2015-08-10 | 2020-12-16 | キヤノン株式会社 | インプリント装置、および物品の製造方法 |

-

2013

- 2013-04-03 JP JP2013078093A patent/JP6188382B2/ja not_active Expired - Fee Related

-

2014

- 2014-04-01 CN CN201410127464.9A patent/CN104102090B/zh not_active Expired - Fee Related

- 2014-04-01 US US14/231,827 patent/US9946156B2/en not_active Expired - Fee Related

- 2014-04-02 KR KR1020140039142A patent/KR101788362B1/ko active IP Right Grant

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005167030A (ja) | 2003-12-03 | 2005-06-23 | Sony Corp | マスクおよび露光方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20140120844A (ko) | 2014-10-14 |

| US20140300016A1 (en) | 2014-10-09 |

| US9946156B2 (en) | 2018-04-17 |

| CN104102090A (zh) | 2014-10-15 |

| JP2014203935A (ja) | 2014-10-27 |

| CN104102090B (zh) | 2017-12-29 |

| JP6188382B2 (ja) | 2017-08-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101788362B1 (ko) | 임프린트 장치, 물품의 제조 방법 및 위치정렬 장치 | |

| KR102206936B1 (ko) | 패턴 형성 방법, 리소그래피 장치, 리소그래피 시스템, 및 물품의 제조 방법 | |

| CN110083009B (zh) | 压印方法、压印装置和器件制造方法 | |

| US9921469B2 (en) | Imprint method, imprint apparatus, and method of manufacturing article | |

| KR101676195B1 (ko) | 임프린트 장치, 임프린트 방법 및 물품의 제조 방법 | |

| KR101989652B1 (ko) | 임프린트 방법, 임프린트 장치 및 물품의 제조 방법 | |

| KR102004624B1 (ko) | 패턴 성형 방법 및 물품의 제조 방법 | |

| US9971256B2 (en) | Imprint apparatus, imprint method, and method of manufacturing article | |

| US10011057B2 (en) | Imprint apparatus, and method of manufacturing article | |

| US20140272174A1 (en) | Pattern formation method and pattern formation device | |

| JP2016063219A (ja) | インプリント装置、インプリントシステム及び物品の製造方法 | |

| US20160207248A1 (en) | Imprint apparatus, imprinting method, and method of manufacturing articles | |

| KR102563573B1 (ko) | 임프린트재에 패턴을 형성하는 방법 및 장치 | |

| US9927701B2 (en) | Detection apparatus, imprint apparatus, and method of manufacturing article | |

| US10754257B2 (en) | Method of manufacturing pattern and article manufacturing method | |

| JP6381721B2 (ja) | インプリント方法、インプリント装置及びデバイス製造方法 | |

| JP2019024089A (ja) | インプリント方法、インプリント装置および物品の製造方法 | |

| JP6792669B2 (ja) | パターン形成方法、リソグラフィ装置、リソグラフィシステムおよび物品製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20140402 |

|

| PG1501 | Laying open of application | ||

| A201 | Request for examination | ||

| AMND | Amendment | ||

| PA0201 | Request for examination |

Patent event code: PA02012R01D Patent event date: 20150402 Comment text: Request for Examination of Application Patent event code: PA02011R01I Patent event date: 20140402 Comment text: Patent Application |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20160302 Patent event code: PE09021S01D |

|

| AMND | Amendment | ||

| E601 | Decision to refuse application | ||

| PE0601 | Decision on rejection of patent |

Patent event date: 20160927 Comment text: Decision to Refuse Application Patent event code: PE06012S01D Patent event date: 20160302 Comment text: Notification of reason for refusal Patent event code: PE06011S01I |

|

| AMND | Amendment | ||

| PX0901 | Re-examination |

Patent event code: PX09011S01I Patent event date: 20160927 Comment text: Decision to Refuse Application Patent event code: PX09012R01I Patent event date: 20160502 Comment text: Amendment to Specification, etc. Patent event code: PX09012R01I Patent event date: 20150402 Comment text: Amendment to Specification, etc. |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20170103 Patent event code: PE09021S01D |

|

| AMND | Amendment | ||

| PX0701 | Decision of registration after re-examination |

Patent event date: 20170720 Comment text: Decision to Grant Registration Patent event code: PX07013S01D Patent event date: 20170119 Comment text: Amendment to Specification, etc. Patent event code: PX07012R01I Patent event date: 20161222 Comment text: Amendment to Specification, etc. Patent event code: PX07012R01I Patent event date: 20160927 Comment text: Decision to Refuse Application Patent event code: PX07011S01I Patent event date: 20160502 Comment text: Amendment to Specification, etc. Patent event code: PX07012R01I Patent event date: 20150402 Comment text: Amendment to Specification, etc. Patent event code: PX07012R01I |

|

| X701 | Decision to grant (after re-examination) | ||

| PR0701 | Registration of establishment |

Comment text: Registration of Establishment Patent event date: 20171013 Patent event code: PR07011E01D |

|

| PR1002 | Payment of registration fee |

Payment date: 20171013 End annual number: 3 Start annual number: 1 |

|

| PG1601 | Publication of registration | ||

| PR1001 | Payment of annual fee |

Payment date: 20201005 Start annual number: 4 End annual number: 4 |

|

| PC1903 | Unpaid annual fee |