KR100614456B1 - 디스플레이 기판 전극의 도전율을 향상시키는 방법 - Google Patents

디스플레이 기판 전극의 도전율을 향상시키는 방법 Download PDFInfo

- Publication number

- KR100614456B1 KR100614456B1 KR1020007012603A KR20007012603A KR100614456B1 KR 100614456 B1 KR100614456 B1 KR 100614456B1 KR 1020007012603 A KR1020007012603 A KR 1020007012603A KR 20007012603 A KR20007012603 A KR 20007012603A KR 100614456 B1 KR100614456 B1 KR 100614456B1

- Authority

- KR

- South Korea

- Prior art keywords

- transparent conductive

- resist

- strip

- metal

- substrate

- Prior art date

Links

- 229910052751 metal Inorganic materials 0.000 title claims abstract description 143

- 239000002184 metal Substances 0.000 title claims abstract description 143

- 239000000758 substrate Substances 0.000 title claims abstract description 100

- 238000000034 method Methods 0.000 claims abstract description 81

- 230000000737 periodic effect Effects 0.000 claims abstract description 11

- 239000007769 metal material Substances 0.000 claims abstract description 6

- 229920002120 photoresistant polymer Polymers 0.000 claims description 33

- 238000005530 etching Methods 0.000 claims description 21

- 238000000576 coating method Methods 0.000 claims description 17

- 239000011248 coating agent Substances 0.000 claims description 16

- 229910052802 copper Inorganic materials 0.000 claims description 16

- 239000000463 material Substances 0.000 claims description 14

- 238000000151 deposition Methods 0.000 claims description 12

- 238000000059 patterning Methods 0.000 claims description 5

- 239000007788 liquid Substances 0.000 claims description 4

- 230000003213 activating effect Effects 0.000 claims description 3

- 229910052782 aluminium Inorganic materials 0.000 claims description 3

- 239000011344 liquid material Substances 0.000 claims description 3

- 239000000956 alloy Substances 0.000 claims description 2

- 229910045601 alloy Inorganic materials 0.000 claims description 2

- 229910052804 chromium Inorganic materials 0.000 claims description 2

- 229910052737 gold Inorganic materials 0.000 claims description 2

- 229910052742 iron Inorganic materials 0.000 claims description 2

- 229910052759 nickel Inorganic materials 0.000 claims description 2

- 229910052697 platinum Inorganic materials 0.000 claims description 2

- 229910052709 silver Inorganic materials 0.000 claims description 2

- 239000000126 substance Substances 0.000 claims description 2

- 229910052718 tin Inorganic materials 0.000 claims description 2

- 229910052719 titanium Inorganic materials 0.000 claims description 2

- 239000012780 transparent material Substances 0.000 claims description 2

- 229910052721 tungsten Inorganic materials 0.000 claims description 2

- 238000001465 metallisation Methods 0.000 abstract description 3

- 239000010408 film Substances 0.000 description 40

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 15

- 239000010949 copper Substances 0.000 description 15

- 238000002834 transmittance Methods 0.000 description 13

- 239000004020 conductor Substances 0.000 description 10

- HEMHJVSKTPXQMS-UHFFFAOYSA-M Sodium hydroxide Chemical compound [OH-].[Na+] HEMHJVSKTPXQMS-UHFFFAOYSA-M 0.000 description 9

- 239000004973 liquid crystal related substance Substances 0.000 description 9

- 239000011159 matrix material Substances 0.000 description 7

- 230000008021 deposition Effects 0.000 description 6

- 239000010409 thin film Substances 0.000 description 6

- 238000001035 drying Methods 0.000 description 5

- 238000013459 approach Methods 0.000 description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 229910052760 oxygen Inorganic materials 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- 238000004544 sputter deposition Methods 0.000 description 4

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 238000005336 cracking Methods 0.000 description 3

- 229910003460 diamond Inorganic materials 0.000 description 3

- 239000010432 diamond Substances 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000007772 electrode material Substances 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 229920000307 polymer substrate Polymers 0.000 description 3

- 238000004528 spin coating Methods 0.000 description 3

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 238000009472 formulation Methods 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 238000007747 plating Methods 0.000 description 2

- IUVCFHHAEHNCFT-INIZCTEOSA-N 2-[(1s)-1-[4-amino-3-(3-fluoro-4-propan-2-yloxyphenyl)pyrazolo[3,4-d]pyrimidin-1-yl]ethyl]-6-fluoro-3-(3-fluorophenyl)chromen-4-one Chemical compound C1=C(F)C(OC(C)C)=CC=C1C(C1=C(N)N=CN=C11)=NN1[C@@H](C)C1=C(C=2C=C(F)C=CC=2)C(=O)C2=CC(F)=CC=C2O1 IUVCFHHAEHNCFT-INIZCTEOSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 238000004070 electrodeposition Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000009477 glass transition Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000003999 initiator Substances 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 239000007791 liquid phase Substances 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 230000005499 meniscus Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 229920000306 polymethylpentene Polymers 0.000 description 1

- 239000011116 polymethylpentene Substances 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134336—Matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/13439—Electrodes characterised by their electrical, optical, physical properties; materials therefor; method of making

-

- C—CHEMISTRY; METALLURGY

- C09—DYES; PAINTS; POLISHES; NATURAL RESINS; ADHESIVES; COMPOSITIONS NOT OTHERWISE PROVIDED FOR; APPLICATIONS OF MATERIALS NOT OTHERWISE PROVIDED FOR

- C09K—MATERIALS FOR MISCELLANEOUS APPLICATIONS, NOT PROVIDED FOR ELSEWHERE

- C09K2323/00—Functional layers of liquid crystal optical display excluding electroactive liquid crystal layer characterised by chemical composition

- C09K2323/06—Substrate layer characterised by chemical composition

- C09K2323/061—Inorganic, e.g. ceramic, metallic or glass

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/805—Electrodes

- H10K50/81—Anodes

- H10K50/814—Anodes combined with auxiliary electrodes, e.g. ITO layer combined with metal lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/805—Electrodes

- H10K59/8051—Anodes

- H10K59/80516—Anodes combined with auxiliary electrodes, e.g. ITO layer combined with metal lines

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Geometry (AREA)

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

본 발명은 투명한 도전성 전극에 인접하여 패터닝된 보조 금속층을 마련하여, 디스플레이 기판 위의 투명한 도전성 전극의 도전율을 향상시키는 방법에 관한 것이다. 본 발명의 방법은 a) 금속 피막(26) 또는 레지스트 스트립(24)을 증착시키기 위하여 경사지게 조준된 금속 재료 비임(28)을 사용하거나, b) 금속 피막에 레지스트 잔류물을 제공하거나, 또는 연속된 금속 피막에 하부의 투명한 도전성층과 동시에 에칭될 수 있는 주기적인 배열의 구멍을 형성함으로써, 보조 금속층(26)을 투명한 도전성 전극(22)과 정렬시킬 필요성을 배제시킨다.

Description

본 발명은 도전성을 향상시키기 위한 보조 금속층이 있는 투명한 도전성 전극을 갖는 디스플레이 기판 및 높은 정밀도의 정렬 공정 없이 보조 금속층을 마련하는 방법에 관한 것이다.

화상 소자(픽셀)를 활성화시키기 위하여 전계가 인가되어야 하고 광학적 투명성이 필수적인 많은 디스플레이 장치의 용례에 있어서 투명한 도전성 산화물(Tansparent Conductive Oxide; TCO) 박막이 사용되고 있다. 예를 들면, 액정 디스플레이 기판은 종종 평행한 TCO 물질 스트립을 전극으로 채용하고 있다. 디스플레이 장치에서, 한 쌍의 그러한 기판이 이들 기판의 대향하는 TCO 전극 스트립이 매트릭스를 형성하는 방향으로 조합되는 경우, 임의의 쌍의 TCO 스트립이 교차하는 디스플레이의 영역은 픽셀을 형성한다. 한 쌍의 교차하는 TCO 스트립 사이에 전계를 인가하면, 이들 사이에 배치된 액정이 재배향될 수 있다. 이러한 재배향은 빛이 활성화된 영역을 투과하는 방식에 영향을 준다. 예를 들면, 액정 디스플레이를 투과하는 편광은 활성화된 픽셀 영역의 외부로 투과하는 빛에 대하여 수직으로 편광되어 활성화된 픽셀을 통해서 투과된다. 그러면, 빛이 디스플레이의 임의의 지점을 통해서 투과되고 있는 동안 디스플레이가 활성화된 영역에서 어둡게 나타나도록 편광기를 채용할 수도 있다.

픽셀이 활성 및 불활성화될 수 있는 속도는 결정적으로 TCO 전극의 도전율에 좌우된다. 대형 또는 고해상도의 디스플레이를 채용하는 용례를 비롯한 많은 용례에서, 픽셀이 온/오프될 수 있는 속도에 상응하는 보다 짧은 "재생률"이 필요할 수 있다. 특히 픽셀 밀도가 높은 디스플레이에서 TCO 전극의 도전율을 상승시키면 보다 짧은 재생률이 실현될 수 있다. TCO 전극의 도전율을 향상시키면 균일성을 개선시킴으로써 디스플레이의 화질(appearance)을 향상시킨다.

TCO 층의 도전율을 향상시키는 한 가지 방법은 그것을 높은 온도(약 250℃ 이상)에서 어닐링(annealing)하는 것이다. 기판 재료로서 유리를 사용하는 경우, 이 방법을 행할 수 있다. 그러나, 면적이 큰 액정 디스플레이와 같은 많은 용례에서, 유리 기판은 너무 무거우며, 따라서 중합체 기판이 선호되고 있다. 액정 디스플레이에 있어서 기판 재료로서 적합한 중합체 재료는 종종 유리 천이 온도를 가지며, TCO 층의 도전율을 향상시키기 위하여 어닐링하는 데에 필요한 높은 온도보다는 훨씬 낮은 융점을 갖는다. 따라서, 중합체 기판이 채용되는 경우, 고온 어닐링 작업은 TCO 전극의 도전율을 향상시키고자 할 때 사용 가능한 선택 사항은 아니다.

TCO 층의 도전율을 향상시키는 다른 한 가지 수단은 TCO 층과 접촉하는 보조 금속층을 마련하는 것이다. 전형적으로, 금속층은 TCO 전극 위에 증착된 금속 재료의 좁은 스트립 또는 선 형태를 취한다. 금속 스트립을 부가하면, 다음과 같은 관계식에 따른 비저항을 낮춤으로써 TCO 전극의 도전율을 향상시킨다.

식 중, RT 는 전극 전체의 비저항이고, R TCO 는 TCO 층의 비저항이며, RM 은 금속 스트립의 비저항이다. 전형적인 경우이지만, RM 이 RTCO 보다 훨씬 작으면, RT 는 RM 에 접근하며, 따라서 전극은 피복되지 않은 TCO 전극의 비저항보다 훨씬 낮은 비저항을 갖게 된다. 금속층이 전극의 길이를 따라 연속되는 한 도전율은 향상된다. 픽셀이 작고, 따라서 전극도 작은 고밀도 디스플레이의 경우, 도전율을 저하시키는 균열 또는 파단이 발생하기 쉬울 수도 있는 작은 보조 금속층을 필요로 하기 때문에, 이는 중요하다.

최종 장치의 투명성이 종종 필수적이고, 또 TCO 전극의 도전율을 향상시키기에 충분한 두께의 금속층은 광학적으로 불투명한 것이 일반적이기 때문에, 금속 스트립이 TCO 전극을 실질적으로 덮지 않는 것이 중요하다. 더욱이, 독립적으로 어드레스할 수 있는 TCO 전극 스트립이 기판 위에 상호 근접하게 배치되는 경우, 각 금속 스트립과 각 TCO 스트립과의 정렬은 필수적이다. 정렬되지 않으면, 금속 스트립이 인접한 TCO 전극과 교차하여 인접한 전극을 가로질러 전기적인 쇼트를 초래할 수도 있다. 이러한 정렬은, 전극 스트립이 더 길거나 또는 더 근접하여 에러의 발생 여지가 더 적은 고해상도의 대형 디스플레이에서는 특히 결정적으로 중요하다.

전형적으로, 보조 금속 스트립을 갖는 TCO 전극을 제조하는 데에는 3 가지 방법(또는 그 변형 방법) 중 한 가지가 사용되고 있다. 첫번째 방법으로, 미리 존재하는 TCO 스트립 위에 마스크를 통해서 얇은 금속 스트립을 직접 증착시킬 수 있다. 이는 증착용 마스크의 패터닝된 전극과의 정밀한 정렬을 필요로 한다. 두번째 방법으로, 아직 전극으로 패터닝되지 않은 TCO 층을 갖는 기판상에 금속 스트립을 증착시킬 수도 있다. 그 후, TCO 층의 소정 부분들과 어떤 불필요한 금속을 제거하여 보조 금속 스트립을 갖는 TCO 전극을 형성한다. 이는 에칭 마스크 또는 레이저 스크라이브(laser scribe)의 패터닝된 스트립과의 정밀한 정렬을 필요로 한다. 마지막으로, 기판 위에 금속 스트립을 직접 증착시키고, 이어서 금속 스트립의 상면 위에 직접 TCO 스트립을 증착시킬 수 있다. 역시, 이는 증착용 마스크의 패터닝된 금속 스트립과의 정밀한 정렬을 필요로 한다. 이들 각 방법에 있어서, 필요한 정밀 정렬 공정은 공정 효율을 떨어뜨리고, 결함을 초래할 위험이 있다.

정밀 정렬 공정이 없이 TCO 전극에 보조 금속을 마련하는 방법이 캐시(Cathey) 명의의 미국 특허 제5,342,477호에 개시되어 있다. 이 방법은 각기 투명한 전도성 재료 스트립 위에 적층된 투명한 이산화규소 스트립을 구비하는 복수 개의 투명한 전극을 갖는 기판을 마련하는 공정을 포함한다. 그 후, 전체 표면에 고도전성 재료를 피복한다. 그 후, 고도전성 재료를 전극 상면 위에 있는 그 전도성 재료가 제거되어 전극들 사이의 영역이 노출될 때까지 수직으로 에칭한다. 남는 것은 투명한 전극 적층체의 각 측부를 따라 배치되는 도전성 재료의 "배선(runner)"이다. 캐시 명의의 특허에 개시된 방법은 고정밀 정렬 공정을 필요로 하지 않지만, 그것의 실현 가능성에 영향을 주는 중요한 결점을 갖는다. 우선, 이 방법은 비교적 두꺼운 전극 적층체에 의존하므로, 도전성 재료가 증착 중에 전극의 가장자리에 누적되고 에칭 공정 후에도 남게 된다. 그 전극 적층체는 실질적으로 투명하지만, 전극의 두께가 증대되면 디스플레이의 휘도가 떨어지게 된다. 둘째, 도전성 "배선"은 전극의 투명한 도전성 부분의 측부에만 접촉한다. 투명한 도전성 부분은 얇아야 하기 때문에, 도전성 배선과 투명한 도전성 스트립 사이의 전체 표면 접촉 면적은 매우 좁다. 그러므로, 투명한 도전성 스트립으로부터 도전성 배선이 박리될 수 있다. 이러한 박리가 발생하는 경우, 도전성 배선은 아무런 작용도 하지 못한다.

정밀한 정렬 공정 없이 TCO 전극의 가장자리에 보조 금속 스트립을 마련하는 다른 한 가지 방법은 일본 특개평4-360124호에서 논의되고 있다. 이 공보에서 개시된 방법에서는, TCO 전극을 통상적인 포토리소그래피에 의하여 기판 위에 형성한다. TCO 재료 위에 포토레지스트가 잔류하며, 전극의 노출된 측부 가장자리에 금속을 전착시킨다. 그 후, 포토레지스트를 제거하여 가장자리를 따라 금속 스트립을 갖는 일련의 TCO 전극을 남게 한다. 이 방법은 상기 캐시 명의의 특허에 개시된 방법의 결점 중 몇 가지를 해결하고 있지만, 금속 도금 기술에 의존함으로써, 전극 사이에 과도한 금속이 누적될 위험이 있는데, 이 금속은 디스플레이의 인접한 전극들을 쇼트시키게 된다. 이러한 위험은 전극간 거리가 매우 작을 수 있는 고밀도 디스플레이의 경우에 특히 현저하다.

본 발명은 사전에 패터닝된 전극에 관하여 정밀한 정렬을 필요로 하지 않고 독립적으로 어드레스 가능한 TCO 전극의 도전율을 향상시키기 위하여 보조 금속층을 패터닝하는 방법을 제공함으로써 전술한 단점들을 해결한다.

본 발명의 한 가지 실시예에 있어서, 본 발명의 방법은 우선, 위에 투명한 도전성층이 있는 실질적으로 투명한 기판을 마련하는 공정을 포함한다. 다음에, 투명한 도전성층 위에 평행한 레지스트 스트립을 형성하여, 투명한 도전성층의 소정 영역을 레지스트에 의해 덮이지 않은 상태로 남긴다. 그 후에, 조준된 금속 비임(collimated metal beam)을 사용하여 투명한 도전성층과 레지스트 스트립 위에 금속 피막을 증착시키는데, 이 경우 조준된 비임은 평행한 레지스트 스트립에 의해서 부분적으로 차단되는 각도로 입사한다. 이는 레지스트에 의하여 덮이지 않은 투명한 도전성층의 부분들을 노출된 상태로 남긴다. 그 후, 투명한 도전성층의 노출된 부분을 제거한다. 마지막으로, 레지스트 스트립을, 그 위에 있는 임의의 금속 피막과 함께 제거하여, 기판 위에 각기 보조 금속 스트립을 갖고, 또 독립적으로 어드레스 가능한 복수 개의 전극을 형성한다.

다른 한 가지 실시예에 있어서, 본 발명의 방법은 우선 실질적으로 투명한 기판을 마련하는 공정을 포함한다. 다음에, 이 투명한 기판 위에 평행한 레지스트 스트립을 형성한다. 그 후, 기판과 레지스트 스트립 위에 금속을 증착시켜, 금속 재료가 레지스트 스트립의 측부에 확실하게 증착되게 한다. 그 후, 금속 피막을 에칭하여, 레지스트 스트립의 상면과 이들 레지스트 스트립 사이의 기판 영역으로부터 금속 피막을 제거하지만, 레지스트 스트립의 측부로부터는 금속 피막을 제거하지 않는다. 남는 금속 피막은 레지스트 스트립의 가장자리를 따라서 연속된 금속선을 형성한다. 다음에, 레지스트 스트립, 금속선 및 노출된 기판을 실질적으로 덮도록 투명한 도전성 박막을 증착한다. 마지막으로, 레지스트 스트립을 제거한다. 이로써, 기판 위에는 투명한 도전성 박막의 평행한 스트립이 남는데, 이들 투명한 도전성 박막의 평행한 스트립은 각기 측부에서 연속된 금속선에 의하여 경계를 이룬다. 측부에서 금속선에 의해 경계가 형성된 투명한 도전성 박막의 평행한 스트립은 기판의 표면 위에 독립적으로 어드레스 가능한 전극을 제공하는데, 각 전극은 초기에 형성된 레지스트 스트립의 폭에 상응하는 거리만큼 분리된다.

또 다른 한가지 실시예에 있어서, 본 발명의 방법은 위에 투명한 도전성층이 있는 실질적으로 투명한 기판을 마련하는 공정을 포함한다. 도전성층에 인접하여, 기판과 마주한 표면 위에 또는 투명한 도전성층과 기판 사이에 연속된 금속 피막을 형성한다. 이 연속된 금속 피막은 원형 구멍의 육각형 배열이나 다이아몬드형 구멍의 규칙적 배열과 같은 주기적인 구멍의 배열에 의하여 특징지워진다. 이들 구멍은 기판 요소가 실질적으로 투명하게 남도록 보장한다. 그 후, 투명한 도전성층의 소정 부분들과 이들 부분에 인접한 어떤 금속 피막을 제거함으로써 독립적으로 어드레스 가능한 투명한 전극을 형성한다.

본 발명은 또한 전자 디스플레이 장치에 사용하기에 적합한 기판 요소를 포함한다. 기판 요소는 실질적으로 투명한 기판과 복수 개의 독립적으로 어드레스 가능한 전극을 포함한다. 이들 전극은 투명한 도전성 재료와 주기적 배열의 구멍을 갖는 연속된 금속 피막으로 구성된다.

본 발명의 목적은 보조 금속층의 형성 전에 그 금속층들의 정밀한 정렬을 필요로 하지 않고 TCO 전극에 인접한 보조 금속층을 마련함으로써 TCO 전극의 도전율을 향상시키는 방법을 제공하는 것이다. 본 발명의 또 다른 목적은 TCO 전극에 인접한 보조 금속층을 마련함으로써 액정 디스플레이 기판 위의 TCO 전극의 도전율을 향상시키는 방법을 제공하는 데에 있다. 본 발명의 또 다른 목적은 투명한 도전성층과 패터닝된 금속층을 포함하는 독립적으로 어드레스 가능한 투명한 전극을 갖는 디스플레이 기판 요소를 제공하는 데 있다.

도 1a 내지 도 1e는 본 발명의 방법의 특정 실시예에 포함되는 공정의 개략적인 모식도.

도 2a 내지 도 2g는 본 발명의 방법의 다른 한 가지 실시예에 포함되는 공정의 개략적인 모식도.

도 3a 내지 도 3f는 본 발명의 방법의 특정 실시예에 포함된 공정을 보여주는 개략적인 공정의 개략적인 평면도 및 측면도.

도 4a 내지 도 4e는 본 발명에 채용될 수 있는 여러 가지 금속 피막 패턴의 개략적인 모식도.

본 발명은 투명한 도전성 전극에 보조 금속층을 마련하여 전극의 투명한 성질을 크게 바꾸지 않고 전극의 도전율을 향상시키는 방법을 포함한다. 금속층은 가령 금속 증착용 또는 에칭용 마스크를 미리 패터닝된 전극 구조와 정렬시키는 것과 같은 고정밀 정렬 공정을 사용하지 않고 마련된다. 본 발명에서 마련된 금속층은 특정 용례에 적합한 어떤 도전성 금속 재료여도 좋지만, 증착이나 스퍼터링과 같은 공지된 기술에 의하여 기판 위에 증착될 수 있는 재료를 포함하는 것이 바람직하다. 그러한 재료의 예로는, 한정하는 것은 아니지만, Cr, Cu, Ag, Au, Ni, W, Al, Pt, Ti, Fe, Sn, 이들 금속의 조합 또는 합금이 있다.

구체적인 실시예를 고려하면, 본 발명의 여러 가지 양태가 가장 잘 이해되겠지만, 후술되는 실시예 및 그 실시예에 포함된 실례들은 본 발명의 범위 및 그것을 정하고 있는 청구 범위를 한정하려는 의미는 결코 아니다.

A. 제1 실시예

본 발명의 방법의 한 가지 실시예가 도 1a 내지 도 1e에 도시되어 있다. 우선, 투명한 도전성 전극층(22)이 있는 기판(20)을 포함하는 기판 요소를 마련한다. 기판(20)은 전자 디스플레이 장치에 사용하기에 적합한 실질적으로 투명한 재료이다. 바람직한 기판은 유리 및 임의의 적절한 투명한 중합체 재료를 포함한다. 투명한 도전성층(22)은 바람직하기로는 투명한 도전성 산화물(TCO) 재료로서, 이 TCO 재료는 인듐 주석 산화물(ITO)인 것이 바람직하다.

다음, 도 1b에 도시된 바와 같이, 레지스트 스트립(24)을 마련한다. 레지스트 스트립(24)의 폭 w는 완성된 디스플레이의 픽셀의 폭에 해당한다. 도전성층(22)의 표면 위에 레지스트를 도포하고 그것을 건조시켜 두께 h의 피막을 형성함으로써 레지스트 스트립(24)이 마련된다. 그 후, 레지스트 피막을 특정 파장의 빛에 노출시켜 레지스트 중의 광개시제(photo-initiators)를 활성화시킬 수 있다. 이 레지스트 피막은 마스크를 통해서 빛에 노출되므로, 특정 영역만이 활성화된다. 레지스트가 포지티브 레지스트냐 또는 네가티브 레지스트냐에 따라, 용액 중에서의 헹굼에 의하여 활성화된 영역 또는 비활성화된 영역이 제거될 수 있다. 결과적인 레지스트 피막은 완성된 디스플레이 기판의 픽셀 사이의 비활성 영역(inactive area)에 해당하는 거리 P만큼 분리된 복수 개의 레지스트 스트립이다. 레지스트는 전극 재료와 어떤 악영향을 미치는 반응을 하지 않는 원하는 어떤 레지스트이어도 좋다. 상업적으로 구입할 수 있는 많은 레지스트 제제가 있으며, 특정 레지스트가 선택되면 사용자는 이들 레지스트의 피복, 건조, 활성화 및 제거 공정을 알게 될것이다.

그 후, 도 1c에 도시된 바와 같이, 기판 위에 금속 피막(26)을 증착한다. TCO 표면에 좁은 금속 스트립을 형성하기 위하여, "섀도우 피복(shadow coating)이라 불리는 기술이 채용된다. 섀도우 피복에 있어서는, 대개는 공지의 증착 기술을 사용하여 진공 챔버 중에서 증착될 금속의 조준된 비임(28)이 형성된다. 그 후, 조준된 비임을 기판 요소의 평면에 대하여 소정의 입사각(30)으로 지향시킨다. 레지스트 스트립(24)은 이들 레지스트 스트립 사이의 영역에 단지 폭이 d인 스트립만이 형성되도록 조준된 비임의 일부를 차단하는 기능을 한다. TCO 표면 위의 금속 피막의 폭 d는 다음 식으로 주어진다.

식 중, θ는 기판 요소의 평면을 기준으로 하여 측정한 조준된 비임의 입사각(30)이다. 섀도우 피복 공정은 도 1c에 도시된 바와 같이, 폭이 P-d인 TCO 층의 영역을 노출된 상태로 남긴다.

그 후, 금속 피막을 에칭 장벽으로 사용하여 TCO 층(22)을 에칭한다. 그 결과가 도 1d에 도시되어 있다.

그 후, 레지스트 스트립(24)을 그 레지스트 위에 있는 임의의 금속 피막(26)과 함께 벗겨지도록 떼어내 제거한다. 도 1e에 도시된 결과적인 기판 요소는 복수 개의 독립적으로 어드레스 가능한 전극이 있는 기판(20)을 포함하는데, 각 전극은 TCO 층(22)과 보조 금속층(26)을 갖는다. 보조 금속층은 TCO 전극의 도전율을 향상시킨다. 아울러, 보조 금속층은 종종 불투명하게 할 만큼 충분히 두꺼우므로 어두운 매트릭스(dark matrix)로서 작용한다.

어두운 매트릭스는 디스플레이의 비활성 영역(inactive areas)을 통해서 투과되는 빛을 차단하는 디스플레이 기판 위의 불투명한 물질이다. 이 어두운 매트릭스는 디스플레이의 콘트라스트(contrast)를 향상시킨다. 2 개 이상의 인접한 픽셀이 활성화되어 어둡게 나타나는 경우, 상기 어두운 매트릭스가 없으면 빛이 활성화된 픽셀들 사이의 비활성 영역을 통해서 투과될 수 있다. 이는 활성화된 픽셀이 검은색이 아닌 회색으로 보이게 하여 콘트라스트를 저하시킨다. 어두운 매트릭스가 존재하면 이러한 문제가 경감된다.

어두운 매트릭스는 도 1에 도시된 공정 중에 적용될 수 있다. 노출된 TCO 층의 제거 공정(도 1d에 도시됨) 후에, 그 표면 위에 비전도성의 불투명한 물질을 증착시킬 수 있다. 그러므로, 레지스트 스트립이 제거되는 경우, 결과적인 기판 요소의 구조는 전극들 사이에 어두운 매트릭스로서 작용하는 불투명한 층이 부가되어 도 1e에 도시된 바와 같이 된다. 인접한 전극이 전기적으로 독립된 상태로 유지되도록 상기 불투명한 물질이 비전도성인 것은 중요하다.

실례 A1

일본 도쿄에 소재하는 니폰 제온사(Nippon Zeon Co., Ltd.)가 Zeonex라고 하는 상표명으로 판매하고 있는 폴리메틸펜텐(polymethylpentene) 기판에 두께 80 nm (0.08 ㎛)의 ITO 층을 피복하였다. 그 후에, 상기 ITO 층의 표면 위에, 메사츄세츠, 말보로에 소재하는 시플리사(Shipley Co.)가 Shipley Resist 827이라는 상표명으로 판매하는 포토레지스트를 1500 회전/분(rpm)으로 60 초 동안 스핀 피복법(spin coating)으로 피복하였다. 그 후, 포토레지스트를 75 ㎛ 폭의 평행한 구멍들이 마련된 마스크를 통해서 파장 365 ㎛, 강도 9.8 mW/cm2의 자외선 방사선에 30초 동안 노출시켰다. 그 후, 포토레지스트를 시플리사가 Shipley Developer 354라는 상표로서 판매하는 현상제에 70 초 동안 담궜다. 그 후, 시료를 헹구고 건조시켰다. 이 시점에서, 시료는 도 1b에 도시된 것과 유사하다. 그 후, 표면에 입사각 7°의 조준된 Cr 금속 비임을 사용하여 섀도우 피복(shadow coating)을 행하였다. Cr 피막은 두께가 200 nm(0.2 ㎛) 였다. 그 후에, 시료를 10% HCl 용액에 70 초 동안 담궈서 노출된 ITO 층을 제거하였다. 이어서, 계속 아세톤 초음파 욕조에 담금으로써 남은 레지스트를 제거하였다. 결과적인 기판 요소의 구조는 도 1e에 도시된 것과 유사하다.

B. 제2 실시예

본 발명의 방법의 다른 한 가지 실시예가 도 2a 내지 2g에 도시되어 있다. 우선, 도 2a에 도시된 바와 같은 실질적으로 투명한 디스플레이 기판(32)을 마련한다. 기판(32)은 앞서 논의된 바와 같은 전자 디스플레이 기판 요소에 사용하기에 적합한 어떤 재료라도 좋다.

기판 위에, 도 2a에 도시된 바와 같이 레지스트 스트립(34)을 형성한다. 이들 스트립은 통상적인 포토리소그래피 기술에 의하여 형성된다. 전형적으로, 전체 기판에는 액상 물질을 피복하거나 적층함(lamination)으로써 레지스트가 도포된다. 레지스트를 소정 파장 및 강도의 빛에 선택적으로 노출시키고, 이어서 상기 A. 부분에서 논의된 바와 같이 활성화된 물질을 제거함으로써 패터닝한다. 도 2a의 레지스트 스트립(34)은 도 1b의 레지스트 스트립(24)과 대비될 수 있다. 도 1b에서, 레지스트 스트립의 폭은 완성된 디스플레이 기판 요소 위의 요망되는 전극의 폭에 상응하게 선택된 반면, 도 2a의 레지스트 스트립(34)의 폭은 완성된 디스플레이 기판 요소 위의 전극 사이의 원하는 간극의 폭에 상응하게 선택된다.

다음, 도 2b에 도시된 바와 같이, 기판과 레지스트 스트립 위에 금속(36)을 증착한다. 금속은 증착, 스퍼터링, 화학적 도금, 전착 또는 당업계에 공지된 다른 방법과 같은 어떤 적절한 기술로 증착될 수 있다. 금속은 기판과 레지스트 스트립의 표면을 실질적으로 덮도록 피복하는 것이 바람직하다.

다음, 도 2c에 도시된 바와 같이, 금속 피막 위에 제2 레지스트(38)를 피복한다. 제2 레지스트를 액상으로 피복하여, 레지스트 스트립(34)에 의해 형성된 모서리 영역의 금속 피막에 미니스커스(meniscus)가 형성되게 하는 것이 바람직하다. 예를 들면, 적합한 액상 레지스트는 메사츄세츠, 말보로에 소재하는 시프리사가 Shipley 1818이라는 상표명으로 판매하는 것이다. 액상 레지스트의 미니스커스는 금속 피막 위의 모서리에 부가되는 레지스트가 축적되도록 보장한다. 그러므로, 제2 레지스트를 에칭하여 레지스트 스트립의 상면 위와 레지스트 스트립 사이의 금속 피막을 노출시키면, 도 2d에 도시된 바와 같이 여분의 제2 레지스트 (38)가 금속 피막의 모서리에 남는다. 제2 레지스트의 에칭은 통상적인 이온 반응성 에칭 또는 플라스마 에칭 기술을 사용하여 행하는 것이 바람직하다.

다음, 금속 피막을 에칭하는데, 이 경우 남은 제2 레지스트가 에칭 장벽으로 작용한다. 에칭은 남은 제2 레지스트가 덮인 부분을 제외한 전체 금속 피막을 제거한다. 이에 따라, 레지스트 스트립의 각각의 가장자리를 따라 배치되는 금속 피막의 연속된 스트립 또는 선이 남는다. 그 후, 남은 제2 레지스트를 기판 요소로부터 벗겨내고, 도 2e에 도시된 바와 같이 기판(32), 레지스트 스트립(34) 및 레지스트 스트립의 가장자리에 인접하여 잔류하는 금속 스트립(39)을 남긴다.

다음, 기판 요소 위에 투명한 전도성 물질(39)을 증착하여 도 2f에 도시된 바와 같이 기판의 노출된 영역을 거의 덮는다.

마지막으로, 레지스트 스트립(34)을 그 위에 잔류하는 임의의 투명한 도전성 물질과 함께 제거하여 투명한 도전성 물질로 이루어진 평행한 스트립(39)으로 형성되는 독립적으로 어드레스 가능한 전극을 기판(32)에 남기는데, 각각의 평행한 스트립은 도 2g에 도시된 바와 같이 그것의 가장자리를 따라 배치되는 보조 금속 스 트립(36)을 갖는다.

이 부분에서 설명되고 도 2a 내지 도 2g에 도시되어 있는 본 발명의 방법의 실시예는 특별한 장점을 제공한다. 우선, 각 전극에 대하여 2 개의 보조 금속 스트립(36)이 형성되기 때문에, 전극은 하나의 보조 금속 스트립을 갖는 경우 보다 도전율이 더 높고, 따라서 전극에 더 얇은 도전성층이 형성될 수 있게 하며, 이에 따라 기판 요소를 통한 투과율을 향상시킨다. 추가로, 전극의 비저항은 제2 레지스트의 에칭 양을 조절하는 방식으로 조정가능한 바, 에칭을 많이 할수록 노출되는 금속 피막은 더 많아지며(이는 에칭시 더 많은 금속 피막이 제거됨을 의미함), 이에 따라 보조 금속 스트립의 비저항은 더 높아진다. 둘째로, 보조 금속 스트립은 미리 패터닝된 투명한 도전성 전극으로부터가 아닌 미리 패터닝된 레지스트 스트립으로부터 형성된다. 이는 금속 스트립이 투명한 도전성 전극 재료와는 독립하여 패터닝될 수 있게 하며, 따라서 보다 얇은 전극을 형성할 수 있다. 셋째로, 본 발명의 방법의 이 실시예의 마지막 공정이 금속 부가 공정이 아닌 제거 공정이기 때문에, 인접한 전극을 쇼트시킬 수 있는 과도한 금속을 부가할 위험이 없다.

실례 B1

본 실례는 레지스트 스트립(34)이 기판과 일체인 평행한 릿지인 미소 복제 기판(microreplicated substrate)에서의 도 2a 내지 도 2g에 도시된 공정을 설명한다. 액정 디스플레이 장치의 미소 복제 플라스틱 기판은 웬즈(Wenz) 명의의 미국 특허 제5,268,782호에 설명되어 있다. 약술하면, 액정 디스플레이 기판에는 일련의 미소 복제된 평행한 릿지가 마련될 수 있으며, 각 릿지는, 예컨대 사용되는 액 정의 타입에 따라 기판의 표면으로부터 약 1 ㎛ 내지 20 ㎛의 범위에서 같은 높이까지 돌출된다. 공동 계류 중인 미국 특허 출원 제08/999,287호에서 설명되고 있는 바와 같이, 이들 릿지는 추가적인 마스크 정렬 공정을 사용하지 않고 기판을 추가로 패터닝하는 데에 사용될 수 있다.

미소 복제된 플라스틱 액정 디스플레이 기판의 시료에 스퍼터링 증착법으로 약 2000 Å(0.2 ㎛) 두께의 구리 박막을 피복하였다. 다음, 야스이-세이키(Yasui-Seiki) 마이크로그라비야 피복 장치, CAG-150에서 180R 너얼 롤(knurl roll)을 사용하여, 구리 위에 얇은 포토레지스트층을 피복하였다. Shipley 1818 레지스트를 메틸 에틸 케톤에 희석시켜 고체 농도가 20 %인 용액을 얻음으로써 포토레지스트 용액을 마련하였다. 공기 충돌 오븐 내에서, 100 ℃의 온도로 포토레지스트 피막을 건조시켰다. 건조 후에, 약 1 내지 1.5 ㎛ 두께의 포토레지스트 피막을 얻었다. 그러나, 기판 릿지의 가장자리를 따라 형성되는 피막의 두께는 도포 중의 표면 장력의 효과 때문에 훨씬 더 높았다. 그 후에, 포토레지스트 피막을 RF 산소 플라스마 중에서 에칭하여 채널의 중앙에서 레지스트 피막을 제거하였다. 에칭 후에, 릿지의 가장자리를 따라 포토레지스트가 잔류하도록 에칭 시간을 조정하였다. 산소 플라스마는 100 mTorr의 압력, 100 sccm의 유량 및 120 W의 RF 출력으로 발생되었다. 그러한 조건 하에서의 에칭 시간은 3 분이었다. 포토레지스트의 에칭에 이어서, 노출된 구리를 스프레이 시스템 내에서 10 % H2SO4 용액을 사용하여 약 50 ℃에서 2분 동안 에칭하였다. 다음, 4 % NaOH 용액을 45 ℃에서, 역시 스프레이하여 잔류하는 레지스트를 벗겨냈다. 이에 따라 얻은 기판은 도 2e에 도시된 것과 유사한 방식으로 릿지의 가장자리를 따라 구리선을 가졌다. 다음, 시료에 ITO를 피복하고, 이어서 야스이-세이키 피복 장치를 사용하여 Shipley 1818 포토레지스트를 피복하여 채널 내에 약 2.5 내지 3.0 ㎛ 두께의 레지스트를 형성하였다. 그 후, 시료를 전술한 조건의 산소 플라스마로 2분 동안 에칭하였다. 이에 따라, 릿지의 상면에서만 레지스트가 제거되어, 릿지 사이의 채널에는 ITO를 보호하는 레지스트를 남겼다. 그 후, 릿지 상면에 있는 노출된 ITO를 10 % H2SO4를 사용하여 약 45 ℃에서 1 분 동안 에칭하였다. 마지막으로, 약 50 ℃에서 4 % NaOH를 사용하여 잔류하는 레지스트를 벗겼다. 이렇게 하여 형성된 시료는 도 2에서 ITO 스트립 사이에 도시된 갭이 존재하는 위치에 미소 복제된 평행한 릿지가 존재한다는 것을 제외하고는 도 2g에 도시된 것과 매우 유사하였다.

실례 B2

본 실례는 평면형 기판 위에 구리제 버스선을 형성하는 것을 설명한다. 평면 위에 버스선을 형성하는 공정은 릿지가 형성된 미소 복제 기판에 대한 실례 B1의 공정과 매우 유사하다. 우선, 네가티브 포토레지스트(상표명, Hercules SF 206)를 100 ㎛ PET 박막 위에 적층하고, 표준 리소그래피 공정을 사용하여 패터닝하여 선을 형성하였다. 그 결과는 도 2a에 도시된 바와 같다. 포토레지스트의 패터닝 후에, 기판에 도 2b에 도시된 바와 같이 구리를 피복시켰다. 다음, 야스이-세이킨 마이크로그라비야 피복 장치를 사용하여 기판 위에 Shipley 1818 포토레지스트를 피복하여 도 2c에 도시된 바와 같은 시료를 얻었다. 그 후, Shipley 포토레지스트를 플라스마 에칭하여 도 2d도에 도시된 바와 같이 Hercules SF 206 포 토레지스트의 스트립을 제외하고는 그 Shipley 포토레지스트를 제거하였다. 그 후에, 노출된 구리층을 약 50 ℃의 온도의 10 % H2SO4 용액 중에서 2 분 동안 에칭하였다. 산소 플라스마 중에서 Shipley 포토레지스트를 계속 제거하여 도 2e에 도시된 바와 같은 시료를 얻었다. 구리선들을 포함하는 기판에 도 2f에 도시된 바와 같이 ITO를 피복하였다. Hercules 레지스트를 약 45 ℃의 온도의 4 % NaOH 용액 중에서 2 분 동안 벗겨내서 도 2g에 도시된 바와 같이 기판 위에 패터닝된 ITO 선을 형성하였다.

C. 제3 실시예

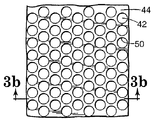

본 발명의 또 다른 한 가지 실시예가 도 3a 내지 도 3f에 도시되어 있다. 우선, 실질적으로 투명한 기판(40)과, TCO 층(42)과, 주기적으로 배열된 구멍을 갖는 갖는 연속된 금속층(44)을 포함하는 기판 요소를 마련한다. 비록 도 3a 내지 3f의 금속층은 TCO 층의 상면 위에 위치하고 있으나, 그 금속층은 기판과 TCO 층 사이에 배치될 수도 있다. 도 3a 내지 도 3f에 도시된 방법의 각 공정이 평면도 및 단면도로 도시되어 있다. 단면도들은 각각 3b-3b선, 3d-3d선 및 3f-3f선을 따라 취한 것이다.

도 3a 및 3b의 평면도에 도시된 바와 같이, 금속층(44)은 주기적 배열의 구멍(50)에 의하여 특징지워진다. 상기 금속층은 증착 또는 스퍼터링과 같은 공지의 기술로 균일한 금속층을 증착함으로써 형성된다. 그 후에, 금속층 위에 레지스트를 피복하고 원하는 패턴을 갖는 마스크를 통해서 빛에 노출시킨다. 그 후, 잔류하는 레지스트 피막이 하부의 금속층을 노출시키는 일련의 구멍을 형성하도록 활성화된 레지스트를 씻어낸다. 그 후, 노출된 금속을 에칭하고 레지스트를 제거한다. 이에 따른 금속층은 주기적인 배열의 구멍을 갖는 연속된 층이다. 독립적으로 어드레스 가능한 투명한 도전성 전극이 이 단계에서는 아직 형성되어 있지 않기 때문에, 포토레지스트 마스크를 어떤 특별한 배향으로 정렬시킬 필요가 없다.

각 구멍의 형상 및 이들 구멍의 주기적 배열은 후술 되는 바와 같이 많은 형태를 취할 수 있다. 구멍의 형상 및 배열은 금속층의 도전율 및 기판 요소의 투명성 모두에 영향을 미친다. 단순화하기 위하여, 도 3a 내지 도 3f에는 원형 구멍이 육각형 배열로 배치된 금속층이 도시되어 있다.

다음, 도 3c 및 도 3d에 도시된 바와 같이, 레지스트의 스트립(46)을 마련한다. 레지스트 스트립(46)의 폭은 완성된 디스플레이의 픽셀의 폭에 해당한다. 레지스트 스트립(46)은 표면에 레지스트를 피복하고 건조시켜 피막을 형성함으로써 마련된다. 그 후, 레지스트 피막을 그 레지스트 내의 광개시제를 활성화시키기 위하여 특정 파장의 빛에 노출시켜도 된다. 단지 특정 영역만이 활성화되도록 레지스트 피막을 마스크를 통해서 빛에 노출시킨다. 레지스트가 포지티브 레지스트인가 또는 네가티브 레지스트인가에 따라, 용액 중에서의 헹굼에 의하여 활성화된 영역 또는 비활성화된 영역이 제거될 수 있다. 결과적인 레지스트 피막은 디스플레이의 픽셀 사이의 비활성 영역에 해당하는 거리만큼 분리되어 있는 복수 개의 레지스트 스트립이다. 그 레지스트는 전극 재료와 양립성이 있는 어떤 원하는 레지스트이라도 좋다. 상업적으로 입수 가능한 레지스트 제제가 많이 있으며, 사용자는 특정 레지스트가 선택되면 이들 레지스트의 피복, 건조, 활성화 및 제거 공정을 알 것이다.

다음, 레지스트 스트립에 의하여 덮이지 않은 금속 및 TCO 층의 소정 영역을 에칭으로 제거한다. 그 후, 레지스트 피막을 제거하여 도 3e 및 도 3f에 도시된 기판 요소를 형성할 수도 있다. 이들 도면에서도 볼 수 있는 바와 같이, 기판 요소는 실질적으로 투명한 기판(40)과 독립적으로 어드레스 가능한 전극을 포함하고, 이들 전극은 각기 TCO 층(42) 및 주기적인 배열의 구멍(50)에 의하여 특징지워지는 연속된 금속층(44)을 갖는다.

독립적으로 어드레스 가능한 전극의 연속된 금속층은 다기능을 발휘한다. 우선, 금속층은 피복되지 않은 TCO 전극에 비하여 전극의 도전율을 향상시킨다. 둘째, 주기적 배열의 구멍은 금속층이 전기적으로 연속될 수 있게 하는 한편, 기판 요소의 투명도에는 최소한의 영향을 미친다. 셋째, 금속층이 전극의 전체 폭을 덮기 때문에, 정밀한 정렬 공정을 필요로 하지 않는다. 오히려, 동일한 에칭 마스크를 사용하여 금속 및 TCO 층이 함께 제거되므로, 정밀한 정렬을 필요로 하는 금속층을 위한 별도의 마스크를 사용할 필요가 없다. 마지막으로, 금속층의 조직은 기계적 안정성을 제공한다. 많은 용례에 있어서, 중합체 기판을 갖는 대형 디스플레이가 바람직할 수 있다. 이들 기판은 종종 가요성이어서 처리 중에 예기치 않게 굴곡되거나, 뒤틀리거나, 또는 찌그러질 수 있다. 그러한 응력은 TCO 전극 또는 단일 보조 금속 스트립의 균열을 야기할 수 있다. 그러나, 주기적 배열의 구멍을 갖는 금속층은 복수 개의 도전로(導電路)를 제공하므로, 균열로 인한 전극의 손상 및 도전율 손실 가능성이 감소된다. 금속층에 사용될 수 있는 다른 구멍 형상 및 배열 구조의 실례가 도 4a 및 도 4e에 도시되어 있다. 이들 배열 구조를 투과하는 빛의 투과율은 구멍의 면적 밀도에 의하여 정하여진다.

다이아몬드 형상 구멍의 배열이 도 4a에 도시되어 있다. 이 패턴은 4 변을 갖는 구멍으로서, 각변의 길이는 a 이고, 구멍들 사이의 수직 거리는 d이며, 꼭지각이 θ인 구멍들에 의하여 형성된다. 이 구조의 투과율 T는 다음 식과 같다.

그러므로, d가 작아질수록 T는 100 %에 접근한다.

정방형 배열의 정방형 홀이 도 4b에 도시되어 있다. 각 정방형 홀은 한 변의 길이가 a이고, 구멍들 사이의 거리는 b이다. 그러므로, 이 패턴의 투과율은 다음 식으로 주어진다.

역시, b가 작아질수록, 이 패턴의 투과율은 100 %에 접근한다.

도 4c에는 육각형 배열의 원형 구멍이 도시되어 있다. 각 원형 구멍의 반경은 r이고 이들 구멍의 중심간 거리는 d이다. 이 패턴의 투과율은 다음과 같다.

이 패턴의 최대 투과율은 90.7 %, 즉 d = 2r인 경우다. 규칙적 배열의 등변 삼각형 쌍들이 도 4에 도시되어 있다. 거리 a는 인접한 삼각형의 정점 사이의 거리이고, 거리 b는 인접한 삼각형의 밑변간 거리이며, d는 삼각형 구멍의 한 변의 길이이다. 이 패턴의 투과율은 다음과 같다.

그러므로, a 또는 b 중 어느 것 또는 이들 모두를 감소시키면 투과율은 더 높아진다.

마지막으로, 육각형 배열의 육각형 구멍이 도 4e에 도시되어 있다. 육각형 구멍의 각 변의 길이는 a이고, 구멍들 사이의 간격은 b이다. 이 패턴의 투과율은 다음과 같이 주어진다.

b가 감소하면, T는 100 %에 접근한다.

실례 C1

a = 51 ㎛, d = 10 ㎛, θ= 45°의 도 4a에 도시된 바와 같은 다이아몬드 격자 마스크를 사용하였다. 이 마스크의 투과율 또는 구경비는 61 % 였다. 패터닝된 금속 피막을 형성하기 위하여, 우선 PET 기판 위에 구리를 100 nm(0.1 ㎛) 두께까지 증착시켰다. 구리 피막의 시트 저항(sheet resistance)은 0.74 Ω/square인 것으로 측정되었다. 그 후, 구리 표면에 Shipley 818 포토레지스트를 2000 rpm으로 40 초 동안 스핀 코팅법으로 피복하고, 105 ℃에서 30 분 동안 건조시켰다. 그 후, 포토레지스트를 파장이 365 nm이고 강도가 12.9 mW/cm2인 자외선광에 15 초 동안 노출시켰다. 포토레지스트의 활성화된 영역을 헹궈서 구리 표면의 다이아몬드형 부분을 노출시켰다. 노출된 구리를 묽은 FeCl3 용액으로 에칭하여 다이아몬드형 구멍을 만들었다. 이 실례에 있어서는 과도 에칭(over-etching)으로 인하여, 구리 패턴의 폭 d는 이상적인 10 ㎛가 아닌 5 ㎛였다. 그 후, 포토레지스트를 제거하였으며, 시료에 ITO를 피복하였다. 결과적인 시트 저항은 25 Ω/square인 것으로 측정되었으며, 광투과율은 가시광선 스펙트럼 중에서 두 표면간 반사 손실을 포함하여, 70 % 였으며, 패턴의 구경비는 78 %였다.

실례 C2

구리 피막의 두께가 20 nm(0.2 ㎛)였고, 과도 에칭이 최소화된 것을 제외하고는 실례 C1에서와 동일한 절차를 수행하였다. 결과적인 시트 저항은 4.3 Ω/square였고, 광투과율은 65 %였다.

실례 C3

사용한 마스크의 치수가 a = 190 ㎛, d = 10 ㎛, 그리고 θ= 45°인 것을 제외하고는 실례 C1과 동일한 절차를 수행하였다. 또한, 사용한 금속은 알루미늄이었고, 두께 100 nm(0.1 ㎛)까지 피복하였다. 패터닝 및 ITO 피복 후의 결과적 인 시트 저항은 10 Ω/square였고, 광투과율은 78 %였다

본 발명에 따르면, 디스플레이 장치의 투명한 도전성 전극에 보조 금속층을 형성하여 전극의 도전율을 향상시킬 수 있으며, 또한 이들 보조 금속층을 형성함에 있어서 높은 정밀도의 정렬 공정을 필요로 하지 않기 때문에, 생산성이 대폭 향상된다.

Claims (10)

- 투명한 도전성 전극의 도전율을 향상시키는 방법으로서,위에 투명한 도전성층(22)이 있는 실질적으로 투명한 기판(20)을 마련하는 공정과;상기 투명한 도전성층(22) 위에 평행한 레지스트 스트립(24)을 형성하여, 투명한 도전성층(22)의 소정 영역이 상기 레지스트에 의하여 덮이지 않은 상태로 남게 하는 공정과;조준된 금속 재료 비임(28)을 사용하여 투명한 도전성층(22)과 레지스트 스트립(24) 위에 금속 피막(26)을 증착하는 공정으로서, 상기 조준된 비임은 평행한 레지스트 스트립에 의하여 부분적으로 차단되는 각도(30)로서 입사하여 덮이지 않은 투명한 도전성층(22)의 소정 부분들이 노출된 채 남도록 하는 공정과;투명한 도전성층(22)의 노출된 부분을 제거하는 공정; 그리고레지스트 스트립(24)과 그 레지스트 스트립 위에 있는 임의의 금속 피막(26)을 제거하여 기판에 독립적으로 어드레스 가능한 복수 개의 전극을 형성하는 공정을 포함하는 것인 투명한 도전성 전극의 도전율 향상 방법.

- 투명한 도전성 전극의 도전율을 향상시키는 방법으로서,제1 주표면을 갖는 실질적으로 투명한 기판(32)을 마련하는 공정과;기판의 소정 영역이 노출된 채 남도록 기판(32)의 매끈한 주표면 위에 레지스트 스트립(34)을 패터닝하는 공정으로서, 각각의 상기 레지스트 스트립은 기판에 인접한 하연부, 이 하연부와 반대측의 상연부 및 2 개의 측연부를 갖게 되는 공정과;상기 레지스트 스트립(34)과 기판(32)의 노출된 영역들을 덮도록 금속을 증착시키는 공정과;금속의 소정 부분들을 선택적으로 제거하여, 레지스트 스트립(34)의 측부 가장자리를 따라 연속된 금속 스트립(36)을 형성하는 공정과;레지스트 스트립(34), 금속 스트립(36) 및 기판의 노출된 영역(32)을 거의 덮도록 투명한 전도성층(39)을 증착시키는 공정; 그리고상기 레지스트 스트립과 이 레지스트 스트립(34)의 상연부에 인접한 임의의 금속(36) 및 투명한 도전성층(39)의 소정 부분들을 제거하여 기판 위에 독립적으로 어드레스 가능한 전극을 형성하는 공정으로서, 전극의 적어도 일부가 투명한 도전성층(39)의 스트립을 포함하고, 각 도전성층의 스트립은 남아 있는 연속된 금속 스트립(36)에 의하여 경계가 형성되는 측연부를 갖게 되는 공정을 포함하고, 상기 금속의 소정 부분을 선택적으로 제거하여 레지스트 스트립의 측부 가장자리를 따라 연속된 금속 스트립을 형성하는 공정은, (a) 과잉의 액상 물질이 레지스트 스트립의 측연부 근처에서 금속 위에 남도록 금속 위에 액상 물질을 피복하는 공정과; (b) 액상 물질을 경화시켜 제2 레지스트(38)를 형성하는 공정과; (c) 제2 레지스트(38)를 백에칭(back etching)하여 레지스트 스트립(34)의 측연부 근처의 과잉 물질만이 남도록 하는 공정과; (d) 노출된 금속(36)을 에칭으로 제거하는 공정과; (e) 남은 제2 레지스트(38)를 제거하는 공정을 포함하는 것인 투명한 도전성 전극의 도전율 향상 방법.

- 투명한 도전성 전극의 도전율을 향상시키는 방법으로서,제1 주표면을 갖는 실질적으로 투명한 기판(40)을 마련하는 공정과;상기 기판(40)의 주표면에 인접한 투명한 도전성층(42)을 마련하는 공정과;상기 투명한 도전성층(42)에 인접하여, 적어도 일부에 주기적인 배열의 구멍을 갖는 연속적인 금속 피막(44)을 형성하는 금속 피막 형성 공정과;투명한 도전성층(42)의 소정 부분들과 이 소정 부분들 위에 있는 금속 피막(44)을 제거하여 기판 위에 복수 개의 독립적으로 어드레스 가능한 전극을 형성하는 공정을 포함하며, 상기 금속 피막에 있는 구멍의 크기는 각 전극의 크기보다 작아서, 각 전극에는 복수 개의 구멍이 나타나는 것인 투명한 도전성 전극의 도전율 향상 방법.

- 제1항 내지 제3항 중 어느 하나의 항에 있어서, 투명한 도전성층은 투명한 도전성 산화물인 것인 투명한 도전성 전극의 도전율 향상 방법.

- 제1항 내지 제3항 중 어느 하나의 항에 있어서, 금속 재료는 Cr, Cu, Ag, Au, Ni, W, Al, Pt, Ti, Fe, Sn, 또는 이들의 조합 및 합금인 것인 투명한 도전성 전극의 도전율 향상 방법.

- 제3항에 있어서, 주기적인 배열의 구멍을 갖는 연속된 금속 피막을 형성하는 공정은, 금속 피막을 증착시키는 공정과, 이 금속 피막 위에 포토레지스트를 피복하는 공정과, 레지스트를 적절한 파장 및 강도의 빛에 노출시켜 제거될 금속 피막의 영역에 인접한 포토레지스트 영역을 활성화시키는 공정과, 포토레지스트의 활성화된 영역을 제거하여 금속 피막의 영역을 노출시키는 공정과, 금속 피막의 노출된 영역을 에칭하는 공정과, 남은 포토레지스트를 제거하는 공정을 포함하는 것인 투명한 도전성 전극의 도전율 향상 방법.

- 제3항에 있어서, 투명한 도전성층의 일부와 그 위의 소정의 금속 피막을 제거하는 공정은, 투명한 도전성층과 금속 피막에 인접한 포토레지스트 스트립을 형성하는 공정과, 포토레지스트 스트립을 통해서 상기 투명한 도전성층과 그 위의 소정의 금속 피막의 실질적으로 평행한 스트립형 부분들을 선택적으로 에칭하여 기판 위에 독립적으로 어드레스 가능한 전극을 형성하는 공정과, 포토레지스트를 제거하는 공정을 포함하는 것인 투명한 도전성 전극의 도전율 향상 방법.

- 삭제

- 삭제

- 삭제

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/076,165 | 1998-05-12 | ||

| US09/076,165 US6037005A (en) | 1998-05-12 | 1998-05-12 | Display substrate electrodes with auxiliary metal layers for enhanced conductivity |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20010043511A KR20010043511A (ko) | 2001-05-25 |

| KR100614456B1 true KR100614456B1 (ko) | 2006-08-23 |

Family

ID=22130346

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020007012603A KR100614456B1 (ko) | 1998-05-12 | 1999-03-31 | 디스플레이 기판 전극의 도전율을 향상시키는 방법 |

Country Status (8)

| Country | Link |

|---|---|

| US (2) | US6037005A (ko) |

| EP (2) | EP1469341A1 (ko) |

| JP (1) | JP2002514790A (ko) |

| KR (1) | KR100614456B1 (ko) |

| AU (1) | AU3374099A (ko) |

| CA (1) | CA2331044A1 (ko) |

| DE (1) | DE69918436T2 (ko) |

| WO (1) | WO1999059024A2 (ko) |

Families Citing this family (46)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3737176B2 (ja) * | 1995-12-21 | 2006-01-18 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| JP3907804B2 (ja) * | 1997-10-06 | 2007-04-18 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| JP2000098116A (ja) * | 1998-09-18 | 2000-04-07 | Canon Inc | 素子又は素子作製用モールド型の作製方法 |

| JP4434411B2 (ja) | 2000-02-16 | 2010-03-17 | 出光興産株式会社 | アクティブ駆動型有機el発光装置およびその製造方法 |

| JP3617458B2 (ja) | 2000-02-18 | 2005-02-02 | セイコーエプソン株式会社 | 表示装置用基板、液晶装置及び電子機器 |

| US7022910B2 (en) | 2002-03-29 | 2006-04-04 | Konarka Technologies, Inc. | Photovoltaic cells utilizing mesh electrodes |

| US6841008B1 (en) * | 2000-07-17 | 2005-01-11 | Cypress Semiconductor Corporation | Method for cleaning plasma etch chamber structures |

| JP2002131773A (ja) * | 2000-10-26 | 2002-05-09 | Sharp Corp | 液晶表示素子 |

| GB0029315D0 (en) * | 2000-12-01 | 2001-01-17 | Koninkl Philips Electronics Nv | Method of increasing the conductivity of a transparent conductive layer |

| GB0029427D0 (en) * | 2000-12-02 | 2001-01-17 | Koninkl Philips Electronics Nv | Pixellated devices such as active matrix liquid crystal displays |

| GB0102167D0 (en) | 2001-01-27 | 2001-03-14 | Koninl Philips Electronics Nv | Pixellated devices such as active matrix liquid crystal displys and methods of manufacturing such |

| GB0102756D0 (en) * | 2001-02-03 | 2001-03-21 | Koninkl Philips Electronics Nv | Method of improving the conductivity of transparent conductor lines |

| US6798464B2 (en) | 2001-05-11 | 2004-09-28 | International Business Machines Corporation | Liquid crystal display |

| JP2002343580A (ja) * | 2001-05-11 | 2002-11-29 | Pioneer Electronic Corp | 発光ディスプレイ装置及びその製造方法 |

| US7053970B2 (en) * | 2001-07-26 | 2006-05-30 | Nitto Denko Corporation | Liquid crystal display and the method of its fabrication |

| TW588204B (en) * | 2002-03-14 | 2004-05-21 | Wintek Corp | Transparent conduction plate having low junction resistance and manufacturing method thereof |

| US20040188150A1 (en) * | 2003-03-25 | 2004-09-30 | 3M Innovative Properties Company | High transparency touch screen |

| US20050156512A1 (en) * | 2003-12-30 | 2005-07-21 | Vadim Savvateev | Electroluminescent devices with at least one electrode having apertures and methods of using such devices |

| KR101026804B1 (ko) | 2004-02-20 | 2011-04-04 | 삼성전자주식회사 | 유기 전계 발광 표시장치의 보조전극 형성방법 |

| KR101026982B1 (ko) * | 2004-06-03 | 2011-04-11 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이 기판과 제조방법 |

| KR100620851B1 (ko) * | 2004-06-14 | 2006-09-19 | 엘지전자 주식회사 | 유기 전계발광 표시소자 및 그 제조방법 |

| KR100692865B1 (ko) * | 2004-10-29 | 2007-03-09 | 엘지전자 주식회사 | 유기 전계발광표시소자 및 그 제조방법 |

| US7160583B2 (en) * | 2004-12-03 | 2007-01-09 | 3M Innovative Properties Company | Microfabrication using patterned topography and self-assembled monolayers |

| JP4595565B2 (ja) * | 2005-01-31 | 2010-12-08 | 株式会社デンソー | 自発光表示装置 |

| US7992293B2 (en) * | 2006-04-04 | 2011-08-09 | Hanita Coatings R.C.A. Ltd | Method of manufacturing a patterned conductive layer |

| US20090165296A1 (en) * | 2006-04-04 | 2009-07-02 | Yoash Carmi | Patterns of conductive objects on a substrate and method of producing thereof |

| TW200818981A (en) * | 2006-08-30 | 2008-04-16 | Sumitomo Chemical Co | Organic electroluminescence device |

| EP1978407A1 (en) * | 2007-03-28 | 2008-10-08 | CRF Societa'Consortile per Azioni | Method for obtaining a transparent conductive film |

| WO2008122027A2 (en) | 2007-04-02 | 2008-10-09 | Konarka Technologies, Inc. | Novel electrode |

| CN101304640B (zh) * | 2007-05-09 | 2011-03-30 | 深圳富泰宏精密工业有限公司 | 电子产品的壳体及其制造方法 |

| FR2917897B1 (fr) * | 2007-06-25 | 2010-05-28 | Univ Rennes | Multicouche transparent et conducteur |

| JP5571870B2 (ja) * | 2007-09-21 | 2014-08-13 | 株式会社東芝 | 極微細構造を有する光透過型金属電極およびその製造方法 |

| CN101939698B (zh) * | 2007-12-14 | 2014-09-17 | 3M创新有限公司 | 制备电子器件的方法 |

| JP5283926B2 (ja) * | 2008-02-25 | 2013-09-04 | 株式会社東芝 | 光透過型金属電極およびその製造方法 |

| FR2928463B1 (fr) * | 2008-03-04 | 2010-12-03 | Saint Gobain | Dispositif electrochrome comportant un maillage. |

| EP2620523B1 (en) * | 2008-06-30 | 2018-06-13 | 3M Innovative Properties Company | Method of forming a microstructure |

| EP2311301B1 (en) * | 2008-06-30 | 2012-04-25 | 3M Innovative Properties Company | Method of forming a patterned substrate |

| FR2934417B1 (fr) | 2008-07-25 | 2010-11-05 | Centre Nat Rech Scient | Composants electroniques a encapsulation integree |

| TWI459436B (zh) * | 2008-10-27 | 2014-11-01 | Tpk Touch Solutions Inc | The Method of Making Double - sided Graphic Structure of Touch Circuit |

| KR101070114B1 (ko) * | 2009-09-15 | 2011-10-05 | 삼성전기주식회사 | 디스플레이용 어레이 기판 및 디스플레이용 기판의 제조 방법 |

| WO2012109494A2 (en) * | 2011-02-09 | 2012-08-16 | Kinestral Technologies, Inc. | Electrochromic multi-layer devices with spatially coordinated switching |

| EP2929417A4 (en) | 2012-12-07 | 2016-07-20 | 3M Innovative Properties Co | METHOD FOR PRODUCING TRANSPARENT CONDUCTORS ON A SUBSTRATE |

| CN103021291B (zh) * | 2012-12-27 | 2015-06-03 | 广东威创视讯科技股份有限公司 | 一种高像素密度led显示屏 |

| KR102254683B1 (ko) * | 2013-07-31 | 2021-05-21 | 쓰리엠 이노베이티브 프로퍼티즈 캄파니 | 패턴화된 나노와이어 투명 전도체들에 대한 전자 컴포넌트들의 본딩 |

| US20160266496A1 (en) * | 2015-03-10 | 2016-09-15 | Uab Research Foundation | Fabrication and encapsulation of micro-circuits on diamond and uses thereof |

| TWI677123B (zh) * | 2018-11-29 | 2019-11-11 | 機光科技股份有限公司 | 去定位器及使用該去定位器的發光裝置 |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS4942437A (ko) * | 1972-04-05 | 1974-04-22 | ||

| JPS6019608B2 (ja) * | 1978-10-03 | 1985-05-17 | シャープ株式会社 | 電極パタ−ン形成方法 |

| JPH0685032B2 (ja) * | 1985-10-17 | 1994-10-26 | キヤノン株式会社 | カイラルスメクティック液晶素子 |

| JPS6365063A (ja) * | 1986-09-08 | 1988-03-23 | Ricoh Co Ltd | 補助金属電極付き透明電極の形成方法 |

| JPS6432233A (en) * | 1987-07-28 | 1989-02-02 | Sharp Kk | Liquid crystal display device |

| JP2694229B2 (ja) * | 1988-03-07 | 1997-12-24 | 株式会社 半導体エネルギー研究所 | 電気光学装置用電極の作製方法 |

| US5187601A (en) * | 1988-03-07 | 1993-02-16 | Semiconductor Energy Laboratory Co., Ltd. | Method for making a high contrast liquid crystal display including laser scribing opaque and transparent conductive strips simultaneously |

| JPH0216529A (ja) * | 1988-07-05 | 1990-01-19 | Seiko Epson Corp | 透明電極の低抵抗化方法 |

| JPH02228629A (ja) * | 1989-02-28 | 1990-09-11 | Sharp Corp | 液晶表示装置 |

| JPH03125443A (ja) * | 1989-10-09 | 1991-05-28 | Sharp Corp | 実装基板の電極及び該実装基板の電極を有する液晶表示装置 |

| JPH03245527A (ja) * | 1990-02-23 | 1991-11-01 | Rohm Co Ltd | 微細加工方法 |

| JP2652072B2 (ja) * | 1990-02-26 | 1997-09-10 | キヤノン株式会社 | 遮光層の形成方法 |

| JP2601932B2 (ja) * | 1990-04-13 | 1997-04-23 | インターナシヨナル・ビジネス・マシーンズ・コーポレーシヨン | 液晶表示装置およびその製造方法 |

| US5282068A (en) * | 1990-11-08 | 1994-01-25 | Canon Kabushiki Kaisha | Liquid crystal display with opaque insulating layer and metal layer at and wider than inter-electrode gap and method of manufacturing |

| JPH04280227A (ja) * | 1991-03-07 | 1992-10-06 | Fuji Photo Film Co Ltd | 液晶表示素子の製造方法 |

| JPH04360124A (ja) * | 1991-06-07 | 1992-12-14 | Hitachi Ltd | 液晶表示素子 |

| KR970000359B1 (ko) * | 1991-09-26 | 1997-01-08 | 가부시기가이샤 도오시바 | 액정표시장치 |

| US5163220A (en) * | 1991-10-09 | 1992-11-17 | The Unites States Of America As Represented By The Secretary Of The Army | Method of enhancing the electrical conductivity of indium-tin-oxide electrode stripes |

| JP2877588B2 (ja) * | 1991-10-28 | 1999-03-31 | ローム株式会社 | 金属酸化物薄膜のパターン形成法 |

| US5268782A (en) * | 1992-01-16 | 1993-12-07 | Minnesota Mining And Manufacturing Company | Micro-ridged, polymeric liquid crystal display substrate and display device |

| JP2823178B2 (ja) * | 1992-04-06 | 1998-11-11 | シャープ株式会社 | 金属配線基板及びその製造方法 |

| JPH06148661A (ja) * | 1992-11-12 | 1994-05-27 | Matsushita Electric Ind Co Ltd | 表示装置用基板の製法 |

| US5342477A (en) * | 1993-07-14 | 1994-08-30 | Micron Display Technology, Inc. | Low resistance electrodes useful in flat panel displays |

| US5426266A (en) * | 1993-11-08 | 1995-06-20 | Planar Systems, Inc. | Die bonding connector and method |

| TW340192B (en) * | 1993-12-07 | 1998-09-11 | Sharp Kk | A display board having wiring with three-layered structure and a display device including the display board |

| EP0742682B1 (en) * | 1995-05-12 | 2005-02-23 | STMicroelectronics, Inc. | Low-profile socketed integrated circuit packaging system |

| US5646480A (en) * | 1995-06-19 | 1997-07-08 | Northrop Grumman Corporation | Metal assist structure for an electroluminescent display |

| JPH09230359A (ja) * | 1996-02-27 | 1997-09-05 | Matsushita Electric Ind Co Ltd | 液晶素子とその製造方法 |

-

1998

- 1998-05-12 US US09/076,165 patent/US6037005A/en not_active Expired - Lifetime

-

1999

- 1999-03-31 KR KR1020007012603A patent/KR100614456B1/ko not_active IP Right Cessation

- 1999-03-31 WO PCT/US1999/007065 patent/WO1999059024A2/en active IP Right Grant

- 1999-03-31 EP EP04015150A patent/EP1469341A1/en not_active Withdrawn

- 1999-03-31 EP EP99915155A patent/EP1084445B1/en not_active Expired - Lifetime

- 1999-03-31 CA CA002331044A patent/CA2331044A1/en not_active Abandoned

- 1999-03-31 DE DE69918436T patent/DE69918436T2/de not_active Expired - Lifetime

- 1999-03-31 JP JP2000548768A patent/JP2002514790A/ja active Pending

- 1999-03-31 AU AU33740/99A patent/AU3374099A/en not_active Abandoned

- 1999-10-22 US US09/425,098 patent/US6198051B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| WO1999059024A2 (en) | 1999-11-18 |

| EP1084445A2 (en) | 2001-03-21 |

| WO1999059024A3 (en) | 2000-01-13 |

| AU3374099A (en) | 1999-11-29 |

| JP2002514790A (ja) | 2002-05-21 |

| DE69918436T2 (de) | 2005-07-28 |

| EP1469341A1 (en) | 2004-10-20 |

| EP1084445B1 (en) | 2004-06-30 |

| CA2331044A1 (en) | 1999-11-18 |

| US6037005A (en) | 2000-03-14 |

| KR20010043511A (ko) | 2001-05-25 |

| DE69918436D1 (de) | 2004-08-05 |

| US6198051B1 (en) | 2001-03-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100614456B1 (ko) | 디스플레이 기판 전극의 도전율을 향상시키는 방법 | |

| JP5512180B2 (ja) | フォトレジストの縁部のバリの形成方法とアレイ基板の製造方法 | |

| CN102116984B (zh) | 液晶显示设备及其制造方法 | |

| US8053295B2 (en) | Liquid crystal display device and method of fabricating the same | |

| JP5741992B2 (ja) | Tft−lcdアレイ基板及びその製造方法 | |

| JP4674926B2 (ja) | 液晶ディスプレイパネル及びその製造方法 | |

| US6498087B2 (en) | Method of increasing the conductivity of a transparent conductive layer | |

| CN105446037B (zh) | 显示基板及其制作方法、显示器件 | |

| KR101717648B1 (ko) | 표시장치 및 그 제조방법 | |

| US5246468A (en) | Method of fabricating a lateral metal-insulator-metal device compatible with liquid crystal displays | |

| RU2069417C1 (ru) | Способ изготовления тонкопленочных транзисторов матриц жидкокристаллических экранов | |

| JP4502575B2 (ja) | 表示装置の配線形成方法 | |

| KR20020071643A (ko) | 액정표시소자 및 그 제조방법 | |

| KR100408030B1 (ko) | 표시소자의 전극패턴 형성방법 | |

| KR20040046384A (ko) | 액정표시장치 및 그 제조방법 | |

| KR20060024061A (ko) | 플렉서블한 액정표시장치용 어레이 기판의 제조 방법 | |

| JP2921503B2 (ja) | 電気的コンタクトの製造方法 | |

| JPS6341083A (ja) | 薄膜半導体素子の製造方法 | |

| KR20070078456A (ko) | 표시장치의 제조방법 | |

| JPH07142951A (ja) | 弾性表面波デバイスの製造方法 | |

| JPH04229833A (ja) | 液晶表示装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20100811 Year of fee payment: 5 |

|

| LAPS | Lapse due to unpaid annual fee |