KR100443436B1 - 절연게이트형반도체장치 - Google Patents

절연게이트형반도체장치 Download PDFInfo

- Publication number

- KR100443436B1 KR100443436B1 KR1019970039449A KR19970039449A KR100443436B1 KR 100443436 B1 KR100443436 B1 KR 100443436B1 KR 1019970039449 A KR1019970039449 A KR 1019970039449A KR 19970039449 A KR19970039449 A KR 19970039449A KR 100443436 B1 KR100443436 B1 KR 100443436B1

- Authority

- KR

- South Korea

- Prior art keywords

- region

- impurity

- channel forming

- forming region

- channel

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 98

- 239000012535 impurity Substances 0.000 claims abstract description 255

- 230000000694 effects Effects 0.000 claims abstract description 59

- 238000000034 method Methods 0.000 claims description 66

- 229910052796 boron Inorganic materials 0.000 claims description 25

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 claims description 24

- 239000013078 crystal Substances 0.000 claims description 22

- 229910052698 phosphorus Inorganic materials 0.000 claims description 21

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 claims description 19

- 239000011574 phosphorus Substances 0.000 claims description 19

- 239000000969 carrier Substances 0.000 claims description 17

- 229910052785 arsenic Inorganic materials 0.000 claims description 11

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 claims description 10

- 229910052760 oxygen Inorganic materials 0.000 claims description 7

- 239000001301 oxygen Substances 0.000 claims description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 6

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 6

- 239000011159 matrix material Substances 0.000 claims description 6

- 229910052795 boron group element Inorganic materials 0.000 claims description 4

- 229910052696 pnictogen Inorganic materials 0.000 claims description 4

- 229910021332 silicide Inorganic materials 0.000 claims description 4

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical group [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 4

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 3

- 229910052799 carbon Inorganic materials 0.000 claims description 3

- 229910052757 nitrogen Inorganic materials 0.000 claims description 3

- 230000000116 mitigating effect Effects 0.000 claims description 2

- 239000000463 material Substances 0.000 claims 5

- 230000007423 decrease Effects 0.000 abstract description 8

- 239000010408 film Substances 0.000 description 60

- 239000010410 layer Substances 0.000 description 46

- 239000000758 substrate Substances 0.000 description 33

- 230000015572 biosynthetic process Effects 0.000 description 19

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 17

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 16

- 229910052710 silicon Inorganic materials 0.000 description 16

- 239000010703 silicon Substances 0.000 description 16

- 238000010586 diagram Methods 0.000 description 12

- 230000003647 oxidation Effects 0.000 description 12

- 238000007254 oxidation reaction Methods 0.000 description 12

- 230000008569 process Effects 0.000 description 9

- 230000004888 barrier function Effects 0.000 description 8

- 230000005684 electric field Effects 0.000 description 8

- 238000005468 ion implantation Methods 0.000 description 7

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- 238000000137 annealing Methods 0.000 description 6

- 238000004519 manufacturing process Methods 0.000 description 6

- 238000000059 patterning Methods 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 5

- 230000005669 field effect Effects 0.000 description 5

- 238000010438 heat treatment Methods 0.000 description 5

- 238000002513 implantation Methods 0.000 description 5

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 5

- 239000011229 interlayer Substances 0.000 description 4

- 238000010884 ion-beam technique Methods 0.000 description 4

- 238000005204 segregation Methods 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 230000002159 abnormal effect Effects 0.000 description 3

- 230000015556 catabolic process Effects 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 230000004913 activation Effects 0.000 description 2

- 239000000654 additive Substances 0.000 description 2

- 230000000996 additive effect Effects 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 2

- 238000010894 electron beam technology Methods 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 238000005224 laser annealing Methods 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- 229910021341 titanium silicide Inorganic materials 0.000 description 2

- PCTMTFRHKVHKIS-BMFZQQSSSA-N (1s,3r,4e,6e,8e,10e,12e,14e,16e,18s,19r,20r,21s,25r,27r,30r,31r,33s,35r,37s,38r)-3-[(2r,3s,4s,5s,6r)-4-amino-3,5-dihydroxy-6-methyloxan-2-yl]oxy-19,25,27,30,31,33,35,37-octahydroxy-18,20,21-trimethyl-23-oxo-22,39-dioxabicyclo[33.3.1]nonatriaconta-4,6,8,10 Chemical compound C1C=C2C[C@@H](OS(O)(=O)=O)CC[C@]2(C)[C@@H]2[C@@H]1[C@@H]1CC[C@H]([C@H](C)CCCC(C)C)[C@@]1(C)CC2.O[C@H]1[C@@H](N)[C@H](O)[C@@H](C)O[C@H]1O[C@H]1/C=C/C=C/C=C/C=C/C=C/C=C/C=C/[C@H](C)[C@@H](O)[C@@H](C)[C@H](C)OC(=O)C[C@H](O)C[C@H](O)CC[C@@H](O)[C@H](O)C[C@H](O)C[C@](O)(C[C@H](O)[C@H]2C(O)=O)O[C@H]2C1 PCTMTFRHKVHKIS-BMFZQQSSSA-N 0.000 description 1

- 241000293849 Cordylanthus Species 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 230000005535 acoustic phonon Effects 0.000 description 1

- 239000003054 catalyst Substances 0.000 description 1

- MLYYVTUWGNIJIB-BXKDBHETSA-N cefazolin Chemical compound S1C(C)=NN=C1SCC1=C(C(O)=O)N2C(=O)[C@@H](NC(=O)CN3N=NN=C3)[C@H]2SC1 MLYYVTUWGNIJIB-BXKDBHETSA-N 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000005247 gettering Methods 0.000 description 1

- 230000020169 heat generation Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000002401 inhibitory effect Effects 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- -1 oxygen ions Chemical class 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- SBEQWOXEGHQIMW-UHFFFAOYSA-N silicon Chemical compound [Si].[Si] SBEQWOXEGHQIMW-UHFFFAOYSA-N 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 238000009279 wet oxidation reaction Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/22—Diffusion of impurity materials, e.g. doping materials, electrode materials, into or out of a semiconductor body, or between semiconductor regions; Interactions between two or more impurities; Redistribution of impurities

- H01L21/225—Diffusion of impurity materials, e.g. doping materials, electrode materials, into or out of a semiconductor body, or between semiconductor regions; Interactions between two or more impurities; Redistribution of impurities using diffusion into or out of a solid from or into a solid phase, e.g. a doped oxide layer

- H01L21/2251—Diffusion into or out of group IV semiconductors

- H01L21/2254—Diffusion into or out of group IV semiconductors from or through or into an applied layer, e.g. photoresist, nitrides

- H01L21/2255—Diffusion into or out of group IV semiconductors from or through or into an applied layer, e.g. photoresist, nitrides the applied layer comprising oxides only, e.g. P2O5, PSG, H3BO3, doped oxides

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823807—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the channel structures, e.g. channel implants, halo or pocket implants, or channel materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8248—Combination of bipolar and field-effect technology

- H01L21/8249—Bipolar and MOS technology

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/0611—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region

- H01L27/0617—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region comprising components of the field-effect type

- H01L27/0623—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region comprising components of the field-effect type in combination with bipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/0619—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE] with a supplementary region doped oppositely to or in rectifying contact with the semiconductor containing or contacting region, e.g. guard rings with PN or Schottky junction

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1025—Channel region of field-effect devices

- H01L29/1029—Channel region of field-effect devices of field-effect transistors

- H01L29/1033—Channel region of field-effect devices of field-effect transistors with insulated gate, e.g. characterised by the length, the width, the geometric contour or the doping structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/15—Structures with periodic or quasi periodic potential variation, e.g. multiple quantum wells, superlattices

- H01L29/158—Structures without potential periodicity in a direction perpendicular to a major surface of the substrate, i.e. vertical direction, e.g. lateral superlattices, lateral surface superlattices [LSS]

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Nanotechnology (AREA)

- Mathematical Physics (AREA)

- Theoretical Computer Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Thin Film Transistor (AREA)

Abstract

단채널 효과를 방지하면서 채널 길이가 짧은 미세한 반도체 장치를 실현한다.

채널 형성 영역(103)에 대하여 인위적이고도 국부적으로 도트 패턴 형상의 불순물 영역(104)을 형성한다. 이 불순물 영역(104)이 드레인측 공핍층(depletion layer)의 채널 형성 영역(103)으로의 확장을 억제하고, 단채널 효과를 방지한다. 또한, 불순물 영역(104)에 의해서 채널 폭 W를 실질적으로 세분화하하고, 그것에 수반하여 생기는 협채널 효과에 의하여 단채널 효과에 의한 한계치 전압의 저하를 완화한다.

Description

본 명세서에서 개시하는 발명은, 결정 반도체 기판, 예를 들면 단결정 실리콘 기판 혹은 SOI 기판(SIMOX 등)을 이용하여 형성된 절연 게이트형 반도체 장치, 특히 절연 게이트형 전계 효과 트랜지스터(이하, 단순히 IG-FET라고 약기한다)의 구성 및 그 제작 방법에 관한 것이다. 특히, 채널 길이가 1μm 이하(대표적으로는 0.01∼0.35μm)의 미세 소자를 제작하는 경우에 효과를 발휘하는 기술이다.

따라서, 본 발명은 IG-FET을 집적화하여 구성된 IC, VLSI, ULSI 등의 여러가지의 반도체 집적화 회로에 응용할 수 있다.

근년에, VLSI 등의 집적화 회로는 점점 미세화의 일로를 걷는 경향에 있으며, 배선의 폭도 0.18μm 이하, 또는 0.1μm 이하와 같은 디프서브미크론 영역의 가공 치수가 요구되고 있다.

지금까지 반도체 소자의 미세화는 스케일링법에 따라서 진행되고 있으며, 미세화가 집적화 회로의 특성 향상을 가져오는 것은 일반적으로 알려져 있었다. 그러나, 서브미크론 영역의 미세 가공이 되면 단순하게는 스케일링법에 따르지 않는 문제가 발생하게 된다.

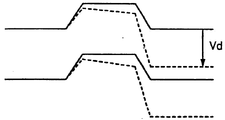

그와 같은 문제로서 단채널 효과라는 현상이 대표적으로 알려져 있다. 단채널 효과란, 게이트 전극의 선폭이 짧아지는, 즉 채널 형성 영역이 짧아짐에 따라서, 채널 형성 영역의 전하가 게이트 전압뿐만 아니라, 소스/드레인 영역의 공핍층(depletion layer) 전하라든지 전계 및 전위 분포의 영향을 크게 받기 때문에 일어나는 현상이다.

이러한 상황을 간략화하여 도 3에 나타낸다. 301은 소스 영역, 302는 드레인 영역, 303은 채널 영역, 304는 게이트 전극이다. 또한, 305로 나타나는 점선은 드레인 전압(Vd)이 작을 때 형성되는 공핍층을 나타낸다.

통상, 채널 영역(303)을 흐르는 전류는 게이트 전압(Vg)만으로써 제어된다. 이 경우, 305로 나타나는 바와 같이, 채널 영역(303) 부근의 공핍층은 채널에 대략 평행하게, 균일한 전계가 형성된다.

그러나, 드레인 전압(Vd)이 높아지면, 드레인 영역(302) 부근의 공핍층이 채널 영역(303), 소스 영역(301)의 쪽으로 확장되고, 306에서 나타나는 실선으로 나타나는 바와 같이, 드레인 공핍층의 전하라든지 전계가 소스 영역(301), 채널 영역(303) 부근의 공핍층으로 영향을 미치게 된다. 즉, 온 전류가 복잡한 전계 분포에 의해 변화하고, 게이트 전압(Vg)만으로 제어하는 것이 곤란한 상황이 되기 때문이다.

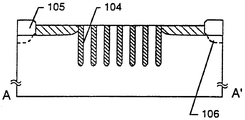

여기에서, 단채널 효과가 생기는 경우에 있어서의 채널 형성 영역 주변의 에너지 상태를 도 4를 이용하여 설명한다. 도 4에 있어서 실선으로 나타내는 상태도는 드레인 전압이 0V일 때의 소스 영역(401), 채널 형성 영역(402), 드레인 영역(403)의 에너지 밴드도이다.

이 상태에서 충분히 큰 드레인 전압(Vd)이 인가되면, 도 4에서 점선으로 나타내는 상태로 변화한다. 즉, 드레인 전압(Vd)에 의해 형성된 드레인 영역(403)의 공핍층 전하라든지 전계가, 소스 및 채널 영역(401,402)의 공핍층 전하에 영향을 주고, 에너지(전위) 상태는 소스 영역(401)으로부터 드레인 영역(403)에 걸쳐서 연속적으로 변화하게 된다.

그리고, 이러한 단채널 효과가 반도체 소자, 예를 들면 IG-FET에 주는 영향으로서는 한계치 전압(Vth)의 저하라든지 펀치스루 현상이 잘 알려져 있다. 또한, 펀치스루 현상에 의해서 드레인 전류에 대한 게이트 전압의 영향이 저하하면 서브스렛숄드 특성이 나빠지는 것도 알려져 있다.

우선, 한계치 전압의 저하는 N 채널형 FET에 대해서도 P채널형 FET에 대해서도 동일하게 나타나는 현상이다. 또한, 이 저하의 정도는 드레인 전압에 의존할 뿐만 아니라, 기판 불순물 농도, 소스/드레인 확산층 깊이, 게이트 산화막 두께, 기판 바이어스 등의 여러 가지의 파라미터에 의존한다.

한계치 전압의 저하는 소비 전력을 작게 하는 의미로서는 바람직하지만, 일반적으로는 집적 회로의 구동 전압이 작아짐으로써 주파수 특성이 높아지지 않는 것과 같은 단점이 문제가 된다.

그래서, 지금까지는 한계치 전압을 제어하기 위한 수단으로서는 채널 형성 영역 전체에, 균일하게 하나의 도전성을 부여하는 불순물 원소를 첨가하여, 그 첨가량으로써 한계치 전압을 제어하는 것이 일반적이었다. 그러나, 이 방법도 역시 단채널 효과 자체를 방지하는 것은 불가능하며, 펀치스루 현상 등이 발생하였다. 또한, 첨가한 불순물이 캐리어를 산란시키기 때문에 캐리어의 이동도를 저하시키는 요인도 되고 있었다.

또한, 펀치스루 현상에 따른 서브스렛숄드 특성의 열화란 서브스렛숄드 계수(S 값)가 커지는, 즉 FET의 스윗칭 특성이 열화하는 것을 의미한다. 여기에서 서브스렛숄드 특성에 미치는 단채널 효과의 영향을 도 5에 도시한다.

도 5는 횡축에 게이트 전압(Vg), 종축에 드레인 전류(Id)의 대수를 받아들인 그래프이고, 501의 영역에서의 기울기(서브스렛숄드 특성)의 역수가 S값이다. 도 5에서는 채널 길이를 서서히 짧게 하였을 때의 특성 변화를 비교하고 있고, 화살표의 방향을 향하여 채널 길이는 짧아지고 있다.

그 결과, 채널 길이가 짧아짐에 따라서 특성의 기울기가 작아진다. 즉 S값이 커지는 경향인 것을 확인할 수 있다. 이것은 채널 길이가 짧아짐에 따라서 FET의 스윗칭 특성이 열화하는 것을 의미한다.

이상은 반도체 소자의 채널 형성 영역의 길이가 극단적으로 짧아진 경우에 생긴 단채널 효과의 설명이지만, 채널 형성 영역의 폭이 극단적으로 좁아진 경우에는 협채널 효과라는 현상도 발생한다.

도 6에 나타내는 것은 일반적인 IG-FET를 채널 방향(소스와 드레인을 연결하는 방향)과 수직인 면에서 분단한 단면도이다. 601은 단결정 실리콘 기판, 602는 선택 산화법으로 형성된 필드 산화막이다. VLSI에서 사용되는 개개의 반도체 소자는 필드 산화막(602)에 의해서 각각 분리되어 있다.

또한, 603은 게이트 전극이고, 게이트 전극(603)에 전압을 인가함으로써 채널 영역(604)이 형성된다. 또, 필드 산화막(602) 아래에는 불순물 영역(605)이 배치되어 있고, 채널 스톱퍼로서 기능한다.

협채널 효과는 채널폭(W)이 좁아짐에 따라서, 채널 영역(604)에 대하여 필드 산화막(602), 불순물 영역(605)의 버즈비크 부분(Bird's Beak)이 크게 영향을 줌에 따라서 야기된다. 구체적으로는, 경계치 전압의 증가라든지 실효 채널폭의 전원전압 의존성 등을 들 수 있다.

현재의 반도체 산업에 있어서는, 극한까지 집적화된 반도체 집적 회로가 요구되며, 개개의 반도체 소자의 미세화를 어디까지 추구할 수 있을지가 열쇠로 되어 있다. 그러나, 디프서브미크론 영역의 핀 패턴을 형성하는 기술이 개발되었다고 해도, 상술한 바와 같은 단채널 효과의 문제가 소자의 미세화를 막는 치명적인 장해로 되어 있었다.

본 발명은 상기 문제점을 감안하여 행해진 것으로, 반도체 소자의 미세화에 따른 단채널 효과를 효과적으로 억제하기 위한 기술을 개시하는 것이다. 그리고, 단채널 효과에 의해서 실현이 곤란했던 디프서브미크론 영역의 미세 소자를 형성가능하게 하는 것을 과제로 한다.

<과제를 해결하기 위한 수단>

본 명세서에서 개시하는 발명의 구성은,

결정 반도체를 이용하여 형성된 소스 영역, 드레인 영역 및 채널 형성 영역과,

상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 적어도 갖는 절연 게이트형 반도체 장치에 있어서,

상기 채널 형성 영역은 캐리어가 이동하는 영역과,

상기 드레인 영역으로부터 상기 채널 형성 영역 및 소스 영역을 향하여 확장되는 공핍층을 피닝(pinning)하기 위해서 인위적이고 또한 국부적으로 형성된 불순물 영역을 갖고,

상기 불순물 영역에는 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소가 첨가되어 있는 것을 특징으로 한다.

또한, 다른 발명의 구성은,

결정 반도체를 이용하여 형성된 소스 영역, 드레인 영역 및 채널 형성 영역과,

상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 적어도갖는 절연 게이트형 반도체 장치에 있어서,

상기 채널 형성 영역은 캐리어가 이동하는 영역과,

상기 드레인 영역으로부터 상기 채널 형성 영역 및 소스 영역을 향하여 확장되는 공핍층을 피닝하기 위해서 인위적이고 또한 국부적으로 형성된 불순물 영역을 가지며,

상기 불순물 영역에는 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소가 첨가되고,

상기 캐리어가 이동하는 영역에서는 캐리어의 불순물 산란을 방지하는 수단 혹은 캐리어의 격자 산란 이외의 요인에 의한 이동도 저하를 방지하는 수단이 설치되는 것을 특징으로 한다.

또한, 다른 발명의 구성은,

결정 반도체를 이용하여 형성된 소스 영역, 드레인 영역 및 채널 형성 영역과,

상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 적어도 갖는 절연 게이트형 반도체 장치에 있어서,

상기 채널 형성 영역은 캐리어가 이동하는 영역과,

불순물 원소의 첨가에 의해 소정의 한계치 전압으로 제어하기 위해서 인위적이고 또한 국부적으로 형성된 불순물 영역을 가지며,

상기 불순물 영역에는 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소가 첨가되어 있는 것을 특징으로 한다.

또한, 다른 발명의 구성은,

결정 반도체를 이용하여 형성된 소스 영역, 드레인 영역 및 채널 형성 영역과,

상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 적어도 갖는 절연 게이트형 반도체 장치에 있어서,

상기 채널 형성 영역은 캐리어가 이동하는 영역과,

불순물 원소의 첨가에 의해 소정의 한계치 전압으로 제어하기 위해서 인위적이고 또한 국부적으로 형성된 불순물 영역을 가지며,

상기 불순물 영역에는 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소가 첨가되며,

상기 캐리어가 이동하는 영역에서는 캐리어의 불순물 산란을 방지하는 수단 혹은 캐리어의 격자 산란 이외의 요인에 의한 이동도 저하를 방지하는 수단이 설치되는 것을 특징으로 한다.

또한, 다른 발명의 구성은,

결정 반도체를 이용하여 형성된 소스 영역, 드레인 영역 및 채널 형성 영역과,

상기 채널 형성 영역에서 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소를 첨가함으로써 인위적이고 또한 국부적으로 형성된 불순물 영역과,

상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 적어도 갖는 절연 게이트형 반도체 장치에 있어서,

상기 불순물 영역은 절연성을 가지고 있고,

상기 채널 형성 영역에서 상기 불순물 영역 이외의 영역에는 상기 불순물 원소가 첨가되지 않은 또는 극미량으로 첨가되는 것을 특징으로 한다.

또, 불순물 영역 이외의 영역에 불순물 원소가 첨가되지 않거나 또는 극미량으로 첨가되어 있는 것은 채널을 형성하는 영역(반도체층)은 진성 또는 실질적으로 진성 영역인 것을 의미한다.

또, 본 명세서에서 진성 영역이란, N형이라든지 P형을 부여하는 불순물 원소 및 탄소, 질소, 산소와 같은 불순물 원소를 의도적으로 첨가하지 않는 영역을 나타낸다. 또한, 실질적으로 진성 영역이란, 의도적으로 N형이라든지 P형을 부여하는 불순물 원소를 첨가하지 않더라도 생기는 도전형을 상쇄한 영역, 또는 한계치 제어가 가능한 범위에서 소스 및 드레인 영역과 동일 도전형을 나타내는 영역을 가리킨다.

또한, 본 명세서에서 진성 또는 실질적으로 진성 영역이란, 인 또는 붕소의 농도가 5×1017atoms/cm3이하이고, 탄소 또는 질소 또는 산소의 농도가 2×1018atoms/cm3이하인 영역을 가리킨다.

또한, 본 발명에 있어서 상기 불순물 원소로서는, N채널형 FET에 대하여는 P형을 부여하는 억셉터(acceptor)가 될 수 있는 13족 원소(대표적으로는 붕소)를 이용할 수 있다. 또한, P채널형 FET에 대해서는 N형을 부여하는 도너(donor)가 될 수 있는 15족 원소(대표적으로는 인, 비소)를 사용할 수 있다.

이러한, 불순물 원소를 첨가하여 형성된 불순물 영역은 채널 형성 영역의 에너지 밴드폭을 시프트시키고, 한계치 전압을 양 음 어느 방향으로 이동시킬 수 있다. 따라서, 해당 불순물 원소의 첨가 농도는 적어도 한계치 전압의 제어가 가능한 농도(대표적으로는 1×1017∼1×1020atoms/cm3, 바람직하게는 1×1018∼1×1019atoms/cm3)로 한다.

상술한 불순물 영역에서 한계치 전압을 제어하기 위한 기판 불순물 농도(전형적인 단결정 실리콘 기판에서는 약 1×1015atoms/cm3정도)의 적어도 100 배 정도의 농도가 필요하기 때문에 1×1017atoms/cm3가 하한이 된다. 또한, 1×1020atoms /cm3를 초과하면 장치의 부담이 커지므로 바람직하지 않다.

또한, 본 명세서 중에서는 결정 반도체로서 단결정 실리콘을 대표예로 하지만, 이 단결정 실리콘이란 현재의 VLSI, ULSI 레벨로 일반적으로 사용되고 있는 수준의 단결정 실리콘은 물론이며, 더욱 고수준의 단결정 실리콘(궁극적으로는 우주공간에서 제작된 이상 상태의 단결정 실리콘)도 포함하고 있는 것으로 한다.

본 발명의 주안점은 채널 형성 영역에 인위적이고 또한 국부적으로 형성된 불순물 영역에 의해 드레인 공핍층의 확장을 효과적으로 억제하여, 종래부터의 문제였던 펀치스루 현상이라든지 그것에 따르는 서브스렛숄드 특성의 열화를 방지하는 것에 있다.

본 출원인은 마치 채널 형성 영역에 불순물 영역의 핀을 형성하는 것과 유사하므로, 본 발명에 의한 IG-FET를 피닝형 트랜지스터라고 부르고 있다. 또, 본 명세서중에 있어「피닝」이란 「억지(抑止)」를 의미하고, 「피닝한다」란 「억지한다」라는 의미로 사용되고 있다.

또한, 채널 길이의 미세화에 따른 단채널 효과에 기인하는 대표적 현상인 한계치 전압의 저하를, 인위적으로 협채널 효과를 생기게 함으로써 완화하는 것도 본 발명의 중요한 구성이다.

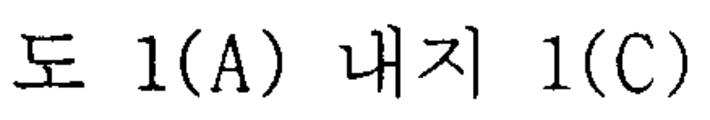

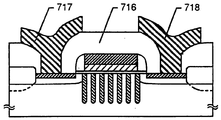

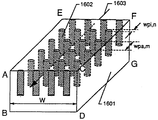

도 1(A)에 나타내는 것은 일반적인 IG-FET의 소스 영역, 드레인 영역 및 채널 형성 영역을 상면에서 보았을 때의 상태의 모식도이다. 또, 101이 소스 영역, 102가 드레인 영역, 103이 채널 형성 영역이다.

그리고, 본 발명의 특징은 채널 형성 영역(103)내에 도트 패턴 상으로 불순물 영역(104)이 형성되어 있는 점이다. 본 발명에 있어서는, 첨가하는 불순물 원소로서 P채널형 FET에 대하여는 인(P) 또는 비소(As), N채널형 FET에 대해서는 붕소(B)를 사용한다.

첨가된 불순물은 채널 형성 영역(103)내에 국부적으로 에너지 밴드폭이 큰 에너지 장벽을 형성한다. 예를 들면, N채널형 FET에 대하여 P형을 부여하는 불순물 원소인 붕소를 첨가한 경우에는, 도 14(A)로 나타내는 상태였던 에너지 밴드를 도 14(B)로 나타내는 상태로 하고, 페르미 레벨(Ef)을 시프트시킴으로써 장벽(△ E)이 더 큰 장벽(△ E') 가 된다. 물론, 페르미 레벨을 시프트시키는 것은 결과적으로 채널 형성 영역의 에너지 밴드를 시프트시키는 것이 분명하다.

이 영역은 역도전성을 가지며, 저항값이 낮은 에너지적으로는 충분히 장벽으로 된다. 마찬가지로 P채널형 FET에 대하여 인 또는 비소를 첨가한 경우에도 역도전성 영역이 형성되어 에너지 장벽으로서 활용할 수 있다.

특히, 도 1(A)에 나타내는 바와 같이 드레인 영역(102)과 채널 형성 영역(103)의 접합부는 가장 전계의 변화가 심한 영역이기 때문에, 이 위치에 불순물 영역(104)을 배치해 두는 것이 바람직하다. 또한, 게이트 전극에 의한 전계가 드레인 영역(102)내에도 미치는 경우는 드레인 영역(102)내에 불순물 영역(104)을 형성하는 것도 가능하다. 반대로 소스 영역(101)내에는 불순물 영역(104)은 형성하지 않는 편이 바람직하다.

또한, 본 발명은 0.2μm, 또한 0.1μm와 같은 디프서브미크론 영역의 미세가공을 필요로 하는 미세 소자를 형성할 때 극히 효과적이다. 따라서, 채널 형성 영역의 길이(채널 길이 또는 소스/드레인간 거리)도 0.01∼1.0μm, 대표적으로는 0.01∼0.35μm와 같은 짧은 것으로 되기 때문에, 불순물 영역은 더욱 가는 패턴을 자르지 않으면 안된다.

예를 들면, 도트 패턴 상의 불순물 영역을 형성할 때 레지스트 마스크를 이용하는 경우에는 레지스트 마스크에 트인 구멍을 설치하는 패터닝은 해상도의 문제로 인해 통상의 노광법을 사용할 수 없다. 그와 같은 경우에는, 패터닝을 전자 묘화법이라든지 FIB 법을 사용하여 행함으로써 미세 패턴을 실현하면 된다.

또한, 이 도트 패턴 상의 불순물 영역은 패터닝에 의해 인위적으로 배열하여 형성되기 때문에, 도 1(A)와 같은 배치뿐만 아니라, 임의의 여러 배치로 하는 것이 가능하다.

다음에, 도 1(A)에 나타내는 소스 영역/채널 형성 영역/드레인 영역의 구성을 갖는 절연 게이트형 반도체 장치(IG- FET)를 구동시켰을 때에, 어떻게 단채널 효과가 억제되는지를 이하에 설명한다.

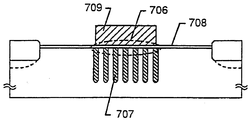

우선, 도 1(A)를 A-A'로 자른 단면도를 도 1(B)에 나타낸다. 105는 필드 산화막, 106은 채널 스톱퍼이다. 불순물 영역(104)의 형상은 조건 설정에 따라서 여러 가지의 변화를 채용할 수 있지만, 여기에서는 이상적으로 산란이 없는 것으로서 막대 형상으로 주입된 경우를 예를 든다.

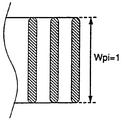

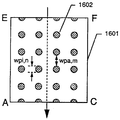

또한, 도 1(A)를 B-B'로 자른 단면도를 도 1(C)에 나타낸다. 107은 필드 산화막이다. 통상, 필드 산화막의 아래에는 채널 스톱퍼가 배치되지만 여기에서는 약기한다. 또한, 어떤 불순물 영역(104)의 폭은 wpi,n으로 나타나며, 그 간격은 wpa,m으로 나타난다. 여기에서, n, m은 채널 형성 영역(103)내에서, wpi,n이 n번째의 불순물 영역의 폭이고, wpa,m이 m번째 불순물 영역간의 간격(캐리어의 이동하는 패스)인 것을 의미한다.

여기까지의 설명은 단지 구조에 대한 설명이지만, 다음에 그 효과에 대한 설명을 한다. 우선, 도 1(B)에 나타내는 구조를 갖는 반도체 장치에 대하여 게이트 전압, 드레인 전압을 인가한 경우에는, 도 2(A)에 나타내는 상태에서 소스측 공핍층(201), 채널측 공핍층(202), 드레인측 공핍층(203)이 형성된다. 즉, 드레인측 공핍층(203)은 불순물 영역(204)이 장벽이 되어 소스측으로의 확장이 방지된 형이 된다.

도 1(B)에서는 판단하기 어렵지만 불순물 영역(204)은 도 1(A)에 나타내는바와 같이 배치되어 있으므로, 채널 형성 영역을 막는 격자 상의 필터로 드레인측 공핍층의 확장을 억제하는 모델을 생각하면 이해하기 쉽다.

따라서, 본 발명에 의한 구조의 반도체 장치에 있어서는, 도 2(A)에 나타내는 바와 같이 공핍층이 실질적으로 서로 간섭하지 않도록 분단된다. 즉, 소스측 공핍층(201), 채널측 공핍층(202)이, 드레인측 공핍층(203)의 영향을 받지 않고 분포하게 하기 때문에, 에너지 상태는 도 2(B)에 나타내는 상태가 된다.

즉, 도 5에 나타낸 종래의 에너지 상태도와 다르고, 채널 영역의 에너지 상태는 거의 게이트 전압에 의한 전계에만 제어되기 때문에, 채널 영역에 대하여 거의 평행한 형상을 가진다. 따라서, 단채널 효과 특유의 펀치스루 현상과 같은 문제가 없고, 드레인 내압이 높은 반도체 장치를 구성할 수 있다.

또한, 도 2(A)에 나타내는 바와 같이, 본 발명에 있어서는 공핍층이 차지하는 부피가, 도 3에 나타낸 바와 같은 종래의 것과 비교하여 감소하고 있기 때문에, 종래부터도 공핍층 전하가 작고, 공핍층 용량이 작은 특징이 있다. 여기에서, S값을 도출하는 식은 다음 식으로 나타난다.

[수학식 3]

즉, 상술하는 바와 같이, 도 5에 나타내는 그래프에 있어서 501로 나타나는 영역에서 기울기 역수를 나타내는 것을 알 수 있다. 또한, 수학식 3의 식은 근사적으로 다음 식으로 나타낼 수 있다.

[수학식 4]

수학식 4에 있어서, k는 볼트먼 정수, T는 절대 온도, q는 전하량, Cd 는 공핍층 용량, Cit는 계면 준위의 등가용량, Cox는 게이트 산화막 용량이다. 따라서, 본 발명에 의하면 공핍층 용량(Cd)이 종래부터도 충분히 작아지므로, S값을 85mV/decade 이하(바람직하게는 70mV/decade 이하)의 작은 값으로 할 수 있는, 즉 우수한 서브스렛숄드 특성을 얻을 수 있다.

또한, 본 발명이 목표로 하는 것은 공핍층 용량(Cd) 및 계면 준위의 등가 용량(Cit)을 0에 가능한 한 가깝게 하는 것이다. 즉, Cd= Cit = 0 이 되는 이상 상태에서의 S값(60mV/decade)에 가깝게 하는 것에 있다.

또한, 채널 형성 영역이 도 1(C)에 나타내는 구조로 되어 있는 것은 단채널 효과에 의한 한계치 전압의 저하를 완화하는 데에 있어서 매우 중요하다. 왜냐하면, 도 1(C)에 나타내는 구조가 의도적으로 협채널 효과를 만들어 내기 위해 필요한 구성이기 때문이다.

예를 들면, 도 1(C)에 나타내는 바와 같은 단면에 착안하면, 채널 형성 영역의 폭(W)은 불순물 영역(104)에 의해서 분단되고, 실질적으로 좁은 채널폭(wpa, m)을 가진 복수의 채널 형성 영역의 집합체라고 간주할 수 있다.

즉, 복수의 좁은 채널폭(wpa,m)을 갖는 영역에서 협채널 효과가 얻어지는 것이다. 매크로적으로 보면 도 1(A)에 나타내는 바와 같이 채널 형성 영역 전체에 이와 같은 협채널 효과가 얻어지는 영역이 존재하기 때문에, 전체적으로도 협채널 효과가 얻어지며, 한계치 전압이 증가한다고 생각된다.

따라서, 채널 길이가 짧아짐으로써 단채널 효과에 의해서 한계치 전압이 저하하였다고해도, 상기의 이유로 협채널 효과에 의해서 한계치 전압을 의도적으로 증가시켜 한계치 제어를 행할 수 있으므로, 결과적으로 한계치 전압의 변화를 완화할 수 있게 된다.

또, 다른 발명의 구성은,

결정 반도체를 이용하여 소스 영역, 드레인 영역 및 채널 형성 영역을 형성하는 공정과,

상기 채널 형성 영역에서 인위적이고 또한 국부적으로 불순물 영역을 형성하는 공정과,

상기 채널 형성 영역 상에 게이트 절연막 및 게이트 전극을 형성하는 공정을 적어도 갖는 절연 게이트형 반도체 장치의 제작 방법에 있어서,

상기 불순물 영역에는 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소가 인위적이고 또한 국부적으로 첨가되어 있는 것을 특징으로 한다.

또한, 다른 발명의 구성은,

결정 반도체를 이용하여 형성된 소스 영역, 드레인 영역 및 채널 형성 영역을 형성하는 공정과,

상기 채널 형성 영역 상에 게이트 절연막 및 게이트 전극을 형성하는 공정을 적어도 갖는 절연 게이트형 반도체 장치의 제작 방법으로서,

상기 드레인 영역으로부터 상기 채널 형성 영역 및 소스 영역을 향하여 확장되는 공핍층을 피닝하기 위한 불순물 영역을 형성하기 위해서, 상기 채널 형성 영역에 대하여 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소를 인위적이면서 국부적으로 첨가하는 공정을 갖는 것을 특징으로 한다.

또, 다른 발명의 구성은,

결정 반도체를 이용하여 형성된 소스 영역, 드레인 영역 및 채널 형성 영역을 형성하는 공정과,

상기 채널 형성 영역 상에 게이트 절연막 및 게이트 전극을 형성하는 공정을 적어도 갖는 절연 게이트형 반도체 장치의 제작 방법으로서,

불순물 원소의 첨가에 의해 소정의 한계치 전압으로 제어하기 위한 불순물 영역을 형성하기 위해서, 상기 채널 형성 영역에 대하여 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소를 인위적이고 또한 국부적으로 첨가하는 공정을 갖는 것을 특징으로 한다.

또한, 다른 발명의 구성은

결정 반도체를 이용하여 소스 영역, 드레인 영역 및 채널 형성 영역을 형성하는 공정과,

상기 채널 형성 영역에서 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소를 첨가함에 의해, 인위적이고 또한 국부적으로 불순물 영역을 형성하는 공정과,

상기 채널 형성 영역 상에 게이트 절연막 및 게이트 전극을 형성하는 공정을 적어도 갖는 절연 게이트형 반도체 장치의 제작 방법에 있어서,

상기 불순물 영역은 절연성을 가지고 있고,

상기 채널 형성 영역에서 상기 불순물 영역 이외의 영역에는 상기 불순물 원소가 첨가되지 않거나 또는 극미량으로 첨가되어 있는 것을 특징으로 한다.

도 1(A) 내지 1(C)은 채널 형성 영역의 구성을 나타내는 도면.

도 2(A) 및 2(B)는 채널 형성 영역의 구성을 나타내는 도면.

도 3은 종래 반도체 장치를 설명하기 위한 도면.

도 4는 채널 형성 영역의 에너지 상태를 나타내는 도면.

도 5는 종래 반도체 장치의 특성을 설명하기 위한 도면.

도 6은 종래 반도체 장치의 구성을 나타내는 도면.

도 7(A) 내지 7(E)은 절연 게이트형 전계 효과 트랜지스터의 제작 공정을 나타내는 도면.

도 8(A) 내지 8(C)은 불순물 영역의 형성 조건을 설명하기 위한 도면.

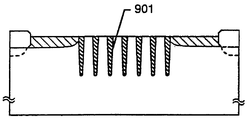

도 9(A) 및 9(B)는 불순물 영역의 깊이 방향의 형상을 나타내는 도면.

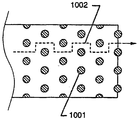

도 10(A) 내지 10(C)은 불순물 영역의 형상 및 배치를 설명하기 위한 도면.

도 11(A) 내지 11(E)은 절연 게이트형 전계 효과 트랜지스터의 구조를 나타내는 도면.

도 12(A) 내지 12(C)는 불순물 영역의 제작 공정을 나타내는 도면.

도 13(A) 및 13(B)은 절연 게이트형 전계 효과 트랜지스터의 구조를 나타내는 도면.

도 14(A) 및 14(B)는 채널 형성 영역의 에너지 상태를 나타내는 도면,

도 15는 채널 형성 영역의 구성을 나타내는 도면.

도 16(A) 내지 16(C)은 채널 형성 영역의 구성을 나타내는 도면.

도 17(A) 및 17(B)은 불순물의 편석(segregation) 상태를 설명하기 위한 도면.

도 18은 반도체 장치의 응용예를 나타내는 도면.

*도면의 주요 부분에 대한 부호 설명*

101: 소스 영역 102: 드레인 영역

103: 채널 형성 영역 104: 불순물 영역(도트 패턴)

105: 필드 산화막 106: 채널 스톱퍼

도 1(A) 내지 1(C)에서, 소스 영역(101), 드레인 영역(102)에서 사이에 끼워진 영역이 채널 형성 영역(103)이다. 본 발명은 채널 형성 영역(103)에 대하여 인위적이고, 또한, 국부적으로 불순물을 첨가하여 불순물 영역(104)을 형성한다.

또한, 불순물 영역(104)은 도트 패턴 상의 형상을 가지며, 규칙성을 갖고서 배열된다. 본 발명에서는 불순물 영역에 첨가하는 불순물로서 N채널형인 경우에는 붕소가, P채널형인 경우에는 인 또는 비소가 사용되기 때문에, 역도전형을 갖는 불순물 영역을 캐리어가 통과하는 것은 아니다. 즉, 불순물 영역 간에만 채널 영역이 형성되고, 그곳을 패스로서 캐리어의 이동이 행해진다.

이상과 같은 구성으로 한 반도체 장치를 구동시킨 경우, 드레인 영역(102)부근에 형성되는 드레인측 공핍층은 불순물 영역(104)에 막혀지는 횡방향(채널 형성 영역 아래)으로 확장되지 않는다. 즉, 소스 영역(101) 및 채널 형성 영역(103)부근의 에너지 상태(전위 상태)가 드레인측 공핍층에 영향을 미치지 않으므로, 각각의 전계는 실질적으로는 독립적으로 형성된다.

따라서, 이른바 단채널 효과에 기인하는 펀치스루 현상이라든지 서브스렛숄드 특성의 열화가 없고, 높은 드레인 내압을 실현할 수 있다.

또한, 불순물 영역(104)은 실질적으로 채널폭을 좁게 하고, 불순물 영역(104) 간에는 이른바 협채널 효과가 생긴다. 따라서, 단채널 효과에 기인하는한계치 전압의 저하를, 협채널 효과에 기인하는 한계치 전압의 증가에 의해서 완화 또는 상쇄하는 것이 가능하다.

이상 구성으로 형성되는 본 발명에 대하여, 이하에 기재하는 실시예에 따라서 상세한 설명을 한다.

[실시예1]

본 발명을 사용하여 단결정 실리콘(규소) 기판 상에 절연 게이트형 전계 효과 트랜지스터를 형성하는 예를 도 7(A) 내지 7(E)를 이용하여 설명한다. 또, 본 실시예에서는 설명을 간략화하기 위해서 P형 실리콘 기판 상에 단체의 N채널형 FET을 형성하는 경우의 예를 나타낸다.

우선, 701은 P형 실리콘 기판이고, 그 위에는 패드 산화막으로서 산화규소막(702), 또한 그 위에는 나중에 선택 산화시 마스크로서 기능하는 질화규소막(703)을 형성한다. 산화규소막(702) 및 질화규소막(703)의 막 두께는 500∼2000Å이면 좋다. (도 7(A))

다음에, 패터닝에 의해 소자 형성 영역에만 질화규소막(703)을 남기고, 그 상태에서 P형을 부여하는 불순물 원소의 이온 주입을 행하며, 또한 그 후, 1000∼1100℃ 온도에서 웨트 산화를 행한다.

이 공정으로 인해 노출된 실리콘 표면은 선택적으로 열산화되고, 도 7(B)에 나타내는 바와 같이 필드 산화막(704)이 형성된다. 필드 산화막(704)은 소자끼리 절연 분리하는 기능을 가진다.

또한, 상술한 이온 주입 공정에 의해 주입된 P형을 부여하는 불순물 원소(B)는 필드 산화막(704)의 아래에 채널 스톱퍼(705)를 형성한다. 이것은 필드 산화막(704) 아래에 채널이 형성되지 않도록 하기 위한 영역으로, 통상, 모체가 되는 기판(본 실시예에서는 P형 실리콘 기판)과 같은 도전성을 갖게 한다.

그리고, 질화규소막(704), 산화규소막(패드 산화막, 705)을 제거하여 도 7(B)에 나타내는 상태가 얻어진다. 이 같은 선택 산화 공정에서는 LOCOS법, PLANOX법, Isoplanar법, SWAMI법 등 여러 가지의 선택 산화를 이용하는 것이 가능하다.

다음에, 채널 형성 영역(706)에 대하여 역도전형을 부여하는 붕소를 첨가하여, 공핍층의 스톱퍼가 되는 불순물 영역(707)을 형성한다. 불순물 원소를 첨가하는 영역(707)은 패터닝에 의해 도시하지 않는 레지스트에 트인 구멍을 설치하여 선택적으로 설계하면 된다. 또한, 미세한 불순물 영역(707)을 형성하기 위해서는 이온 주입법을 이용하여 불순물 원소를 첨가하는 것이 바람직하다.

또, 불순물 영역(707)을 도트 패턴 상으로 하기 위해서는 극히 미세한 리소그라피 기술을 필요로 한다. 그것을 위해서, 전자빔을 사용하는 기술(전자 묘화법)이라든지 이온빔을 사용하는 기술(FIB 법)을 이용하여 도트 패턴 형상의 노광을 행하면 된다.

이 때, 불순물 영역(707)끼리의 간격(wpa,m)은 각각 균일하게 하는 것이 바람직하다. 왜냐하면, 한계치 전압의 불균형(협채널 효과의 불균형에 기인한다)이라든지 발열의 불균형(불순물 영역 사이를 흐르는 전류 밀도의 불균형에 기인한다)을 발생할 우려가 있기 때문이다.

또한, 불순물 영역(707)에 첨가한 불순물 원소는 파네스 어닐, 레이저 어닐,램프 어닐 등으로써 활성화하는 것이 바람직하다. 단, 열확산을 극력 억제하도록 주의한다. 예를 들면, 파네스 어닐의 경우 500∼800℃(바람직하게는 600∼700℃)정도로 행함으로써 불순물의 열확산을 계속 억제하면서, 충분한 활성화를 행할 수 있다.

또한, 이온 주입 시에 기판을 가열함으로써 주입과 동시에 불순물 원소를 활성화해도 된다. 또한, 이온 주입 시의 RF파워를 올림으로써 주입 시점에서의 불순물 원소의 활성화 효율을 향상한다. 이것은 단독 효과를 이용하여 활성화해도 되며, 상술한 어닐 공정과 조합시켜서 활성화해도 된다.

불순물의 첨가가 종료하면, 열산화 처리를 행하여 100∼500Å의 열산화막(708)을 형성한다. 이 열산화 처리에 의해 형성된 얇은 열산화막(708)은 그대로 게이트 절연막으로서 기능한다.

또한, 채널 형성 영역(706)에 있어서 산화막(708)상에 게이트 전극(709)으로서 폴리실리콘막을 형성한다. 폴리실리콘막은 성막하는 단계에서 미리 불순물 원소를 첨가해 두고 도전성을 갖게 하면 좋다. 이렇게 해서 도 7(C)에 나타내는 상태가 얻어진다.

그 후, 도 7(D)에 나타내는 바와 같이, N형을 부여하는 불순물 원소(P 또는 As) 를 첨가하여, 자기 정합적으로 소스 영역(710), 드레인 영역(711)을 형성한다. 그 후, 게이트 전극(709)을 덮도록 하여 질화규소막을 3000Å의 두께로 성막하고, 에칭백법을 사용하여 게이트 전극(709)의 측면에만 사이드웰(712)을 잔존시킨다.

다음에, 이 상태에서 전면에 스팩터법에 의해 티타늄막을 성막하여, 가열,레이저 어닐링, 램프 어닐링 등의 수단에 의한 실리사이드 형성을 행한다. 이 공정에 의해, 소스 영역(710) 및 드레인 영역(711)의 표면 및 게이트 전극(709)의 표면에는 티타늄실리사이드(713∼715)가 형성된다. 티타늄실리사이드(713∼715)는 극히 저저항이기 때문에, 나중에 형성하는 배선과 저항 접촉을 확보하는 데에 있어서 바람직하다.

실리사이드 형성이 종료하면, 층간 절연막으로서 질화규소막(716)을 성막하고, 컨택트홀을 형성하여 소스 전극(717), 드레인 전극(718)을 형성한다. 이렇게해서 도 7(E)에 나타내는 바와 같은 구조의 IG-FET가 완성된다.

본 발명에서는 IG-FET의 채널 형성 영역에 도트 패턴 상으로 불순물 영역을 형성하는 것에 특징이 있지만, 도트 패턴의 형성 장소는 어떤 범위의 조건을 만족할 필요가 있다. 그것에 대해서, 도 8(A) 내지 8(C)를 이용하여 이하에 기재한다.

도 8(A) 내지 8(C)에서, 801은 채널 형성 영역의 일부를 나타낸다. 채널폭은 W 이다. 여기에서, 채널폭(W)내, 도트 패턴(802)이 점유하고 있는 폭을 Wpi라고 정의한다. Wpi의 값으로서는 예를 들면 10∼100 Å도 있으면 충분하다. 또한, 임의의 도트 패턴(802)의 폭을 Wpi,1, Wpi,2, Wpi,3ㆍㆍㆍ Wpi,n으로 하면, Wpi는 다음 식으로 나타난다.

[수학식 1]

단, 본 발명의 구성을 달성하기 위해서는 채널 형성 영역의 단부 이외 영역에, 불순물 영역이 하나 이상 형성되어 있을 필요가 있으므로 n은 1이상 정수이다.

또한, 채널폭(W)내, 도트 패턴간의 영역(전류가 흐르는 패스, 803)이 점유하고 있는 폭을 Wpa라고 정의한다. Wpa의 값으로서는 예를 들면 100∼3000Å(대표적으로는 500∼1500Å)로 할 수 있다. 또한, 임의의 도트 패턴간의 영역(803)을 Wpa,1, Wpa,2, Wpa,3ㆍㆍㆍ Wpa,m으로 하면, Wpa는 다음 식으로 나타난다.

[수학식 2]

단지, 상술하는 바와 같이 채널 형성 영역의 단부 이외의 영역에 불순물 영역이 하나 이상 형성되어 있기 때문에, 채널 형성 영역은 적어도 2분되어 m은 2이상의 정수가 된다.

즉, 전채널폭(W)은 W = Wpi + Wpa, 또한, n+m은 3이상이라는 관계가 성립한다. 그리고, W와 Wpi, W와 Wpa 및 Wpi와 Wpa와의 관계는, 동시에 이하의 조건을 만족하는 것이 바람직하다.

Wpa/W=0. 1∼0.9

Wpi/Wpa=1/9∼9

이 수학식의 의미하는 것은 Wpa/W 또는 Wpi/W가 0 또는 1이어서는 안된다는 것이다. 예를 들면, Wpa/W=0 (Wpi/W =1과 동의)인 경우, 도 8(B)에 나타내는 바와 같이 채널 형성 영역을 완전히 불순물 영역에서 막기 때문에 전류가 흐르는 패스가존재하지 않는 상태가 된다.

반대로 Wpa/W=1 (Wpi/W=0과 동의)인 경우, 도 8(C)에 나타내는 바와 같이 채널 형성 영역에 불순물 영역이 전혀 존재하지 않기 때문에 드레인측 공핍층의 확장을 억제할 수 없다.

이상 이유에 의해, Wpa/W 및 Wpi/W의 관계식은 0.1∼0.9(바람직하게는 0.2∼0.8)의 범위에 들어가고, 또한, 동시에 Wpi/Wpa = 1/9∼9 를 만족하는 것이 바람직하다. 또, 채널 길이를 L로 하면, 채널 형성 면적은 W× L로 나타난다.

또한, 본 발명은 FET의 성능을 나타내는 대표적인 파라미터의 이동도의 향상에 효과적이다. 그 이유에 대하여 이하에 설명한다.

이동도는 반도체(본 실시예에서는 실리콘 기판) 중의 캐리어의 산란에 의해서 결정되지만, 실리콘 기판에 있어서의 산란은 격자 산란과 불순물 산란으로 대별된다. 격자 산란은 실리콘 기판 중의 불순물 농도가 낮고, 비교적 고온에서 지배적이고, 불순물 산란은 불순물 농도가 높고, 비교적 저온에서 지배적이다. 이들이 영향을 주어 형성되는 전체적인 이동도(μ)는 다음 식으로 나타난다.

[수학식 5]

이 수학식5에서 나타나는 식은 전체적인 이동도(μ)가, 격자 산란의 영향을 받는 경우의 이동도(μi(i은 lattice를 의미한다)의 역수 및 불순물 산란의 영향을 받은 경우의 이동도(μi(i는 impurity를 의미한다)의 역수의 합에 반비례하는 것을의미한다.

여기에서, 격자 산란으로서는 드리프트 전계가 그다지 강하지 않으면 음향 포논이 중요한 역할을 하며, 그 때의 이동도(μi)는, 다음 식과 같이 온도의 -3/2승에 비례한다 . 따라서, 캐리어의 유효 질량(m*)과 온도(T)로 결정된다.

[수학식 6]

또한, 불순물 산란에 의한 이동도(μi)는 다음 식과 같이 온도의 3/2 승에 비례하고, 이온화한 불순물의 농도(Ni)에 역비례한다. 즉, 이온화한 불순물의 농도(Ni)를 조절함으로써 변화시킬 수 있다.

[수학식 7]

이 수학식에 의하면, 종래와 같이 채널 형성 영역 전체에 불순물을 첨가하는 채널 도프에서는 불순물 산란의 영향을 받아 이동도를 높일 수 없다. 그러나, 본 발명에서는 국부적으로 불순물 영역을 형성하고 있기 때문에, 인접하는 불순물 영역의 사이(Wpa의 폭을 갖는 영역)에는 불순물이 첨가되지 않는다.

즉, 이론적으로는 수학식 7에서 이온화한 불순물의 농도(Ni)를 끝없이 0에 가까이 하는 것을 의미하기 때문에, 이동도(μi) 는 끝없이 무한대에 가까워지게 된다. 즉, 수학식 5에서 1/μi의 항을 무시할 수 있는 정도로까지 불순물을 감소시키는 것을 의미하기 때문에 전체의 이동도(μ)는 끝없이 이동도(μi) 에 가까워진다.

또한, 캐리어의 유효 질량(m*)을 작게 함으로써 이동도(μi)를 더욱 크게 하는 것도 이론적으로는 가능하다. 이것은 극저온 영역에서, 캐리어(특히 전자의 경우)의 유효 질량이 결정축의 축방향에 의존하여 변화하는 현상을 이용하는 것으로 이룰 수 있다.

문헌에 의하면, 소스/드레인 간을 연결하는 채널 방향(캐리어의 이동하는 방향)이 단결정 실리콘의 <1 0 0> 축방향과 일치하도록 구성하였을 때, 최소의 유효질량을 얻을 수 있다.

예를 들면, 도 15에 나타내는 바와 같이, (1 0 0) 면을 갖는 단결정 실리콘 기판(1501)상에 소스 영역(1502), 채널 형성 영역(1503), 드레인 영역(1504)이 형성되어 있다고 한다. 이 때, 채널 방향(1505)을 [1 0 0]으로 하였을 때가 이것에 상당한다. 단지, 이 예는 4°K라는 극저온 영역에서의 결과이다.

또한, 결정 격자 사이를 캐리어가 잘 빠져나가 갈 수 있도록, 채널 방향 및 불순물 영역(707)의 축방향(배열 방향)과, 결정 격자의 축방향을 거의 평행(축방향의 어긋남을 ±10°이내로 받아들인다)하게 하는 것이 바람직하다. 단결정이면 실리콘 원자는 규칙적으로 배열되기 때문에, 결정 격자의 배열 방향과 평행하게 이동하는 캐리어는 격자 산란의 영향을 거의 받지 않아도 된다.

예를 들면, 단결정 실리콘 기판에 있어서 상기와 같은 방향에서 회전축을 0°로 하면, 그 외에도 90°, 180°, 270°의 회전축인 경우에 같은 효과를 얻을 수있다.

또한, 본 발명에서는 P채널형 FET에 대하여 P(인)을 사용하여 불순물 영역을 형성하지만, 인에는 금속 원소를 게터링하는 성질이 있기 때문에, 전류가 흐르는 경로로부터 산란의 원인이 될 수 있는 금속 원소 등을 제거하여, 불순물 영역에 고정하는 효과도 가지고 있다.

이상과 같이, 채널 형성 영역을 이동하는 캐리어는 채널 형성 영역 내에 존재하는 불순물 영역 이외의 영역을 통과한다. 이 모양을 도 16(A) 내지 16(C)의 모식도를 사용하여 간단히 설명한다.

도 16(A)에 있어서, 1601로 나타나는 것은 채널 형성 영역이다. 즉, 도 16(A)는 채널 형성 영역을 우측으로 기운 상방으로부터 본 도면이다. 본 발명을 실시한 채널 형성 영역은 입체적으로는 도 16(A)와 같이 불순물 영역(1602)이 형성되어 있다.

도 16(A)에 기재된 화살표(1603)는 캐리어(전자 또는 정공)의 진행 방향을 나타내는 것이다. 도 16(A)에 나타내는 바와 같이 채널 형성 영역(1601)내에는 복수의 불순물 영역(1602)이 배치되고, 캐리어는 그 불순물 영역(1602) 이외의 영역을 통과한다.

캐리어의 진행 방향을 채널 형성 영역(1601)의 상면에서 보면 도 16(B)와 같다. 도 16(B)는 도 16(A)에서, ACEF에서 나타나는 면을 본 도면이다. 이 도 16(B)를 보면, 캐리어가 불순물 영역(1602)을 피하여, 불순물 산란이 없는 영역을 이동하고 있는 것을 알 수 있다.

즉, 대부분의 캐리어는 화살표로 나타내는 바와 같이, 불순물 영역(1602)의 사이를 통하여 소스/드레인 간을 이동한다. 물론, 불순물 영역을 피하도록 하여 지그재그로 이동하는 경우도 포함된다.

또한, 도 16(C)에 나타낸 것은 채널 형성 영역(1601)을 측면으로부터 본 도면이다. 또, 도 16(C)은 도 16(A)에 있어서, ABCD에서 나타나는 면을 본 도면이다. 또한, 1603으로 나타나는 것은 화살표이고, 지면을 향하여 바로앞 방향으로 화살표 끝이 향하고 있는 것을 나타낸다. 이 도면으로부터 캐리어가 불순물 영역(1602)의 사이를 이동한다는 것이 알 수 있다.

[실시예2]

본 실시예에서는 본 발명을 이용하여 N채널형 FET (NMOS)와 P채널 형FET(PMOS)를 상보적으로 조합한 CMOS 회로를 구성하는 경우의 예를 나타낸다. CMOS 회로의 제작 공정의 상세한 것은 여기에서는 생략하지만, 본 발명에서는 실시예1에서 설명한 바와 같이, 게이트 절연막을 형성하기 전에 채널 형성 영역에만 도트 패턴 형상의 불순물 영역을 형성한다.

도 13(A)에 본 발명을 이용하는 경우의 CMOS 회로의 단면을 나타낸다. 도 13(A)는 일반적인 제작 방법으로 형성된 CMOS 회로를 채널 방향에서 분단한 단면도이다.

도 13(A)에서, 1301은 N형 실리콘 기판, 1302는 n웰, 1303은 p 웰이다. 결국, n 웰(1302)상에 P채널형 FET(PMOS), p 웰(1303)상에 N채널형 FET (NMOS)가 형성된다.

NMOS 및 PMOS는 각각 선택 산화법으로 형성된 필드 산화막(1304)으로 분리되고, p 웰측의 필드 산화막의 아래에는 채널 스톱퍼(1305)가 배치된다.

또한, n 웰(1302)에는 P형을 부여하는 불순물, 예를 들면 붕소가 첨가되고 PMOS의 소스 영역(1306), 드레인 영역(1307)이 배치되어 있다. 또한, p 웰(1303)에는 N형을 부여하는 불순물, 예를 들면 인이라든지 비소가 첨가되고 NMOS의 드레인 영역(1308), 소스 영역(1309)이 배치된다.

또한, 소스 영역(1306), 드레인 영역(1307) 및 소스 영역(1308), 드레인 영역(1309)에서 끼워진 채널 형성 영역에는 미리 게이트 절연막(1310)을 형성하기 전에 도트 패턴 상의 불순물 영역(1311,1312)을 형성해 둔다.

본 실시예에서 게이트 절연막(1310)의 형성 전에 불순물 영역(1311,1312)을 형성하는 이유는 게이트 절연막(1310)과 채널 형성 영역의 계면에 손상을 주기 때문이지만, 게이트 절연막(1310)을 통해서 불순물을 첨가하는 방법을 받아들이는 것도 가능하다.

또, 본 실시예로서는 불순물 영역(1311, 1312)을 형성함에 있어서 NMOS와 PMOS로 첨가하는 불순물 원소를 구별하여 사용하지 않으면 안된다. 본 실시예에서는 NMOS에 대하여 붕소를 사용하고, PMOS에 대하여 인을 사용한다. PMOS에 첨가하는 불순물 원소는 비소라도 상관없다.

또한, 본 실시예와 같은 CMOS 회로를 구성하는 경우, 도 13(A)에 나타내는 바와 같이 드레인 영역(1307, 1308)내에도 불순물 영역(1311, 1312)을 형성해 두는 것이 바람직하다.

또, 예를 들면 본 발명의 반도체 장치를 화소 등과 같이 소스와 드레인이 교체되는 소자에 이용할 때는 소스 영역과 드레인 영역의 쌍방 내에 불순물 영역을 형성하면 된다.

그리고, 채널 형성 영역 상에 도전성 재료로 형성되는 게이트 전극(1313, 1314)을 형성하고, 그것을 덮도록 하여 층간 절연막(1315)이 성막된다. 또한, 층간 절연막(1315)에 컨택트홀을 형성하여, PMOS의 소스 전극(1316), PMOS 및 NMOS의 공통 드레인 전극(1317), NMOS의 소스 전극(1318)을 배치한다.

도 13(A)에 나타내는 구조의 CMOS 회로는 본 발명에 의해 단채널 효과를 문제로 하지 않고서 미세화할 수 있기 때문에, 극히 집적도가 높은 집적화 회로를 구성할 수 있다.

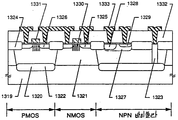

또한, 도 13(A)에 나타낸 CMOS 회로와 바이폴러트랜지스터를 조합시킨 BiCMOS 회로를 구성하는 것도 가능하다. 본 발명을 이용하여 형성한 BiCMOS 회로의 예를 도 13(B)에 나타낸다.

도 13(B)에서, 1319는 P형 실리콘 기판이고, 1320은 매설 N+영역, 1321은 에피텍셜 성장에 의해 형성된 p 웰이고, 매설 N+영역(1320)상의 p 웰(1321)은 N형으로 도핑되며 콘택터로서 기능하는 n 웰(1322)로 되어 있다. 또한, 1323은 매설 N+영역(1320)으로부터의 나오는 전극이 되는 DeepN+영역이다.

1324는 통상의 선택 산화법으로 형성된 필드 산화막이고, p 웰(1321)에는 n+영역(1325), n 웰 영역(1322)에는 p+영역(1326)이 형성되어 있다. 또, 바이폴러트랜지스터를 구성하는 측의 n 웰(1322)에는 활성 베이스가 되는 p-영역(1327)이 먼저 형성되며, 이어서 외부 베이스가 되는 p+영역(1328), n+영역(1329)이 배치된다.

또, PMOS 측 및 NMOS 측의 양방에는 불순물 영역(1330)이 배치된다. 불순물 영역(1330)은 상기 n+영역이라든지 p+영역을 형성한 후에 형성해도 되며, 그 전이라도 좋다. 물론, NMOS 라면 13족 원소를 사용하고, PMOS이면 15족의 원소를 사용한다.

그리고, 게이트 전극(1331), 층간 절연막(1332), 소스/드레인 배선(1333)을 배치하여 BiCMOS 회로를 구성한다. BiCMOS 회로는 바이폴러트랜지스터의 고속 동작성과 CMOS 회로의 저소비 전력성을 유효하게 병용하기 위한 회로 구성이다.

[실시예3]

실시예1에서는 불순물 영역(707)의 깊이 방향의 형상을 막대 형상으로 기재하였지만, 이것은 주입 시에 산란이 전혀 없는 경우와 같은 이상 상태로서, 실제로는 이온 주입의 조건에 의해서 여러 가지의 형상의 불순물 영역을 형성하는 것이 가능하다.

예를 들면, 보통, 이온 주입법에 의해서 첨가된 경우에는 도 9(A)에 나타내는 바와 같이 쐐기 형상의 불순물 영역(901)이 형성된다. 또한, 반대로 도 9(B)에나타내는 물방울 형상의 불순물 영역(902)을 형성하는 것도 가능하다. 특히, 도 9(B)에 나타내는 바와 같은 형상으로 하면, 불순물 영역(902)의 하부에서 인접하는 불순물 영역끼리 상호 접촉하는 상태가 된다.

이 상태에서는 실질적으로 채널 형성 영역이 벌크 기판과 절연 분리된 SOI 구조라고 간주할 수 있다. 이 구조는 드레인측 공핍층이 채널 형성 영역의 공핍층에 영향을 주는 것을 매우 효과적으로 억제할 수 있다. 또한, 채널 형성 영역의 공핍층이 하방으로 확장되는 것을 방지하는 효과도 기대할 수 있다.

[실시예4]

실시예1에서는 도 1(A)에 나타낸 바와 같은 매트릭스 상으로 도트 패턴(불순물 영역)을 배치하는 예를 나타내었지만, 설계 패턴을 바꿈으로써 다른 여러 가지의 배치 패턴으로 할 수 있다.

예를 들면, 도 10(A)에 나타내는 바와 같이, 불순물 영역(1001)이 교대로 맞물리도록 배치한 패턴으로 하는 것도 가능하다. 이 경우, 도트 패턴간의 틈을 다음 열에서 보충하는 구성이 되기 때문에, 드레인측 공핍층의 횡방향으로의 확장을 효과적으로 방지할 수 있다. 특히, 채널 길이가 0. 1μm 이하가 된 경우와 같이 단채널 효과의 영향이 극히 커지는 IG-FET에서 매우 효과적인 구성이다.

단, 캐리어의 이동하는 경로가 점선으로 나타낸 바와 같이 사행 모양(꾸불꾸불한 모양)이 되므로, 캐리어의 이동 거리가 길어지는 만큼, 이동도가 저하할 가능성도 있다. 그러나, 이 구조가 효과를 발휘하는 채널 길이 0. 1μm 이하의 영역에서는, 소스 영역으로부터 나온 캐리어가 일순에 드레인 영역에 도달하기 때문에,실질적으로는 다소 이동 거리가 길어지더라도 문제되지 않는다고 생각된다.

따라서, 예를 들면 채널 길이가 0. 1μm 이상인 경우에는 도 1(A)에 나타낸 바와 같이 도트 패턴상 불순물 영역을 배치하고, 채널 길이가 0. 1μm 이하인 경우에는 도 10(A)에 나타내는 바와 같이 배치하는 것이 바람직하다.

또한, 도 10(B)에 나타내는 바와 같이, 도트 패턴을 채널 방향과 수직인 타원형 또는 장방형으로 할 수 있다. 이 경우, 드레인측 공핍층을 억제하기에 적절한 구성이 되지만, 캐리어의 이동을 방해할 가능성도 있기 때문에, 예를 들면 0. 2μm 이하로 채널 길이가 매우 짧은 반도체 장치에 이용하는 것이 바람직하다.

또한, 도 10(C)에 나타내는 바와 같이, 도트 패턴을 채널 방향과 평행한 타원형 또는 장방형으로도 할 수 있다. 이 경우, 협채널 효과가 보다 현저하게 나타나는 구성이 되기 때문에, 한계치 전압을 많이 증가시키는 것이 필요할 경우에 효과적인 구성이라고 할 수 있다.

[실시예5]

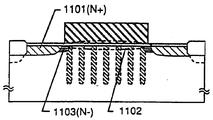

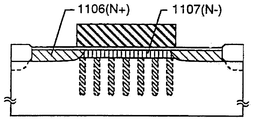

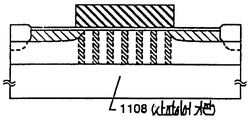

본 발명은 실시예1에서 나타낸 바와 같은 횡형 IG-FET뿐만 아니라, 또한 여러 가지 구조의 IG-FET에 대해서도 적용할 수 있다. 예를 들면, 평형 IG-FET에는 그 외에도 LDD (오프 세트) 구조(도 11(A)), 2중 드레인 구조(도 11(B)), 매설 채널 구조(도 11(C)), SOI 구조(도 11(D)), SIMOX 구조(도 11(E)) 등이 있다.

본 실시예에서는, N채널형 FET을 예로 들어, 상기 구조에 응용한 경우에 대해서 설명한다. 또, 도면 중의 N+, N-은 N형 도전성의 강약을 상대적으로 나타낸 것으로, N+는 N-보다도 강한 N형 도전성을 가지고 있다는 것을 의미한다.

도 11(A)는 소스 또는 드레인 영역(1101)과 채널 형성 영역(1102)의 사이에 저농도 불순물 영역(1103)을 배치한 구조이다. 저농도 불순물 영역(1103)이 존재하는 만큼, 드레인측 공핍층은 완만히 확장되기 쉽지만, 본 발명에 의해 그 확장을 억제할 수 있다.

또한, 도 11(B)는 소스 또는 드레인 영역(1104)의 측면에 0. 1∼0. 5μm폭의 도전성 영역(1105)을 형성한 구조이다. 소스 또는 드레인 영역(1104)과 도전성 영역(1105)은 같은 도전성이고, 도전성 영역(1105) 쪽이 도전성은 약하다. 예를 들면, 소스 또는 드레인 영역(1104)을 As(비소)를 주입하여 형성하고, 약한 도전성 영역(1105)을 P(인)을 주입하여 형성함으로써 구성할 수 있다.

도 11(C)에 나타내는 매설 채널 구조는 N채널형 FET와 P채널형 FET에서 CMOS회로를 구성할 때에 결과적으로 형성되는 구성인 경우에도, 단채널 효과도 영향을 받기 쉬운 구조이다.

구조적으로는, 예를 들면 N채널형 FET에서, 채널 형성 영역의 계면 부근에 소스/드레인 영역(1106)과 동일 또는 약한 도전성 영역(1107)을 형성하여 구성된다.

따라서, 이 도전성 영역(1107)의 바로 아래에 채널이 형성되지만, 이 같은 경우에도 본 발명을 실시함으로써 단채널 효과를 억제하여, 펀치스루 현상이라든지 한계치 전압의 저하를 방지할 수 있다.

또한, SOI 구조는 소자로서 사용하는 반도체층을 박막화하여 공핍층을 감소시킬 목적도 포함시켜 개발된 기술이므로 그 자체 단채널 효과를 억제하는 효과를 가지고 있다. 예를 들면, 도 11(D)에 나타내는 구조는 일반적으로 SOS(silicon-on-sapphire) 구조라고 불리고, 사파이어 기판(1108)상에 실리콘 단결정을 성장시켜서 형성한다.

그러나, 1μm 이하의 단결정 실리콘층을 형성하는 것은 곤란하고, 공핍층의 확장을 억제하는 것에도 한계가 있다. 따라서, 본 발명을 SOI 구조에 응용하면 보다 확실하게 단채널 효과를 방지할 수 있게 된다.

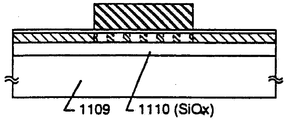

또, 같은 SOI 구조의 부류에 포함되지만 일반적으로 SIMOX(separation-by-implanted oxygen)라고 불리는 기판 상에 IG-FET를 형성한 예가 도 11(E)이다. 이 경우, 단결정 실리콘 기판(1109)에 대하여 산소를 주입하는 것에 의해서 매설 산화층(1110)을 형성한다. 또한, 산소의 주입 깊이를 얕게 함으로써 극히 얇은 단결정 박막을 형성할 수 있다.

이러한 경우에도, 본 발명을 이용할 수 있다. 이 경우, 드레인측 공핍층이 채널 형성 영역으로 확장되는 것을 억지하는 효과를 기대할 수 있다.

[실시예6]

본 발명에 있어서 채널 형성 영역에 불순물 영역을 형성하는 수단으로서, 레지스트 마스크를 사용한 패터닝에 의한 방법 이외에도, 불순물이 변형에 편석하는 성질이라든지 산화물에 들어가는 성질 등을 이용하는 방법도 가능하다.

우선, 실시예1의 순서에 따라서 도 7(B)와 같은 상태를 얻는다. 즉, 도12(A)에 있어서, 1201은 실리콘 기판, 1202는 필드 산화막, 1203은 채널 스톱퍼이다.

이 상태에서, 집속 이온빔 등을 이용하여 실리콘 기판 표면의 국부적인 이방성 에칭 가공을 행하고, 홈 형상 또는 구멍 형상 패턴(1204)을 원하는 위치에 원하는 형상으로 묘화한다.(도 12(A))

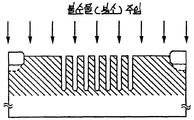

다음에, 불순물 원소(여기에서는 붕소를 예를 든다)를 기판(1201) 전면에 첨가한다. 이 불순물 원소는 나중에 N채널형 FET의 불순물 영역을 형성하기 위한 것이다. 또한, 주입 깊이는 홈 형상 또는 구멍 형상 패턴(1204)의 깊이보다도 깊은 것이 바람직하다.(도 12(B))

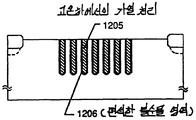

불순물 원소의 첨가가 종료하면, 다음에 1000∼1200℃전후의 고온에서 가열처리를 행한다. 이 가열 처리에 의해 홈 형상 또는 구멍 형상 패턴(1204)의 측벽에는 열산화막(1205)이 형성되고, 홈 형상 또는 구멍 형상 패턴(1204)은 매립된다. 따라서, 이 영역은 실질적으로 SiOx 로 나타나는 산화물 영역(1205)이 된다. 이 경우, 가열 처리를 산화성 분위기에서 행하면 산화물 영역(1205)의 형성 속도가 증가하므로 바람직하다.

그리고, 동시에 실리콘 기판(1201) 전체에 첨가되어 있던 불순물 원소(붕소)가 산화물 영역(1205)에 들어간다. 여기에서, 열산화 공정에 의해 열산화막/실리콘 계면 부근의 붕소 또는 인 농도가 어떠한 분포를 나타내는지를 도 17(A) 및 17(B)을 이용하여 설명한다.

도 17(A) 및 17(B)에 나타내는 바와 같이, Si내에 존재하는 첨가 이온(B, P)은 산화막이 형성되면 재분포한다. 이것은 실리콘(Si)내 및 열산화막(SiOx) 내에서의 첨가 이온의 용해도와 확산 속도가 다르기 때문에 발생하는 현상이다. 불순물의 Si내에서의 용해도를 [C]Si로 하고, SiOx내에서의 용해도를 [C]SiOx로 하였을때, 평형 편석 계수(m)는 다음 식으로 정의된다.

이 때, Si/SiOx계면 부근의 불순물의 편석은 m의 값에 지배된다. 통상, Si내에서 불순물의 확산 계수가 충분히 크다고 해서, m<1 인 경우, Si내의 불순물은 SiO2내에 들어간다(도 17(A)). 또한, m>1 인 경우, SiOx가 불순물을 배척하고, 그 결과로서 Si/SiOx계면 부근의 불순물 농도가 증대한다 (도 17(B)).

문헌에 의하면, 붕소의 m 값은 0.3 정도이고, 인의 m의 값은 10정도였다. 따라서, 본 실시예에 있어서의 열산화 공정 후의 붕소의 농도 분포는 도 17(A)와 같고, 열산화막내에 붕소가 들어가며, 불순물 영역(1206)의 측면(Si/SiOx계면 부근)에 있어서의 붕소 농도는 극히 미량 상태가 된다. 또한, 반대로 형성된 산화물(1205)내에는 다량의 붕소가 함유된다.

이와 같은 열산화막내로 붕소가 들어가는 현상은 이미 알려져 있었지만, 본 발명과 같은 에너지 장벽(불순물 영역)을 형성하기 위해서 이 현상을 이용하는 발상은 완전히 새로운 것이다.

또, 도 17(B)에 나타내는 바와 같이, 불순물 원소로서 인을 사용한 경우에는열산화막과 실리콘과의 계면에 편석(파일업)한다. 이 현상도 또, P채널형 FET에 불순물 영역을 형성할 경우에 활용할 수 있다.

또한, 단결정 실리콘 기판(1201)에 도전형을 부여하기 위해서 인이라든지 붕소와 같은 도전성을 부여하는 불순물 원소가 첨가되어 있는 경우, 본 실시예와 같은 산화물로의 인 또는 붕소의 편석 현상을 이용하는 것으로 대폭적인 이동도의 향상을 도모할 수 있다.

왜냐하면, 본 실시예를 실시하면 불순물 영역(대표적으로는 SiOx 로 나타나는 산화물) 주변의 불순물(인 또는 붕소)이 불순물 영역에 수집되므로, 불순물 영역간의 캐리어가 이동하는 영역에서의 불순물 산란의 영향을 극히 적게 할 수 있기 때문이다.

이 사실은 앞서 설명한 바와 같이 수학식 5에서 μi가 커지는 것에 상당하므로, 전체의 이동도(μ)는 이상적으로 μ=μi에 가까워진다. 즉, 실질적으로 격자 산란만으로 결정되는 극히 큰 이동도를 실현할 수 있다.

또한, 본 실시예와 같이 홈을 형성하는 방법 이외에도, 예를 들면, 집속 이온빔과 같은 마스크레스로 이온 주입을 행할 수 있는 장치를 사용하여, 직접 단결정 실리콘 기판상에 산소 이온을 주입하여, 가열 처리를 행함으로써 이온 주입한 영역을 산화물 영역에 변성시키는 것도 가능하다. 집속 이온빔 이외에도 전자빔 등을 사용해도 된다.

[실시예7]

본 실시예에서는 본 발명을 이용한 반도체 장치를 제품(전자 기기)에 조합한 경우의 일례를 나타낸다. 여기에서는, 노트북 컴퓨터에 조합된 IC 회로를 예를 들어 설명한다. 설명은 도 18을 이용한다.

도 18에서, 3001은 본체, 3002는 뚜껑부, 3003은 키보드, 3004는 화상 표시부이고, 본체(3001)내에는 여러 집적 회로(3005)가 조합된다.

집적 회로(3005)를 취출해 보면, 외부는 패키지(3011)로 덮여지고 내부의 반도체칩은 수지 등으로 보호되어 있다. 또한, 내부의 반도체칩은 리드(3012)에 의해서 외부와 접속된다. 통상, 보는 집적 회로(IC 칩)(3005)는 외관상으로는 흑색의 패키지(3011)와 리드(3012)밖에 보이지 않으므로 완전히 블랙박스로 되어 있다.

그 패키지(3011)로 보호된 반도체칩을 꺼내어 보면, 예를 들면, 다음과 같은 구성으로 되어 있다. 먼저, 기판(3013)상에는 연산부(프로세서, 3014)와 메모리부(3015)가 배치되어 있다. 또, 3016은 반도체 소자와 리드(3012)를 접속하는 본딩부이다.

연산부(3014), 메모리부(3015)는 CMOS 회로, BiCMOS 회로, DRAM 회로, SRAM회로 등, 그 외에도 여러 가지 회로를 사용하여 구성되어 있다. 본 실시예에서 나타낸 도 15와 같은 구성은 동일 기판 상에 연산부(3014)와 메모리부(3015)가 배치되어 있는 것에 특징이 있다.

이와 같이 연산부(3014)와 메모리부(3015)가 인접한 구성으로 하면, 연산부(3014)와 메모리부(3015) 사이의 데이터의 주고받기가 매우 고속으로 행해지게 되므로, 동작 속도가 빠른 회로를 형성하는 것이 가능하다.

또한, 원 칩상에 필요한 회로를 모두 집적화하는 것도 가능하기 때문에, 제조 비용을 대폭 감소하는 것도 기대할 수 있다. 또한, 배치 면적을 줄임으로써 제품의 소형화를 도모할 수 있다.

본 발명을 이용하면 단채널 효과를 문제로 삼지 않고 반도체 소자의 미세화를 행할 수 있으므로, 상기와 같은 원칩화와 병용함으로써 반도체 전자 기기의 한층 소형화, 휴대화를 실현할 수 있다.

[실시예8]

본 발명은 실시예7에 나타낸 예 이외에도 여러 가지 반도체 전자기기에 응용하는 것이 가능하다. 왜냐하면, 본 발명에 의한 반도체 장치의 전기 특성은 매우 우수하며, 이것을 사용하여 구성한 IC 회로는 높은 주파수 특성을 실현할 수 있기 때문이다.

본 발명을 이용하여 형성된 반도체 소자 단체의 디바이스 특성은 매우 우수하였으며, N채널형 FET의 한계치 전압 Vth,n은 -0.5∼3.0 V, P채널형 FET의 한계치 전압(Vth,p)은 -3.0∼0.5V의 범위에서 필요로 하는 구동 전압에 맞추어서 조절할 수 있다. 또한, S값은 60∼85mV/decade, 바람직하게는 60∼70mV/decade 가 얻어진다.

또한, 실시예1에서 설명한 바와 같은 이유에 의해 높은 이동도(1000㎠/Vs 이상)를 얻을 수 있다. 이동도를 계산식으로 구하는 경우, 이동도는 채널폭(W)에 반비례하기 때문에 주의가 필요하다. 본 발명을 실시하는 경우, 채널 형성 영역에서는 불순물 영역에 의해서 적지 않게 채널폭이 좁게 되어 있기 때문에, 실측채널폭(Wpa)을 대입하지 않으면 실제의 이동도는 얻어지지 않는다.

이상과 같은 우수한 전기 특성을 달성할 수 있는 본 발명의 반도체 장치로 IC 회로를 구성하면, 극히 양호한 주파수 특성을 얻을 수 있다. 예를 들면, 본 발명의 반도체 장치를 사용하여 9단의 링오실레이터를 구성하면, 3.3V의 구동 전압으로 2∼10GHz의 주파수 특성을 실현할 수 있다.

예를 들면, 고주파 전자 기기인 휴대 전화 등과 같이 높은 주파수 특성을 필요로 하는 전자기기에 대하여도 본 발명은 유효하다. 휴대 전화의 입력부 등에 사용되는 IC 회로는 2GHz의 주파수 특성을 필요로 하는 것이지만, 본 발명은 그와 같은 고주파 IC 회로에 대해서도 충분히 대응할 수 있다.

본 발명을 이용함으로써 채널 길이가 짧게 된 경우에 생기는 단채널 효과를 방지하는 것이 가능하다. 구체적으로는, 우선 드레인측 공핍층이 소스 영역이라든지 채널 형성 영역 아래로 확장되는 것을, 채널 형성 영역에 국부적으로 형성한 불순물 영역에서 차단되며, 채널 형성 영역의 에너지(전위) 상태에 드레인 전압이 영향을 주지 않는 구성으로 한다. 이것에 의해 펀치스루 현상이라든지 서브스렛숄드 특성의 열화를 방지하는 것이 가능하다. 또한, 동시에 높은 드레인 내압을 실현할 수 있다.

또한, 단채널 효과의 특징의 하나인 한계치 전압의 저하를 협채널 효과에 의한 한계치 전압의 증가에 의해서 억제할 수 있다. 이 협채널 효과는 채널 형성 영역에 국부적으로 불순물 영역을 형성하는 본 발명의 구성에 따라서 인위적으로 이룰 수 있는 효과이다.

이상과 같이, 본 발명을 이용함으로써 채널 길이가 짧은 디프서브미크론 영역에서의 반도체 장치에 있어서도, 단채널 효과를 일으키지 않고서 동작시킬 수 있다. 즉, IG-FET로 대표되는 반도체 장치의 한층 더 집적화와 성능의 향상을 기대할 수 있다.

Claims (37)

- 절연 게이트형 반도체 장치에 있어서,주표면을 갖는 반도체내에 형성되는 소스 영역, 드레인 영역 및 채널 형성 영역과,상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 포함하고,상기 채널 형성 영역은 캐리어들이 이동하는 영역과. 상기 드레인 영역으로부터 상기 채널 형성 영역 및 상기 소스 영역을 향하여 확장하는 공핍층을 피닝하기 위한 복수의 불순물 영역들을 포함하고, 각각의 불순물 영역은 상기 반도체의 상기 주표면상에 원형 형상을 가지며,상기 불순물 영역에는 상기 채널 형성 영역의 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소들이 첨가되고, 상기 불순물 원소들은 상기 소스 및 드레인 영역들의 것과 반대인 도전형을 가지며,채널 폭 방향에서의 상기 불순물 영역들의 폭들 Wpi는 10∼100Å의 범위내에 있고, 상기 채널 폭 방향에서의 상기 불순물 영역들 간의 폭들 Wpa는 100∼3000Å의 범위내에 있는, 절연 게이트형 반도체 장치.

- 절연 게이트형 반도체 장치에 있어서,주표면을 갖는 반도체내에 형성되는 소스 영역, 드레인 영역 및 채널 형성영역과,상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 포함하고,상기 채널 형성 영역은 캐리어들이 이동하는 영역과, 상기 드레인 영역으로부터 상기 채널 형성 영역 및 상기 소스 영역을 향하여 확장하는 공핍층을 피닝하기 위한 복수의 불순물 영역들을 포함하고, 각각의 불순물 영역은 상기 반도체의 상기 주표면상에 원형 형상을 가지며,상기 불순물 영역에는 상기 채널 형성 영역의 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소들이 첨가되고 상기 불순물 원소들은 상기 소스 및 드레인 영역들의 것과는 반대인 도전형을 가지며,상기 불순물 영역들은 매트릭스 형태로 배열되는, 절연 게이트형 반도체 장치.

- 절연 게이트형 반도체 장치에 있어서,주표면을 갖는 반도체내에 형성되는 소스 영역, 드레인 영역 및 채널 형성 영역과,상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 포함하고,상기 채널 형성 영역은 캐리어들이 이동하는 영역과, 불순물 원소들의 첨가에 의해 상기 반도체 장치의 한계치 전압을 미리 결정된 값으로 제어하기 위한 복수의 불순물 영역들을 포함하고, 각각의 불순물 영역은 상기 반도체의 상기 주표면상에 원형 형상을 가지며,상기 불순물 원소들은 상기 채널 형성 영역의 에너지 밴드폭(Eg)을 시프트시키고 상기 불순물 원소들은 상기 소스 및 드레인 영역들의 것과는 반대인 도전형을 가지며,상기 불순물 영역들의 깊이는 상기 반도체 내의 필드 산화 막과 상기 소스 및 드레인 영역들보다 더 깊은, 절연 게이트형 반도체 장치.

- 절연 게이트형 반도체 장치에 있어서,주표면을 갖는 반도체내에 형성되는 소스 영역, 드레인 영역 및 채널 형성 영역과,상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 포함하고,상기 채널 형성 영역은 캐리어들이 이동하는 영역과, 불순물 원소들의 첨가에 의해 상기 반도체 장치의 한계치 전압을 미리 결정된 값으로 제어하기 위한 복수의 불순물 영역들을 포함하고, 각각의 불순물 영역은 상기 반도체의 상기 주표면상에 원형 형상을 가지며,상기 불순물 원소들은 상기 채널 형성 영역의 에너지 밴드폭(Eg)을 시프트시키고 상기 불순물 원소들은 상기 소스 및 드레인 영역들의 것과는 반대인 도전형을 가지며,상기 불순물 영역들의 채널 길이 방향에서의 배열은 상기 채널 형성 영역에서의 결정 격자들의 축 방향과 실질적으로 평행하거나 ±10°이내의 각을 만드는, 절연 게이트형 반도체 장치.

- 제 3 항 또는 제 4 항에 있어서,상기 불순물 영역들은 협채널 효과로 인해 한계치 전압을 증가시켜, 한계치 전압을 감소시키는 단채널 효과를 완화하는, 절연 게이트형 반도체 장치.

- 제 3 항 또는 제 4 항에 있어서,캐리어들은 상기 불순물 영역들 이외의 영역내의 소스 영역 및 드레인 영역사이에서 이동하는, 절연 게이트형 반도체 장치.

- 절연 게이트형 반도체 장치에 있어서,주표면을 갖는 반도체내에 형성되는 소스 영역, 드레인 영역 및 채널 형성 영역과,상기 채널 형성 영역의 에너지 밴드폭(Eg)을 시프트시키는 불순물 원소들의 첨가에 의해 상기 채널 형성 영역내에 형성된 복수의 불순물 영역들과,상기 채널 형성 영역 위에 형성된 게이트 절연막 및 게이트 전극을 포함하고,상기 불순물 영역들은 절연 성질을 가지며 이에 의해 캐리어들이 상기 채널형성 영역내의 상기 불순물 영역들을 제외한 영역들내에서 이동하고,상기 불순물 원소들은 소스 및 드레인 영역들의 것과는 반대인 도전형을 가지며,

- 제 2 항 내지 제 4 항 또는 제 7 항중 어느 한 항에 있어서,채널 폭 방향에서의 상기 불순물 영역들의 폭들 Wpi, 상기 채널 폭 방향에서의 상기 불순물 영역들 간의 폭들 Wpa, 및 상기 채널 형성 영역의 폭 W는, Wpi/W = 0.1∼0.9, Wpa/W = 0.1∼0.9, 및 Wpi/Wpa = 1/9∼9 의 관계식들을 만족하는, 절연게이트형 반도체 장치.

- 제 1 항 내지 제 4 항중 어느 한 항에 있어서,상기 채널 형성 영역의 채널 방향에 수직인 적어도 한 단면이 상기 불순물 영역들에 의해 구획되는 복수의 협채널 형성 영역들의 집합체로서 실질적으로 간주되는, 절연 게이트형 반도체 장치.

- 제 1 항 내지 제 4 항 또는 제 7 항중 어느 한 항에 있어서,상기 채널 형성 영역 내의 상기 불순물 영역들 이외에 캐리어들이 이동하는 상기 영역은 진성 또는 실질적으로 진성 영역들인, 절연 게이트형 반도체 장치.

- 제 8 항에 있어서,상기 Wpi의 값이 10∼100Å의 범위에 있고 상기 Wpa의 값은 100∼3000Å의 범위에 있는, 절연 게이트형 반도체 장치.

- 제 1 항 또는 제 2 항 또는 제 7 항중 어느 한 항에 있어서,상기 반도체 장치의 한계치 전압이 상기 불순물 영역들에 첨가된 불순물 원소들의 농도에 따라 미리 결정된 값으로 조정되는, 절연 게이트형 반도체 장치.

- 제 1 항 내지 제 4 항 또는 제 7 항중 어느 한 항에 있어서,상기 반도체는 단결정 반도체인, 절연 게이트형 반도체 장치.

- 제 1 항 내지 제 4 항 또는 제 7 항중 어느 한 항에 있어서,상기 불순물 원소들은 13족 또는 15족의 원소들인, 절연 게이트형 반도체 장치.

- 제 14 항에 있어서,상기 13족의 원소들은 붕소를 포함하고, 상기 15족의 원소들은 인 또는 비소중 적어도 하나를 포함하는, 절연 게이트형 반도체 장치.

- 제 1 항 또는 제 3 항 또는 제 4 항 또는 제 7 항중 어느 한 항에 있어서,상기 불순물 영역들은 매트릭스 형태로 배열되는, 절연 게이트형 반도체 장치.

- 제 1 항 내지 제 4 항 또는 제 7 항중 어느 한 항에 있어서,상기 불순물 영역들내의 상기 불순물 원소들의 농도가 1×1017∼1×1020atoms/cm3인, 절연 게이트형 반도체 장치.

- 제 1 항 내지 제 4 항 또는 제 7 항중 어느 한 항에 있어서,상기 채널 형성 영역의 채널 길이가 0.01∼0.35마이크로미터의 범위에 있는, 절연 게이트형 반도체 장치.

- 제 3 항 또는 제 4 항 또는 제 7 항중 어느 한 항에 있어서,상기 불순물 영역들은 상기 반도체에서 드레인 공핍층의 스톱퍼로서 기능하는, 절연 게이트형 반도체 장치.

- 제 1 항 또는 제 2 항 또는 제 4 항 또는 제 7 항중 어느 한 항에 있어서,상기 불순물 영역들의 깊이가 상기 반도체내의 필드 산화막과 소스 및 드레인 영역들보다 더 깊은, 절연 게이트형 반도체 장치.

- 제 1 항 내지 제 4 항 또는 제 7 항중 어느 한 항에 있어서,상기 소스 및 드레인 영역들은 실리사이드 영역들을 각각 포함하는, 절연 게이트형 반도체 장치.

- 제 1 항 내지 제 4 항 또는 제 7 항중 어느 한 항에 있어서,상기 반도체 장치는 휴대용 전화 및 노트북형 개인용 컴퓨터로 이루어지는 그룹으로부터 선택되는, 절연 게이트형 반도체 장치.

- 반도체 장치에 있어서,주표면을 갖는 반도체내에 형성되는 소스 영역, 드레인 영역 및 채널 형성 영역과,상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 포함하고,상기 채널 형성 영역은 복수의 불순물 영역들을 포함하고, 각각의 불순물 영역은 상기 반도체의 상기 주표면상에 원형 형상을 가지며,상기 불순물 영역들은 상기 소스 및 드레인 영역들의 것과 반대인 도전형을 갖는 물질을 포함하며,상기 채널 형성 영역의 길이는 0.01∼1.0마이크로미터이며,상기 불순물 영역들의 깊이는 상기 반도체내의 필드 산화막과 소스 및 드레인 영역들보다 더 깊은, 반도체 장치.

- 반도체 장치에 있어서,주표면을 갖는 반도체내에 형성되는 소스 영역, 드레인 영역 및 채널 형성 영역과,상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 포함하고,상기 채널 형성 영역은 캐리어들이 이동하는 영역과, 복수의 불순물 영역들을 포함하고, 각각의 불순물 영역은 상기 반도체의 상기 주표면상에 원형 형상을 가지며,상기 불순물 영역들은 상기 소스 및 드레인 영역들의 것과는 반대인 도전형을 갖는 물질을 포함하며,상기 불순물 영역들은 매트릭스 형태로 배열되는, 반도체 장치.

- 제 25 항에 있어서,상기 물질은 붕소, 인, 및 비소로 이루어지는 그룹으로부터 선택되는, 반도체 장치.

- 반도체 장치에 있어서,주표면을 갖는 반도체내에 형성되는 소스 영역, 드레인 영역 및 채널 형성 영역과,상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 포함하고,상기 채널 형성 영역은 캐리어들이 이동하는 영역과, 복수의 불순물 영역들을 포함하고, 각각의 불순물 영역은 상기 반도체의 상기 주표면상에 원형 형상을 가지며,상기 불순물 영역들은 상기 소스 및 드레인 영역들의 것과는 반대인 도전형을 갖는 물질을 포함하며,캐리어들이 이동하는 상기 영역은 탄소, 질소 및 산소를 2×1018atoms/cm3이하의 농도들로 각각 포함하며,상기 불순물 영역들의 채널 길이 방향에서의 배열이 상기 채널 형성 영역에서의 결정 격자의 축 방향과 실질적으로 평행하거나 ±10°이내의 각을 만드는, 반도체 장치.

- 제 24 항 또는 제 25 항 또는 제 27 항중 어느 한 항에 있어서,상기 반도체 장치는 휴대용 전화 및 노트북형 개인용 컴퓨터로 이루어지는 그룹으로부터 선택되는, 반도체 장치.

- 반도체 장치에 있어서,주표면을 갖는 반도체내에 형성되는 소스 영역, 드레인 영역 및 채널 형성 영역과,상기 채널 형성 영역 상에 형성된 게이트 절연막 및 게이트 전극을 포함하고,상기 채널 형성 영역은 캐리어들이 이동하는 영역과, 복수의 불순물 영역들을 포함하고, 각각의 불순물 영역은 상기 반도체의 상기 주표면상에 원형 형상을 가지며,상기 불순물 영역들은 매트릭스 형태로 배열되며,상기 반도체 장치는 휴대용 전화 및 노트북형 개인용 컴퓨터로 이루어지는 그룹으로부터 선택되는, 반도체 장치.

- 제 24 항 또는 제 25 항 또는 제 27 항 또는 제 29 항중 어느 한 항에 있어서,상기 채널 형성 영역의 채널 길이가 0.01∼0.35마이크로미터의 범위에 있는, 반도체 장치.

- 제 24 항 또는 제 25 항 또는 제 27 항 또는 제 29 항중 어느 한 항에 있어서,상기 불순물 영역들은 상기 반도체에서 드레인 공핍층의 스톱퍼로서 기능하는, 반도체 장치.

- 제 25 항 또는 제 27 항 또는 제 29 항중 어느 한 항에 있어서,상기 불순물 영역들의 깊이가 상기 반도체내의 필드 산화막과 소스 및 드레인 영역들보다 더 깊은, 반도체 장치.

- 제 24 항 또는 제 25 항 또는 제 27 항 또는 제 29 항중 어느 한 항에 있어서,상기 소스 및 드레인 영역들은 실리사이드 영역들을 각각 포함하는, 반도체 장치.

- 제 24 항 또는 제 25 항 또는 제 27 항 또는 제 29 항중 어느 한 항에 있어서,상기 반도체 장치의 한계치 전압이 상기 불순물 영역들에 첨가된 불순물 원소들의 농도에 따라 제어되고, 캐리어들이 상기 채널 형성 영역들내의 상기 불순물 영역들 이외의 영역내의 소스 영역 및 드레인 영역 사이에서 이동하는, 반도체 장치.

- 제 24 항 또는 제 25 항 또는 제 29 항중 어느 한 항에 있어서,상기 물질은 붕소, 인, 및 비소로 이루어지는 그룹으로부터 선택되는, 반도체 장치.

- 제 24 항 또는 제 25 항 또는 제 29 항중 어느 한 항에 있어서,상기 불순물 영역의 채널 길이 방향에서의 배열이 상기 채널 형성 영역에서의 결정 격자들의 축 방향과 실질적으로 평행하거나 ±10°이내의 각을 만드는, 반도체 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP96-232552 | 1996-08-13 | ||

| JP23255296A JP3949193B2 (ja) | 1996-08-13 | 1996-08-13 | 絶縁ゲイト型半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020020047936A Division KR100453400B1 (ko) | 1996-08-13 | 2002-08-13 | 반도체 장치 제작 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19980018784A KR19980018784A (ko) | 1998-06-05 |

| KR100443436B1 true KR100443436B1 (ko) | 2004-10-20 |

Family

ID=16941122

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970039449A KR100443436B1 (ko) | 1996-08-13 | 1997-08-13 | 절연게이트형반도체장치 |

| KR1020020047936A KR100453400B1 (ko) | 1996-08-13 | 2002-08-13 | 반도체 장치 제작 방법 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020020047936A KR100453400B1 (ko) | 1996-08-13 | 2002-08-13 | 반도체 장치 제작 방법 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US6218714B1 (ko) |

| JP (1) | JP3949193B2 (ko) |

| KR (2) | KR100443436B1 (ko) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4103968B2 (ja) * | 1996-09-18 | 2008-06-18 | 株式会社半導体エネルギー研究所 | 絶縁ゲイト型半導体装置 |

| US6590230B1 (en) | 1996-10-15 | 2003-07-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US6118148A (en) | 1996-11-04 | 2000-09-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP4017706B2 (ja) | 1997-07-14 | 2007-12-05 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US6686623B2 (en) | 1997-11-18 | 2004-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile memory and electronic apparatus |

| JP4236722B2 (ja) * | 1998-02-05 | 2009-03-11 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US7015546B2 (en) * | 2000-02-23 | 2006-03-21 | Semiconductor Research Corporation | Deterministically doped field-effect devices and methods of making same |

| US6724037B2 (en) * | 2000-07-21 | 2004-04-20 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile memory and semiconductor device |

| JP4275336B2 (ja) * | 2001-11-16 | 2009-06-10 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR100493018B1 (ko) * | 2002-06-12 | 2005-06-07 | 삼성전자주식회사 | 반도체 장치의 제조방법 |

| US7052966B2 (en) * | 2003-04-09 | 2006-05-30 | Newport Fab, Llc | Deep N wells in triple well structures and method for fabricating same |

| US7829394B2 (en) * | 2005-05-26 | 2010-11-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of the same |

| US8304783B2 (en) * | 2009-06-03 | 2012-11-06 | Cree, Inc. | Schottky diodes including polysilicon having low barrier heights and methods of fabricating the same |

| WO2012006890A1 (zh) * | 2010-07-15 | 2012-01-19 | 电子科技大学 | 一种利用应力集中效应增强沟道应力的mos晶体管 |

| US8916867B2 (en) | 2011-01-20 | 2014-12-23 | Semiconductor Energy Laboratory Co., Ltd. | Oxide semiconductor element and semiconductor device |

| TWI491050B (zh) * | 2011-11-25 | 2015-07-01 | Sony Corp | 電晶體,顯示器及電子裝置 |

| FR3011678B1 (fr) * | 2013-10-07 | 2017-01-27 | St Microelectronics Crolles 2 Sas | Procede de relaxation des contraites mecaniques transversales dans la region active d'un transistor mos, et circuit integre correspondant |

| JP2016029719A (ja) * | 2014-07-17 | 2016-03-03 | 出光興産株式会社 | 薄膜トランジスタ |

| WO2019171590A1 (ja) * | 2018-03-09 | 2019-09-12 | 堺ディスプレイプロダクト株式会社 | 薄膜トランジスタおよびその製造方法 |

| US20200194555A1 (en) * | 2018-12-18 | 2020-06-18 | United Microelectronics Corp. | Semiconductor device with reduced floating body effects and fabrication method thereof |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS55151363A (en) * | 1979-05-14 | 1980-11-25 | Chiyou Lsi Gijutsu Kenkyu Kumiai | Mos semiconductor device and fabricating method of the same |

| US5350940A (en) * | 1984-02-02 | 1994-09-27 | Fastran, Inc. | Enhanced mobility metal oxide semiconductor devices |

| US4697198A (en) * | 1984-08-22 | 1987-09-29 | Hitachi, Ltd. | MOSFET which reduces the short-channel effect |

| IT1213234B (it) * | 1984-10-25 | 1989-12-14 | Sgs Thomson Microelectronics | Procedimento perfezionato per la fabbricazione di dispositivi a semiconduttore dmos. |

| JPS61256769A (ja) * | 1985-05-10 | 1986-11-14 | Toshiba Corp | 半導体装置 |

| JPH01501272A (ja) | 1986-10-27 | 1989-04-27 | ヒユーズ・エアクラフト・カンパニー | ストライプ状のチャンネルのトランジスタおよびその製造方法 |

| JPH0231464A (ja) * | 1988-07-21 | 1990-02-01 | Mitsubishi Electric Corp | 半導体装置 |

| JPH02105467A (ja) * | 1988-10-13 | 1990-04-18 | Nec Corp | Mos型半導体装置 |

| JPH02159070A (ja) * | 1988-12-13 | 1990-06-19 | Matsushita Electric Ind Co Ltd | 半導体装置とその製造方法 |

| JPH02196468A (ja) * | 1989-01-25 | 1990-08-03 | Nec Corp | 半導体装置 |

| JPH0738447B2 (ja) * | 1989-02-02 | 1995-04-26 | 松下電器産業株式会社 | Mos型半導体装置 |

| JPH036863A (ja) * | 1989-06-05 | 1991-01-14 | Takehide Shirato | 半導体装置 |

| US5210437A (en) * | 1990-04-20 | 1993-05-11 | Kabushiki Kaisha Toshiba | MOS device having a well layer for controlling threshold voltage |

| JPH05283687A (ja) * | 1992-03-31 | 1993-10-29 | Oki Electric Ind Co Ltd | 半導体素子の製造方法 |

-

1996

- 1996-08-13 JP JP23255296A patent/JP3949193B2/ja not_active Expired - Fee Related

-

1997

- 1997-08-08 US US08/907,579 patent/US6218714B1/en not_active Expired - Fee Related

- 1997-08-13 KR KR1019970039449A patent/KR100443436B1/ko not_active IP Right Cessation

-

2001

- 2001-03-16 US US09/811,238 patent/US6617647B2/en not_active Expired - Lifetime

-

2002

- 2002-08-13 KR KR1020020047936A patent/KR100453400B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| US20010023105A1 (en) | 2001-09-20 |

| US6617647B2 (en) | 2003-09-09 |

| JPH1065163A (ja) | 1998-03-06 |

| JP3949193B2 (ja) | 2007-07-25 |

| KR100453400B1 (ko) | 2004-10-20 |

| US6218714B1 (en) | 2001-04-17 |

| KR19980018784A (ko) | 1998-06-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100460550B1 (ko) | 절연게이트형반도체장치및그제작방법 | |

| JP4014677B2 (ja) | 絶縁ゲイト型半導体装置 | |

| KR100443436B1 (ko) | 절연게이트형반도체장치 | |

| KR100443437B1 (ko) | 절연게이트형반도체장치및그제작방법 | |

| JP4103968B2 (ja) | 絶縁ゲイト型半導体装置 | |

| JP4044276B2 (ja) | 半導体装置及びその製造方法 | |

| JP3462301B2 (ja) | 半導体装置及びその製造方法 | |

| JP4499774B2 (ja) | 絶縁ゲイト型半導体装置 | |

| JPH11224946A (ja) | 半導体装置およびその作製方法 | |

| JP4053102B2 (ja) | 半導体装置およびその作製方法 | |

| JP4628399B2 (ja) | 半導体装置 | |

| JP4896699B2 (ja) | 絶縁ゲイト型半導体装置およびその作製方法 | |

| JP4563422B2 (ja) | 半導体装置 | |

| JP4545825B2 (ja) | 半導体装置 | |

| JP5312489B2 (ja) | 半導体装置 | |

| Pal et al. | MOS Fabrication Technology | |

| JP4684358B2 (ja) | 半導体装置の作製方法 | |

| JP2007149853A (ja) | 半導体装置およびその製造方法 | |

| JP2009239306A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A107 | Divisional application of patent | ||

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20130701 Year of fee payment: 10 |

|

| FPAY | Annual fee payment |

Payment date: 20140701 Year of fee payment: 11 |

|

| LAPS | Lapse due to unpaid annual fee |