JP4053102B2 - 半導体装置およびその作製方法 - Google Patents

半導体装置およびその作製方法 Download PDFInfo

- Publication number

- JP4053102B2 JP4053102B2 JP26921496A JP26921496A JP4053102B2 JP 4053102 B2 JP4053102 B2 JP 4053102B2 JP 26921496 A JP26921496 A JP 26921496A JP 26921496 A JP26921496 A JP 26921496A JP 4053102 B2 JP4053102 B2 JP 4053102B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- impurity

- channel formation

- channel

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明が属する技術分野】

本明細書で開示する発明は、SOI(Silicon-On-Insulator)構造を有する絶縁ゲイト型半導体装置、特に絶縁ゲイト型電界効果トランジスタ(以後、単にIG−FETと略記する)の構成およびその作製方法に関する。SOI構造を有する絶縁ゲイト型半導体装置としてはSOS(Silicon-On-Sapphire )基板やSIMOX(Separation-by-Implanted Oxygen)基板などの上に形成された半導体装置を挙げることができる。

【0002】

特に、チャネル長が0.35μm以下(特に、0.1 μm以下)の微細素子を作製する場合において効果を発揮する技術である。従って、本発明はIG−FETを集積化して構成されたIC、VLSI、ULSIなどの様々な半導体集積化回路に応用することが可能である。

【0003】

なお、本明細書中における「半導体装置」という言葉は「半導体を利用して活用される装置」を意味しており、IG−FETの様な半導体素子は言うに及ばず、半導体素子を集積化した集積化回路、さらにはその集積化回路を組み込んだ電子機器までを「半導体装置」の範疇に含めるものとする。なお、本明細書中では説明の便宜上、必要に応じて半導体素子、集積化回路、電子機器等の言葉を使い分けることとする。

【0004】

【従来の技術】

近年、VLSIなどの集積化回路は益々微細化の一途を辿る傾向にあり、配線の幅も0.35〜0.1 μm以下、さらには 0.01 μm以下といったディープサブミクロン領域の加工寸法が要求される様になってきている。

【0005】

それと同時に低消費電力化が要求される様になり、CMOS形ICの低消費電力特性が必要不可欠な構成となりつつある。この様なCMOS形ICを微細化するとN型FETとP型FETとの間で発生するラッチアップ現象が問題となるが、それを解決したのがSOI構造のIG−FETである。

【0006】

また、基板と素子とが完全に絶縁されるため、そこに生じる寄生容量を大幅の低減することが可能となり、高速動作性も追及することができる。

【0007】

以上の様に、SOI構造を有する半導体装置は次世代の高速素子として極めて注目されており、今後、益々需要が高まると予想される。

【0008】

この様な半導体素子の微細化はスケーリング則に従って進められてきており、微細化が集積化回路の特性向上をもたらすことは一般的に知られていた。しかしながら、サブミクロン領域の微細加工となると単純にはスケーリング則に従わない問題が生じる様になる。

【0009】

その様な問題として短チャネル効果という現象が代表的に知られている。短チャネル効果とは、ゲイト電極の線幅が短くなる、即ちチャネル形成領域が短くなるにつれて、チャネル形成領域の電荷がゲイト電圧だけでなく、ソース/ドレイン領域の空乏層電荷や電界および電位分布の影響を大きく受ける様になるために引き起こされる現象である。

【0010】

この様子を簡略化して図3に示す。図3はSIMOX基板上に形成された従来の半導体装置であり、301はシリコン基板、302は酸素注入により形成した埋め込み酸化膜層である。埋め込み酸化膜層302の上には結晶半導体(単結晶シリコン層)が配置されており、それを利用してソース領域303、ドレイン領域304、チャネル領域305、ゲイト電極306である。また、308で示される点線はドレイン電圧Vdが小さい時に形成される空乏層を表している。

【0011】

通常、チャネル領域305を流れる電流はゲイト電圧Vgのみで制御される。この場合、308で示される様に、チャネル領域305近傍の空乏層はチャネルに概略平行となり、均一な電界が形成される。

【0012】

しかし、ドレイン電圧Vdが高くなると、ドレイン領域304近傍の空乏層がチャネル領域305、ソース領域303の方へと広がり、309で示される実線で表される様に、ドレイン空乏層の電荷や電界がソース領域303、チャネル領域305近傍の空乏層へと影響を及ぼす様になる。即ち、オン電流が複雑な電界分布により変化し、ゲイト電圧Vgのみで制御することが困難な状況となるのである。

【0013】

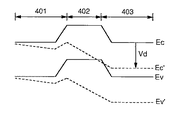

ここで、短チャネル効果が生じる場合におけるチャネル形成領域周辺のエネルギー状態を図4を用いて説明する。図4において実線で示す状態図はドレイン電圧が0Vの時のソース領域401、チャネル形成領域402、ドレイン領域403のエネルギーバンド図である。

【0014】

この状態において十分大きいドレイン電圧Vdが印加されると、図4において点線で示す様な状態へと変化する。即ち、ドレイン電圧Vdにより形成されたドレイン領域403の空乏層電荷や電界が、ソースおよびチャネル領域401、402の空乏層電荷に影響を与え、エネルギー(電位)状態はソース領域401からドレイン領域403にかけて連続的に変化する様になる。

【0015】

そして、このような短チャネル効果が半導体素子、例えばIG−FETに与える影響としてはしきい値電圧(Vth)の低下やパンチスルーによる素子耐圧の低下等の現象がよく知られている。また、パンチスルー現象によってドレイン電流に対するゲイト電圧の影響が低下するとサブスレッショルド特性が悪くなることも知られている。

【0016】

まず、しきい値電圧の低下はNチャネル型FETに対してもPチャネル型FETに対しても同様に見られる現象である。また、この低下の度合いはドレイン電圧に依存するばかりでなく、基板不純物濃度、ソース/ドレイン拡散層深さ、ゲイト酸化膜厚、基板バイアス等の様々なパラメータに依存する。

【0017】

しきい値電圧の低下は消費電力を小さくするといった意味では望ましいことであるが、一般的には集積回路の駆動電圧が小さくなることで周波数特性が高くならないといったデメリットが問題となってしまう。

【0018】

また、チャネル長が短くなるとドレイン側の空乏層がソース側の空乏層と繋がる状態を形成してソース近傍の拡散電位を下げるためチャネルが形成されていなくてもソース/ドレイン間に電流が流れる様になる。これがパンチスルーと呼ばれる現象である。

【0019】

パンチスルー現象が生じると飽和領域でもドレイン電流が飽和しなくなるためドレイン電圧の増加に伴って大電流が流れる様になり、ソース/ドレイン間の素子耐圧が大幅に低下することが問題となっていた。

【0020】

また、パンチスルー現象に伴うサブスレッショルド特性の劣化とはサブスレッショルド係数(S値)が大きくなる、即ちFETのスイッチング特性が劣化することを意味している。ここでサブスレッショルド特性に及ぼす短チャネル効果の影響を図5に示す。

【0021】

図5は横軸にゲイト電圧Vg、縦軸にドレイン電流Idの対数をとったグラフであり、501の領域における傾き(サブスレッショルド特性)の逆数がS値である。この図5ではチャネル長を徐々に短くした時の特性の変化を比較しており、矢印の方向に向かってチャネル長は短くなっている。

【0022】

その結果、チャネル長が短くなるに従って特性の傾きが小さくなる、即ちS値が大きくなる傾向にあることが確認できる。このことは、チャネル長が短くなるに従ってFETのスイッチング特性が劣化することを意味する。

【0023】

以上説明した様な短チャネル効果を抑制する手段として様々な技術が提案されてきている。例えば、埋め込み酸化膜で基板と素子とを絶縁するタイプのSOI構造(貼り合わせ技術やイオン注入技術を利用したもの等)では、埋め込み酸化膜の膜厚を薄くすることが短チャネル効果の抑制に効果的であることが報告されている。しかし、これだけでは十分な解決までには至らなかった。

【0024】

また、チャネル長が0.1 μm程度と極めて短いSOI構造の半導体装置は、チャネル領域における不純物元素の存在確率が極めて小さい(1個乃至数個)という特徴を有しており、室温でも電子の移動速度が通常よりも速くなる現象(速度オーバーシュート効果)が確認されている。(K.Ohuchi et al.,Jpn.J.Appl.Phys. 35, 960(1996). )。

【0025】

さらに、その効果を利用して高速動作性を向上させた高速半導体装置も発表されている。しかしながら、その様な高速半導体装置においては、前述の様な短チャネル効果によるパンチスルー現象とそれに伴う耐圧の劣化といった諸問題は解決されていないのが現状である。

【0026】

また、短チャネル効果によるしきい値電圧の低下を抑制するための手段としては、チャネル形成領域全体に均一に一導電性を付与する不純物元素を添加して、その添加量でもってしきい値電圧を制御する方法が採られてきた。しかし、この方法では添加した不純物がキャリアを散乱させる原因となるのでキャリアの移動度を低下させてしまうことが問題となっていた。

【0027】

また、SOI基板のマザーサブストレートとなる単結晶シリコン基板の作製方法には、極めて酸素含有量の低いFZ法と、応力緩和および反り防止のためにある程度の酸素を含有させたCZ法で形成されたものがある。通常、メモリICやロジックIC用にはCZ法による単結晶シリコン基板が用いられる。

【0028】

しかし、CZ法で形成された単結晶シリコン基板は酸素含有量が減少するに従って熱履歴などによる反り量が増加する特徴があり、逆に反り量を十分低減しうるレベルまで酸素含有量を上げる(通常、 1〜2 ×1018atoms/cm3 程度)と、酸素原子がキャリアの移動を妨げてしまう様なことが起こりうる。

【0029】

【発明が解決しようとする課題】

現状の半導体産業においては、極限まで集積化された半導体集積回路が求められており、個々の半導体素子の微細化をどこまで追求できるかが鍵となっている。しかし、ディープサブミクロン領域のファインパターンを形成する技術が開発されたとしても、前述の様な短チャネル効果の問題が素子の微細化を阻む致命的な障害となっていた。

【0030】

本発明は上記問題点を鑑みてなされたものであり、半導体素子の微細化に伴う短チャネル効果を効果的に抑制するための技術を開示するものである。そして、短チャネル効果によって実現が困難であったディープサブミクロン領域の微細素子を形成可能とすることを課題とする。

【0031】

【課題を解決するための手段】

本明細書で開示する発明の構成は、

絶縁性基板または絶縁層上に形成された結晶半導体を利用して形成されたソース領域、ドレイン領域およびチャネル形成領域と、

前記チャネル形成領域上に形成されたゲイト絶縁膜およびゲイト電極と、

を少なくとも有するSOI構造で構成される絶縁ゲイト型半導体装置であって、

前記チャネル形成領域はキャリアが移動する領域と、

前記ドレイン領域より前記チャネル形成領域およびソース領域に向かって広がる空乏層をピニングするために人為的かつ局部的に形成された不純物領域と、

を有し、

前記不純物領域にはエネルギーバンド幅(Eg)を広げる不純物元素が添加されていることを特徴とする。

【0032】

また、他の発明の構成は、

絶縁性基板または絶縁層上に形成された結晶半導体を利用して形成されたソース領域、ドレイン領域およびチャネル形成領域と、

前記チャネル形成領域上に形成されたゲイト絶縁膜およびゲイト電極と、

を少なくとも有するSOI構造で構成される絶縁ゲイト型半導体装置であって、

前記チャネル形成領域はキャリアが移動する領域と、

不純物元素の添加により所定のしきい値電圧に制御するために人為的かつ局部的に形成された不純物領域と、

を有し、

前記不純物領域にはエネルギーバンド幅(Eg)を広げる不純物元素が添加されていることを特徴とする。

【0033】

また、他の発明の構成は、

絶縁性基板または絶縁層上に結晶半導体を形成する工程と、

前記結晶半導体を利用してソース領域、ドレイン領域およびチャネル形成領域とを形成する工程と、

前記チャネル形成領域において人為的かつ局部的に不純物領域を形成する工程と、

前記チャネル形成領域上にゲイト絶縁膜およびゲイト電極とを形成する工程と、

を少なくとも有するSOI構造で構成される絶縁ゲイト型半導体装置の作製方法において、

前記チャネル形成領域はキャリアが移動する領域と前記不純物領域とで構成され、

前記不純物領域にはエネルギーバンド幅(Eg)を広げる不純物元素が人為的かつ局部的に添加されていることを特徴とする。

【0034】

本発明の主旨は、チャネル形成領域に対して人為的かつ局部的に形成した不純物領域により、ドレイン領域からチャネル形成領域に向かって広がる空乏層を効果的に抑制し、短チャネル効果によって引き起こされるパンチスルー現象、サブスレッショルド特性の劣化、耐圧の劣化などの諸問題を防止することにある。

【0035】

なお、本出願人はあたかもチャネル形成領域に不純物領域のピンを形成することに似ていることから、本発明によるデバイスをピニング型半導体装置と呼んでいる。なお、本明細書中において「ピニング」とは「抑止」を意味しており、「ピニングする」とは「抑止する」という意味で用いている。

【0036】

即ち、チャネル形成領域に対して局部的に不純物領域を形成し、その領域をエネルギー的な障壁として利用するものである。そして、不純物領域をエネルギー的な障壁として利用することでドレイン領域側の空乏層がチャネル形成領域側へ広がるのをエネルギー的に抑止し、それによってチャネル形成領域に形成される電界がゲイト電圧のみによって制御される様にする。

【0037】

本発明は上記構成をなすために不純物領域を形成する不純物元素としてエネルギーバンド幅(Eg)を広げる不純物元素を用いている。その様な不純物元素としては炭素(C)、窒素(N)、酸素(O)から選ばれた一種または複数種類の元素が挙げられる。

【0038】

この場合、添加された不純物はチャネル形成領域に局部的にエネルギーバンド幅の大きいエネルギー障壁を形成する。この様に炭素、窒素、酸素を用いた場合には、図6(A)で示す状態であったチャネル形成領域のエネルギーバンドを図6(B)で示す状態とし、エネルギーバンド幅(Eg)を広げることで障壁ΔE(拡散電位差またはビルトイン電位差と呼ばれる)が形成される。

【0039】

また、本発明において「キャリアが移動する領域」が真性または実質的に真性であることはSOI構造の半導体装置に特有の注目すべき特徴である。なお、本明細書において真性な領域とは、例えばサファイア基板上にエピタキシャル成長させた単結晶シリコン層の様な不純物元素を含有しない領域、またはN型やP型を付与する不純物元素および炭素、窒素、酸素といった不純物元素を意図的に添加しない領域を指している。

【0040】

また、実質的に真性とは、結晶半導体(本明細書では単結晶シリコンを代表例とする)中において、意図的にN型やP型を付与する不純物元素を添加しなくても生ずる導電型を相殺した領域、又はしきい値制御が可能な範囲においてソースおよびドレイン領域と同一導電型を呈する領域を指している。

【0041】

また、実質的に真性な領域において、結晶半導体(結晶シリコン)表面近傍における一導電性を付与する不純物元素(リンまたはボロン)の濃度は 5×1015atoms/cm3 以下(好ましくは 5×1014atoms/cm3 以下)であり、酸素濃度は 2×1018atoms/cm3 以下(好ましくは 1×1017atoms/cm3 以下)である。

【0042】

なお、ここで言う結晶半導体表面近傍とはデバイス素子として機能しうる領域を指しており、SOI基板の単結晶シリコン層、もしくは、少なくともキャリアが移動する領域(反転層)を含む領域を指す。また、本発明の特徴である不純物領域には不純物元素が大量に含まれていて当然であるので、上記不純物濃度の範囲に当てはまらないことは言うまでもない。

【0043】

また、本明細書中においては結晶半導体として単結晶シリコンを代表例とするが、この単結晶シリコンとは現在のIC、LSIレベルで一般的に用いられている水準の単結晶シリコンは勿論のこと、さらに高水準の単結晶シリコン(究極的には宇宙空間で作製された様な理想状態の単結晶シリコン)もその範疇に含まれるものとする。

【0044】

また、SOI構造は大別して2種類があり、一つはSOS基板に代表される様に絶縁性基板上に単結晶シリコン層を成長させた構造である。もう一つはSIMOX基板やウェーハ接合SOIに代表される様に単結晶シリコン基板中に絶縁層を形成させた構造である。特にSIMOX基板は1986年以降SOI構造の主要な形成技術となっている。

【0045】

本発明はSOI構造の作製方法に関係なく、SOI基板全般に活用することができる。即ち、半導体装置を作製する際に、どの様な方法でSOI基板を作製するか、もしくはどの様な方法で単結晶シリコン層を得るかは、作製者が適宜決定することができる。

【0046】

【発明の実施の形態】

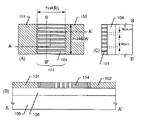

ここでSIMOX基板上に形成された半導体装置に対して本発明を適用した場合について図1を用いて説明する。なお、説明はNチャネル型FETを例にとって行う。

【0047】

図1(A)に示すのは本発明のIG−FETのソース領域、ドレイン領域およびチャネル形成領域を上面から見た時の状態の模式図である。なお、101がソース領域、102がドレイン領域、103がチャネル形成領域である。

【0048】

そして、本発明の特徴はチャネル形成領域103内に人為的かつ局部的に不純物領域104が形成されている点である。ここでは不純物領域104を線状パターン形状に形成した場合を例とするが、不純物領域はドットパターン状に設けることも可能である。

【0049】

なお、不純物領域104をチャネル方向(ソース−ドレイン間を結ぶ方向またはキャリアが移動する方向)と概略平行な線状パターン形状に設けた場合、不純物領域が側壁となってキャリアの移動を規定するエネルギー的なレールを構成するため、キャリア同士の衝突による散乱の発生確率が低減されて移動度が向上するといった利点が生まれるので望ましい。

【0050】

また、本出願人はキャリアの移動するパス、即ち不純物領域と不純物領域との間の領域をポテンシャルスリット領域又はレーン領域と呼んでいる。

【0051】

ここではチャネル形成領域103内の一端から他端に向かって(例えば、ソース領域101からドレイン領域102に向かって)チャネル方向と概略平行に線状パターン形状を有する不純物領域104を形成した場合についての説明を行う。また、添加する不純物として酸素を用いた場合を例とする。

【0052】

添加された不純物(酸素)はチャネル形成領域103内に局部的にエネルギーバンド幅の大きいエネルギー障壁を形成する。図1の様に不純物元素として酸素を用いた場合には、前述の様に図6(A)で示す状態であったチャネル形成領域103のエネルギーバンドを図6(B)で示す状態とし、エネルギーバンド幅(Eg)を広げることで障壁ΔEを形成する。また、酸素を添加して形成された不純物領域は例えば SiOx で示される様な構造の絶縁性の高抵抗領域となり電気的にも障壁となる。

【0053】

特に、図1(A)に示す様にドレイン領域102とチャネル形成領域103との接合部は最も電界の変化の激しい領域であるので、この位置に不純物領域104がかかる様にしておくことが望ましい。また、ゲイト電極による電界がドレイン領域102内にもおよぶ場合はドレイン領域102内部に入り込む様に不純物領域104を形成すると良い。逆にソース領域101内部にはなるべく不純物領域104が入り込まない構成とすることが好ましい。

【0054】

また、この場合の様に不純物元素として酸素(他にも炭素、窒素等)を用いる場合においては、どの場合も不純物領域を絶縁性のエネルギー障壁として活用するのでNチャネル型TFTとPチャネル型TFTとで共通化することができる。このことは、本発明をCMOS回路に適用した場合に製造工程を簡略する上で有利であることを意味する。

【0055】

また、これらの不純物元素は、母体基板がシリコンである場合、シリコン原子と強く結合するので加熱処理などにより再拡散する恐れが少ない。

【0056】

また、本発明は 0.35 μm以下(特に、0.1 μm以下)、さらには0.01μm以下といったディープサブミクロン領域の微細加工を必要とする微細素子を形成する際に極めて効果的である。従って、チャネル形成領域の長さ(チャネル長またはソース/ドレイン間距離)も0.01〜0.35μmといった短いものとなるため、不純物領域はさらに細かいパターンを切らなければならない。

【0057】

例えば、線状パターン状の不純物領域を形成する際にレジストマスクを利用する場合にはレジストマスクに開孔を設けるパターニングは解像度の問題から通常の露光法を用いることができない。その様な場合においては、KrFやArF等のエキシマレーザーを用いた露光法、電子(ビーム)描画法、 FIB(Focussed Ion Beam )法等の技術を用いて行うことでディープサブミクロン領域の微細パターンを実現すれば良い。

【0058】

また、不純物領域はパターニングにより人為的に配列して形成されるので、図1(A)の様な配置だけでなく、任意の様々な配置とすることが可能である。

【0059】

次に、図1(A)に示すソース領域/チャネル形成領域/ドレイン領域の構成を有する絶縁ゲイト型半導体装置(IG−FET)を駆動させた際に、どの様にして短チャネル効果が抑制されるかを以下に説明する。

【0060】

まず、図1(A)をA−A’で切った断面図を図1(B)に示す。105はシリコン基板、106は埋め込み酸化膜である。不純物領域104はソース領域101とドレイン領域102とを繋ぐ様にして形成されているので、A−A’で切った断面では図1(B)の様に不純物領域104が現れる。

【0061】

また、図1(A)をB−B’で切った断面図を図1(C)に示す。図1(C)はチャネル方向と垂直にチャネル形成領域103を切断した断面を表していることになる。

【0062】

この時、ある不純物領域104の幅はwpi,nで表され、その不純物領域間の間隔(ポテンシャルスリット領域の幅)はwpa,mで表される。ここでn、mはチャネル形成領域103内において、wpi,nがn番目の不純物領域の幅であり、wpa,mがm番目のポテンシャルスリット領域(キャリアの移動するパス)であることを意味している。

【0063】

ここまでの説明は単に構造についての説明であったが、次にその効果についての説明を行う。ここで図2(A)に示すのは、本発明のIG−FETのチャネル形成領域のみに着目した模式図である。

【0064】

まず、図1(B)に示す様な構造を有する半導体装置に対してゲイト電圧、ドレイン電圧を印加した場合には、図2(A)に示す様な状態でソース側空乏層201、チャネル側空乏層202、ドレイン側空乏層203が形成される。即ち、ドレイン側空乏層203は不純物領域204が障壁となってソース側への広がりを防止された形となる。なお、205は埋め込み酸化膜の一部である。

【0065】

図1(B)では判りにくいが不純物領域204は図1(A)に示す様に配置されており、チャネル方向から見ると図1(C)の様な状態で配置されている。従って、チャネル形成領域103を塞ぐ格子状のフィルターでドレイン側空乏層の広がりを抑えているというモデルで考えれば理解しやすい。

【0066】

従って、本発明による構造の半導体装置においては、図2(A)に示す様に空乏層が実質的に相互に干渉することなく分断される。即ち、ソース側空乏層201、チャネル側空乏層202が、ドレイン側空乏層203の影響を受けないで分布することになるので、エネルギー状態は図2(B)に示す状態となる。

【0067】

即ち、図4に示した従来のエネルギー状態図と異なり、チャネル領域のエネルギー状態は殆どゲイト電圧による電界のみに制御されるので、チャネル領域に対して概略平行な形状を有する。従って、短チャネル効果特有のパンチスルー現象の様な問題がなく、ドレイン耐圧の高い半導体装置を作製することができる。

【0068】

さらに、図2(A)に示す様に、本発明においてはドレイン電圧が高くなった状態においても空乏層の占める体積が図3に示した様な従来のものと比べて減少しているため、従来よりも空乏層電荷が小さく、空乏層容量が小さい特徴がある。ここで、S値を導出する式は次式で表される。

【0069】

【数3】

【0070】

即ち、前述の様に、図5に示すグラフにおいて501で示される領域における傾きの逆数を表していることが判る。また、数3の式は近似的に次式の様に表すことができる。

【0071】

【数4】

【0072】

数4において、kはボルツマン定数、Tは絶対温度、qは電荷量、Cd は空乏層容量、Citは界面準位の等価容量、Coxはゲイト酸化膜容量である。従って、本発明によれば空乏層容量Cd が従来よりも十分小さくなるので、S値を85mV/decade 以下(好ましくは70mV/decade 以下)の小さな値とすることができる、即ち優れたサブスレッショルド特性を得ることができるのである。

【0073】

また、本発明が目指すところは、空乏層容量Cd および界面準位の等価容量Citを0に可能な限り近づけることである。即ち、Cd =Cit=0となる理想状態におけるS値(60mV/decade )に近づけることにある。

【0074】

また、チャネル形成領域が図1(C)に示す構造となっていることは短チャネル効果によるしきい値電圧の低下を緩和する上で非常に重要である。なぜならば、図1(C)に示す構造が意図的に狭チャネル効果を生み出すために必要な構成だからである。

【0075】

この狭チャネル効果とは、元来バルクシリコン上に形成したMOSFETで確認されている現象であり、チャネル幅が狭くなった時に素子を分離するフィールド酸化膜のバーズビークやチャネルストッパーの不純物拡散の影響等を受けてしきい値電圧が増加するという現象である。

【0076】

本発明の構成となる思想の一つは、チャネル形成領域に人為的に不純物領域を形成・配置することで意図的に狭チャネル効果を生じさせることである。そして、本発明の構成は不純物領域間の距離(図1(C)におけるwpa,mに相当する)を3 〜 300 nm( 好ましくは3 〜 100 nm) の範囲で精密に制御することでしきい値電圧の制御を行うという思想に基づいている。

【0077】

例えば、図1(C)に示す様にある断面に着目すると、チャネル形成領域の幅Wは不純物領域104によって分断され、実質的に狭いチャネル幅wpa,mを持つ複数のチャネル形成領域の集合体と見なすことができる。

【0078】

即ち、その複数の狭いチャネル幅wpa,mを有する領域において狭チャネル効果が得られると考えられる。マクロ的に見ると図1(A)に示す様にチャネル形成領域全体にこの様な狭チャネル効果が得られる領域が存在するので、全体的にも狭チャネル効果が得られ、しきい値電圧が増加すると考えられる。

【0079】

従って、チャネル長に短くなることで短チャネル効果によってしきい値電圧が低下したとしても、以上の理由により狭チャネル効果によってしきい値電圧を意図的に増加させてしきい値制御を行うことができるので、結果的にしきい値電圧の変化を緩和することが可能となる。

【0080】

以上の構成でなる本発明について、以下に記載する実施例でもって詳細な説明を行うこととする。また、これより記載する実施例は、本発明の構成の一例を示すものであり、半導体装置作製者の必要に応じて様々な応用を実施することが可能である。

【0081】

従って、特許請求の範囲に記載された事項は、以下に記載する実施例以外の応用であっても、本発明の構成をもってなしうる全ての発明をも包含するものと考える。

【0082】

【実施例】

〔実施例1〕

本発明を用いてSIMOX基板上に絶縁ゲイト型電界効果トランジスタを形成する例を図7を用いて説明する。なお、本実施例ではNチャネル型FETとPチャネルFETとを相補的に組み合わせたCMOS回路を形成する場合の例について説明する。

【0083】

まず、弱いN型またはP型導電性を有する単結晶シリコン基板701を用意する。そして、1×1018atoms/cm2 程度のドーズ量で酸素イオンを注入し、800〜1300℃の範囲内で加熱処理を行うことで埋め込み酸化膜702を形成する。こうして、厚さ0.05〜0.5 μmの埋め込み酸化膜702と厚さ10 〜 200 nm(好ましくは、20 〜 60 nm)の単結晶シリコン層703を得る。

【0084】

この際、SOI技術の最も大きな特徴の一つは、得られた単結晶シリコン層703に含まれる不純物元素(母体となる単結晶シリコン基板701に予め含まれてしまうもの)は1個乃至数個程度と殆ど皆無に等しく、極めて高純度の真性または実質的に真性な単結晶シリコン層が得られる点である。

【0085】

また、勿論埋め込み酸化膜702の膜厚や単結晶シリコン層703の膜厚は本実施例で示す範囲の値に限定されるものではなく、必要に応じて適宜調節することは可能である。SIMOX基板に関する詳細な説明は、例えば、丸善株式会社,志村史夫著,半導体シリコン結晶工学,平成5年9月30日発行,P217以下を参照すると良い。

【0086】

こうして図7(A)に示す様なSIMOX基板が得られる。勿論、SIMOX基板ではなく、ウェーハ貼り合わせ技術を用いて形成したSOI基板、サファイア基板の様な絶縁性基板上に単結晶シリコン層を成長させたSOS基板、多孔質シリコンの酸化を利用したFIPOS(Full Isolation by Porous Oxidized Silicon )基板等、他のタイプのSOI基板を用いても構わない。

【0087】

図7(A)の状態が得られたら、熱酸化処理を施すことにより図示しない薄い熱酸化膜を形成し、その上に窒化珪素膜でなるマスクパターン704、705を形成する。その際、マスクパターン704は後のNチャネル型FET上に、マスクパターン705は後のPチャネル型FET上に配置する。

【0088】

そして、その状態で1000〜1200℃程度の高温で熱酸化を行い、素子分離のためにフィールド酸化膜706を形成する。こうして、Nチャネル型FETの活性層となる領域707とPチャネル型FETの活性層となる領域708を得る。

【0089】

こうして図7(B)に示す状態が得られたら、マスクパターン704、705および図示しない熱酸化膜を除去する。そして、P(リン)を添加してNチャネル型FETのソース領域709、ドレイン領域710を形成し、さらにB(ボロン)を添加してPチャネル型FETのソース領域711、ドレイン領域712を形成する。

【0090】

この際、リンおよびボロンはレジストマスクを用いて打ち分ければ良い。また、この際に不純物を添加しない領域は真性または実質的に真性な領域であり、Nチャネル型FETのチャネル形成領域713、Pチャネル型FETのチャネル形成領域714を構成する。(図7(C))

【0091】

以上の様に、チャネル形成領域を真性または実質的に真性な領域とした場合、半導体装置の活性層は、Nチャネル型FETを例にすると、N+ (ソース領域)−I(チャネル形成領域)−N+ (ドレイン領域)の様な構成となる。ここで、N+ は強いN型を示すことを意味しており、Iは真性または実質的に真性であることを意味している。

【0092】

この様な構成の他にも、例えばN+ (ソース領域)−N--(チャネル形成領域)−N+ (ドレイン領域)、P+ (ソース領域)−P--(チャネル形成領域)−P+ (ドレイン領域)の様な構成を採ることも可能である。なお、N--は極弱いN型を、P--は極弱いP型を示すことを意味している。

【0093】

この様な構成は、移動度が向上する利点を有する反面、耐圧が低下する欠点が問題となっていた。しかしながら、本発明を利用することで高い耐圧特性を有する半導体装置を作製することが可能であるため、高い移動度と高い耐圧とを同時に満たすことができる。

【0094】

次に、図7(C)に示す状態が得られたら、図7(D)に示す様に、チャネル形成領域713、714に対して炭素(C)、窒素(N)、酸素(O)から選ばれた一種または複数種類の元素を添加し、空乏層のストッパーとなる不純物領域715、716を形成する。本実施例では不純物元素として酸素を用い、添加する領域715、716はパターニングにより図示しないレジストマスクに開孔を設けて選択的に設計する。

【0095】

なお、不純物領域715、716は極めて微細な加工寸法で形成する必要があるため精巧なリソグラフィ技術を必要とする。そのためには、電子ビームを用いる技術(電子描画法)、イオンビームを用いる技術(FIB 法) 、エキシマレーザーを用いる技術等を用いて線状パターン形状の露光を行えば良い。

【0096】

またこの時、ポテンシャルスリット領域の幅(wpa,m)は3 〜 300 nm( 好ましくは3 〜 100 nm) の範囲内に制御する。また、全ての間隔(wpa,m)は±20%以内(好ましくは±5 %以内)に納まる様に制御する。このポテンシャルスリット領域の幅(wpa,m)は狭チャネル効果に直接的に影響を与えるので精密に制御することが重要なのである。

【0097】

なお、ポテンシャルスリット領域の幅の下限界である3 nmという値は量子効果が起こらない限界値として定めている。本発明ではポテンシャルスリット領域の幅を量子効果の生じない又は現れない範囲内で制御する様に注意している。

【0098】

従って、図1(A)に示す上面図の様に配置された不純物領域715、716はポテンシャルスリット領域の幅(wpa,m)が全て揃った状態で形成される。そのため、しきい値電圧のバラツキ(狭チャネル効果のバラツキに起因する)や発熱のバラツキ(ポテンシャルスリット領域を流れる電流密度のバラツキに起因する)を効果的に抑制することができる。

【0099】

また、半導体装置の耐圧を効果的に向上させるためには図7(D)に示す様に不純物領域715、716をドレイン領域710、712に入り込む様に配置することが有効である。その際、ソース領域は入り込む様に配置してもしなくても良いが入り込まない方が好ましい(本実施例ではチャネル形成領域の境界を明確にするためソース領域にも不純物領域が入り込む場合を例とする)。

【0100】

また、チャネル形成領域とソース/ドレイン領域間にLDD領域を設ける構成とする場合には、LDD領域内部にまで、又はLDD領域を超えてドレイン領域内部にまで渡って不純物領域を形成することが好ましい。以上の様な構成は、半導体装置の耐圧をより向上させるために有効である。

【0101】

図7(D)に示す様な状態が得られたら、800 〜1200℃程度の温度範囲による熱酸化処理を行い10 〜 50 nmの熱酸化膜717、718を形成する。この熱酸化処理により形成された薄い熱酸化膜717、718はそのままゲイト絶縁膜として機能する。また、活性層/ゲイト絶縁膜界面は界面準位の少ない良好なものとなる。

【0102】

また、この熱酸化工程によって不純物領域715、716に添加された酸素がシリコンと反応して酸化絶縁物(酸化シリコン)に変成する。この状態では不純物領域715、716は共に、電気的に完全な絶縁領域となる。また、この酸化絶縁物中において、含有される酸素濃度の最大値は 1×1019〜 2×1022atoms/cm3 の範囲となる。

【0103】

なお、上記熱酸化工程をハロゲン雰囲気で行うことも好ましい。その場合、不純物領域715、716とポテンシャルスリット領域との界面に偏析したNi(ニッケル)、Cu(銅)などの重金属をゲッタリング除去することができる。

【0104】

これら重金属は単結晶シリコンの形成過程等において内部に少なからず残留するものであり、キャリアの再結合中心となって移動度を低下させてしまう恐れがある。従って、熱酸化工程をハロゲン雰囲気で行えばハロゲン元素(例えば、塩素、弗素など)による金属元素のゲッタリング効果を期待することができる。

【0105】

さらに、チャネル形成領域713、714の上方において熱酸化膜717、718上にゲイト電極としてポリシリコン膜719、720を形成する。ゲイト電極719、720は成膜する段階で予め不純物元素を添加しておいて導電性を持たせれば良い。こうして図8(A)に示す状態が得られる。

【0106】

その後、図8(B)に示す様に、ゲイト電極719、720を覆う様にして窒化珪素膜を300 nmの厚さに成膜し、エッチバック法を用いてゲイト電極719、720の側面のみにサイドウォール721、722を残存させる。この際、ソース/ドレイン領域のゲイト絶縁膜は同時に除去される。

【0107】

次に、この状態で全面にスパッタ法により図示しないチタン膜を成膜し、加熱、レーザーアニール、ランプアニールなど手段のよるシリサイド形成を行う。この工程により、Nチャネル型FETのソース領域709およびドレイン領域710の表面ならびにゲイト電極719の表面にはチタンシリサイド723〜725が形成される。

【0108】

また、同時にPチャネル型FETのソース領域711およびドレイン領域712の表面ならびにゲイト電極720の表面にはチタンシリサイド726〜728が形成される。

【0109】

チタンシリサイド723〜728は極めて低抵抗であるので、後に形成する配線とのオーミック接触を確保する上で好ましい。(図8(B))

【0110】

シリサイド形成が終了したら、層間絶縁膜として窒化珪素膜729を成膜し、コンタクトホールを形成してNチャネル型FETのソース電極730、Pチャネル型FETのソース電極731およびN/Pチャネル型FET兼用のドレイン電極732を形成する。こうして図8(C)に示す様なCMOS構造のIG−FETが完成する。

【0111】

図8(C)に示す構造のCMOS回路は本発明のより短チャネル効果を問題としないで微細化することができるので、極めて集積度の高い集積化回路を構成することが可能である。

【0112】

また、本実施例ではシングルゲイト型のIG−FETを例としているが、SOI構造であるので活性層の上面および下面にチャネルを形成するダブルゲイト型FETを作製する場合にも本発明を適用できる。勿論、パワーMOSFET、MESFET、MISFET等に適用することもできる。

【0113】

また、本実施例ではIG−FETのチャネル形成領域に線状パターン状に不純物領域を形成することに特徴があるが、線状パターンの形成にはある範囲の条件を満たす必要がある。そのことについて、図9を用いて以下に記載する。

【0114】

図9において、901はチャネル形成領域の一部を示している。チャネル幅はWである。ここで、チャネル幅Wの内、線状パターン902が占有している幅をWpiと定義する。Wpiの値としては例えば1 〜 10 nmもあれば十分である。また、任意の線状パターン902の幅をWpi,1、Wpi,2、Wpi,3・・・Wpi,nとすると、Wpiは次式で表される。

【0115】

【数1】

【0116】

但し、本発明の構成を達成するためにはチャネル形成領域の端部以外の領域に、不純物領域が少なくとも一つ形成されている必要があるのでnは1以上の整数である。

【0117】

また、チャネル幅Wの内、ポテンシャルスリット領域(キャリアの移動するパス)903が占有している幅をWpaと定義する。Wpaの値としては量子効果の現れないレベル、即ち3 〜 300 nm(好ましくは3 〜 100 nm)とする。本発明ではWpaをチャネル長(0.01〜0.35μm)の1/3 〜1/1 程度とすることでVth,nおよびVth,pを 0〜±0.3 Vの範囲に調節することができる。また、任意のポテンシャルスリット領域903をWpa,1、Wpa,2、Wpa,3・・・Wpa,mとすると、Wpaは次式で表される。

【0118】

【数2】

【0119】

但し、前述の様にチャネル形成領域の端部以外の領域に不純物領域が少なくとも一つ形成されているので、チャネル形成領域は少なくとも2分されてmは2以上の整数となる。

【0120】

即ち、全チャネル幅WはW=Wpi+Wpa、かつ、n+mは3以上という関係が成り立っている。そして、WとWpi、WとWpaおよびWpiとWpaとの関係は、同時に以下の条件を満たすことが望ましい。

Wpi/W=0.1 〜0.9

Wpa/W=0.1 〜0.9

Wpi/Wpa=1/9 〜9

【0121】

これらの数式の意味するところは、Wpa/WまたはWpi/Wが0または1であってはならないという事である。例えば、Wpa/W=0(Wpi/W=1と同義)の場合、図9(B)に示す様にチャネル形成領域を完全に不純物領域で塞いでしまうので電流の流れるパスが存在しない状態となる。

【0122】

逆にWpa/W=1(Wpi/W=0と同義)の場合、図9(C)に示す様にチャネル形成領域に不純物領域が全く存在しないのでドレイン側空乏層の広がりを抑えることができない。

【0123】

以上の理由により、Wpa/WおよびWpi/Wの関係式は0.1 〜0.9 (好ましくは0.2 〜0.8 )の範囲に収まり、また、同時にWpi/Wpa=1/9 〜9 を満たすことが望ましい。

【0124】

また、本発明において線状パターン形状を有する不純物領域を図1(A)に示す様に配置することはFETの性能を示す代表的なパラメータである移動度の向上に対して非常に大きな意味がある。その理由について以下に説明する。

【0125】

移動度は半導体(本実施例ではシリコン基板)中のキャリアの散乱によって決まるが、シリコン基板における散乱は格子散乱と不純物散乱とに大別される。格子散乱はシリコン基板中の不純物濃度が低く、比較的高温で支配的であり、不純物散乱は不純物濃度が高く、比較的低温で支配的である。これらが影響し合って形成される全体的な移動度μは次式で表される。

【0126】

【数5】

【0127】

この数5で示される式は、全体的な移動度μが、格子散乱の影響を受けた場合の移動度μl ( lはlattice を意味する) の逆数および不純物散乱の影響を受けた場合の移動度μi ( iはimpurityを意味する) の逆数の和に反比例することを意味している。

【0128】

ここで、格子散乱ではドリフト電界がそれほど強くなければ音響フォノンが重要な役割を果たし、その時の移動度μl は、次式の様に温度の-3/2乗に比例する。従って、キャリアの有効質量(m*)と温度(T)で決まってしまう。

【0129】

【数6】

【0130】

また、不純物散乱による移動度μi は、次式の様に温度の3/2 乗に比例し、イオン化した不純物の濃度Ni に逆比例する。即ち、イオン化した不純物の濃度Ni を調節することで変化させることができる。

【0131】

【数7】

【0132】

これらの式によると、従来の様にチャネル形成領域全体に不純物を添加するチャネルドープでは不純物散乱の影響を受けて移動度を稼ぐことができない。しかしながら、本発明では局部的に不純物領域を形成しているので、ポテンシャルスリット領域(Wpaの幅を持つ領域) には不純物が添加されない。

【0133】

即ち、理論的には数7においてイオン化した不純物の濃度Ni を限りなく0に近づけることを意味するため、移動度μi は限りなく無限大に近づいていくことになる。即ち、数5において1/μi の項を無視することができる程度にまで不純物を減少させることを意味するので全体の移動度μは限りなく移動度μl に近づいていく。

【0134】

また、キャリアの有効質量(m*)を小さくすることで移動度μl をさらに大きくすることも理論的には可能である。これは極低温の領域において、キャリア(特に電子の場合)の有効質量が結晶軸の軸方位に依存して変化する現象を利用することで成しうる。

【0135】

文献によれば、ソース/ドレイン間を結ぶチャネル方向(キャリアの移動する方向)が単結晶シリコンの<100>軸方向と一致する様に構成した時、最小の有効質量を得ることができる。

【0136】

例えば、図10に示す様に、(100)面を有する単結晶シリコン基板1001上にソース領域1002、チャネル形成領域1003、ドレイン領域1004が形成されているとする。この時、チャネル方向1005を[100]とした場合の様な時がこれに相当する。但し、この例は4°Kという極低温領域における結果である。

【0137】

また、結晶格子間をうまくキャリアがすり抜けて行ける様に、チャネル方向および不純物領域707の軸方向(配列方向)と、結晶格子の軸方向とを概略平行(軸方向のずれを±10°以内に収める)にさせることが望ましい。単結晶ならばシリコン原子は規則正しく配列しているので、結晶格子の配列方向と平行に移動するキャリアは格子散乱の影響を殆ど受けないで済む。

【0138】

例えば、単結晶シリコン基板において上記の様な方向における回転軸を0°とすると、他にも90°、180°、270°の回転軸の場合において同様の効果を得ることができる。

【0139】

以上の様に、チャネル形成領域を移動するキャリアはチャネル形成領域内に存在する不純物領域以外の領域を通る。この様子を図11の模式図を用いて簡単に説明する。

【0140】

図11(A)において、1101で示されるのはチャネル形成領域である。即ち、図11(A)はチャネル形成領域を右斜め上方から見た図である。本実施例を実施したチャネル形成領域は、立体的には図11(A)の様に不純物領域1102が形成されている。

【0141】

図11(A)に記載された矢印1103はキャリア(電子または正孔)の進行方向を示すものである。図11(A)に示す様にチャネル形成領域1101内には複数の不純物領域1102が配置されており、キャリアはそれら不純物領域1102以外の領域を通過する。

【0142】

キャリアの進行方向をチャネル形成領域1101の上面から見ると図11(B)の様に見える。図11(B)は図11(A)において、ACEFで表される面を見た図である。図11(B)に示される様に、キャリアは不純物領域1102を避け、不純物散乱のない領域を移動する。

【0143】

即ち、大部分のキャリアは矢印で示す様に、不純物領域1102の間を通ってソース/ドレイン間を移動する。勿論、不純物領域がドットパターン形状に設けられている様な場合には、不純物領域を避ける様にしてジグザグに移動する場合も含まれる。

【0144】

また、図11(C)に示すのは、チャネル形成領域1101を側面から見た図である。なお、図11(C)は図11(A)において、ABCDで表される面を見た図である。また、1103で示されるのは矢印であり、紙面に向かって手前方向に矢先が向いていることを示している。この図もキャリアが不純物領域1102の間を移動することを示している。

【0145】

また、線状パターン形状を有する不純物領域に挟まれた領域(ポテンシャルスリット領域)におけるエネルギー状態(電位状態)を模式的に表した分布図は図12(A)の様になっていると考えられる。

【0146】

図12(A)において、1201、1202で示される領域は不純物領域のエネルギー状態を示しており、エネルギー的に高い障壁となっている。そして、不純物領域から離れるに従って徐々にエネルギー的に低い領域1203となる。即ち、チャネル領域を移動するキャリア(ここでは電子を例にとる)は1203で示されるエネルギー状態の低い領域を優先的に移動し、1201、1202で示されるエネルギー障壁(不純物領域)は壁の様な役割を果たす。

【0147】

ここで、チャネル領域を移動するキャリア(電子)のイメージを模式的に図12(B)で表す。イメージ的には、チャネル領域を移動するキャリア1200は図12(B)に表す様にまるで雨樋の中を転がる球体の様にその方向性が規定され、ソース領域からドレイン領域に向かってほぼ最短距離を移動する。

【0148】

本出願人は図12(A)の様なエネルギー分布を電気的なスリットとして捉えてポテンシャルスリット領域と呼んでいる。また、図12(B)の様なモデルからレーンを転がる球体をイメージしてレーン領域とも呼ぶことがある。

【0149】

また、図12(B)に示す様に、チャネル形成領域には図12(A)に示した様なポテンシャルスリット領域が複数並列に配置されて構成されているが、1201、1202で示される領域を越えることがないため、隣接するポテンシャルスリット領域との間においてキャリアの移動は行われない。

【0150】

以上の理由によりキャリアが他のキャリアと衝突する確率は大幅に減少するため、移動度が大幅に向上する。即ち、本発明の構成は不純物散乱を低減するのみならず、キャリア同士の自己衝突による散乱をも低減することで大幅な移動度の向上を実現することができる。

【0151】

この様に従来においては常に悪影響を及ぼすとされてきたエネルギー障壁(グレインバンダリーなど)を逆に意図的に形成して利用するという本発明の発想は非常に新しいものである。

【0152】

〔実施例2〕

本発明において、チャネル形成領域に不純物領域を形成する手段として、不純物の偏析作用を利用した方法をとることもできる。本実施例では、その様な例として熱酸化膜近傍におけるボロン(B)およびリン(P)の偏析を利用した方法について図13を用いて説明する。

【0153】

実施例1に示した構造の半導体装置を作製する時、酸素を添加することによって不純物領域を形成した後に800 〜1200℃程度の加熱処理を行うと、添加された酸素とシリコン(Si)とが反応して熱酸化物が形成されることは述べた。

【0154】

本実施例はその際に不純物領域の周辺(ポテンシャルスリット領域)に含有されていた不純物元素(ボロンまたはリン)が不純物領域に偏析する現象を利用した技術である。ここで、熱酸化工程により熱酸化膜/シリコン界面近傍のボロンまたはリンの濃度がどの様な分布を示すかを図13を用いて説明する。

【0155】

図13に示す様に、Si中に存在する添加イオン(B、P)は酸化膜が形成されると再分布する。これは、シリコン(Si)中および熱酸化膜( SiOx )中において添加イオンの溶解度と拡散速度が異なるために起こる現象である。不純物のSi中における溶解度を [C] Siとし、 SiOx 中における溶解度を [C] SiOxとする時、平衡偏析係数mは次式で定義される。

m= [C] Si/ [C] SiOx

【0156】

この時、Si/SiOx 界面近傍の不純物の偏析はmの値に支配される。通常、Si中における不純物の拡散係数が十分大きいとして、m<1の場合、Si中の不純物は SiOx 中に取り込まれる(図13(A))。また、m>1の場合、SiO x が不純物を排斥し、その結果としてSi/SiOx 界面近傍の不純物濃度が増大する(図13(B))。

【0157】

文献値によると、ボロンのmの値は0.3 程度であり、リンのmの値は10程度である。従って、本実施例における熱酸化工程後のボロンの濃度分布は図13(A)の様になり、熱酸化膜中にボロンが取り込まれ、不純物領域の側面(Si/SiOx 界面近傍)におけるボロン濃度は極めて微量な状態となる。また、逆に形成された熱酸化物中には多量のボロンが含有される。

【0158】

この様な熱酸化膜中へのボロンの取込み現象は既に知られていたが、本発明の様にキャリアの移動する領域における不純物濃度を低減するためにこの現象を利用する発想は全く新しいものである。

【0159】

なお、図13(B)に示す様に、不純物元素としてリンを用いた場合には熱酸化膜とシリコンとの界面に偏析(パイルアップ)する。この現象もまた、リン濃度を低減する上で有効に利用することができる。

【0160】

以上の様に、本実施例の様な酸化物へのリンまたはボロンの偏析現象を利用することで大幅な移動度の向上を図ることが可能である。なぜならば、本実施例を実施すると不純物領域(代表的には SiOX で示される酸化物)周辺の不純物(リンまたはボロン)が不純物領域に収集されてしまうので、ポテンシャルスリット領域(キャリアが移動する領域)における不純物散乱の影響を極めて少なくすることができるからである。

【0161】

また、本実施例の技術にハロゲン元素による金属元素のゲッタリング効果を組み合わせることで、ポテンシャルスリット領域におけるキャリアの不純物散乱をさらに低減することも可能である。

【0162】

このことは、先にも述べた様に数5においてμi が大きくなることに相当するので、全体の移動度μは理想的にμ=μl に近づいていく。即ち、実質的に格子散乱のみで決まる極めて大きな移動度を実現しうることを示す。

【0163】

〔実施例3〕

本実施例では、チャネル形成領域に形成する不純物領域の形状をドットパターン状とする場合の例を示す。説明は図14を用いて行う。なお、説明の便宜上、図1と同じ符号を併用する。

【0164】

図14に示す半導体装置の構造は、図1において線状パターン形状を有する不純物領域をドットパターン形状に置き換えたものである。まず、図1と異なるのは図14(A)に示す様に不純物領域1401が配置される点である。

【0165】

また、図14(A)をA−A’で切断した断面は図14(B)に示す様になり、B−B’で切断した断面は図14(C)に示す様になる。

【0166】

なお、本実施例ではドットパターン状の不純物領域の例として円形の不純物領域を記載しているが、楕円形、正方形、長方形などであっても構わない。

【0167】

ドットパターン状に不純物領域を形成した場合、実施例1に示したレーン領域の様な役割はなくなるが、キャリアの移動しうる実効チャネル面積は増加するので半導体装置に流せる電流量を増やすことができる。

【0168】

〔実施例4〕

実施例1および実施例3では、不純物領域の形状として線状パターン形状の場合とドットパターン形状の場合とを最も単純な形状で説明した。本実施例では、不純物領域の形状の様々なバリエーションについて説明する。

【0169】

図15(A)に示す形状は線状パターン形状の他のバリエーションである。図15(A)に示す構造は、本発明においてドレイン領域側からチャネル形成領域側へと広がる空乏層をピニング(抑止)する効果をより確実にし、短チャネル効果に起因するパンチスルー現象を防止することを第一とした構造である。

【0170】

図15(A)において、不純物領域1501の特徴は、上面から見た場合に線状パターン形状の不純物領域の側面に対して凹凸部1502を付与した形となっており、いわゆるフィッシュボーン形状となっていることである。即ち、側面の凹凸部1502が空乏層の広がりを効果的に抑止するのである。

【0171】

また、図15(A)の構成をさらに発展させて、よりピニング効果を確実なものとした例が図15(B)に示す構成である。即ち、交互にかみ合ったフィッシュボーン形状とすることで空乏層に対する対向面積を増やし、空乏層の広がりを効果的に防止することができる。

【0172】

この際、図15(B)に示す様に、ある凹凸部(フィッシュボーンの骨に相当する部分)が、隣の不純物領域の凹凸部と交互に重なり合う様に形成することが望ましい(1503で示される領域)。

【0173】

ただし、この構造とした場合、キャリアが1504で示される破線の沿って移動するため移動距離が長くなることを避けられない。そして、移動距離が長くなるということは、その分キャリアの散乱確率が増加して移動度を低下させる要因となりかねない。

【0174】

しかし、本発明が効果を発揮する極めて微細な半導体装置においては、チャネル形成領域が真性または実質的に真性である以上、多少移動距離が長くなっても不純物散乱の影響は大きく変化しないと考えられる。それよりも微細化にともなう短チャネル効果(特にパンチスルー現象)の影響を抑制することの方が重要であると言える。

【0175】

また、ある一本の不純物領域に着目した場合、隣接する凹凸部同士の間の距離(図中、Lpaで表される距離)も制御が必要である。なぜならば、Lpaの長さがキャリアの移動度に影響してくるからである。

【0176】

即ち、ピニング効果を高めるためには距離Lpaを短くし、移動度向上に重きを置くなら距離Lpaを長くすることが好ましい。本発明では距離Lpaを7 〜 300 nm(好ましくは10 〜 100 nm)の範囲で制御する。

【0177】

また、本発明は線状パターンのみならず、ドットパターン状の不純物領域を形成する場合においても様々なバリエーションを採りうる。例えば、図15(C)に示す様に不純物領域1506が交互に配置された構成とすることができる。

【0178】

この場合、ドットパターン状の不純物領域1506間の隙間を隣接する列で補う構成となるので、空乏層の広がりを抑止する効果が強くなる。また、この場合もキャリアの移動経路は破線1507で示す様になるが、前述の様に素子が微細になればさほど問題とはならない。

【0179】

また、図15(D)に示す様に、ドットパターン形状の不純物領域1508をチャネル方向と垂直な楕円形または長方形とすることもできる。図15(D)に示す構成は空乏層の抑止を最重点課題とした時に有効な構成であると言える。

【0180】

以上の様に、短チャネル効果に起因するパンチスルー現象を効果的に防止するためには、不純物領域の形状を工夫すれば良い。不純物領域は人為的に形成されるので形状も作製者の自由に設計できる。

【0181】

特に、本実施例で示した様な図15(A)〜図15(D)に示した形状は、チャネル長が0.1 μm以下といった様な極めて微細な半導体装置を形成する場合に効果的である。なぜならば、その様な微細素子となるとパンチスルー現象による耐圧の低下が致命的な問題となるため、移動度の向上よりも耐圧の向上に重きを置くべきだからである。

【0182】

〔実施例5〕

本実施例では、本発明の不純物領域を形成する際に実施例4とは異なる工夫を施した例を示す。本実施例の説明は図16を用いて行なう。

【0183】

図16(A)に示すのは、不純物領域1601の幅(Wpi)をソース領域1602近傍とドレイン領域1603近傍とで変化させた例である。具体的には、ドレイン領域1603近傍に近づくに従い、徐々にWpiが増加していく様な構成とする。

【0184】

図16(A)の様な構成とすると、短チャネル効果に伴うパンチスルー現象の原因となるドレイン領域側の空乏層の広がりを効果的に抑制することができる。また、ソース領域側においてはポテンシャルスリット領域1604の幅(Wpa)が十分に広いのでキャリアの移動がスムーズに行なわれる。

【0185】

また、この構成は図16(A)の様な構成以外に限らず、例えば図16(B)の様にフィッシュボーン形状を有する不純物領域1605の凹凸部1606の長さを、ドレイン領域1607に近づくにつれて長くする様な構成としても達成することができる。

【0186】

また、図16(C)に示す様に、ドレイン領域1608近傍において不純物領域1609を構成する不純物元素の濃度を高くする構成とすることも可能である。この場合、図16(C)に示す様に、上面から見た場合にはソース領域1610からドレイン領域1608に渡って不純物領域1609が形成されている。

【0187】

そして、不純物領域1609を構成する不純物元素の濃度は、ソース領域1610近傍における濃度よりもドレイン領域1608近傍における濃度の方が高い構成とすることができる。(図16(D))

【0188】

なお、図16(D)は不純物領域1609内の不純物元素濃度の変化を表したグラフであり、横軸は距離、縦軸は濃度を表している。図16(D)に示した様に、ソース領域1611近傍の濃度プロファイルとドレイン領域1612近傍の濃度プロファイルを異なる様にするには、不純物領域1609を形成する際に添加する不純物元素の濃度を調節すれば良い。

【0189】

即ち、不純物元素の濃度プロファイルは図16(D)に示す様な形状にこだわる必要はなく、作製者の必要に応じて適宜不純物添加工程を調節して濃度プロファイルを決定すれば良い。

【0190】

以上の様に、本実施例に示した様な構成はソース領域およびドレイン領域の位置が特定されている場合において有効であり、例えば液晶表示装置の画素を駆動する半導体装置の様にソース/ドレインが充放電に応じて逆転する様な場合には必ずしも有効とは言えない。液晶表示装置に用いる場合には、周辺駆動回路を構成するインバータ回路などの様にソース/ドレインが特定される用途に用いるべきであると言える。

【0191】

また、本実施例では不純物領域の形状としてチャネル方向に概略平行な線状パターン形状を有する構成とする例を示したが、本実施例の構成をドットパターン形状に不純物領域に適用することは容易である。従って、本実施例は一例を示すのみであって、他の様々な考えうる例は作製者の必要に応じて適宜なされるものであると考える。

【0192】

〔実施例6〕

実施例1ではチャネル形成領域に対して人為的かつ局部的に不純物元素(炭素、窒素、酸素)を添加して不純物領域を形成する例を示した。本実施例では、不純物領域の形成方法として他の方法を用いた場合について図17を用いて説明する。

【0193】

図17(A)に示すのはSOI基板の単結晶シリコン層のみを拡大した図である。1701は絶縁層であり、1702が単結晶シリコン層である。SOI基板としては、SOS基板、SIMOX基板、FIPOS基板等を用いることができる。

【0194】

そして、電子ビーム法、FIB法、エキシマレーザー法などの微細リソグラフィ技術を利用して不純物領域を形成するためのレジストパターン1703をチャネル形成領域上に配置する。

【0195】

図17(A)に示す状態が得られたら、Ar(アルゴン)をイオン注入法により添加する。なお、本実施例ではArを用いるが、He(ヘリウム)、Ne(ネオン)等の希ガスを注入するのであっても良い。(図17(B))

【0196】

このイオン注入の目的は、単結晶シリコン層に対してダメージを与えることにあるため、電気的に不活性な元素を用いる。なぜならば、本実施例で開示する方法は、単結晶シリコンを熱酸化した際にダメージを受けた領域が優先的に酸化される性質を利用するものだからである。

【0197】

従って、図17(B)においてArが添加された領域1704は、他の領域に比べてダメージを受けた、結晶配列の乱れた領域となる。

【0198】

次に、レジストパターン1703を除去した後、図17(C)に示す様に、800 〜1200℃の温度範囲で加熱処理を行う。本実施例では、1000℃60min の処理の内、最初の30分を酸化性雰囲気で処理し、残りの時間を窒素(N2 )90%、酸素(O2 )9%、塩化水素(HCl)1%のハロゲン雰囲気に切り換えて処理を続ける構成とする。

【0199】

即ち、最初の30分間は熱酸化のための加熱処理であり、後の30分間はハロゲン元素による金属元素のゲッタリング効果を狙った加熱処理である。後者の加熱処理を窒素含有量の多い雰囲気で行うのは、単結晶シリコン層が過剰に酸化されるのを防止するためである。

【0200】

こうして図17(C)に示す様に、単結晶シリコン層には熱酸化膜1705が形成される。そして同時に領域1704が優先的に酸化反応が進行して、単結晶シリコン層内部まで侵入した不純物領域(この場合、酸化シリコンで成る)1706が形成される。なお、図17(C)では不純物領域1706が下方の絶縁層1701にまで達していないが、Arの注入条件によって絶縁層に達する様にする場合もあり得る。

【0201】

以上の様に、本実施例で開示する技術は、上記の様な過程で形成された不純物領域1706を空乏層をピニングする領域として活用するものである。また、本実施例は、例えば電子ビームや集束イオンビームを直接単結晶シリコン層に照射してダメージを与えても実施することができる。

【0202】

また、本実施例はハロゲン元素による金属元素のゲッタリング効果と、実施例2に示したリンやボロンの熱酸化膜への偏析現象を共に利用する構成になるので、真性または実質的に真性な、キャリアが移動する領域(特に、不純物領域1706の周辺)1707には、不純物散乱の原因や再結合中心となる不純物元素が存在しない。従って、極めて高い移動度を期待しうる半導体装置を作製することができる。

【0203】

〔実施例7〕

本発明の特徴はチャネル形成領域に対して人為的かつ局部的に不純物領域を設ける点にあるが、チャネル形成領域に局部的に添加された不純物元素(炭素、窒素、酸素から選ばれた一種または複数種類の元素)は、水素アニール処理を施した低酸素シリコン基板を用いる場合に有効な効果を示す。

【0204】

従来例で触れた様に、通常のLSI回路を構成する半導体装置(サイリスタを除く)はCZ法で形成されたシリコン基板を用いており、応力緩和のために所定量の酸素がシリコン基板中に含まれている。しかし、最近ではの酸化膜耐圧の向上、微小欠陥の低減の要求が強まり、水素雰囲気でのアニールによって表面層5μm位までの酸素濃度を 1×1017atoms/cm3 以下にまで下げた基板が多く用いられている。

【0205】

その反面、この様な低酸素処理を施したシリコン基板は基板表面層が応力に対して非常に脆くなってしまい、半導体装置の製造プロセスの過程でクラックや反りが発生する原因ともなってしまう可能性がある。

【0206】

しかしながら、本発明に低酸素処理を施したシリコン基板を用いるとチャネル形成領域に形成された不純物領域に応力が集中する様になるので、不純物領域が結晶半導体に発生する応力を緩和する緩衝領域としての機能を有する。

【0207】

この応力を緩和する緩衝領域として機能するという効果は、本発明における不純物領域の特筆すべき効果の一つである。なお、この効果は不純物元素として酸素を用いた場合において特に顕著である。

【0208】

従って、低酸素処理を施したシリコン基板を用いて半導体装置を作製する際に製造プロセス過程において発生する応力による影響を緩和することができるので、製造歩留りが大幅に向上する。

【0209】

また、この様なシリコン基板は酸化膜耐圧の向上、微小欠陥の低減の効果以外に、キャリアの不純物散乱の影響が低減するといった効果も期待できる。即ち、酸素を低減することはポテンシャルスリット領域をより真性または実質的に真性な領域に近づけることを意味しているので、キャリアの移動度を極めて高いものとしうる。

【0210】

〔実施例8〕

本実施例では、本発明を利用した半導体装置(半導体素子)で構成される集積化回路(本明細書では半導体装置の範疇に含まれる)について、いくつかの例を挙げて説明する。説明には図18および図19を用いる。

【0211】

図18(A)に示すのは、Nチャネル型FETとPチャネル型FETとを二階建てに積層して構成したスタックト型CMOS回路に本発明を適用した場合の例である。一般的には動作性能の問題からPチャネル型FETが下層側に形成されることが多い。本実施例も下層側をPチャネル型FETとしている。

【0212】

図18(A)において、下層は通常のIC技術で形成されたPチャネル型FETであり、1801はN型シリコン基板、1802はフィールド酸化膜、1803、1804はそれぞれソース領域およびドレイン領域である。本実施例では、低濃度不純物領域(ドレイン領域側はLDD領域と呼ばれる)1805、1806を設ける構成とする。

【0213】

また、1807は導電性を有するポリシリコンでなるゲイト電極であり、その直下には本発明の特徴である不純物領域1808が配置されている。なお、図18(A)では不純物領域1808の一端は低濃度不純物領域1806の内部にあり、他端はLDD領域1805を超えてドレイン領域1804の内部にある。

【0214】

上層にはSOI技術を用いてNチャネル型FETが形成されている。Nチャネル型FETの活性層となる単結晶シリコン層は公知のウェハーの貼り合わせ技術を利用することで得られる。従って、1809で示される層間絶縁膜は下層のFETを覆う層間絶縁膜と、接合するウェハーの熱酸膜との積層膜で構成され、接合面(点線で示される)を含んでいる。

【0215】

そして、公知のTFT技術を用いてソース領域1810、チャネル形成領域1811、ドレイン領域1812を形成する。ここでもチャネル形成領域1811を挟み込む様に低濃度不純物領域1813、1814が配置される。また、チャネル形成領域1811対しては本発明である不純物領域1815を配置する。

【0216】

さらに、ゲイト電極1816を覆って層間絶縁膜1817が成膜され、配線1818、1819、1820が形成される。なお、配線1818はPチャネル型FETのドレイン領域1804とNチャネル型FETのドレイン領域1812とに共通の配線となる。

【0217】

以上説明した構造でなる図18(A)に示すスタックト型CMOS回路は素子の占有面積を低減することができるため、VLSIやULSI回路を構成する際に集積度を向上させることができる。

【0218】

また、本発明を適用することで耐圧特性を損ねることなく高速動作性を追及することができるので、周波数特性の優れたCMOS回路を構成することが可能となる。

【0219】

次に、図18(B)に示すのは、CMOS回路とバイポーラトランジスタとを複合したBi−CMOS回路に本発明を適用した例である。ここでは、下層がバイポーラトランジスタであり、上層がSOI構造の半導体装置で構成されるCMOS回路である。

【0220】

図18(B)において、1821はP型シリコン基板であり、1822は埋め込みN+ 領域、1823はエピタキシャル成長により形成されたpウェルであり、埋め込みN+ 領域1822上のpウェルはN型にドーピングされてコレクタとして機能するnウェル1824となっている。また、1825は埋め込みN+ 領域1822からの取り出し電極となるDeepN+ 領域である。また、1826は通常の選択酸化法で形成されたフィールド酸化膜である。

【0221】

バイポーラトランジスタを構成するnウェル1824には活性ベースとなるp- 領域1827がまず形成され、次いで外部ベースとなるp+ 領域1828、エミッタ領域となるn+ 領域1829が配置される。

【0222】

以上の構成でなるバイポーラトランジスタの上方にはウェハー貼り合わせ技術を用いて得られた単結晶シリコン層を活性層とする、SOI構造のCMOS回路が構成されている。1830で示される層間絶縁膜が接合面(点線で示される)を含んでいる。ここでは、CMOS回路の詳細な説明は実施例1で十分に述べたのでここでは省略する。

【0223】

図18(B)では、Nチャネル型FETの不純物領域1831、Pチャネル型FETの不純物領域1832共に、ソース領域1833、1834には入り込まず、ドレイン領域1835、1836のみに入り込む様な配置とする。

【0224】

そして、上層のCMOS回路と下層のバイポーラトランジスタとを配線1837、1838で接続してBi−CMOS構造を実現することができる。

【0225】

この様にして構成されるBi−CMOS回路はバイポーラトランジスタの高速動作性とCMOS回路の低消費電力性を有効に併用するための回路構成である。また、本実施例の様に、CMOS回路とバイポーラトランジスタを積層化する三次元構造とすることで、従来の問題であった占有面積の大きさを大幅に小さくすることが可能である。

【0226】

次に、図19(A)に示すのは、SOI技術を用いて作製したDRAM(Dynamic Rondom Access Memory)に本発明を適用した例である。DRAMとは記憶する情報を電荷としてコンデンサに蓄える形式のメモリである。コンデンサへの情報としての電荷の出し入れは、コンデンサに直列に接続された半導体装置(電界効果トランジスタ)によって制御される。ここでは、スタックトキャパシタ型のDRAMについて説明する。

【0227】

図19(A)において、1901はシリコン基板、1902は、シリコン基板1901とその上に設けられる容量蓄積用電極1903とを分離する絶縁膜である。容量蓄積用電極1903の上方には高誘電率材料でなる絶縁膜1904を介して容量電極1905が設けられている。本実施例では絶縁膜1904としてTa2O5 を用いるが、他にもSi3N4 などを用いることができる。

【0228】

この様な構造によって、容量蓄積用電極1903と容量電極1905との間には大容量のキャパシタが形成される。図19(A)に示す積層構造において、下層は完全に容量を蓄積する領域として活用している点が特徴である。そして、その容量に蓄積する電荷の出し入れはSOI技術を用いて上層部に形成されたIG−FETによって成される。

【0229】

本実施例では上層に配置するデータ信号制御用に半導体装置として、LDD領域を設けたNチャネル型FETを用いている。活性層となる単結晶シリコン層はウェハー貼り合わせ技術を用いて得られるが、レーザー又は電子ビームによるポリシリコン(又はアモルファスシリコン)の再結晶化技術を用いても良い。なお、図中の点線で示されるのは貼り合わせの接合界面である。

【0230】

単結晶シリコン層でなる活性層はソース領域1906、ドレイン領域1907で構成され、チャネル形成領域には本発明の不純物領域1908が配置されている。なお、不純物領域1908はLDD領域1909を突き抜けてドレイン領域1907の内部にまで入り込む様にして設けられている。

【0231】

ビット線1910で送られてきたデータ信号は、ワード線1911の電圧を制御することでドレイン電極1912に伝えられる。そして、その信号は上層のドレイン電極1912と下層の容量電極1905とを接続する埋め込みプラグ1913を介して下層にキャパシタ(容量)に蓄積される。

【0232】

DRAMの特徴は1個のメモリを構成する素子数がIG−FETとキャパシタだけで非常に少ないので、高集積密度の大規模メモリを構成するのに適していることである。また、製造コストも低く抑えられるので、現在最も大量に使用されている回路であると言える。

【0233】

次に、本発明を利用して作製したFETをSRAM(Static Rondom Access Memory )に適用した例について説明する。説明には図19(B)を用いることとする。

【0234】

SRAMはフリップフロップ等の双安定回路を記憶素子に用いたメモリであって、双安定回路のON−OFFあるいはOFF−ONの2安定状態に対応して2進情報値(0または1)を記憶するものである。電源の供給がある限り記憶が保持される点で有利である。

【0235】

記憶回路はNMOS回路やCMOS回路で構成される。図19(B)に示すSRAMの回路はCMOS回路を組み合わせたセルの断面図である。なお、最下層に配置された2つのFETはどちらもPチャネル型FETであり、中層の2つのFETはどちらもNチャネル型FETである。従って、説明は基本的に図面に向かって右側の上下FETで構成されたCMOS回路を中心に説明する。

【0236】

図19(B)において、N型シリコン基板1914にはP型ウェルでなるソース領域1915ドレイン領域1916が形成され、ゲイト絶縁膜1917を介してゲイト電極1918が配置される。図面に向かって左右に配置される素子はフィールド酸化膜1919で分離されている。

【0237】

また、1920で示されるのは本発明の不純物領域である。ここではドレイン領域にのみ入り込む様な配置とし、ソース領域には不純物領域が入り込まない様に構成する。

【0238】

中層のNチャネル型FETの活性層はSOI技術の一つであるレーザー(又は電子)ビーム再結晶化法を用いて形成する。この技術は、平坦化された層間絶縁膜1921上にポリシリコン又はアモルファスシリコンを形成して、それをレーザービームや電子ビーム等で溶融させて再結晶化させるものである。

【0239】

勿論、ウェハー貼り合わせ技術等のSOI技術を用いても構わないのであるが、本実施例では再結晶化法を用いることで、中層のNチャネル型FETのドレイン領域1922を直接Pチャネル型FETのドレイン領域1916と接続する構成としている。

【0240】

上記手段によって得られた活性層(単結晶シリコン層)には公知のTFT技術を用いてソース領域1923ドレイン領域1922が設けられ、ゲイト絶縁膜1924を介してゲイト電極1925が配置されている。そのゲイト電極1925の直下(チャネル形成領域)には本発明の不純物領域1926がドレイン領域1922のみに入り込む様な構成で設けられている。

【0241】

Nチャネル型FETのゲイト電極1925は導電性を付与してポリシコンで形成されるが、ゲイト電極1925の形成と同時に同じ材料で接続配線1927を形成する。この接続配線1927は右側のCMOS回路の出力信号を、左側のCMOS回路のゲイト電極1928、1929へと伝えるための配線である。なお、図19(B)において、点線で示したのは図面上では記載されないが接続配線1927と各ゲイト電極1928、1929とが電気的に接続されていることを示している。

【0242】

そして、最上層にはトランスファゲートとして機能するNチャネル型FETが配置される。このFETの活性層はウェハー貼り合わせ技術を用いて得られた単結晶シリコン層である。単結晶シリコン層は島状に加工された後、ソース領域1930、ドレイン領域1931、本発明の不純物領域1932を形成されて活性層となる。

【0243】

このトランスファゲートとなるNチャネル型FETのドレイン領域1931は接続電極1933を介して中層に設けられた接続配線1927と電気的に接続されている。そして、ワード線1934に電圧を印加することでビット線1935からのデータ信号をCMOS回路へと伝達する。

【0244】

以上説明して様な構成でなるCMOS型SRAMは動作マージンが広い、データ保持電流が極めて少ないといった長所があり、低電圧のバッテリーバックアップ用に用いられることが多い。また、SRAMは、高速動作が可能で、信頼性が高くシステムへの組む込みが容易なことなどの特徴もある。

【0245】

以上の様に、本実施例で説明したBi−CMOS回路やSRAM回路等の半導体装置は、本発明を適用することで短チャネル効果を防止しつつ微細化することができるので、信頼性(高耐圧特性等)と高速動作特性を同時に追及することが可能となる。即ち、この先必要となるシステム・オン・チップ構想を念頭に置いた超高集積化回路を実現するために、本発明は絶大な効果を発揮する技術であると言える。

【0246】

〔実施例9〕

本実施例では、本発明を利用した半導体装置を製品(電子機器)に組み込んだ場合の一例を示す。ここでは、ノート型パソコンに組み込まれたIC回路を例にとって説明する。説明は図20を用いて行う。

【0247】

図20において、3001は本体、3002はフタ部、3003はキーボード、3004は画像表示部であり、本体3001内には様々な集積回路3005が組み込まれている。

【0248】

集積回路3005を取り出してみると、外部はパッケージ3011で覆われて内部の半導体チップは樹脂等で保護されている。また、内部の半導体チップはリード3012によって外部と接続される。通常、目にする集積回路(ICチップ)3005は、外目には黒色のパッケージ3011とリード3012しか見えないので完全にブラックボックスとなっている。

【0249】

そのパッケージ3011で保護された半導体チップを取り出して見ると、例えば次の様な構成となっている。まず、基板3013上には演算部(プロセッサー)3014とメモリ部3015が配置されている。なお、3016は半導体素子とリード3012とを接続するボンディング部である。

【0250】

演算部3014、メモリ部3015はCMOS回路、Bi−CMOS回路、DRAM回路、SRAM回路など、他にも様々な回路を用いて構成されている。本実施例で示した図20の様な構成は、同一基板上に演算部3014とメモリ部3015が配置されていることに特徴がある。これは、いわゆるシステム・オン・チップ(システムIC)と呼ばれる構想である。

【0251】

この様に演算部3014とメモリ部3015とが隣接した構成とすると、演算部3014とメモリ部3015との間のデータのやりとりが非常に高速で行われる様になるため、動作速度の速い回路を形成することが可能となる。

【0252】

また、ワンチップ上に必要な回路を全て集積化することも可能であるので、製造コストを大幅に低減することも期待できる。さらには、配置面積を減らすことで製品の小型化を図ることもできる。実施例8で説明した様に、SOI技術は三次元的な集積化回路を構成することができるので、今後、集積度は益々高密度となるに違いない。

【0253】

加えて、本発明を利用すれば短チャネル効果を問題とせずにIG−FET、さらには集積化回路の微細化を行うことができるので、上記の様なワンチップ化を実現することで半導体装置である応用電子機器のさらなる小型化、携帯化が期待できる。

【0254】

〔実施例10〕

本実施例では、本発明を適用したIG−FETおよびそれを組み合わせて構成される集積化回路を組み込んだ電子機器の例を示す。なお、前述の様に本明細書中では便宜上、IG−FET、集積化回路、電子機器等と記載しているが、基本的には全て半導体を利用して作製される装置であるので「半導体装置」の範疇に含まれているものとする。

【0255】

本発明を適用しうる半導体装置(電子機器)としては、一般的にIC回路を必要とする半導体装置全てが含まれる。従って、適用範囲は極めて広く日常の殆どの場面で使用される装置が含まれる。

【0256】

具体的には、例えば液晶表示装置、EL表示装置、CL表示装置といったアクティブタイプの電気光学装置およびTVカメラ、パーソナルコンピュータ、カーナビゲーション、TVプロジェクション、ビデオカメラ、携帯情報端末機器等が挙げられる。携帯情報端末機器としては、携帯電話やモバイル(モービル)コンピュータといった半導体装置が含まれる。以上に挙げた様な半導体装置として代表的な例を図21を用いて簡単に説明する。

【0257】

図21(A)はTVカメラであり、本体2001、カメラ部2002、表示装置2003、操作スイッチ2004で構成される。本発明は装置内部に組み込まれる集積化回路2005に適用することができる。

【0258】

図21(B)はカーナビゲーションであり、本体2101、表示装置2102、操作ボタン2103、アンテナ2104で構成される。本発明は装置内部に組み込まれる集積化回路2105に適用することができる。なお、表示装置2102はモニターとして利用されるが、地図の表示が主な目的なので解像度の許容範囲は比較的広いと言える。

【0259】

図21(C)は携帯情報端末機器(本実施例では携帯電話)であり、本体2301、音声出力部2302、音声入力部2303、表示装置2304、操作ボタン2305、アンテナ2306で構成される。本発明は装置内部に組み込まれる集積化回路2307に適用することができる。

【0260】

図21(C)に示す様な携帯電話は高周波動作を必要とする半導体装置であるので、極めて高速な動作特性を要求される。そこで本発明を適用することで耐圧を損ねることなく高速動作する集積化回路を組み込むことができる。

【0261】

図21(D)はビデオカメラであり、本体2401、表示装置2402、接眼部2403、操作ボタン2404、テープホルダー2405で構成される。本発明は装置内部に組み込まれる集積化回路2406に適用することができる。表示装置2402に映し出された撮影画像は接眼部2403を通してリアルタイムに見ることができるので、使用者は画像を見ながらの撮影が可能となる。

【0262】

以上の様に、本発明の応用範囲は極めて広く、半導体集積化回路を有する様々な半導体装置(電子機器を含む)に対して適用することが可能である。

【0263】

〔実施例11〕

本発明による半導体装置の電気特性は非常に優れたものであり、これを用いて構成した集積化回路は高い周波数特性を実現しうる。本実施例では、本発明を利用した半導体装置の性能に関する例を示す。

【0264】

本発明を利用して形成された半導体素子単体のデバイス特性(IG−FETの電流−電圧特性)は非常に優れたものとなり、Nチャネル型FETのしきい値電圧Vth,nは-0.3〜3.0 V、Pチャネル型FETのしきい値電圧Vth,pは-3.0〜0.3 Vの範囲(代表的には 0〜±0.3 Vの範囲)で必要とする駆動電圧に合わせて調節できる。また、S値は60〜85mV/decade 、ともすれば60〜70mV/decade の極めて優れたサブスレッショルド特性が得られる。

【0265】

また、実施例1で説明した様な理由により高い移動度(1000cm2/Vs以上)を得ることができる。移動度を計算式で求める場合、移動度はチャネル幅Wに反比例するので注意が必要である。本発明を実施する場合、チャネル形成領域においては不純物領域によって少なからずチャネル幅が狭くなっているので、実測チャネル幅Wpaを代入しなければ実際の移動度は得られない。

【0266】

以上の様な優れた電気特性を達しうる本発明の半導体装置で集積化回路を構成すると、極めて良好な周波数特性を得ることができる。例えば、本発明の半導体装置を用いて9段のリングオシレータを構成すると、3.3 Vの駆動電圧で2〜10GHzの周波数特性を実現しうる。

【0267】

また、例えば、高周波電子機器である携帯電話などの様に高い周波数特性を必要とする電子機器に対しても本発明は有効である。携帯電話の入力部等に用いられる集積化回路は、I/O 回路やMUX/DMUX回路等に様に2GHz程度(2.4 GHz)の周波数特性を必要とするのであるが、本発明はその様な高周波集積化回路に対しても十分に対応することができる。

【0268】

また、本発明をSOI構造の半導体装置に適用しているので、従来のバルクシリコン基板に作製した集積化回路よりも、10%以上も速い動作特性を有し、70%以下の消費電力で駆動しうる集積化回路を構成できる。

【0269】

【発明の効果】

本発明を利用することでチャネル長が短くなった場合に生じる短チャネル効果を防止することが可能となる。具体的には、まずドレイン側空乏層がソース領域やチャネル形成領域下に広がるのを、チャネル形成領域に局部的に形成した不純物領域で遮り、チャネル形成領域のエネルギー(電位)状態にドレイン電圧が影響しない構成とする。これによりパンチスルー現象やサブスレッショルド特性の劣化を防止することが可能となる。また、同時に高いドレイン耐圧を実現することができる。

【0270】

また、短チャネル効果の特徴の一つであるしきい値電圧の低下を狭チャネル効果によるしきい値電圧の増加によって抑制することができる。この狭チャネル効果は、チャネル形成領域に局部的に不純物領域を形成するという本発明の構成によって人為的に成しうる効果である。

【0271】

以上の様に、本発明を利用することでチャネル長の極めて短いディープサブミクロン領域における半導体装置においても、短チャネル効果を引き起こすことなく動作させることができる。従って、本発明の半導体装置を利用することで非常に高密度に集積化された集積化回路を構成することができる。

【0272】

また、本発明ではチャネル形成領域にエネルギー的にスリット状のレーン領域を形成することでキャリアの移動方向を規定し、キャリア同士の自己衝突による散乱を低減することが可能である。

【0273】

即ち、キャリアの移動度低下を招く原因となる不純物散乱、格子散乱、キャリア同士の自己衝突による散乱が大幅に低減され、移動度が大きく向上する。即ち、IG−FETに代表される半導体装置のより一層の性能向上が望める。

【図面の簡単な説明】

【図1】 チャネル形成領域の構成を示す図。

【図2】 チャネル形成領域の構成を示す図。

【図3】 従来の半導体装置を説明するための図。

【図4】 チャネル形成領域のエネルギー状態を示す図。

【図5】 従来の半導体装置の特性を説明するための図。

【図6】 チャネル形成領域のエネルギー状態を示す図。

【図7】 絶縁ゲイト型電界効果トランジスの作製工程を示す図。

【図8】 絶縁ゲイト型電界効果トランジスの作製工程を示す図。

【図9】 不純物領域の形状および配置を説明するための図。

【図10】 チャネル形成領域の構成を示す図。

【図11】 チャネル形成領域の構成を示す図。

【図12】 チャネル形成領域のエネルギー状態を示す図。

【図13】 不純物の偏析状態を説明するための図。

【図14】 チャネル形成領域の構成を示す図。

【図15】 チャネル形成領域の構成を示す図。

【図16】 チャネル形成領域の構成を示す図。

【図17】 不純物領域の作製工程を示す図。

【図18】 半導体装置の構成を示す図。

【図19】 半導体装置の構成を示す図。

【図20】 半導体装置の構成を示す図。

【図21】 半導体装置の構成を示す図。

【符号の説明】

101 ソース領域

102 ドレイン領域

103 チャネル形成領域

104 不純物領域

105 シリコン基板

106 埋め込み酸化膜

Claims (15)

- 絶縁性基板または絶縁層上の単結晶半導体に形成されたソース領域、ドレイン領域およびチャネル形成領域と、

前記チャネル形成領域上にゲイト絶縁膜を介して形成されたゲイト電極と、

を有する絶縁ゲイト型半導体装置であって、

前記チャネル形成領域は、キャリアが移動する領域と、炭素、窒素、酸素から選ばれた一種または複数種類の元素を含む不純物領域とを有し、

前記不純物領域は、前記チャネル形成領域表面から前記絶縁性基板または前記絶縁層に達する深さを有するとともに、上面からみたとき、前記ソース領域及び前記ドレイン領域の一方から他方へ向かう線状パターンを有し、

前記キャリアが移動する領域と前記不純物領域は、チャネル幅方向において交互に並んでいることを特徴とする絶縁ゲイト型半導体装置。 - 絶縁性基板または絶縁層上の単結晶半導体に形成されたソース領域、ドレイン領域およびチャネル形成領域と、

前記チャネル形成領域上にゲイト絶縁膜を介して形成されたゲイト電極と、

をそれぞれ有するNチャネル型FET及びPチャネル型FETを有する絶縁ゲイト型半導体装置であって、

前記チャネル形成領域は、キャリアが移動する領域と、炭素、窒素、酸素から選ばれた一種または複数種類の元素を含む不純物領域とを有し、

前記不純物領域は、前記チャネル形成領域表面から前記絶縁性基板または前記絶縁層に達する深さを有するとともに、上面からみたとき、前記ソース領域及び前記ドレイン領域の一方から他方へ向かう線状パターンを有し、

前記キャリアが移動する領域と前記不純物領域は、チャネル幅方向において交互に並んでいることを特徴とする絶縁ゲイト型半導体装置。 - 請求項1または請求項2において、上面からみたとき、前記不純物領域がフィッシュボーン形状であることを特徴とする絶縁ゲイト型半導体装置。

- 請求項1または請求項2において、上面からみたとき、前記不純物領域同士が、交互にかみ合ったフィッシュボーン形状であることを特徴とする絶縁ゲイト型半導体装置。

- 請求項1または請求項2において、上面からみたとき、前記不純物領域の幅が、前記ソース領域から前記ドレイン領域へ向かうにつれ増加していくことを特徴とする絶縁ゲイト型半導体装置。

- 請求項1または請求項2において、上面からみたとき、前記不純物領域同士が交互にかみ合ったフィッシュボーン形状であり、前記フィッシュボーンのチャネル幅方向への凸部の長さが、前記ソース領域から前記ドレイン領域へ向かうにつれ長くなることを特徴とする絶縁ゲイト型半導体装置。

- 請求項1または請求項2において、前記不純物領域中の前記元素の濃度が、前記ソース領域近傍における濃度よりも前記ドレイン領域近傍における濃度の方が高いことを特徴とする絶縁ゲイト型半導体装置。

- 絶縁性基板または絶縁層上の単結晶半導体に形成されたソース領域、ドレイン領域およびチャネル形成領域と、

前記チャネル形成領域上にゲイト絶縁膜を介して形成されたゲイト電極と、

を有する絶縁ゲイト型半導体装置であって、

前記チャネル形成領域は、キャリアが移動する領域と、酸化シリコンでなる不純物領域とを有し、

前記不純物領域は、前記チャネル形成領域表面から前記絶縁性基板または前記絶縁層に向かって深さを有するとともに、上面からみたとき、前記ソース領域及び前記ドレイン領域の一方から他方へ向かう線状パターンを有し、

前記キャリアが移動する領域と前記不純物領域は、チャネル幅方向において交互に並んでいることを特徴とする絶縁ゲイト型半導体装置。 - 絶縁性基板または絶縁層上の単結晶半導体に形成されたソース領域、ドレイン領域およびチャネル形成領域と、

前記チャネル形成領域上にゲイト絶縁膜を介して形成されたゲイト電極と、

をそれぞれ有するNチャネル型FET及びPチャネル型FETを有する絶縁ゲイト型半導体装置であって、

前記チャネル形成領域は、キャリアが移動する領域と、酸化シリコンでなる不純物領域とを有し、

前記不純物領域は、前記チャネル形成領域表面から前記絶縁性基板または前記絶縁層に向かって深さを有するとともに、上面からみたとき、前記ソース領域及び前記ドレイン領域の一方から他方へ向かう線状パターンを有し、

前記キャリアが移動する領域と前記不純物領域は、チャネル幅方向において交互に並んでいることを特徴とする絶縁ゲイト型半導体装置。 - 請求項8または請求項9において、前記不純物領域は、Ar、He、またはNeを前記単結晶半導体に添加した後、加熱処理をして形成されたものであることを特徴とする絶縁ゲイト型半導体装置。

- 請求項1乃至請求項10のいずれか一において、前記不純物領域は前記単結晶半導体に発生する応力を緩和する緩衝領域としての機能を有することを特徴とする絶縁ゲイト型半導体装置。

- 請求項1乃至請求項11のいずれか一において、前記キャリアが移動する領域の幅は3〜300nmの範囲で制御されることを特徴とする絶縁ゲイト型半導体装置。

- 絶縁性基板または絶縁層上の単結晶半導体に形成されたソース領域、ドレイン領域及びチャネル形成領域と、

前記チャネル形成領域上にゲイト絶縁膜を介して形成されたゲイト電極と、

を有する絶縁ゲイト型半導体装置の作製方法であって、

前記チャネル形成領域にAr、He、またはNeを選択的に添加して、当該添加領域を上面からみたとき、前記ソース領域及び前記ドレイン領域の一方から他方へ向かう線状パターンを有するようにし、

加熱処理により前記添加領域を酸化シリコンでなる不純物領域にし、

前記不純物領域は前記チャネル形成領域表面から前記絶縁性基板または前記絶縁層に向かって深さを有することを特徴とする絶縁ゲイト型半導体装置の作製方法。 - 絶縁性基板または絶縁層上の単結晶半導体に形成されたソース領域、ドレイン領域及びチャネル形成領域と、

前記チャネル形成領域上にゲイト絶縁膜を介して形成されたゲイト電極と、

を有する絶縁ゲイト型半導体装置の作製方法であって、

前記チャネル形成領域にAr、He、またはNeを選択的に添加して、当該添加領域を上面からみたとき、前記ソース領域及び前記ドレイン領域の一方から他方へ向かう線状パターンを有するようにし、

加熱処理により、前記添加領域を酸化シリコンでなる不純物領域にし、更に前記不純物領域に金属元素をゲッタリングし、

前記不純物領域は前記チャネル形成領域表面から前記絶縁性基板または前記絶縁層に向かって深さを有することを特徴とする絶縁ゲイト型半導体装置の作製方法。 - 請求項13または請求項14において、前記ソース領域、前記ドレイン領域、前記チャネル形成領域、及び前記ゲイト電極とをそれぞれ有するNチャネル型FET及びPチャネル型FETを有することを特徴とする絶縁ゲイト型半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP26921496A JP4053102B2 (ja) | 1996-09-18 | 1996-09-18 | 半導体装置およびその作製方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP26921496A JP4053102B2 (ja) | 1996-09-18 | 1996-09-18 | 半導体装置およびその作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH1093099A JPH1093099A (ja) | 1998-04-10 |

| JP4053102B2 true JP4053102B2 (ja) | 2008-02-27 |

Family

ID=17469267

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP26921496A Expired - Fee Related JP4053102B2 (ja) | 1996-09-18 | 1996-09-18 | 半導体装置およびその作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4053102B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4275336B2 (ja) | 2001-11-16 | 2009-06-10 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5439793B2 (ja) * | 2008-11-06 | 2014-03-12 | 富士通株式会社 | 二次イオン質量分析法の深さ校正用試料、その製造方法及び二次イオン質量分析方法 |

| KR20230154098A (ko) * | 2009-10-08 | 2023-11-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| WO2012157472A1 (en) * | 2011-05-13 | 2012-11-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

-

1996

- 1996-09-18 JP JP26921496A patent/JP4053102B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH1093099A (ja) | 1998-04-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4103968B2 (ja) | 絶縁ゲイト型半導体装置 | |

| JP4499774B2 (ja) | 絶縁ゲイト型半導体装置 | |

| JP4014676B2 (ja) | 絶縁ゲイト型半導体装置およびその作製方法 | |

| JP4014677B2 (ja) | 絶縁ゲイト型半導体装置 | |

| KR100488311B1 (ko) | 반도체장치 | |

| KR100443437B1 (ko) | 절연게이트형반도체장치및그제작방법 | |

| JP3949193B2 (ja) | 絶縁ゲイト型半導体装置 | |

| JPH10135469A (ja) | 半導体装置およびその作製方法 | |

| JP4053102B2 (ja) | 半導体装置およびその作製方法 | |

| JP5312489B2 (ja) | 半導体装置 | |

| JP4545825B2 (ja) | 半導体装置 | |

| JP4515530B2 (ja) | 半導体装置 | |

| JP4684358B2 (ja) | 半導体装置の作製方法 | |

| JP4896699B2 (ja) | 絶縁ゲイト型半導体装置およびその作製方法 | |

| JP4628399B2 (ja) | 半導体装置 | |

| JP4563422B2 (ja) | 半導体装置 | |

| JP2009004595A (ja) | 半導体装置及び当該半導体装置を具備する電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050623 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070710 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070903 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070925 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071022 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071205 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101214 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101214 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101214 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111214 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111214 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121214 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121214 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131214 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |