JP7640239B2 - インターフェース回路並びにメモリ装置及びその動作方法 - Google Patents

インターフェース回路並びにメモリ装置及びその動作方法 Download PDFInfo

- Publication number

- JP7640239B2 JP7640239B2 JP2020152603A JP2020152603A JP7640239B2 JP 7640239 B2 JP7640239 B2 JP 7640239B2 JP 2020152603 A JP2020152603 A JP 2020152603A JP 2020152603 A JP2020152603 A JP 2020152603A JP 7640239 B2 JP7640239 B2 JP 7640239B2

- Authority

- JP

- Japan

- Prior art keywords

- command

- data processing

- memory

- circuit

- control signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/061—Improving I/O performance

- G06F3/0613—Improving I/O performance in relation to throughput

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1605—Handling requests for interconnection or transfer for access to memory bus based on arbitration

- G06F13/1642—Handling requests for interconnection or transfer for access to memory bus based on arbitration with request queuing

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1605—Handling requests for interconnection or transfer for access to memory bus based on arbitration

- G06F13/161—Handling requests for interconnection or transfer for access to memory bus based on arbitration with latency improvement

- G06F13/1615—Handling requests for interconnection or transfer for access to memory bus based on arbitration with latency improvement using a concurrent pipeline structrure

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1605—Handling requests for interconnection or transfer for access to memory bus based on arbitration

- G06F13/1647—Handling requests for interconnection or transfer for access to memory bus based on arbitration with interleaved bank access

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1673—Details of memory controller using buffers

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1684—Details of memory controller using multiple buses

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/382—Information transfer, e.g. on bus using universal interface adapter

- G06F13/385—Information transfer, e.g. on bus using universal interface adapter for adaptation of a particular data processing system to different peripheral devices

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/061—Improving I/O performance

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0655—Vertical data movement, i.e. input-output transfer; data movement between one or more hosts and one or more storage devices

- G06F3/0659—Command handling arrangements, e.g. command buffers, queues, command scheduling

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0673—Single storage device

- G06F3/0679—Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0683—Plurality of storage devices

- G06F3/0688—Non-volatile semiconductor memory arrays

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

- G11C5/04—Supports for storage elements, e.g. memory modules; Mounting or fixing of storage elements on such supports

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/06—Address interface arrangements, e.g. address buffers

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Read Only Memory (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Memory System (AREA)

- Dram (AREA)

Description

揮発性メモリ装置は、読み取り/書き込み速度が速いものの、外部電源供給が中断されれば、保存された内容が消えてしまう。

一方、不揮発性メモリ装置は、読み取り/書き込み速度が揮発性メモリ装置に比べて遅いものの、外部電源供給が中断されても、その内容を保存する。

特に、フラッシュメモリに基づいて具現されたソリッドステートドライブ(SSD)は、パーソナルコンピュータ、ノート型パソコン、ワークステーション、サーバシステムなどにおける大容量ストレージデバイスとして使われている。

一般的なSSD装置は、SATAインターフェース又は「PCI-express」インターフェースに基づいて、コンピューティングシステムと接続される。

そのような現象は、コンピューティングシステムの性能を阻害する要因として作用し、前述した問題点を解決するための様々な性能向上技法が開発されている。

特に、メモリインターリービング動作で、メモリ装置は、追加的なコマンドの入力なしに、中断されていたデータ処理を再開することができる。

したがって、追加的なコマンドの入力及び/又はデコーディングなどにかかる時間を短縮することができ、メモリ装置及び保存装置のデータ処理にかかる時間を短縮することができる。

さらに、データ通信にかかる時間を短縮することにより、メモリ装置及び保存装置の動作速度を向上させることができる。

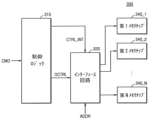

データ処理システム10は、ホスト100及びメモリシステム400を含み、メモリシステム400は、メモリコントローラ200及びメモリ装置300を含む。

しかし、それらに制限されるものではなく、例えば、メモリコントローラ200は、メモリ装置300と共にメモリシステム400、又は単一のチップ、単一のパッケージ、単一のモジュールなどのストレージデバイスとして提供され得る。

また、メモリシステム400は、PCカード、コンパクトフラッシュ(登録商標)カード(CF)、スマートメディアカード(SM/SMC)、メモリスティック(登録商標)、マルチメディアカード(MMC、RS-MMC、MMCmicro)、SDカード(SD、miniSD、microSD)、ユニバーサルフラッシュ記憶装置(UFS)などを構成する。

他の例として、メモリシステム400は、SSD(Solid State Disk/Drive)を構成することも可能である。

例示的には、ホスト100は、メモリコントローラ200と、USB(Universal Serial Bus)プロトコル、MMC(Multi Media Card)プロトコル、PCI(Peripheral Component Interconnection)プロトコル、PCI-E(PCI-Express)プロトコル、ATA(Advanced Technology Attachment)プロトコル、Serial-ATAプロトコル、Parallel-ATAプロトコル、SCSI(Small Computer Small Interface)プロトコル、ESDI(Enhanced Small Disk Interface)プロトコル、IDE(Integrated Drive Electronics)プロトコル、MIPI(Mobile Industry Processor Interface)プロトコル及びUFS(Universal Flash Storage)プロトコルのような様々なインターフェースプロトコルの内の少なくとも一つに基づいて、データDATAを交換する。

例えば、メモリコントローラ200は、ホスト100から受信したデータ処理要請REQに応答して、メモリ装置300に保存されたデータDATAを読み取るか、又はメモリ装置300にデータDATAを書き込むように、メモリ装置300を制御する。

例えば、メモリコントローラ200は、メモリ装置300に、アドレスADDR、コマンドCMD及び制御信号などを提供することにより、メモリ装置300の書き込み動作、読み取り動作、及び消去動作などを制御する。

また、上記動作のためのデータDATAが、メモリコントローラ200とメモリ装置300との間で送受信される。

一実施形態において、メモリコントローラ200は、メモリ装置300にリードイネーブル信号(Read Enable Signal)を提供する。

例えば、メモリ装置300は、第1メモリチップ(340_1)~第Nメモリチップ(340_N)(但し、Nは2以上の自然数)を含む。

メモリチップは、メモリウェイ(memory way)と称することもある。

第1メモリチップ(340_1)~第Nメモリチップ(340_N)それぞれは、少なくとも一つのメモリセルアレイを含む。

メモリセルアレイは、複数のワードラインと複数のビットラインとが交差する領域に配置される複数のメモリセルを含み、複数のメモリセルは、不揮発性メモリセルであり得る。

例えば、それぞれのメモリセルは、2ビットのデータを保存する2ビットマルチレベルセルであってもよく、3ビットのデータを保存するトリプルレベルセル(TLC)であってもよく、4ビットのデータを保存するクアドラプルレベルセル(QLC)であってもよく、それ以上のビットデータを保存するマルチレベルセルであってもよい。

しかし、本発明は、それらに限定されず、例えば、一部のメモリセルは、1ビットのデータを保存するシングルレベルセル(SLC)であり、他の一部のメモリセルは、マルチレベルセルであってもよい。

また、一実施形態において、メモリ装置300は、COP(Cell-on-Peri又はCell-over-Peri)構造を有してもよい。

メモリ装置300は、メモリコントローラ200から受信した信号に応答して、データDATAの書き込み動作、読み取り動作、及び消去動作などの動作を行う。

一実施形態において、メモリ装置300は、メモリコントローラ200から提供されるリードイネーブル信号に基づいて、データストローブ信号を生成する。

また、一実施形態において、メモリ装置300は、リードイネーブル信号に基づいて生成されたデータストローブ信号をメモリコントローラ200に提供する。

一実施形態において、メモリ装置300の動作周波数は、1GHz以上であってもよい。

インターフェース回路320は、メモリ装置300の外部から入力される少なくとも一つの信号をバッファリングする。

例えば、インターフェース回路320は、メモリコントローラ200から提供されるコマンドCMD、及び/又はコマンドCMDに基づいて生成されるデータ処理制御信号を保存する。

インターフェース回路320は、バッファチップ又はバッファ回路と称することもある。

ここで、バッファチップは、メモリ装置300の外部から入力される信号をバッファリングするように構成される。

複数のレジスタは、複数のメモリチップについてのコマンド情報を保存する。

ここで、コマンド情報とは、メモリコントローラ200から提供されるコマンドCMDと関連した情報であり、コマンドCMD及び/又はコマンドCMDに基づいてメモリ装置300の内部で生成されるデータ処理制御信号を含む。

データ処理制御信号は、メモリ装置300の書き込み動作、読み取り動作、及び消去動作のようなデータ処理に必要な制御信号を含む。

例えば、データ処理制御信号は、電圧制御信号、ロウデコーダ制御信号、カラムデコーダ制御信号、及びデータ入出力制御信号のような様々な制御信号の内の少なくとも一つを含む。

一実施形態において、メモリコントローラ200から特定のメモリチップについてのコマンドCMDが入力される場合、インターフェース回路320は、アドレスADDR及び/又はチップ選択信号に基づいて、複数のレジスタの内、特定のメモリチップに対応するレジスタを選択し、選択されたレジスタに、コマンドCMDと関連したコマンド情報を保存する。

そのために、一実施形態において、インターフェース回路320は、複数のレジスタの内、コマンド情報が保存される一つのレジスタを選択するためのデマルチプレクサ回路322(図4参照)を含み得る。

例えば、メモリ装置300内の複数のメモリチップが、第2メモリチップ(340_2)(図2参照)をさらに含む場合、メモリ装置300は、第1メモリチップ(340_1)に対する第1データ処理を行う途中で、第2メモリチップに対するデータ処理コマンドに応答して、第1データ処理を中断し、第2メモリチップに対する第2データ処理を行う。

第2データ処理の実行が完了することに応答して、メモリ装置300は、第1メモリチップ(340_1)に対する第1データ処理の内、行われていない残りのデータ処理を行う。

それは、第1メモリチップ(340_1)の選択を表すアドレスADDR及び/又はチップ選択信号がメモリ装置300に入力されることに対する応答でもある。

それによって、第2データ処理が完了した後、第1データ処理の内、残りのデータ処理が行われるためには、メモリ装置が、メモリコントローラから第1データ処理と関連したコマンド(例えば、データ処理コマンド又は再開(resume)コマンド)をさらに受信しなければならない。

そのような追加的なコマンドを受信するのに時間がかかるため、メモリ装置のデータ処理時間が増加するという問題点が、比較例としてのメモリ装置に存在していた。

そのために、インターフェース回路320は、アドレスADDR及び/又はチップ選択信号に基づいて、複数のレジスタの内、要求されるメモリチップに対応するレジスタを選択し、選択されたレジスタからコマンドCMDと関連したコマンド情報を提供し、提供されたコマンド情報を出力する。

そのために、一実施形態において、インターフェース回路320は、複数のレジスタの内、コマンド情報を提供する一つのレジスタを選択するためのマルチプレクサ回路326(図4参照)を含み得る。

したがって、追加的なコマンドの入力及び/又はコマンドのデコーディングなどにかかる時間を短縮することができ、メモリ装置300及びメモリシステム400のデータ通信にかかる時間を短縮することができる。

さらに、データ通信にかかる時間を短縮することにより、メモリ装置300及びメモリシステム400の動作速度を向上させることができる。

図2のメモリ装置300は、図1のメモリ装置300に対応する構成であり、図1と重複する説明は省略する。

メモリ装置300は、制御ロジック310、インターフェース回路320、データ処理制御回路330、及び複数のメモリチップを含み、複数のメモリチップは、第1メモリチップ(340_1)、第2メモリチップ(340_2)~第Nメモリチップ(340_N)を含む。

例えば、制御ロジック310は、メモリコントローラ200(図1参照)から受信したコマンドCMD、アドレスADDR、及び制御信号などに基づいて、複数のメモリチップに含まれたメモリセルアレイにデータを書き込むか、又はメモリセルアレイからデータを読み取るための各種内部制御信号を生成する。

一実施形態において、制御ロジック310は、インターフェース回路320を制御してもよい。

そのために、制御ロジック310は、インターフェース回路制御信号(CTRL_INT)をインターフェース回路320に提供する。

一実施形態において、プロセッシング回路は、中央処理装置(Central Processing Unit: CPU)、算術論理装置(Arithmetic Logic Unit: ALU)、デジタル信号プロセッサ、マイクロコンピュータ、FPGA(Field Programmable Gate Array)、システム・オン・チップ(SoC)、プログラミング可能なロジックコントローラ、マイクロプロセッサ、注文型半導体(Application Specific Integrated Circuit:ASIC)などを含むが、それらに制限されるものではない。

一実施形態において、インターフェース回路320は、複数のメモリチップそれぞれに対応する複数のレジスタを含み、それぞれのレジスタは、対応するメモリチップについてのコマンド情報を保存する。

ここで、実施形態によって、コマンド情報は、コマンドCMDそのものであってもよく、コマンドCMDに基づいて生成されるデータ処理制御信号を含んでもよく、コマンドCMD及びデータ処理制御信号の両方を含んでもよい。

図2では、インターフェース回路320のそれぞれのレジスタが、対応するメモリチップについてのコマンドCMDを保存する実施形態を中心に説明する。

一実施形態において、インターフェース回路320は、複数のレジスタの内の一つのレジスタを選択することにより、選択されたレジスタからコマンドを提供される。

ここで、提供されたコマンドを、選択されたコマンド(CMD_s)とする。

インターフェース回路320は、選択されたコマンド(CMD_s)をデータ処理制御回路330に提供する。

第2メモリチップ(340_2)に対する第2データ処理が完了した後、インターフェース回路320は、第1レジスタに保存された第1メモリチップ(340_1)に対する第1コマンドを、選択されたコマンド(CMD_s)として出力する。

データ処理制御回路330は、コマンドCMD及び/又は選択されたコマンド(CMD_s)に基づいて、複数のメモリチップの内の少なくとも一つのメモリチップに対するデータ処理を制御する。

一方、データ処理制御回路330は、様々な形態に具現可能であり、一実施形態によって、データ処理制御回路330は、ハードウェア形態に具現されてもよく、ハードウェアとソフトウェアが結合された形態に具現されてもよい。

データ処理制御回路330がハードウェア形態に具現される場合、データ処理制御回路330は、コマンドCMD及び/又は選択されたコマンド(CMD_s)に基づいて、データ処理制御信号を生成するための回路を含む。

また、例えば、データ処理制御回路330がソフトウェア形態に具現される場合、メモリ装置300内の任意のメモリにローディングされたプログラム及び/又はインストラクションが、制御ロジック310又はメモリ装置300内の任意のプロセッサにより実行されることにより、データ処理制御信号が生成される。

しかし、上記実施形態に限定されるものではなく、データ処理制御回路330は、ファームウェアのようにソフトウェアとハードウェアが結合された形態に具現されてもよい。

そのために、インターフェース回路320は、第1メモリチップ(340_1)に対応する第1レジスタに保存された第1コマンドを、選択されたコマンド(CMD_s)として、データ処理制御回路330に提供する。

データ処理制御回路330は、選択されたコマンド(CMD_s)に基づいて、第1メモリチップ(340_1)に対する第1データ処理と関連したデータ処理制御信号を生成する。

データ処理制御回路330は、生成されたデータ処理制御信号を利用して、第1メモリチップ(340_1)に対する第1データ処理の内の残りのデータ処理が行われるようにする。

したがって、追加的なコマンドの入力及び/又はコマンドのデコーディングなどにかかる時間を短縮することができ、メモリ装置300のデータ通信にかかる時間を短縮することができる。

さらに、データ通信にかかる時間を短縮することにより、メモリ装置300の動作速度を向上させることができる。

図3は、特に、図2のメモリ装置300において、データ処理制御回路330がハードウェアと結合されたソフトウェアにより具現された場合のメモリ装置300を示す。

図3のメモリ装置300については、図2との相違点を中心に説明する。

メモリ装置300は、制御ロジック310、インターフェース回路320、及び複数のメモリチップを含み、複数のメモリチップは、第1メモリチップ(340_1)、第2メモリチップ(340_2)~第Nメモリチップ(340_N)を含む。

インターフェース回路320は、複数のレジスタの内の一つのレジスタを選択し、選択されたレジスタから、選択されたコマンド(CMD_s)を出力する。

インターフェース回路320は、選択されたコマンド(CMD_s)を制御ロジック310に提供する。

制御ロジック310は、メモリ装置300の外部(例えば、図1のメモリコントローラ200)から提供されるコマンドCMD及び/又は選択されたコマンド(CMD_s)に基づいて、複数のメモリチップの内の少なくとも一つのメモリチップについてのデータ処理を制御する。

例えば、制御ロジック310は、選択されたコマンド(CMD_s)に基づいて、データ処理に必要なデータ処理制御信号を生成する。

言い換えれば、図2と比較するとき、制御ロジック310が、図2のデータ処理制御回路330の機能まで行うことができる。

図4のインターフェース回路320は、図1~図3のインターフェース回路320に対応する構成であり、図1~図3と重複する説明は省略する。

図4は、図2及び図3を共に参照して説明する。

インターフェース回路320は、デマルチプレクサ回路322、複数のレジスタ324、マルチプレクサ回路326、及び経路選択回路328を含む。

第1レジスタ(325_1)~第Nレジスタ(325_N)それぞれは、第1メモリチップ(340_1)~第Nメモリチップ(340_N)に対応する。

例えば、第1レジスタ(325_1)は、第1メモリチップ(340_1)についてのコマンドと関連したコマンド情報を保存する。

コマンド情報は、コマンドそのもの及び/又はコマンドに基づいて生成されるデータ処理制御信号を含み、一実施形態において、コマンドは、データ処理と関連したデータ処理コマンドを含み得る。

言い換えれば、デマルチプレクサ回路322は、複数のレジスタ324の内の一つのレジスタを選択し、選択されたレジスタに、入力されるコマンド情報CIを提供する。

そのとき、コマンド情報CIが第1メモリチップ(340_1)と関連している場合であれば、デマルチプレクサ回路322は、コマンド情報CIを、第1メモリチップ(340_1)に対応する第1レジスタ(325_1)に提供する。

同様に、コマンド情報CIが第2メモリチップ(340_2)と関連している場合であれば、デマルチプレクサ回路322は、コマンド情報CIを、第2メモリチップ(340_2)に対応する第2レジスタ(325_2)に提供する。

そのとき、一実施形態において、デマルチプレクサ回路322は、経路選択回路328により提供されるデマルチプレクサ制御信号(CTRL_D)に基づいて、複数のレジスタ324の内の一つのレジスタを選択し得る。

図2及び図3と比較すれば、一実施形態において、選択されたコマンド情報(CI_s)は、選択されたコマンド(CMD_s)を含んでもよい。

そのとき、一実施形態において、マルチプレクサ回路326は、経路選択回路328により提供されるマルチプレクサ制御信号(CTRL_M)に基づいて、複数のレジスタ324の内の一つのレジスタを選択する。

マルチプレクサ回路326は、選択されたコマンド情報(CI_s)を、制御ロジック310又はデータ処理制御回路330に提供する。

例えば、メモリ装置300に、第1メモリチップ(340_1)に対する第1コマンドが入力された場合、経路選択回路328は、デマルチプレクサ回路322が複数のレジスタ324の内の第1レジスタ(325_1)を選択するようにするために、第1レジスタ(325_1)の選択を指示するデマルチプレクサ制御信号(CTRL_D)をデマルチプレクサ回路322に提供する。

同様に、例えば、メモリ装置300が、第1メモリチップ(340_1)に対するデータ処理を再開しようとする場合、経路選択回路328は、マルチプレクサ回路326が複数のレジスタ324の内の第1レジスタ(325_1)を選択するようにするために、第1レジスタ(325_1)の選択を指示するマルチプレクサ制御信号(CTRL_M)をマルチプレクサ回路326に提供する。

図5は、図2~図4を共に参照して説明する。

まず、メモリ装置300は、第1メモリチップ(340_1)に対する第1コマンドに応答して、第1メモリチップ(340_1)に対する第1データ処理を行う(ステップS120)。

例えば、経路選択回路328は、アドレスADDR及び/又はチップ選択信号に基づいて、デマルチプレクサ回路322が第1レジスタ(325_1)を選択するように、デマルチプレクサ制御信号(CTRL_D)をデマルチプレクサ回路322に提供する。

デマルチプレクサ回路322は、デマルチプレクサ制御信号(CTRL_D)によって、入力される第1コマンドと関連したコマンド情報を第1レジスタ(325_1)に提供する。

そのとき、デマルチプレクサ制御信号(CTRL_D)は、アドレスADDR及び/又はチップ選択信号に基づいて、経路選択回路328により生成されたものであり得る。

第1レジスタ(325_1)は、提供されたコマンド情報を保存する。

一実施形態において、コマンド情報は、第1コマンドそのもの及び/又は第1コマンドに基づいて生成されるデータ処理制御信号を含み得る。

一実施形態において、第2コマンドの入力に応答して、メモリ装置300は、第1メモリチップ(340_1)に対する第1データ処理を中断し、第2コマンドに基づいて、第2メモリチップ(340_2)に対する第2データ処理を行う。

他の実施形態において、第1コマンドは、第1メモリチップ(340_1)に対するデータ読み取りコマンドであり、第2コマンドは、第2メモリチップ(340_2)に対するデータ書き込みコマンドであってもよい。

一実施形態において、第1メモリチップ(340_1)の選択を表すアドレスADDR及び/又はチップ選択信号が入力されることに応答して、第1データ処理の内の残ったデータ処理の少なくとも一部を行う。

一実施形態において、経路選択回路328は、アドレスADDR及び/又はチップ選択信号に基づいて、マルチプレクサ回路326が第1レジスタ(325_1)を選択するように、マルチプレクサ制御信号(CTRL_M)をマルチプレクサ回路326に提供する。

そのとき、マルチプレクサ制御信号(CTRL_M)は、アドレスADDR及び/又はチップ選択信号に基づいて、経路選択回路328から生成されたものであってもよい。

例えば、マルチプレクサ回路326は、コマンド情報を制御ロジック310又はデータ処理制御回路330に提供する。

一実施形態において、コマンド情報が第1コマンドを含む場合、制御ロジック310又はデータ処理制御回路330は、提供された第1コマンドに基づいて、様々なデータ処理制御信号を生成することにより、第1データ処理の内の残りのデータ処理を制御する。

一実施形態において、メモリ装置300は、第2データ処理が完了することに応答して、第1データ処理の内の残りのデータ処理を行う。

一実施形態において、メモリ装置300は、メモリ装置300の外部から入力される追加的なコマンド(例えば、再開コマンド)なしで、インターフェース回路320に保存された第1コマンドに基づいて、第1データ処理の内の残りのデータ処理を行うことができる。

図6は、図1~図4を共に参照して説明する。

また、図6は、データ処理制御回路330がソフトウェアとして制御ロジック310に具現された実施形態における動作方法の実施形態を示す。

制御ロジック310は、第1コマンドCMD1に応答して、第1メモリチップ(340_1)に対する第1データ処理を制御する(ステップS220)。

インターフェース回路320は、第1コマンドCMD1と関連した第1コマンド情報を保存する(ステップS230)。

例えば、第1メモリチップ(340_1)に対応する第1レジスタは、第1コマンド情報を保存する。

第1コマンド情報は、第1コマンドCMD1、又は第1コマンドCMD1に基づいて生成されるデータ処理制御信号の内の少なくとも一つを含む。

メモリコントローラ200は、第2メモリチップ(340_2)に対する第1コマンドCMD2を、インターフェース回路320及び制御ロジック310へ伝送する(ステップS250)。

図6には、ステップS240がステップS250よりも先行するように示しているが、それに制限されない。

実施形態によって、ステップS240は、ステップS250に応答して行われてもよい。

第1メモリチップ(340_1)の選択を表すアドレスADDR及び/又はチップ選択信号がメモリ装置300に入力されることに応答して、インターフェース回路320は、第1レジスタに保存された第1コマンド情報を選択することにより、第1コマンド情報を、選択されたコマンド情報(CI_s)として、制御ロジック310に提供する(ステップS270)。

例えば、図6には示していないが、ステップS270以前に、メモリコントローラ200は、第1メモリチップ(340_1)の選択を表すアドレスADDR及び/又はチップ選択信号をインターフェース回路320に提供してもよい。

制御ロジック310は、インターフェース回路320から提供された第1コマンド情報に基づいて、第1メモリチップ(340_1)に対する第1データ処理の内の残りのデータ処理を制御する(ステップS280)。

図7Aを参照すると、経路選択回路328aは、アドレス比較回路(328_1a)及び制御信号生成回路(328_2a)を含む。

アドレス比較回路(328_1a)は、アドレスADDRに基づいて、複数のメモリチップの内の一つのメモリチップを判断する。

例えば、アドレス比較回路(328_1a)は、アドレス、又はアドレスの範囲に対応するメモリチップ情報を含むルックアップテーブルを保存し、入力されるアドレスADDRをルックアップテーブルと比較することにより、入力されるアドレスADDRに対応するメモリチップを判断する。

制御信号生成回路(328_2a)は、メモリチップ情報MDIに基づいて、制御信号を生成する。

例えば、制御信号生成回路(328_2a)は、メモリチップ情報MDIに基づいて、デマルチプレクサ制御信号(CTRL_D)及びマルチプレクサ制御信号(CTRL_M)を生成する。

ところで、アドレス比較回路(328_1a)及び制御信号生成回路(328_2a)は、様々な形態で具現可能であり、実施形態によって、ハードウェア、ソフトウェア又はそれらの組み合わせにより具現される。

制御信号生成回路(328_2b)は、チップ選択信号CSに基づいて、制御信号を生成する。

例えば、チップ選択信号CSは、複数のメモリチップ、メモリチップ又はメモリウェイの内のいずれか一つのメモリチップ、メモリチップ又はメモリウェイを指示する選択信号を総称する信号でもある。

例えば、制御信号生成回路(328_2b)は、チップ選択信号CSに基づいて、デマルチプレクサ制御信号(CTRL_D)及びマルチプレクサ制御信号(CTRL_M)を生成する。

特に、図8は、メモリ装置300のインターフェース回路320の構成の一実施形態を示す。

図8は、図4との相違点を中心に説明する。

言い換えれば、図4と比較するとき、経路選択回路328は、インターフェース回路320の外部にも具現される。

経路選択回路328は、様々な形態に具現可能であり、例えば、ハードウェア、ソフトウェア又はそれらの組み合わせにより具現される。

一実施形態において、経路選択回路328が、ハードウェアと結合したソフトウェアにより具現される場合、経路選択回路328は、図2及び図3の制御ロジック310の一部として具現されてもよい。

図9のメモリ装置300について、図2及び図3を参照して示したメモリ装置300との相違点を中心に説明する。

メモリ装置300は、制御ロジック310、データ処理制御信号生成回路315、インターフェース回路320及び複数のメモリチップを含み、複数のメモリチップは、第1メモリチップ(340_1)、第2メモリチップ(340_2)~第Nメモリチップ(340_N)を含む。

データ処理制御信号生成回路315は、入力されるコマンドCMDに基づいて、データ処理制御信号DCTRLを生成する。

データ処理制御信号DCTRLは、メモリ装置300内で、入力されるコマンドCMDによって、データ処理を行うために必要な様々な制御信号の内の少なくとも一つを含む。

データ処理制御信号生成回路315は、データ処理制御信号DCTRLをインターフェース回路320に提供する。

データ処理制御信号生成回路315がハードウェア形態に具現される場合、データ処理制御信号生成回路315は、コマンドCMDに基づいて、データ処理制御信号DCTRLを生成するための回路を含む。

また、例えば、データ処理制御信号生成回路315が、ハードウェアと結合されたソフトウェア形態に具現される場合、メモリ装置300内の任意のメモリにローディングされたプログラム及び/又はインストラクションが、制御ロジック310又はメモリ装置300内の任意のプロセッサにより実行されることにより、データ処理制御信号DCTRLが生成される。

しかし、上記実施形態に限定されるものではなく、データ処理制御信号生成回路315は、ファームウェアのようにソフトウェアとハードウェアが結合された形態に具現されてもよい。

また、インターフェース回路320は、メモリインターリービング動作などで、保存されたデータ処理制御信号DCTRLを、複数のメモリチップ又はメモリ装置300内のデータ処理に必要な構成に提供することにより、複数のメモリチップの内の少なくとも一つのメモリチップに対するデータ処理を制御する。

図10は、特に、図9のメモリ装置300において、データ処理制御信号生成回路315がソフトウェアにより具現された場合のメモリ装置300を示す。

図10のメモリ装置300については、図9との相違点を中心に説明する。

制御ロジック310は、入力されるコマンドCMDに基づいて、データ処理制御信号DCTRLを生成し、データ処理制御信号DCTRLをインターフェース回路320に提供する。

言い換えれば、図9と比較するとき、制御ロジック310が、図9のデータ処理制御信号生成回路315の機能まで行うことができる。

メモリ装置300は、制御ロジック310、インターフェース回路320、コマンド選択回路350及び複数のメモリチップを含み、複数のメモリチップは、第1メモリチップ(340_1)、第2メモリチップ(340_2)~第Nメモリチップ(340_N)を含む。

図11のメモリ装置300については、図3との相違点を中心に説明する。

インターフェース回路320は、選択されたコマンド(CMD_s)をコマンド選択回路350に提供する。

コマンド選択回路350は、選択されたコマンド(CMD_s)及び入力されるコマンドCMDの内の一つのコマンドを選択することにより、第2の選択されたコマンド(CMD_s2)を制御ロジック310に提供する。

そのために、コマンド選択回路350は、マルチプレクサを含み得る。

コマンド選択回路350の存在により、それが存在していない場合と異なり、メモリ装置300の外部から入力されるコマンドCMD、及びインターフェース回路320に保存されるか、又はインターフェース回路320から伝送されたコマンド(CMD_s)の内、要求されるコマンドに基づいて、メモリ装置300のデータ処理を制御することができるという利点がある。

SSDシステム1000は、ホスト1100及びSSD1200を含む。

SSD1200は、信号コネクタSIGを介して、ホスト1100と信号を交換し、電源コネクタPWRを介して、電源を入力される。

SSD1200は、SSDコントローラ1110、補助電源装置1220、及び複数のフラッシュメモリ装置(1230、1240、1250)を含む。

そのとき、SSD1200は、図1~図11に示した実施形態を利用して具現される。

それによって、フラッシュメモリ装置(1230、1240、1250)それぞれは、インターフェース回路及び複数のメモリチップを含む。

インターフェース回路は、複数のレジスタを含み、複数のレジスタそれぞれは、対応するメモリチップについてのコマンド情報を保存する。

フラッシュメモリ装置(1230、1240、1250)それぞれは、メモリインターリービング動作などが行われるとき、インターフェース回路に保存されたコマンド情報に基づいて、中断されていたデータ処理を全て行う。

それによって、SSDコントローラ1210が、追加的な再開コマンドのようなコマンドをフラッシュメモリ装置(1230、1240、1250)に提供しなくてもよい。

したがって、フラッシュメモリ装置(1230、1240、1250)及びSSD1200のデータ通信にかかる時間を短縮することができ、さらに、フラッシュメモリ装置(1230、1240、1250)及びSSD1200の動作速度を向上させることができる。

100 ホスト

200 メモリコントローラ

300 メモリ装置

310 制御ロジック

320 インターフェース回路

322 デマルチプレクサ回路

324 レジスタ

325_1 第1レジスタ

325_2 第2レジスタ

325_N 第Nレジスタ

326 マルチプレクサ回路

328 経路選択回路

330 データ処理制御回路

340_1 第1メモリチップ

340_2 第2メモリチップ

340_N 第Nメモリチップ

400 メモリシステム

ADDR アドレス

CI コマンド情報

CI_s 選択されたコマンド情報

CMD コマンド

CMD_s 選択されたコマンド

CTRL_D デマルチプレクサ制御信号

CTRL_M マルチプレクサ制御信号

CTRL_INT インターフェース回路制御信号

DATA データ

REQ データ処理要請

Claims (14)

- 複数のメモリチップを含むメモリ装置に備えられるインターフェース回路であって、

前記複数のメモリチップそれぞれに対応し、データ処理(data operation)コマンドと関連したコマンド情報を保存する複数のレジスタと、

第1アドレス及び第1チップ選択信号の内の少なくとも一つによって、外部から入力される入力コマンド情報を、前記複数のレジスタの内の一つの選択されたレジスタに提供するように構成されるデマルチプレクサ回路と、

第2アドレス及び第2チップ選択信号の内の少なくとも一つによって、前記複数のレジスタのうち、前記選択されたレジスタから出力コマンド情報を提供され、前記出力コマンド情報を出力するように構成されるマルチプレクサ回路と、を有し、

前記複数のメモリチップは、第1メモリチップと、第2メモリチップと、を含み、

前記複数のレジスタは、前記第1メモリチップに対応するコマンド情報を保存する第1レジスタと、前記第2メモリチップに対応するコマンド情報を保存する第2レジスタと、を含み、

前記デマルチプレクサ回路は、前記第1メモリチップに対する第1データ処理コマンドが入力されることに応答して、前記第1データ処理コマンドと関連した第1コマンド情報を、前記第1レジスタに提供するように構成され、

前記インターフェース回路は、前記第2メモリチップに対する第2データ処理の実行が完了することに応答して、前記第1データ処理コマンドに従って、前記第1メモリチップに対する第1データ処理が中断又は再開されるように構成され、

前記マルチプレクサ回路は、前記第1メモリチップの選択を表すアドレス及びチップ選択信号の内の少なくとも一つの入力に応答して、前記第1レジスタに保存された前記第1コマンド情報を選択することにより出力するように構成され、

前記第1アドレス及び前記第1チップ選択信号の内の少なくとも一つに基づいて、前記デマルチプレクサ回路の第1レジスタ選択を制御するためのデマルチプレクサ制御信号と、前記マルチプレクサ回路の第2レジスタ選択を制御するためのマルチプレクサ制御信号と、を生成するように構成される経路選択回路をさらに有し、

前記経路選択回路は、アドレス比較回路及び制御信号生成回路を含み、

前記アドレス比較回路は、前記複数のメモリチップの内の一つのメモリチップを判断して、判断されたメモリチップに基づいて、メモリチップ情報を前記制御信号生成回路に提供し、

前記制御信号生成回路は、前記メモリチップ情報に基づいて、前記デマルチプレクサ制御信号及びマルチプレクサ制御信号を生成することを特徴とするインターフェース回路。 - 前記アドレス比較回路は、前記第1アドレスを保存されたルックアップテーブル(look-up table)と比較することにより、前記複数のメモリチップの内の一つのメモリチップを選択し、

前記制御信号生成回路は、前記デマルチプレクサ回路及び前記マルチプレクサ回路が、前記複数のレジスタの内の前記選択されたメモリチップに対応するレジスタを選択するように、前記デマルチプレクサ制御信号及び前記マルチプレクサ制御信号を生成するように構成されることを特徴とする請求項1に記載のインターフェース回路。 - 前記アドレス比較回路は、前記複数のメモリチップの内、前記第1チップ選択信号に対応するメモリチップを選択し、

前記制御信号生成回路は、前記デマルチプレクサ回路及び前記マルチプレクサ回路が、前記複数のレジスタの内の前記選択されたメモリチップに対応するレジスタを選択するように、前記デマルチプレクサ制御信号及び前記マルチプレクサ制御信号を生成するように構成されることを特徴とする請求項1に記載のインターフェース回路。 - 前記第1コマンド情報は、前記第1データ処理コマンド、及び前記第1データ処理コマンドに基づいて生成されるデータ処理制御信号の内の少なくとも一つを含むことを特徴とする請求項1に記載のインターフェース回路。

- 第1メモリチップ及び第2メモリチップを含むメモリ装置の動作方法であって、

第1コマンドの第1入力に応答して、前記第1メモリチップに対する第1データ処理を行うステップと、

前記第1コマンドと関連した第1コマンド情報を、第1メモリチップに対応する第1レジスタに保存するステップと、

前記第1データ処理を中断するステップと、

第2コマンドの第2入力に応答して、前記第2メモリチップに対する第2データ処理を行うステップと、

前記第2データ処理の実行が完了することに応答して、前記第1レジスタに保存された前記第1コマンド情報に基づいて追加的な再開(resume)コマンドの受信なしに、前記第1メモリチップ上で、前記第1データ処理の内、行われていない残りのデータ処理を行うステップと、を有し、

前記残りのデータ処理を行うステップは、前記第1メモリチップの選択を表すアドレス及びチップ選択信号の内の少なくとも一つの第3入力に応答して、前記第1データ処理の内の前記残りのデータ処理を行うステップを含むことを特徴とするメモリ装置の動作方法。 - 前記メモリ装置は、複数のレジスタを含むインターフェース回路を含み、

前記複数のレジスタはそれぞれ、複数のメモリチップの内の対応する1つに対応するコマンド情報を保存し、

前記複数のメモリチップは、前記第1メモリチップ及び前記第2メモリチップを含むことを特徴とする請求項5に記載のメモリ装置の動作方法。 - 前記第1コマンド情報を保存するステップは、前記複数のレジスタの内、前記第1メモリチップに対応する第1レジスタに、前記第1コマンド情報を保存するステップを含むことを特徴とする請求項6に記載のメモリ装置の動作方法。

- 前記第1コマンド情報は、前記第1コマンド、及び前記第1コマンドに基づいて生成される第1データ処理制御信号の内の少なくとも一つを含むことを特徴とする請求項5に記載のメモリ装置の動作方法。

- 前記第1コマンド情報を保存するステップは、前記第1コマンドを保存するステップを含み、

前記残りのデータ処理を行うステップは、前記保存された第1コマンドに基づいて、前記第1コマンドと関連した第2データ処理制御信号を生成するステップと、

前記第2データ処理制御信号を利用して、前記第1データ処理の内の前記残りのデータ処理を行うステップと、を含むことを特徴とする請求項8に記載のメモリ装置の動作方法。 - 前記第1コマンド情報を保存するステップは、前記第1コマンドに基づいて、第1データ処理制御信号を生成するステップと、

前記第1データ処理制御信号を保存するステップと、を含み、

前記残りのデータ処理を行うステップは、前記保存された第1データ処理制御信号を利用して、前記第1データ処理の内の前記残りのデータ処理を行うステップを含むことを特徴とする請求項8に記載のメモリ装置の動作方法。 - メモリ装置であって、

第1メモリチップ及び第2メモリチップを含む複数のメモリチップと、

前記複数のメモリチップそれぞれに対応する複数のコマンド情報を保存し、前記保存されたコマンド情報の内の少なくとも一つのコマンド情報を選択的に出力するように構成されるインターフェース回路と、

第1選択信号及び第1コマンドに従って前記第1メモリチップに対する第1データ処理を実行し、前記第1データ処理の実行中に第2選択信号及び前記第2メモリチップに対する第2コマンドが入力されることに応答して前記第1メモリチップに対する前記第1データ処理を中断し、前記第2メモリチップに対する前記第2コマンドに対応する第2データ処理が実行されるように前記メモリ装置を制御し、前記第1選択信号が前記メモリ装置に入力されることに応答して前記複数のコマンド情報の内の前記インターフェース回路から受信した前記第1コマンドと関連する第1コマンド情報に基づいて前記第1メモリチップに対する前記第1データ処理の内の残りのデータ処理が実行されるように前記メモリ装置を制御するように構成される制御ロジックと、を有し、

前記インターフェース回路は、前記複数のメモリチップそれぞれに対応するデータ処理コマンドを保存し、

前記制御ロジックは、前記第1コマンドに基づいて、データ処理制御信号を生成し、前記データ処理制御信号に基づいて、前記第1データ処理の内の残りのデータ処理が行われるように前記メモリ装置を制御するように構成され、

前記メモリ装置は、コマンド選択回路をさらに有し、

前記コマンド選択回路は、前記インターフェース回路から受信した前記第1コマンド、及び前記メモリ装置の外部から入力される第3コマンドの内の一つのコマンドを選択して前記制御ロジックに出力し、

前記制御ロジックは、選択されたコマンドに基づいて、前記データ処理制御信号を生成するように構成されることを特徴とするメモリ装置。 - 前記インターフェース回路は、前記複数のメモリチップそれぞれに対応する前記コマンド情報を保存する複数のレジスタと、

第1アドレス及び第1チップ選択信号の内の少なくとも一つに従って、前記メモリ装置の外部から受信した入力コマンド情報を、前記複数のレジスタの内から選択された一つのレジスタに提供するように構成されるデマルチプレクサ回路と、

第2アドレス及び第2チップ選択信号の内の少なくとも一つに従って、前記複数のレジスタの内の前記選択されたレジスタから出力コマンド情報を受信し、前記出力コマンド情報を出力するように構成されるマルチプレクサ回路と、を含むことを特徴とする請求項11に記載のメモリ装置。 - 前記インターフェース回路は、前記第1アドレス及び前記第1チップ選択信号の内の少なくとも一つに基づいて、前記デマルチプレクサ回路の第1レジスタ選択を制御するためのデマルチプレクサ制御信号を生成し、前記第2アドレス及び前記第2チップ選択信号の内の少なくとも一つに基づいて、前記マルチプレクサ回路の第2レジスタ選択を制御するためのマルチプレクサ制御信号を生成するように構成される経路選択回路をさらに含むことを特徴とする請求項12に記載のメモリ装置。

- 前記インターフェース回路は、前記複数のメモリチップそれぞれに対応するデータ処理コマンドに基づいて生成されるデータ処理制御信号を保存し、

前記制御ロジックは、前記第2データ処理の実行が完了することに応答して、前記第1コマンドに対応する第1データ処理制御信号に基づいて、前記第1データ処理の内の残りのデータ処理が行われるように、前記メモリ装置を制御するように構成されることを特徴とする請求項11に記載のメモリ装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2019-0113012 | 2019-09-11 | ||

| KR1020190113012A KR20210031266A (ko) | 2019-09-11 | 2019-09-11 | 인터페이스 회로, 메모리 장치, 저장 장치 및 메모리 장치의 동작 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2021043975A JP2021043975A (ja) | 2021-03-18 |

| JP7640239B2 true JP7640239B2 (ja) | 2025-03-05 |

Family

ID=71620347

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020152603A Active JP7640239B2 (ja) | 2019-09-11 | 2020-09-11 | インターフェース回路並びにメモリ装置及びその動作方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US11199975B2 (ja) |

| EP (1) | EP3792775A1 (ja) |

| JP (1) | JP7640239B2 (ja) |

| KR (2) | KR20210031266A (ja) |

| CN (1) | CN112486866B (ja) |

| SG (1) | SG10202006754WA (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102817228B1 (ko) * | 2020-06-29 | 2025-06-05 | 에스케이하이닉스 주식회사 | 액티브동작을 수행하기 위한 전자장치 |

| CN114550775B (zh) * | 2020-11-24 | 2025-08-29 | 瑞昱半导体股份有限公司 | 内存控制器及其控制方法 |

| US12020771B2 (en) * | 2021-08-13 | 2024-06-25 | Micron Technology, Inc. | Die location detection for grouped memory dies |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009528609A (ja) | 2006-03-28 | 2009-08-06 | ノキア コーポレイション | 不揮発性メモリの読み出し待ち時間を減少させる方法及びデバイス |

| JP2010512586A (ja) | 2006-12-06 | 2010-04-22 | フュージョン マルチシステムズ,インク.(ディービイエイ フュージョン−アイオー) | 空データトークン指令を用いてストレージデバイス中のデータを管理するための装置、システム及び方法 |

| US20110219171A1 (en) | 2010-03-05 | 2011-09-08 | 248 SolidState, Inc | Virtual channel support in a nonvolatile memory controller |

| JP2012068936A (ja) | 2010-09-24 | 2012-04-05 | Toshiba Corp | メモリシステム |

| JP2013200692A (ja) | 2012-03-23 | 2013-10-03 | Toshiba Corp | メモリシステム |

| JP2018525737A (ja) | 2015-07-28 | 2018-09-06 | 華為技術有限公司Huawei Technologies Co.,Ltd. | 増大された効率のためのインテリジェントメモリアーキテクチャ |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4716545A (en) * | 1985-03-19 | 1987-12-29 | Wang Laboratories, Inc. | Memory means with multiple word read and single word write |

| US5136582A (en) * | 1990-05-29 | 1992-08-04 | Advanced Micro Devices, Inc. | Memory management system and method for network controller |

| JPH0447347A (ja) * | 1990-06-12 | 1992-02-17 | Fujitsu Ltd | 記憶制御装置 |

| JP2003036681A (ja) | 2001-07-23 | 2003-02-07 | Hitachi Ltd | 不揮発性記憶装置 |

| US6778436B2 (en) | 2001-10-10 | 2004-08-17 | Fong Piau | Apparatus and architecture for a compact flash memory controller |

| EP2458505B1 (en) * | 2006-02-09 | 2014-10-08 | Google, Inc. | Memory circuit system and method |

| JPWO2007116486A1 (ja) | 2006-03-31 | 2009-08-20 | 富士通株式会社 | メモリ装置、その制御方法、その制御プログラム、メモリ・カード、回路基板及び電子機器 |

| KR100851545B1 (ko) | 2006-12-29 | 2008-08-11 | 삼성전자주식회사 | 커맨드 및 어드레스 핀을 갖는 낸드 플래시 메모리 및그것을 포함한 플래시 메모리 시스템 |

| US8972627B2 (en) * | 2009-09-09 | 2015-03-03 | Fusion-Io, Inc. | Apparatus, system, and method for managing operations for data storage media |

| US8966208B2 (en) * | 2010-02-25 | 2015-02-24 | Conversant Ip Management Inc. | Semiconductor memory device with plural memory die and controller die |

| KR101893176B1 (ko) | 2010-12-03 | 2018-08-29 | 삼성전자주식회사 | 멀티 칩 메모리 장치 및 그것의 구동 방법 |

| US20120239874A1 (en) * | 2011-03-02 | 2012-09-20 | Netlist, Inc. | Method and system for resolving interoperability of multiple types of dual in-line memory modules |

| US9645758B2 (en) * | 2011-07-22 | 2017-05-09 | Sandisk Technologies Llc | Apparatus, system, and method for indexing data of an append-only, log-based structure |

| US9335952B2 (en) | 2013-03-01 | 2016-05-10 | Ocz Storage Solutions, Inc. | System and method for polling the status of memory devices |

| US9684622B2 (en) * | 2014-06-09 | 2017-06-20 | Micron Technology, Inc. | Method and apparatus for controlling access to a common bus by multiple components |

| US9536590B1 (en) * | 2014-09-03 | 2017-01-03 | Marvell International Ltd. | System and method of memory electrical repair |

| US9933950B2 (en) * | 2015-01-16 | 2018-04-03 | Sandisk Technologies Llc | Storage operation interrupt |

| US9921763B1 (en) | 2015-06-25 | 2018-03-20 | Crossbar, Inc. | Multi-bank non-volatile memory apparatus with high-speed bus |

| KR102435181B1 (ko) * | 2015-11-16 | 2022-08-23 | 삼성전자주식회사 | 반도체 메모리 장치, 이를 포함하는 메모리 시스템 및 메모리 시스템의 동작 방법 |

| JP2017123208A (ja) * | 2016-01-06 | 2017-07-13 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| US10025536B2 (en) * | 2016-02-10 | 2018-07-17 | Sandisk Technologies Llc | Memory system and method for simplifying scheduling on a flash interface module and reducing latencies in a multi-die environment |

| US10056132B1 (en) * | 2016-02-16 | 2018-08-21 | Seagate Technology Llc | Assignable registers on a preamp chip |

| US11403241B2 (en) * | 2017-10-02 | 2022-08-02 | Micron Technology, Inc. | Communicating data with stacked memory dies |

| TWI684860B (zh) * | 2018-10-15 | 2020-02-11 | 慧榮科技股份有限公司 | 用來進行讀取加速之方法以及資料儲存裝置及其控制器 |

-

2019

- 2019-09-11 KR KR1020190113012A patent/KR20210031266A/ko not_active Ceased

-

2020

- 2020-04-29 US US16/861,802 patent/US11199975B2/en active Active

- 2020-07-14 CN CN202010676592.4A patent/CN112486866B/zh active Active

- 2020-07-15 SG SG10202006754WA patent/SG10202006754WA/en unknown

- 2020-07-15 EP EP20186037.6A patent/EP3792775A1/en active Pending

- 2020-09-11 JP JP2020152603A patent/JP7640239B2/ja active Active

-

2021

- 2021-11-29 US US17/536,506 patent/US11960728B2/en active Active

-

2025

- 2025-05-26 KR KR1020250068368A patent/KR20250085687A/ko active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009528609A (ja) | 2006-03-28 | 2009-08-06 | ノキア コーポレイション | 不揮発性メモリの読み出し待ち時間を減少させる方法及びデバイス |

| JP2010512586A (ja) | 2006-12-06 | 2010-04-22 | フュージョン マルチシステムズ,インク.(ディービイエイ フュージョン−アイオー) | 空データトークン指令を用いてストレージデバイス中のデータを管理するための装置、システム及び方法 |

| US20110219171A1 (en) | 2010-03-05 | 2011-09-08 | 248 SolidState, Inc | Virtual channel support in a nonvolatile memory controller |

| JP2012068936A (ja) | 2010-09-24 | 2012-04-05 | Toshiba Corp | メモリシステム |

| JP2013200692A (ja) | 2012-03-23 | 2013-10-03 | Toshiba Corp | メモリシステム |

| JP2018525737A (ja) | 2015-07-28 | 2018-09-06 | 華為技術有限公司Huawei Technologies Co.,Ltd. | 増大された効率のためのインテリジェントメモリアーキテクチャ |

Also Published As

| Publication number | Publication date |

|---|---|

| CN112486866A (zh) | 2021-03-12 |

| CN112486866B (zh) | 2025-03-21 |

| SG10202006754WA (en) | 2021-04-29 |

| KR20210031266A (ko) | 2021-03-19 |

| JP2021043975A (ja) | 2021-03-18 |

| US20210072902A1 (en) | 2021-03-11 |

| US11199975B2 (en) | 2021-12-14 |

| US20220083237A1 (en) | 2022-03-17 |

| KR20250085687A (ko) | 2025-06-12 |

| EP3792775A1 (en) | 2021-03-17 |

| US11960728B2 (en) | 2024-04-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6373559B2 (ja) | メモリ装置及びメモリ装置の動作方法 | |

| KR102615659B1 (ko) | 메모리 시스템 및 이의 동작 방법 | |

| US12436717B2 (en) | Memory controller and operating method thereof | |

| US11461226B2 (en) | Storage device including memory controller | |

| KR20150017599A (ko) | 반도체 메모리 장치, 그것을 포함하는 메모리 시스템 및 그것의 동작 방법 | |

| KR102012298B1 (ko) | 비휘발성 메모리 장치 및 그 구동 방법 | |

| KR20250085687A (ko) | 인터페이스 회로, 메모리 장치, 저장 장치 및 메모리 장치의 동작 방법 | |

| KR102766448B1 (ko) | 컨트롤러, 컨트롤러의 동작 방법 및 이를 포함하는 저장 장치 | |

| KR20190010335A (ko) | 레이턴시 정보를 저장하는 저장 장치, 프로세서 및 컴퓨팅 시스템 | |

| US11264086B2 (en) | Memory controller and operating method thereof | |

| KR20200071602A (ko) | 저장 장치 및 그 동작 방법 | |

| US11625178B2 (en) | Storage device and method of operating the same | |

| JP2018152112A (ja) | メモリ装置及びメモリ装置の動作方法 | |

| JP2022159991A (ja) | メモリシステム及びその動作方法 | |

| US20130173852A1 (en) | Memory system | |

| US11941294B2 (en) | Memory controller for controlling suspension of operation and method of operating the same | |

| US12153825B2 (en) | Memory controller and method of operating the same | |

| KR20240003648A (ko) | 메모리 시스템 및 그에 포함된 메모리 컨트롤러의 동작 방법 | |

| KR20220157155A (ko) | 스토리지 장치 및 그 동작 방법 | |

| US12111781B2 (en) | Data burst suspend mode using multi-level signaling | |

| US11182310B2 (en) | Priority determination circuit and method of operating the priority determination circuit for preventing overlapping operation | |

| KR102355436B1 (ko) | 데이터 저장 장치 | |

| US8971135B2 (en) | Semiconductor memory device receiving data in response to data strobe signal, memory system including the same and operating method thereof | |

| CN115083482A (zh) | 存储器装置和包括该存储器装置的存储装置 | |

| CN117055804A (zh) | 数据突发队列管理 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230705 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20240618 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240730 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20241030 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20250204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20250220 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7640239 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |