JP7128312B2 - Rram 書き込み - Google Patents

Rram 書き込み Download PDFInfo

- Publication number

- JP7128312B2 JP7128312B2 JP2021045708A JP2021045708A JP7128312B2 JP 7128312 B2 JP7128312 B2 JP 7128312B2 JP 2021045708 A JP2021045708 A JP 2021045708A JP 2021045708 A JP2021045708 A JP 2021045708A JP 7128312 B2 JP7128312 B2 JP 7128312B2

- Authority

- JP

- Japan

- Prior art keywords

- current

- time interval

- voltage

- during

- bit line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0023—Address circuits or decoders

- G11C13/0026—Bit-line or column circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0023—Address circuits or decoders

- G11C13/0028—Word-line or row circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/003—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0078—Write using current through the cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0083—Write to perform initialising, forming process, electro forming or conditioning

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0092—Write characterized by the shape, e.g. form, length, amplitude of the write pulse

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/82—Array having, for accessing a cell, a word line, a bit line and a plate or source line receiving different potentials

Landscapes

- Semiconductor Memories (AREA)

- Static Random-Access Memory (AREA)

Description

本出願は、2017年1月20日に出願された、米国特許仮出願第62448831号(RRAM用の電流制御リセット動作及びRRAMセット用の傾斜ビット線)に関し、優先権の利益を有する。

Claims (17)

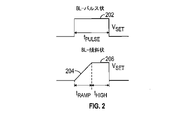

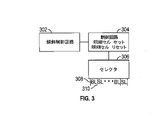

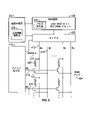

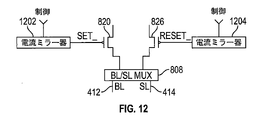

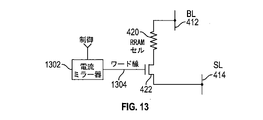

- 抵抗変化ランダムアクセスメモリ(RRAM:Resistive Random Access Memory)セルに結合されているビット線又はソース線に印加される電圧であって、セット又はリセット動作中に前記RRAMセルをセット又はリセットするための電圧を、第1の時間間隔の間に最小電圧値から最大電圧値まで上昇させることと、

前記第1の時間間隔の後の第2の時間間隔の間に前記電圧を前記最大電圧値に保持することと、

前記第2の時間間隔の後に前記電圧の印加を止めることと、を含む方法であって、

前記電圧を上昇させることは、前記RRAMセルのリセット動作中に前記ソース線への電流を更に制限する電流制限器を介して、前記RRAMセルのセット動作中に前記ビット線への電流を制限すること、を含む方法。 - 前記電圧を上昇させるために前記ビット線又は前記ソース線に供給される電流の電流制限を調整すること、を更に含む請求項1に記載の方法。

- 前記電圧を上昇させるための前記第1の時間間隔は、前記ビット線又は前記ソース線に供給される電流制限、及び前記ビット線又は前記ソース線の寄生容量に基づき、

前記電圧を上昇させること及び前記電圧を保持することは、前記RRAMセルのフィラメント構造の抵抗を調整することである、請求項1に記載の方法。 - 前記セット又はリセット動作中の前記第2の時間間隔の間に前記ビット線又は前記ソース線に印加される前記電圧を制限すること、を更に含む請求項1に記載の方法。

- 前記セット又はリセット動作中に前記ビット線又は前記ソース線に共供給源を結合すること、を更に含む請求項1に記載の方法。

- 抵抗変化ランダムアクセスメモリ(RRAM:Resistive Random Access Memory)セルに結合されているビット線又はソース線に印加される電圧であって、セット又はリセット動作中に前記RRAMセルをセット又はリセットするための電圧を、第1の時間間隔の間に最小電圧値から最大電圧値まで上昇させることと、

前記第1の時間間隔の後の第2の時間間隔の間に前記電圧を前記最大電圧値に保持することと、

前記第2の時間間隔の後に前記電圧の印加を止めることと、

前記リセット動作中に前記RRAMセルに結合されているワード線に電流ミラー器を結合すること、を含む方法。 - 抵抗変化ランダムアクセスメモリ(RRAM:Resistive Random Access Memory)セルに結合されているビット線又はソース線に印加される電圧であって、セット又はリセット動作中に前記RRAMセルをセット又はリセットするための電圧を、第1の時間間隔の間に最小電圧値から最大電圧値まで上昇させることと、

前記第1の時間間隔の後の第2の時間間隔の間に前記電圧を前記最大電圧値に保持することと、

前記第2の時間間隔の後に前記電圧の印加を止めることと、

前記セット動作中に前記RRAMセルに結合されているワード線に電流ミラー器を結合すること、を含む方法。 - 前記セット動作中に前記ビット線に共供給器を結合すること、を更に含む請求項1に記載の方法。

- 前記リセット動作中に前記ソース線に共供給器を結合すること、を更に含む請求項1に記載の方法。

- 前記セット動作中に前記ビット線に電流を供給することと、

前記リセット動作中に前記ソース線に電流を供給すること、を更に含む請求項1に記載の方法。 - 前記ソース線に供給される電流の第1の電流制限を、前記ビット線に供給される電流の第2の電流制限よりも低くなるように調整すること、を更に含む請求項1に記載の方法。

- 抵抗変化ランダムアクセスメモリ(RRAM:Resistive Random Access Memory)セルに結合されているビット線又はソース線に印加される電圧であって、セット又はリセット動作中に前記RRAMセルをセット又はリセットするための電圧を、第1の時間間隔の間に最小電圧値から最大電圧値まで上昇させることと、

前記第1の時間間隔の後の第2の時間間隔の間に前記電圧を前記最大電圧値に保持することと、

前記第2の時間間隔の後に前記電圧の印加を止めることと、

前記セット動作中の前記ビット線への電流を制限することと、

前記リセット動作中の前記ソース線への電流を制限ことと、を含む方法。 - 抵抗変化ランダムアクセスメモリ(RRAM:Resistive Random Access Memory)セルに結合されているビット線又はソース線に印加される電圧であって、セット又はリセット動作中に前記RRAMセルをセット又はリセットするための電圧を、第1の時間間隔の間に最小電圧値から最大電圧値まで上昇させることと、

前記第1の時間間隔の後の第2の時間間隔の間に前記電圧を前記最大電圧値に保持することと、

前記第2の時間間隔の後に前記電圧の印加を止めることと、

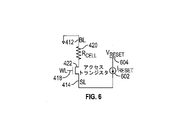

前記ビット線にセット電圧源を結合することと、

前記ソース線にリセット電流に制限された電流源を結合すること、を含む方法。 - 抵抗変化ランダムアクセスメモリ(RRAM:Resistive Random Access Memory)セルに結合されているビット線又はソース線に印加される電圧であって、セット又はリセット動作中に前記RRAMセルをセット又はリセットするための電圧を、第1の時間間隔の間に最小電圧値から最大電圧値まで上昇させることと、

前記第1の時間間隔の後の第2の時間間隔の間に前記電圧を前記最大電圧値に保持することと、

前記第2の時間間隔の後に前記電圧の印加を止めることと、

前記ビット線にセット電流に制限された電流源を結合することと、

前記ソース線にリセット電圧源を結合すること、を含む方法。 - 抵抗変化ランダムアクセスメモリ(RRAM:Resistive Random Access Memory)セルに結合されているビット線又はソース線に印加される電圧であって、セット又はリセット動作中に前記RRAMセルをセット又はリセットするための電圧を、第1の時間間隔の間に最小電圧値から最大電圧値まで上昇させることと、

前記第1の時間間隔の後の第2の時間間隔の間に前記電圧を前記最大電圧値に保持することと、

前記第2の時間間隔の後に前記電圧の印加を止めることと、

前記ビット線にセット電流に制限された電流源を結合することと、

前記ソース線にリセット電流に制限された電流源を結合すること、を含む方法。 - 前記リセット動作中に、前記ソース線に最大リセット電圧から制御された電流源を供給し、前記ビット線を接地すること、を更に含む請求項1に記載の方法。

- 前記リセット動作中に、前記ソース線にリセット電圧を印加し、前記ビット線に制御された電流源を供給すること、を更に含む請求項1に記載の方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2022130469A JP7343670B2 (ja) | 2017-01-20 | 2022-08-18 | Rram 書き込み |

| JP2023140157A JP7577809B2 (ja) | 2017-01-20 | 2023-08-30 | Rram 書き込み |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201762448831P | 2017-01-20 | 2017-01-20 | |

| US62/448,831 | 2017-01-20 | ||

| JP2019559262A JP6857257B2 (ja) | 2017-01-20 | 2017-12-19 | Rram 書き込み |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019559262A Division JP6857257B2 (ja) | 2017-01-20 | 2017-12-19 | Rram 書き込み |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022130469A Division JP7343670B2 (ja) | 2017-01-20 | 2022-08-18 | Rram 書き込み |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2021103603A JP2021103603A (ja) | 2021-07-15 |

| JP7128312B2 true JP7128312B2 (ja) | 2022-08-30 |

Family

ID=62908794

Family Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019559262A Active JP6857257B2 (ja) | 2017-01-20 | 2017-12-19 | Rram 書き込み |

| JP2021045708A Active JP7128312B2 (ja) | 2017-01-20 | 2021-03-19 | Rram 書き込み |

| JP2022130469A Active JP7343670B2 (ja) | 2017-01-20 | 2022-08-18 | Rram 書き込み |

| JP2023140157A Active JP7577809B2 (ja) | 2017-01-20 | 2023-08-30 | Rram 書き込み |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019559262A Active JP6857257B2 (ja) | 2017-01-20 | 2017-12-19 | Rram 書き込み |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022130469A Active JP7343670B2 (ja) | 2017-01-20 | 2022-08-18 | Rram 書き込み |

| JP2023140157A Active JP7577809B2 (ja) | 2017-01-20 | 2023-08-30 | Rram 書き込み |

Country Status (4)

| Country | Link |

|---|---|

| US (4) | US10998044B2 (ja) |

| JP (4) | JP6857257B2 (ja) |

| CN (2) | CN115762599A (ja) |

| WO (1) | WO2018136187A1 (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN116847662A (zh) * | 2016-11-14 | 2023-10-03 | 合肥睿科微电子有限公司 | 存储装置 |

| US10991426B2 (en) * | 2019-01-25 | 2021-04-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory device current limiter |

| US11164627B2 (en) | 2019-01-25 | 2021-11-02 | Micron Technology, Inc. | Polarity-written cell architectures for a memory device |

| DE102019132067A1 (de) | 2019-01-25 | 2020-07-30 | Taiwan Semiconductor Manufacturing Co., Ltd. | Strombegrenzer für speichervorrichtung |

| CN111986721B (zh) * | 2019-05-21 | 2025-03-21 | 华为技术有限公司 | 存储设备与写数据的方法 |

| TWI751537B (zh) | 2020-04-24 | 2022-01-01 | 華邦電子股份有限公司 | 電阻式記憶體儲存裝置及其操作方法 |

| CN113628651B (zh) * | 2020-05-06 | 2023-12-08 | 华邦电子股份有限公司 | 电阻式内存存储装置及其操作方法 |

| TWI737465B (zh) | 2020-08-27 | 2021-08-21 | 華邦電子股份有限公司 | 電阻式記憶體裝置及其操作方法 |

| WO2022226751A1 (zh) * | 2021-04-27 | 2022-11-03 | 中国科学院微电子研究所 | 忆阻器、汉明距离计算方法及存算一体集成应用 |

| EP4099327A1 (en) | 2021-06-04 | 2022-12-07 | Commissariat à l'Energie Atomique et aux Energies Alternatives | Method for programming an array of resistive memory cells |

| US12148487B2 (en) * | 2021-08-06 | 2024-11-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | High-density and high-voltage-tolerable pure core memory cell |

| US11961558B2 (en) | 2021-09-15 | 2024-04-16 | Nxp Usa, Inc. | Hidden writes in a resistive memory |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010170617A (ja) | 2009-01-22 | 2010-08-05 | Sony Corp | 抵抗変化型メモリデバイス |

| JP2012185870A (ja) | 2011-03-03 | 2012-09-27 | Panasonic Corp | 半導体記憶装置 |

| JP2013127826A (ja) | 2011-12-16 | 2013-06-27 | Sharp Corp | 可変抵抗素子の駆動方法 |

| US20130215669A1 (en) | 2010-10-29 | 2013-08-22 | Rambus Inc. | Resistance change memory cell circuits and methods |

| US20160012888A1 (en) | 2014-07-10 | 2016-01-14 | Micron Technology, Inc. | Enhancing nucleation in phase-change memory cells |

| WO2016072173A1 (ja) | 2014-11-06 | 2016-05-12 | ソニー株式会社 | 不揮発性メモリ装置、および不揮発性メモリ装置の制御方法 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4668668B2 (ja) | 2005-04-14 | 2011-04-13 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2007080311A (ja) * | 2005-09-12 | 2007-03-29 | Sony Corp | 記憶装置及び半導体装置 |

| JP2007234133A (ja) * | 2006-03-01 | 2007-09-13 | Matsushita Electric Ind Co Ltd | 半導体記憶装置及び半導体集積回路システム |

| US7457146B2 (en) * | 2006-06-19 | 2008-11-25 | Qimonda North America Corp. | Memory cell programmed using a temperature controlled set pulse |

| WO2008129774A1 (ja) * | 2007-03-13 | 2008-10-30 | Panasonic Corporation | 抵抗変化型記憶装置 |

| KR101390337B1 (ko) * | 2007-09-13 | 2014-04-29 | 삼성전자주식회사 | 멀티-레벨 상변환 메모리 장치, 그것의 프로그램 방법,그리고 그것을 포함한 메모리 시스템 |

| JP5293132B2 (ja) | 2008-12-09 | 2013-09-18 | ソニー株式会社 | 半導体装置 |

| US8199566B1 (en) * | 2009-11-23 | 2012-06-12 | Micron Technology, Inc. | Write performance of phase change memory using set-pulse shaping |

| JP5521850B2 (ja) * | 2010-07-21 | 2014-06-18 | ソニー株式会社 | 抵抗変化型メモリデバイスおよびその駆動方法 |

| US9324421B2 (en) | 2010-11-19 | 2016-04-26 | Hewlett Packard Enterprise Development Lp | Method and circuit for switching a memristive device |

| JP5598338B2 (ja) | 2011-01-13 | 2014-10-01 | ソニー株式会社 | 記憶装置およびその動作方法 |

| JP2012203962A (ja) * | 2011-03-25 | 2012-10-22 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP5266429B1 (ja) * | 2011-12-02 | 2013-08-21 | パナソニック株式会社 | クロスポイント型抵抗変化不揮発性記憶装置 |

| KR101996020B1 (ko) * | 2012-02-08 | 2019-07-04 | 삼성전자주식회사 | 가변 저항 메모리 장치 및 그것의 쓰기 방법 |

| US9165644B2 (en) * | 2012-05-11 | 2015-10-20 | Axon Technologies Corporation | Method of operating a resistive memory device with a ramp-up/ramp-down program/erase pulse |

| JP2015018590A (ja) | 2013-07-11 | 2015-01-29 | 株式会社東芝 | 再構成可能な回路およびそのプログラム方法 |

| US20150070965A1 (en) | 2013-09-12 | 2015-03-12 | Sandisk 3D Llc | FET LOW CURRENT 3D ReRAM NON-VOLATILE STORAGE |

| US10037801B2 (en) * | 2013-12-06 | 2018-07-31 | Hefei Reliance Memory Limited | 2T-1R architecture for resistive RAM |

| US9336881B2 (en) * | 2014-06-16 | 2016-05-10 | Panasonic Intellectual Property Management Co., Ltd. | Variable resistance nonvolatile memory device including a variable resistance layer that changes reversibly between a low resistance state and a high resistance state according to an applied electrical signal |

| US9548116B2 (en) * | 2014-11-26 | 2017-01-17 | Nxp Usa, Inc. | Resistive memory with program verify and erase verify capability |

| US9437292B1 (en) * | 2015-02-13 | 2016-09-06 | Taiwan Semiconductor Manufacturing Company Limited | Circuits and methods for limiting current in random access memory cells |

| US9312001B1 (en) | 2015-02-17 | 2016-04-12 | Winbond Electronics Corp. | Writing and verifying circuit for a resistive memory and method for writing and verifying a resistive memory |

| EP3257047A4 (en) * | 2015-04-15 | 2018-07-04 | Hewlett-Packard Enterprise Development LP | Resistive random access memory (rram) system |

| WO2016203397A1 (en) * | 2015-06-17 | 2016-12-22 | King Abdullah University Of Science And Technology | Compensated readout of a memristor array, a memristor array readout circuit, and method of fabrication thereof |

| US10163503B2 (en) * | 2015-11-16 | 2018-12-25 | Taiwan Semiconductor Manufacturing Co., Ltd. | RRAM array with current limiting element to enable efficient forming operation |

| US9691478B1 (en) * | 2016-04-22 | 2017-06-27 | Macronix International Co., Ltd. | ReRAM array configuration for bipolar operation |

-

2017

- 2017-12-19 US US16/462,721 patent/US10998044B2/en active Active

- 2017-12-19 CN CN202211402996.XA patent/CN115762599A/zh active Pending

- 2017-12-19 JP JP2019559262A patent/JP6857257B2/ja active Active

- 2017-12-19 WO PCT/US2017/067349 patent/WO2018136187A1/en not_active Ceased

- 2017-12-19 CN CN201780084177.6A patent/CN110226203B/zh active Active

-

2020

- 2020-08-03 US US16/984,043 patent/US11238930B2/en active Active

-

2021

- 2021-03-19 JP JP2021045708A patent/JP7128312B2/ja active Active

- 2021-11-29 US US17/536,386 patent/US11682457B2/en active Active

-

2022

- 2022-08-18 JP JP2022130469A patent/JP7343670B2/ja active Active

-

2023

- 2023-06-02 US US18/205,417 patent/US12327587B2/en active Active

- 2023-08-30 JP JP2023140157A patent/JP7577809B2/ja active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010170617A (ja) | 2009-01-22 | 2010-08-05 | Sony Corp | 抵抗変化型メモリデバイス |

| US20130215669A1 (en) | 2010-10-29 | 2013-08-22 | Rambus Inc. | Resistance change memory cell circuits and methods |

| JP2012185870A (ja) | 2011-03-03 | 2012-09-27 | Panasonic Corp | 半導体記憶装置 |

| JP2013127826A (ja) | 2011-12-16 | 2013-06-27 | Sharp Corp | 可変抵抗素子の駆動方法 |

| US20160012888A1 (en) | 2014-07-10 | 2016-01-14 | Micron Technology, Inc. | Enhancing nucleation in phase-change memory cells |

| WO2016072173A1 (ja) | 2014-11-06 | 2016-05-12 | ソニー株式会社 | 不揮発性メモリ装置、および不揮発性メモリ装置の制御方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP7343670B2 (ja) | 2023-09-12 |

| JP6857257B2 (ja) | 2021-04-14 |

| US12327587B2 (en) | 2025-06-10 |

| US11682457B2 (en) | 2023-06-20 |

| US11238930B2 (en) | 2022-02-01 |

| JP2022172165A (ja) | 2022-11-15 |

| US20190371399A1 (en) | 2019-12-05 |

| US20220084593A1 (en) | 2022-03-17 |

| JP7577809B2 (ja) | 2024-11-05 |

| JP2021103603A (ja) | 2021-07-15 |

| CN115762599A (zh) | 2023-03-07 |

| WO2018136187A1 (en) | 2018-07-26 |

| CN110226203A (zh) | 2019-09-10 |

| US20230307045A1 (en) | 2023-09-28 |

| US20210012838A1 (en) | 2021-01-14 |

| US10998044B2 (en) | 2021-05-04 |

| JP2023160881A (ja) | 2023-11-02 |

| CN110226203B (zh) | 2022-12-09 |

| JP2020507880A (ja) | 2020-03-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7128312B2 (ja) | Rram 書き込み | |

| CN109906482B (zh) | 包含存储器单元的设备及其操作方法 | |

| US8767449B2 (en) | Memory devices with in-bit current limiters | |

| EP3588504B1 (en) | Apparatuses and methods for bi-directional access of cross-point arrays | |

| JP4264432B2 (ja) | プログラム可能な抵抗メモリ素子のプログラミング | |

| US10783961B2 (en) | Memory cells, memory systems, and memory programming methods | |

| KR100738092B1 (ko) | 상전이 메모리 소자의 멀티-비트 동작 방법 | |

| US9208865B2 (en) | Resistance-change memory | |

| US11011229B2 (en) | Memory systems and memory programming methods | |

| US8248836B2 (en) | Non-volatile memory cell stack with dual resistive elements | |

| JP6653488B2 (ja) | 抵抗変化型不揮発性記憶素子のフォーミング方法および抵抗変化型不揮発性記憶装置 | |

| TWI397924B (zh) | 非揮發性記憶體中控制脈衝操作的方法和非揮發性記憶體 | |

| KR20170096172A (ko) | 고속 확산성 금속 원자에 기반한 부성 미분 저항(ndr) 디바이스 | |

| US9001552B1 (en) | Programming a RRAM method and apparatus | |

| WO2014043137A1 (en) | Resistive devices and methods of operation thereof | |

| Cabrini et al. | Algorithms to Survive: Programming Operation in Non-Volatile Memories |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210319 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210319 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20220323 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220329 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220629 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20220719 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20220818 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7128312 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |