JP6972575B2 - 周波数特性調整回路、これを用いた光送信モジュール、及び光トランシーバ - Google Patents

周波数特性調整回路、これを用いた光送信モジュール、及び光トランシーバ Download PDFInfo

- Publication number

- JP6972575B2 JP6972575B2 JP2017030312A JP2017030312A JP6972575B2 JP 6972575 B2 JP6972575 B2 JP 6972575B2 JP 2017030312 A JP2017030312 A JP 2017030312A JP 2017030312 A JP2017030312 A JP 2017030312A JP 6972575 B2 JP6972575 B2 JP 6972575B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- current

- optical

- signal

- drive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Optical Modulation, Optical Deflection, Nonlinear Optics, Optical Demodulation, Optical Logic Elements (AREA)

- Optical Communication System (AREA)

Description

前記駆動回路の出力に接続されるキャパシタと、

前記駆動回路で生成される電圧によって制御される電流供給回路と、を有し、

前記電流供給回路は、前記駆動回路から受け取る電圧に応じて異なる電流値の電流を前記光回路素子に供給する。

η=(RL+RS+RM)/(RL+RS+RM+RF)

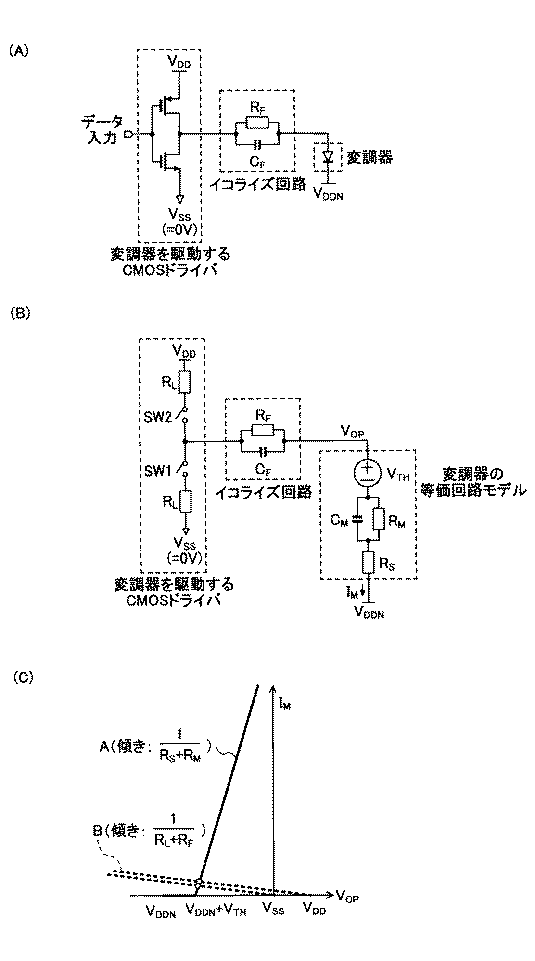

として、イコライズ回路のないとき(RF=0すなわちη=1)とイコライズ回路を挿入したとき(η<1)を比較する。式(3)の右辺で乗算される最初の項のRM/(RL+RS+RM+RF)が低周波領域の利得を決める項であり、CMRM(RL+RS)/(RL+RS+RM+RF)が帯域を決める項である。

IM(VM1)=I1 (4)

IM(VM2)=I2 (5)

Q1−CF(Vss-VM1)=Q2−CF(VDD-VM2) (6)

である。ここで、Q1は、光変調器13に電圧VM1がかかるときの容量CMの電荷量である(Q1=QM(VM1))。Q2は、光変調器13に電圧VM2がかかるときの容量CMの電荷量である(Q2=QM(VM2))。CF(Vss-VM1)は駆動回路11で電圧Vssが選択されたときのキャパシタ12の電荷量、CF(VDD-VM1)は駆動回路11で電圧VDDが選択されたときのキャパシタ12の電荷量である。

IM(VM01)=IM1+IL2 (8)

IM(VM10)=IM2+IL1 (9)

IM(VM11)=IM2+IL2 (10)

Q00−CFL(VSS-VM00)−CFM(VSS-VM00)

≒Q00−CFL(VDD-VM01)−CFM(VSS-VM01)

≒Q00−CFL(VSS-VM10)−CFM(VDD-VM10)

≒Q00−CFL(VDD-VM11)−CFM(VDD-VM11) (11)

ここで変調器の電流-電圧特性をIM(VM)は、マッハツェンダ型光変調器13Dの電流−電圧特性である。

IM(VM00)=I00 (12)

IM(VM01)=I00+(I01−I00)=I01 (13)

IM(VM10)=I00+(I01−I00)+(I10−I01)=I10 (14)

IM(VM11)=I00+(I01−I00)+(I10−I01)+(I11−I10)=I11

(15)

Q00−CF1(VSS−VM00)−CF2(VSS−VM00)−CF3(VSS−VM00)

=Q01−CF1(VDD−VM01)−CF2(VSS−VM01)−CF3(VSS−VM01)

=Q10−CF1(VDD−VM10)−CF2(VDD−VM10)−CF3(VSS−VM10)

=Q11−CF1(VDD−VM11)−CF12(VDD−VM11)−CF3(VDD−VM11)

(16)

である。

<周波数特性調整回路から供給される電流の制御>

次に、周波数特性調整回路10から供給される電流I1及び電流I2の制御について説明する。電流I1と電流I2の制御は、上述した実施例1〜7のいずれにも適用される。

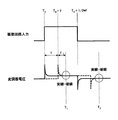

図21は、周波数特性調整回路10から光回路素子に供給される電流がずれた場合の現象を説明する図である。上段は、中間周波数領域より低い周期で交互に「0」と「1」が切り替わる信号を駆動回路11に入力したときの入力波形、下段は、上段の信号が駆動回路11へ入力されたときに光変調器13に加わる電圧の波形を示す。ここでは、光変調器13は、周波数特性調整回路10から光変調器13に供給される電流が、上述した式(4)と式(5)の条件通り供給されれば設計通りの性能を示すが、

IM(VM1)=I1 (4)

IM(VM2)=I2 (5)

周波数特性調整回路10から光変調器13に供給される電流がI1ではなくI1'になった場合、またはI2ではなくI2'になった場合を考える。図21のパターン(A)は、I1'=I1かつI2'=I2のときの駆動回路入力と光変調器の電圧波形を示す。

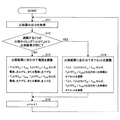

T1>T0+τ+τ1、かつ

T1+τ2<T0+1/(2*f)

という条件が導かれる。この2つの条件式から、

τ<1/(2*f)−τ1−τ2

が導かられる。したがって、波形比較のために、電圧波形をシフトさせる遅延時間τは、τ<1/(2*f)−τ1−τ2を満たすように設定される。

<光トランシーバへの適用>

<電流制御の変形例1>

<電流制御の変形例2>

以上の実施の形態に関し、さらに以下の付記を開示する。

(付記1)

光回路素子と前記光回路素子を駆動する駆動回路の間に配置される回路であって、

前記駆動回路の出力に接続されるキャパシタと、

前記駆動回路で生成される電圧によって制御される電流供給回路と、

を有し、

前記電流供給回路は、前記駆動回路から受け取る電圧に応じて異なる電流値の電流を前記光回路素子に供給する、

ことを特徴とする周波数特性調整回路。

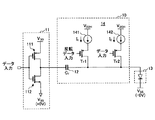

(付記2)

前記電流供給回路は、第1の電流を生成する第1の電流源と、前記第1の電流と異なる第2の電流を生成する第2の電流源と、を有し、

前記駆動回路から第1レベルの電圧が印加されたときに前記第1の電流を供給し、前記駆動回路から第2レベルの電圧が印加されたときに前記第2の電流を供給することを特徴とする付記1に記載の周波数特性調整回路。

(付記3)

前記電流供給回路は、第1の電流を生成する第1の電流源と、差電流を生成する第2の電流源と、を有し、

前記駆動回路から第1レベルの電圧を受け取ったときに前記第1の電流を供給し、前記駆動回路から第2レベルの電圧を受け取ったときに前記第1の電流と前記差電流を足し合わせた第2の電流を供給することを特徴とする付記1に記載の周波数特性調整回路。

(付記4)

前記電流供給回路は、前記第1の電流源と前記キャパシタの間に接続される第1スイッチと、前記第2の電流源と前記キャパシタの間に接続される第2スイッチを有し、

前記第1スイッチと前記第2スイッチは、前記駆動回路の出力に接続されていることを特徴とする付記2または3に記載の周波数特性調整回路。

(付記5)

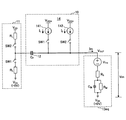

光回路素子を駆動するn個の駆動回路に対応して設けられるn個の付記1〜4のいずれか1項に記載の周波数特性調整回路、

を有し、

i番目の駆動回路の出力をVi、

前記i番目の駆動回路に対応するi番目の周波数特性調整回路が供給する電流をIi、前記i番目の周波数特性調整回路が有するキャパシタのキャパシタンスをCFiとしたときに、

前記光回路素子の電流-電圧特性をIM(VM)、前記光回路素子の電荷-電圧特性をQM(VM)、IM(VM)=ΣIiとするとき、すべてのVi、Iiの組み合わせに対して、

QM(VM)−CFi(Vi-VMi)

が等価となる、または近似するように設定されていることを特徴とする周波数特性調整回路。

(付記6)

電気信号に基づいて光信号を出力する光回路素子と、

前記光回路素子を駆動する駆動回路と、

前記光回路素子と前記駆動回路の間に配置される周波数特性調整回路であって、前記駆動回路の出力に接続されるキャパシタと、前記駆動回路で生成される電圧によって制御される電流供給回路とを有し、前記駆動回路から受け取る電圧に応じて異なる電流値の電流を前記光回路素子に供給する周波数特性調整回路と、

を有する光送信モジュール。

(付記7)

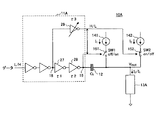

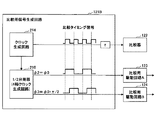

前記周波数特性調整回路の電流条件をモニタするモニタ回路と、

前記モニタ回路の出力基づいて、前記周波数特性調整回路から前記光回路素子に供給される前記電流値を調整する制御回路と、

を有することを特徴とする付記6に記載の光送信モジュール。

(付記8)

前記モニタ回路は、

前記光回路素子と同等の性能を有する1組のダミー光回路素子と、

前記ダミー光回路素子への入力駆動波形を比較する比較器と、

前記ダミー光回路素子を駆動する1組の比較用駆動回路と、

前記比較器に供給されるタイミング信号と、前記比較用駆動回路の一方に供給される基準信号と、前記比較用駆動回路の他方に供給され前記基準信号から所定時間遅延されたシフト信号を生成する信号生成回路と、

を有することを特徴とする付記7に記載の光送信モジュール。

(付記9)

前記制御回路は、前記比較器の出力が連続する2つの比較タイミングで異なる結果を示す場合に、前記周波数特性調整回路から前記光回路素子に供給される電流値を調整することを特徴とする付記8に記載の光送信モジュール。

(付記10)

前記制御回路は、前記比較器の出力が連続する2つの比較タイミングで同じ結果を示す場合に、前記比較器の入力オフセット電圧を調整することを特徴とする付記8に記載の光送信モジュール。

(付記11)

前記モニタ回路は、

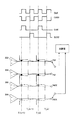

前記光回路素子と同等の性能を有する第1〜第4のダミー光回路素子と、

前記第1〜第4のダミー光回路素子を駆動する第1〜第4の比較用駆動回路と、

第1のダミー光回路素子に入力される電圧波形と第2のダミー光回路素子に入力される電圧波形を差動増幅する第1の差動増幅器と、

第3のダミー光回路素子に入力される電圧波形と第4のダミー光回路素子に入力される電圧波形を差動増幅する第2の差動増幅器と

を有し、

前記信号生成回路は、前記基準信号を反転した反転基準信号と、前記シフト信号を反転した反転シフト信号をさらに生成し、

前記基準信号による駆動波形が前記第1のダミー光回路素子に入力され、前記シフト信号による駆動波形が前記第2のダミー光回路素子に入力され、前記反転基準信号による駆動波形が前記第3のダミー光回路素子に入力され、前記反転シフト信号による駆動波形が前記第4のダミー光回路素子に入力され、

前記比較器は、前記第1の差動増幅器の出力と、前記第2の差動増幅器の出力の比較結果を出力することを特徴とする付記8に記載の光送信モジュール。

(付記12)

前記基準信号は第1の固定電位信号であり、前記反転基準信号は前記第1の固定電位信号と異なる第2の固定電位信号であり、

前記モニタ回路は、第3の差動増幅器と第4の差動増幅器をさらに有し、

前記第1の差動増幅器は、前記第1の固定電位信号により駆動される第1のダミー光回路素子の入力波形と、前記シフト信号により駆動される第2のダミー光回路素子の入力波形を差動増幅し、

前記第2の差動増幅器は、前記第2の固定電位信号により駆動される第3のダミー光回路素子の入力波形と、前記反転シフト信号により駆動される第4のダミー光回路素子の入力波形を差動増幅し、

前記第3の差動増幅器は、前記第2の固定電位信号により駆動される第3のダミー光回路素子の入力波形と、前記シフト信号により駆動される第2のダミー光回路素子の入力波形を差動増幅し、

前記第4の差動増幅器は、前記第1の固定電位信号により駆動される第4のダミー光回路素子の入力波形と、前記反転シフト信号により駆動される第4のダミー光回路素子の入力波形を差動増幅し、

前記比較器は、前記第1の差動増幅器の出力と前記第2の差動増幅器の出力の比較結果を第1の時間に出力し、前記第3の差動増幅器の出力と前記第4の差動増幅器の出力の比較結果を第2の時間に出力することを特徴とする付記11に記載の光送信モジュール。

(付記13)

前記比較器は、

前記第1の差動増幅器の出力と前記第2の差動増幅器の出力を比較して前記第1の時間に第1比較結果を出力する第1比較器と、

前記第3の差動増幅器の出力と前記第4の差動増幅器の出力を比較して前記第2の時間に第2比較結果を出力する第2比較器と、

を有することを特徴とする付記12に記載の光送信モジュール。

(付記14)

前記比較器は、前記第1の時間に前記第1の差動増幅器の出力と前記第2の差動増幅器の出力を選択し、前記第2の時間に前記第3の差動増幅器の出力と前記第4の差動増幅器の出力を選択するスイッチ部を有することを特徴とする付記12に記載の光送信モジュール。

(付記15)

駆動回路と前記駆動回路の出力に接続されるキャパシタの組を複数有し、

複数の組の少なくとも一部において、前記駆動回路の出力がアクティブと高インピーダンスの間で選択可能であることを特徴とする付記6〜14のいずれか1項に記載の光送信モジュール。

(付記16)

前記駆動回路の入力にはデータ信号と制御信号が接続され、前記駆動回路は前記制御信号の値に応じて、入力された前記データ信号の値を出力するか、または出力状態が高インピーダンスとなることを特徴とする付記15に記載の光送信モジュール。

(付記17)

付記6〜16のいずれか1項に記載の光送信モジュールと、

光受信モジュールと、

を有する光トランシーバ。

2、2A、2B、302、302A〜302C 光送信モジュール

3 光受信モジュール

9 制御回路

10、10A、10B、10C、10D、10E、10F、10G 周波数特性調整回路

11、11A 駆動回路

12−1、12−2 キャパシタ

13、13B、13C、13D、13F 光変調器(光回路素子)

13A レーザダイオード(光回路素子)

30、330A、330B、330C 電流条件モニタ回路(モニタ回路)

40 LD(光源)

121、321A、321B、321C、 比較用信号生成回路

122、322A、322B−1、322B−2、322C 比較器

123、124、323、324 比較用駆動回路

125、126、325、326 比較用の周波数特性調整回路

127,128、327、328 ダミー光変調器

141、147、148,241 第1の電流源

142,149、242 第2の電流源

201−1〜201−m、203−1〜203−m 出力状態可変バッファ(駆動回路)

214 クロック生成回路

331、332、333、334、335、336 差動増幅器

CF1−1〜CFm−1、CF1−2〜CFm−2、 キャパシタ

S1〜Sm 制御信号

τ1、τ2、τ3 遅延回路

Claims (12)

- 光回路素子と前記光回路素子を駆動する駆動回路の間に配置される回路であって、

前記駆動回路の出力に接続されるキャパシタと、

前記駆動回路で生成される電圧によって制御される電流供給回路と、

を有し、

前記電流供給回路は、前記駆動回路から受け取る電圧値に応じて異なる電流値の電流を選択的に前記光回路素子に供給し、

前記電流供給回路は、第1の電流を生成する第1の電流源と、前記第1の電流と異なる第2の電流を生成する第2の電流源と、を有し、

前記駆動回路から第1レベルの電圧が印加されたときに前記第1の電流を供給し、前記駆動回路から第2レベルの電圧が印加されたときに前記第2の電流を供給することを特徴とする周波数特性調整回路。 - 光回路素子と前記光回路素子を駆動する駆動回路の間に配置される回路であって、

前記駆動回路の出力に接続されるキャパシタと、

前記駆動回路で生成される電圧によって制御される電流供給回路と、

を有し、

前記電流供給回路は、前記駆動回路から受け取る電圧値に応じて異なる電流値の電流を選択的に前記光回路素子に供給し、

前記電流供給回路は、第1の電流を生成する第1の電流源と、差電流を生成する第2の電流源と、を有し、

前記駆動回路から第1レベルの電圧を受け取ったときに前記第1の電流を供給し、前記駆動回路から第2レベルの電圧を受け取ったときに前記第1の電流と前記差電流を足し合わせた第2の電流を供給することを特徴とする周波数特性調整回路。 - 前記電流供給回路は、前記第1の電流源と前記キャパシタの間に接続される第1スイッチと、前記第2の電流源と前記キャパシタの間に接続される第2スイッチを有し、

前記第1スイッチと前記第2スイッチは、前記駆動回路の出力に接続されていることを特徴とする請求項1または2に記載の周波数特性調整回路。 - 光回路素子を駆動するn個の駆動回路に対応して設けられるn個の請求項1〜3のいずれか1項に記載の周波数特性調整回路、

を有し、

i番目の駆動回路の出力をVi、

前記i番目の駆動回路に対応するi番目の周波数特性調整回路が供給する電流をIi、前記i番目の周波数特性調整回路が有するキャパシタのキャパシタンスをCFiとしたときに、

前記光回路素子の電流-電圧特性をIM(VM)、前記光回路素子の電荷-電圧特性をQM(VM)、IM(VM)=ΣIiとするとき、すべてのVi、Iiの組み合わせに対して、

QM(VM)−CFi(Vi-VMi)

が等価となる、または近似するように設定されていることを特徴とする周波数特性調整回路。 - 電気信号に基づいて光信号を出力する光回路素子と、

前記光回路素子を駆動する駆動回路と、

前記光回路素子と前記駆動回路の間に配置される周波数特性調整回路であって、前記駆動回路の出力に接続されるキャパシタと、記駆動回路で生成される電圧によって制御される電流供給回路とを有し、前記電流供給回路は、前記駆動回路から受け取る電圧値に応じて異なる電流値の電流を選択的に前記光回路素子に供給する周波数特性調整回路と、

を有し、

前記電流供給回路は、第1の電流を生成する第1の電流源と、前記第1の電流と異なる第2の電流を生成する第2の電流源と、を有し、前記駆動回路から第1レベルの電圧が印加されたときに前記第1の電流を供給し、前記駆動回路から第2レベルの電圧が印加されたときに前記第2の電流を供給する、

光送信モジュール。 - 電気信号に基づいて光信号を出力する光回路素子と、

前記光回路素子を駆動する駆動回路と、

前記光回路素子と前記駆動回路の間に配置される周波数特性調整回路であって、前記駆動回路の出力に接続されるキャパシタと、記駆動回路で生成される電圧によって制御される電流供給回路とを有し、前記電流供給回路は、前記駆動回路から受け取る電圧値に応じて異なる電流値の電流を選択的に前記光回路素子に供給する周波数特性調整回路と、

を有し、

前記電流供給回路は、第1の電流を生成する第1の電流源と、差電流を生成する第2の電流源と、を有し、前記駆動回路から第1レベルの電圧を受け取ったときに前記第1の電流を供給し、前記駆動回路から第2レベルの電圧を受け取ったときに前記第1の電流と前記差電流を足し合わせた第2の電流を供給する、

光送信モジュール。 - 電気信号に基づいて光信号を出力する光回路素子と、

前記光回路素子を駆動する駆動回路と、

前記光回路素子と前記駆動回路の間に配置される周波数特性調整回路であって、前記駆動回路の出力に接続されるキャパシタと、記駆動回路で生成される電圧によって制御される電流供給回路とを有し、前記電流供給回路は、前記駆動回路から受け取る電圧値に応じて異なる電流値の電流を選択的に前記光回路素子に供給する周波数特性調整回路と、

前記周波数特性調整回路の電流条件をモニタするモニタ回路と、

前記モニタ回路の出力基づいて、前記周波数特性調整回路から前記光回路素子に供給される前記電流値を調整する制御回路と、

を有することを特徴とする光送信モジュール。 - 前記モニタ回路は、

前記光回路素子と同等の性能を有する1組のダミー光回路素子と、

前記ダミー光回路素子への入力駆動波形を比較する比較器と、

前記ダミー光回路素子を駆動する1組の比較用駆動回路と、

前記比較器に供給されるタイミング信号と、前記比較用駆動回路の一方に供給される基準信号と、前記比較用駆動回路の他方に供給され前記基準信号から所定時間遅延されたシフト信号を生成する信号生成回路と、

を有することを特徴とする請求項7に記載の光送信モジュール。 - 前記制御回路は、前記比較器の出力が連続する2つの比較タイミングで異なる結果を示す場合に、前記周波数特性調整回路から前記光回路素子に供給される電流値を調整することを特徴とする請求項8に記載の光送信モジュール。

- 前記制御回路は、前記比較器の出力が連続する2つの比較タイミングで同じ結果を示す場合に、前記比較器の入力オフセット電圧を調整することを特徴とする請求項8に記載の光送信モジュール。

- 前記モニタ回路は、

前記光回路素子と同等の性能を有する第1〜第4のダミー光回路素子と、

前記第1〜第4のダミー光回路素子を駆動する第1〜第4の比較用駆動回路と、

第1のダミー光回路素子に入力される電圧波形と第2のダミー光回路素子に入力される電圧波形を差動増幅する第1の差動増幅器と、

第3のダミー光回路素子に入力される電圧波形と第4のダミー光回路素子に入力される電圧波形を差動増幅する第2の差動増幅器と

を有し、

前記信号生成回路は、前記基準信号を反転した反転基準信号と、前記シフト信号を反転した反転シフト信号をさらに生成し、

前記基準信号による駆動波形が前記第1のダミー光回路素子に入力され、前記シフト信号による駆動波形が前記第2のダミー光回路素子に入力され、前記反転基準信号による駆動波形が前記第3のダミー光回路素子に入力され、前記反転シフト信号による駆動波形が前記第4のダミー光回路素子に入力され、

前記比較器は、前記第1の差動増幅器の出力と、前記第2の差動増幅器の出力の比較結果を出力することを特徴とする請求項8に記載の光送信モジュール。 - 駆動回路と前記駆動回路の出力に接続されるキャパシタの組を複数有し、

複数の組の少なくとも一部において、前記駆動回路の出力がアクティブと高インピーダンスの間で選択可能であることを特徴とする請求項5〜11のいずれか1項に記載の光送信モジュール。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/649,689 US10720996B2 (en) | 2016-08-19 | 2017-07-14 | Frequency characteristic adjustment circuit, optical transmission module using the same, and optical transceiver |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016161501 | 2016-08-19 | ||

| JP2016161501 | 2016-08-19 | ||

| JP2016223938 | 2016-11-17 | ||

| JP2016223938 | 2016-11-17 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018085708A JP2018085708A (ja) | 2018-05-31 |

| JP6972575B2 true JP6972575B2 (ja) | 2021-11-24 |

Family

ID=62237366

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017030312A Active JP6972575B2 (ja) | 2016-08-19 | 2017-02-21 | 周波数特性調整回路、これを用いた光送信モジュール、及び光トランシーバ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6972575B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6904291B2 (ja) * | 2018-03-20 | 2021-07-14 | 日本電信電話株式会社 | Dmlドライバ |

| TWI678068B (zh) * | 2018-10-22 | 2019-11-21 | 立積電子股份有限公司 | 射頻訊號放大裝置和射頻前端模組 |

| JP7600822B2 (ja) * | 2021-03-30 | 2024-12-17 | 富士通オプティカルコンポーネンツ株式会社 | 光送信装置、光変調器及び起動方法 |

| CN114095106B (zh) * | 2021-11-19 | 2023-05-16 | 北京邮电大学 | 一种针对pam4互连系统信道环境损伤影响的检测方法 |

| CN115001456A (zh) * | 2022-07-14 | 2022-09-02 | 上海嘉楠捷思信息技术有限公司 | 动态锁存器、数据运算单元、芯片、算力板及计算设备 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5739593A (en) * | 1980-08-22 | 1982-03-04 | Nec Corp | Driving circuit of semiconductor light emitting element |

| JPH03201633A (ja) * | 1989-12-27 | 1991-09-03 | Sumitomo Electric Ind Ltd | 半導体レーザの変調回路 |

| JP4506640B2 (ja) * | 2005-10-19 | 2010-07-21 | 住友電気工業株式会社 | 半導体レーザ駆動回路 |

| JP5509662B2 (ja) * | 2009-04-13 | 2014-06-04 | ソニー株式会社 | レーザ駆動装置 |

| CN101752786B (zh) * | 2010-01-08 | 2011-09-07 | 江苏奥雷光电有限公司 | 一种激光器的激光驱动方法 |

| JP2013084839A (ja) * | 2011-10-12 | 2013-05-09 | Sony Corp | 半導体レーザー駆動回路及び半導体レーザー装置 |

| US9153936B2 (en) * | 2013-06-20 | 2015-10-06 | Fujitsu Limited | Power-efficient high-speed driver for a vertical-cavity surface-emitting laser |

| JP6295778B2 (ja) * | 2014-03-28 | 2018-03-20 | 富士通株式会社 | 光半導体装置及び駆動回路の制御方法 |

| US9991965B2 (en) * | 2014-10-28 | 2018-06-05 | Mellanox Technologies Denmark Aps | Driver circuit for an electro-absorption or micro-ring modulator and optical transmitter comprising such driver circuit |

-

2017

- 2017-02-21 JP JP2017030312A patent/JP6972575B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018085708A (ja) | 2018-05-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6972575B2 (ja) | 周波数特性調整回路、これを用いた光送信モジュール、及び光トランシーバ | |

| US10164713B2 (en) | Optical transmitter, optical modulator module, and optical transmission system | |

| US10720996B2 (en) | Frequency characteristic adjustment circuit, optical transmission module using the same, and optical transceiver | |

| US20120045218A1 (en) | Driver and optical transmission apparatus | |

| JP4983466B2 (ja) | 光変調装置および光変調方法ならびに光送信装置 | |

| JPH07183852A (ja) | 光ファイバ伝送装置 | |

| KR102346718B1 (ko) | 광 송수신기 | |

| US7474858B2 (en) | Duobinary optical transmission device using at least one semiconductor optical amplifier | |

| US8325410B2 (en) | Modulation system and method for generating a return-to-zero (RZ) optical data signal | |

| JP5488331B2 (ja) | 駆動回路、光送信装置、駆動方法および光送信方法 | |

| US10642076B2 (en) | Drive circuit | |

| US20160352372A1 (en) | Low power buffer with gain boost | |

| EP3574585B1 (en) | Threshold adjustment compensation of asymmetrical optical noise | |

| US20210135761A1 (en) | Transmission device, optical transceiver module, and optical modulation method | |

| EP2797231B1 (en) | Mismatched differential circuit | |

| US20070116476A1 (en) | Method and apparatus for generating optical duo binary signals with frequency chirp | |

| US7193539B2 (en) | Precoder and optical duo-binary transmission apparatus using the same | |

| US20130177325A1 (en) | Method and Apparatus of Automatic Power Control for Burst Mode Laser Transmitter | |

| JP2010109512A (ja) | ドライバ回路及びドライバic | |

| Kern et al. | 18gb/s optical io: Vcsel driver and tia in 90nm cmos | |

| JP2020122872A (ja) | 光変調器駆動回路 | |

| US20240014905A1 (en) | Optical transmitter that includes optical modulator | |

| KR101138630B1 (ko) | 듀오바이너리 수신기 | |

| US20050265733A1 (en) | Method and apparatus for RZ-DPSK optical signal generation | |

| US20060193230A1 (en) | System and method for generating optical return-to-zero signals with differential bi-phase shift |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20191112 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20200825 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200915 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201016 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210330 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210511 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20211005 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20211018 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6972575 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |