本発明に係る1つの実施形態は、複数の画素を含む撮像装置である。各画素は、光電変換部と、光電変換部で生じた電荷に基づく信号を読み出すための画素回路とを含む。本実施形態の撮像装置は、画素回路が配された基板と、当該基板の上に配された半導体層とを含む。半導体層は、光を受ける第1部分と、遮光された第2部分(電荷保持領域)とを含む。撮像装置は、さらに、第1部分と第2部分とに対して互いに独立にバイアス電圧を印加するバイアス電圧供給部を備える。

第1部分と第2部分とに対して互いに独立にバイアス電圧を印加するバイアス電圧供給部を備える構成によれば、第1部分を受光領域として用い、第2部分を電荷保持領域として用いることができる。そのため、以下に挙げる効果の少なくとも1つを得ることができる。なお、信号を電荷保持領域に保持させるための方法は特に限定されない。例えば、受光領域に生じた信号電荷を電荷保持領域に転送することができる。あるいは、信号電荷に基づく受光領域の電位変化を容量結合などにより伝達することができる。

半導体層の中に、光を受ける受光領域の他に、電荷を保持する電荷保持領域が配されるため、露光期間の終了から信号を読み出すまでの間、露光期間に生じた信号電荷に基づく信号を電荷保持領域に保持することができる。したがって、このような構成によれば、グローバル電子シャッタ動作を行う場合などに、相関二重サンプリング(Correlated Double Sampling、以下CDS)などのノイズ低減処理を容易に行うことができる。結果として、ノイズを低減することができる。なお、グローバル電子シャッタ動作は、複数の画素において同一の露光期間で電荷を蓄積し、その後、複数の画素から順に信号を読み出す動作の一例である。

また、電荷保持領域は遮光されるため、電荷保持領域が信号電荷を保持している間に光電変換により生じた電荷が電荷保持領域に混入することを抑制できる。結果として、ノイズを低減することができる。

半導体層においては、暗電流を低減する技術を適用することができる。したがって、半導体層に電荷保持領域が配されるため、信号電荷を保持している間にノイズの原因となる電荷が混入することを抑制できる。

別の形態としては、第1部分を受光領域として用い、第2部分をOB(Optical Black)領域として用いることができる。そのため、受光領域からの信号とOB領域からの信号との差分処理を行うことで、暗電流などによるノイズを除去することができる。結果として、ノイズの少ない撮像信号を得ることができる。

以下では、本発明の実施例について図面を用いて詳細に説明する。本発明は以下に説明される実施例のみに限定されない。本発明の趣旨を超えない範囲で以下に説明される実施例の一部の構成が変更された変形例も、本発明の実施例である。また、以下のいずれかの実施例の一部の構成を、他の実施例に追加した例、あるいは他の実施例の一部の構成と置換した例も本発明の実施例である。

本発明に係る実施例を説明する。図1(a)に本実施例の撮像装置の画素100の概略図を示す。撮像装置は、画素100の画素回路が配された基板(不図示)と当該基板の上に配された半導体層108を備える。図1(a)は1つの画素100だけを示しているが、本実施例の撮像装置は複数の画素100を含む。

画素100は、半導体層108に配された、受光領域101、電荷転送領域102、および、電荷保持領域103を含む。つまり、受光領域101は半導体層108の第1部分であり、電荷保持領域103は半導体層108の第2部分である。半導体層108は、シリコンなどの無機半導体で構成されうる。あるいは、半導体層108は有機半導体により構成されうる。

半導体層108の上には、受光領域101、電荷転送領域102、および、電荷保持領域103に対してバイアス電圧を印加する上部電極S106が配される。上部電極S106は電源VS104に接続される。電源VS104は、電圧Vsを供給する。本実施例では、上部電極S106が受光領域101および電荷保持領域103の両方にバイアス電圧を印加する。そのため、上部電極S106は、受光領域101の上、および、電荷保持領域103の上に連続して延在した導電層によって構成される。別の観点で言えば、上部電極S106の第1の部分(第1の電極)が受光領域101にバイアス電圧を印加し、上部電極S106の第2の部分(第3の電極)が、電荷保持領域103にバイアス電圧を印加する。なお、上部電極S106の第1の部分(第1の電極)と第2の部分(第3の電極)とは互いに分離されていてもよい。

画素100は、さらに、受光領域101にバイアス電圧を印加する電極P(第2の電極)110と、電極P110に接続された電源VP113を含む。電源VP113は電圧Vpを供給する。画素100は、さらに、電荷保持領域103にバイアス電圧を印加する電極M(第4の電極)112を含む。上部電極S106の第1の部分(第1の電極)と電極P110との間に、半導体層108の受光領域101が配される。上部電極S106の第2の部分(第3の電極)と電極M112との間に、半導体層108の電荷保持領域103が配される。

電極P110と、電極M112とには、互いに電気的に分離されている。このような構成により、受光領域101と電荷保持領域103とに互いに独立してバイアス電圧を印加することができる。本実施例においては、電極P110および電極M112が、半導体層108の受光領域(第1部分)101と電荷保持領域(第2部分)103とに対し、互いに独立にバイアス電圧を印加するバイアス電圧供給部を構成する。なお、受光領域101と電荷保持領域103とに互いに独立してバイアス電圧を印加しない場合は、電極P110と電極M112とが連続して構成されてもよい。また、電荷保持領域103にバイアス電圧を印加しない場合は、電極M112を省略することができる。

上部電極S106は所定の量の光を透過させるように構成される。例えば、透明な導電材料であるITO(Indium Tin Oxide)層や薄膜化された金属層が上部電極S106に用いられる。つまり、受光領域101は光を受けるように構成される。本実施例では、電荷転送領域102の上、および、電荷保持領域103の上に、入射光を遮る遮光層105が配される。つまり、電荷保持領域103は遮光されている。電荷転送領域102の上に遮光層105の一部が配されることにより、電荷転送中に電荷転送領域102で電荷が発生することを抑制できる。これによりノイズを低減することができる。また、電荷保持領域103の上に遮光層105の一部が配されることにより、電荷保持領域103に電荷を保持している間に電荷保持領域103で電荷が発生することを抑制できる。これによりノイズを低減することができる。

上部電極S106と半導体層108との間には、上部電極S106から半導体層108への電荷の注入を低減するためのブロッキング層107が配されている。ブロッキング層107は、半導体層108とは異なるバンドギャップを持つ材料で構成されうる。あるいは、ブロッキング層107は、半導体層108とは異なる不純物濃度を持つ材料で構成されうる。電極P110と半導体層108との間には、絶縁層109が配される。絶縁層109は、さらに、電極M112と半導体層108との間、および、転送電極T111との間に延在している。なお、本実施例の変形例では、ブロッキング層107および絶縁層109のいずれか一方または両方が省略される。

受光領域101と電荷保持領域103との間には、電荷転送領域102が配される。画素100は、電荷転送領域102に印加するバイアス電圧を制御する転送電極T111と、転送電極T111に接続された電源VT114を含む。電源VT114は電圧Vtを供給する。なお、本実施例の変形例では、電荷転送領域102および転送電極T111が省略される。

電極M112には、第1の容量Cm116を介して電源VD115から電圧Vmが供給される。画素100は、電極M112に接続されたリセットトランジスタ117および増幅トランジスタ118を含む。さらに、画素100は増幅トランジスタ118と出力線120の間の電気経路に配された選択トランジスタ119を含む。リセットトランジスタ117、増幅トランジスタ118、および、選択トランジスタ119は画素回路に含まれる素子の例である。増幅トランジスタ118は、受光領域101で生じた電荷に基づく信号を出力する。リセットトランジスタ117は、増幅トランジスタ118の入力ノードの電圧をリセットする。選択トランジスタ119は増幅トランジスタ118と出力線120との接続を制御する。1つの出力線120に複数の画素100が接続される。複数の画素100が複数の画素列を含む画素アレイを構成する場合には、各画素列に1つあるいは複数の出力線120が配される。出力線120には、電流源121、および、列アンプ301が接続される。増幅トランジスタ118および電流源121はソースフォロア回路を構成する。画素100から出力線120に出力された信号は、列アンプ301に入力される。

リセットトランジスタ117、増幅トランジスタ118、および、選択トランジスタ119は、不図示の基板に配される。基板は例えばシリコン基板である。半導体層108は増幅トランジスタ118を含む画素回路の配された基板の上に配される。別の観点で言えば、半導体層108は画素回路の配された基板に積層されている。

図1(b)、(c)は、電荷保持領域103を含む電荷保持部の等価回路図の例を示している。本実施例において、電荷保持部は、半導体層108と絶縁層109とを含む。したがって、電荷保持部は、上部電極S106と電極M112との間の容量成分を含む。図1(b)、(c)の等価回路は、この容量成分を上部電極S106および電極M112の間に配された第2の容量123として示している。なお、図1(b)は、電荷保持部がブロッキング層107を含む実施例を示している。そのため、ブロッキング層107および半導体層108がダイオードの回路記号124で示されている。図1(c)は、半導体層がブロッキング層を含まない実施例を示している。そのため、半導体層108が抵抗の回路記号125で示されている。半導体層108の構造は後述する。

本実施例において、受光領域101、および、電荷保持領域103は、半導体層108の連続する部分に配されている。半導体層108の連続する部分は、例えば、半導体層108のうちほぼ均質な材料により構成された部分である。撮像装置の製造時には製造誤差が生じる。そのため、半導体層108の連続する部分は、製造誤差に起因した材質の違いを含んでもよい。つまり、別の観点では、半導体層108の連続する部分は、半導体層108のうち同時に形成される部分である。半導体層108の連続する部分が同時に形成された後に、その一部のみに加工が行われてもよい。したがって、半導体層108の連続する部分は、互いに異なる厚さあるいは互いに異なる幅を有する複数の部分を含んでいてもよい。

画素100の各部の機能について説明する。半導体層108の受光領域101、上部電極S106の受光領域101の上に配された第1の部分(第1の電極)、電極P110、および、半導体層108と電極P110との間に配された絶縁層109が、光電変換部を構成する。光電変換部は、入射光に応じて信号電荷を生成し、また、入射光によって生成された電荷を信号電荷として蓄積する。上部電極S106と電極P110との間に印加される電圧に応じて、光電変換部における信号電荷の蓄積、および、光電変換部からの信号電荷の排出または転送を制御することができる。

半導体層108の電荷保持領域103、上部電極S106の電荷保持領域103の上に配された第2の部分(第3の電極)、電極M112、および、半導体層108と電極M112との間に配された絶縁層109が、電荷保持部を構成する。電荷保持部は、信号電荷を光電変換部とは別の場所で保持する。電極M112に供給されるバイアス電圧を制御することで、電荷保持部から信号を読み出すことができる。

半導体層108の電荷転送領域102、上部電極S106、転送電極T111、および、半導体層108と転送電極T111との間に配された絶縁層109が、電荷転送部を構成する。本実施例では、受光領域101と電荷保持領域103とが、電荷転送領域102を介して、半導体層108の連続する部分に配されている。このような構成により、電荷転送部は、受光領域101に蓄積された電荷を、電荷保持領域103に転送することができる。電荷の転送は、転送電極T111に供給されるバイアス電圧によって制御される。

本実施例においては、連続して形成された半導体層108の異なる部分に、受光領域101、電荷転送領域102、電荷保持領域103が配される。そして、それぞれの領域を互いに独立に制御している。これにより、受光領域101、電荷転送領域102、および、電荷保持領域103は、互いに異なる機能を実現している。受光領域101は、光電変換による電荷の生成の機能と電荷の蓄積の機能とを有する。電荷転送領域102は、受光領域101から電荷保持領域103への電荷転送の機能を有する。電荷保持領域103は、受光領域101とは独立して、電荷を保持する機能を有する。

次に、画素100の画素回路について説明する。電極M112と増幅トランジスタ118のゲートとは互いに電気的に接続される。図1(a)に示されるように、電極M112と増幅トランジスタ118のゲートとが短絡されてもよい。あるいは、電極M112と増幅トランジスタ118との間の電気経路にスイッチが配されてもよい。

図1(a)においては、電極M112と増幅トランジスタ118のゲートとにより構成されるノードが、ノードBとして示されている。ノードBは、電気的にフローティングとすることが可能である。ノードBが電気的にフローティングになることにより、ノードBの電圧が、電荷保持領域103に保持された電荷に応じて変化しうる。このような構成により、電荷保持領域103に保持された、光電変換で生じた電荷に基づく信号を、増幅トランジスタ118に入力することができる。増幅トランジスタ118は、入力された信号を増幅し、そして、出力線120に出力する。

画素100の画素回路は、電極M112の電圧をリセットするリセットトランジスタ117を有する。リセットトランジスタ117は、リセット電圧Vresを電極M112および増幅トランジスタ118のゲートに供給する。つまり、リセットトランジスタ117は増幅トランジスタ118の入力ノード(ノードB)の電圧をリセットする。リセットトランジスタ117は、オンとオフとが切り替えられるように制御される。リセットトランジスタ117がオンすることで、ノードBにリセット電圧Vresが供給される。リセットトランジスタ117がオフすることで、ノードBは電気的にフローティングになる。

電極M112には、第1の容量Cm116が電気的に接続される。電極M112と第1の容量Cm116とが短絡されてもよい。あるいは、電極M112と第1の容量Cm116との間の電気経路にスイッチが配されてもよい。

第1の容量Cm116は、例えば、絶縁体を間に挟んで対向する2つの電極により構成される。2つの電極はポリシリコンや金属などの導電材料で構成される。あるいは、第1の容量Cm116は、半導体領域と、当該半導体領域の上にゲート絶縁膜を介して配されたゲート電極とを含んで構成される。第1の容量Cm116に含まれる半導体領域は、トランジスタのソース領域やドレイン領域よりも高い不純物濃度を有することが好ましい。ゲート電極は、ポリシリコンや金属などの導電材料で構成される。

第1の容量Cm116は、電極M112に電気的に接続された第1の端子と、第1の端子とは別の第2の端子とを含む。それぞれの端子は、金属、ポリシリコンなどの導電材料、あるいは、半導体領域で構成されうる。第2の端子には、所定の電圧が供給される。本実施例では、第2の端子が電源VD115に接続され、電源VD115から複数の電圧が供給される。あるいは、第2の端子は接地されてもよい。図1(a)において、ノードBが第1の端子を含み、ノードCが第2の端子を含む。

続いて、画素100の制御について説明する。まず、露光期間においては、受光領域101に逆バイアスがかかるように、上部電極S106と電極P110の電圧を制御する。これにより、受光領域101に発生した信号電荷は、露光期間中、受光領域101に蓄積される。次に、受光領域101に保持された電荷を電荷保持領域103に転送するために、電極P110、転送電極T111、および、電極M112の電圧を制御する。例えば、電荷保持領域103のポテンシャルを、受光領域101のポテンシャルより低くすることで電荷を転送することができる。電荷転送により、露光期間が経過した後、信号電荷は電荷保持領域103に保持される。

そして、電荷保持領域103に保持された信号を読み出す時には、半導体層108を空乏化する。具体的には、半導体層108の電荷を上部電極S106へ排出する。上部電極S106と電極M112との間の電圧を制御することで電荷を排出できる。本実施例では、そのために、第1の容量Cm116の第2の端子の電圧を制御している。電源VD115が、第1の電圧と、第1の電圧とは異なる第2の電圧とを、電圧Vdとして第1の容量Cm116の第2の端子へ供給する。なお、本実施例の変形例においては、不図示の電源VMが、第1の電圧と、第1の電圧とは異なる第2の電圧とを、電圧Vmとして電極M112に供給する。本実施例の別の変形例においては、電源VS104が、第1の電圧と、第1の電圧とは異なる第2の電圧とを、電圧Vsとして上部電極S106に供給する。これらの変形例では、第1の容量Cm116の第2の端子は接地されるか、または、第1の容量Cm116が省略される。

電極M112とは別のノードの電圧を制御した際の動作について説明する。上部電極S106の電圧、あるいは、第1の容量Cm116の第2の端子の電圧が変化した際に、電極M112の電圧は、第1の容量Cm116の容量値と、上部電極S106と電極M112とが形成する第2の容量123の容量値との比に応じて変化する。画素の等価回路において、第1の容量Cm116と第2の容量123とは直列に接続された2つの容量として表され、そして、2つの容量の間のノードに電極M112(ノードB)が含まれるからである。

本実施例においては、電極M112の電圧、あるいは、第1の容量Cm116の第2の端子の電圧と、リセットトランジスタ117の供給する電圧Vresと、第1の容量Cm116の容量値と、第2の容量123の容量値とが、所定の関係を有している。この関係を満たすことにより、電極M112の電圧が変化しても、半導体層108を空乏化する電圧を第2電荷保持領域の上部電極S106と電極M112との間に印加することができる。したがって、半導体層から排出されない電荷の量を低減することができる。結果として、ノイズを低減することができる。

以上に説明した制御により、グローバル電子シャッタ動作が可能である。具体的には、複数の画素100において同時にあるいは一括で、光電変換部による信号電荷の蓄積、および、電荷保持部への電荷転送を行う。続いて、複数の画素100から順に信号を読み出す。本実施例では、信号が読み出されるまでの間、信号電荷が半導体層108の電荷保持領域103に保持される。したがって、半導体層108で生じる暗電流を抑制することで、保持されている信号電荷に加わるノイズを低減することができる。また、電荷保持領域103は、増幅トランジスタ118の入力ノードとは電気的に分離されているため、CDSなどによりノイズを低減することができる。

画素100の各部に印加される電圧について説明する。本実施例では、光電変換により生成した電荷のうち、ホールを信号電荷として利用する場合を説明する。なお、本明細書では、特に断りがない限り、接地されたノードの電圧を基準の0Vとしている。

上部電極S106には電源VS104から所定の電圧Vs(本実施例では6V)の電圧が供給される。光電変換部の電極P110には、電源VP113から所定の電圧Vp(本実施例では3V)が供給される。電圧Vsと電圧Vpとは、受光領域101のホールに対して逆バイアスが印加されるような関係を持っている。光電変換により生成したホールは、受光領域101の半導体層108と絶縁層109の界面付近に蓄積される。半導体層108の受光領域101以外の部分は、遮光層105で遮光されている。したがって、光電変換は主として受光領域101で行われる。

本実施例では、信号電荷がホールであるから、電極P110の電圧Vpは転送電極T111の電圧Vtよりも低い。図4の説明で述べるように、基板の表面と平行な面において、転送電極T111は、電極P110の周囲を囲うように配されている。よって電圧Vp<電圧Vtと設定することにより、電極P110の近傍に配された受光領域101にポテンシャルの井戸が形成される。光電変換で生成されたホールは、受光領域101のポテンシャル井戸に効率的に収集される。また転送電極T111の電圧Vtがポテンシャル障壁を形成するため、受光領域101に蓄積された電荷の漏れ出しを低減することができる。信号電荷が電子の場合、電極P110の電圧Vpは転送電極T111の電圧Vtよりも高く設定される。

本実施例では、電源VD115が、第1の容量Cm116の第2の端子に、少なくとも第1の電圧Vd1と、第1の電圧Vd1とは異なる第2の電圧Vd2とを供給する。本実施例では信号電荷がホールであるから、第2の電圧Vd2は第1の電圧Vd1より高い電圧である。本実施例では、第1の電圧Vd1は2Vであり、第2の電圧Vd2は8Vである。信号電荷が電子の場合、第2の電圧Vd2は第1の電圧Vd1より低い電圧である。信号電荷が電子の場合、例えば、第1の電圧Vd1が8Vであり、第2の電圧Vd2が2Vである。

信号電荷がホールの場合、リセット電圧Vresは、上部電極S106に供給される電圧Vsよりも低い電圧である。信号電荷が電子の場合、リセット電圧Vresは、上部電極S106に供給される電圧Vsよりも高い電圧である。本実施例では、ホール信号を利用しているので、上部電極S106に供給される電圧Vsは6V、リセット電圧Vresは3Vである。

本実施例では、ノードCに複数の電圧を含む電圧Vdを供給することで、第1の容量Cm116を介してノードCと容量結合しているノードBの電圧Vmを電源VD115が制御する。そのため、ノードCに供給される電圧Vdと、リセット電圧Vresあるいは上部電極S106に供給される電圧Vsとの直流的な大小関係は特に制限されない。

本実施例では、電極P110に供給される電圧Vpと、転送電極T111に供給される電圧Vtと、電極M112に供給される電圧Vmを制御することで、受光領域101に蓄積された信号電荷を電荷保持領域103へ速やかに、かつ、完全に転送する。信号電荷がホールの場合、電圧Vp>電圧Vt>電圧Vmという関係により、電荷を転送することができる。信号電荷が電子の場合、電圧Vp<電圧Vt<電圧Vmという関係により、電荷を転送することができる。

図2は、本実施例の撮像装置の全体の回路構成を模式的に示す図である。図2には、4行4列の行列状に配された16個の画素100が示されている。1つの列に含まれる複数の画素100が、1つの出力線120に接続される。行駆動回路201は、画素100に駆動信号pRES、駆動電圧pVP(電極P110の電圧VP)、駆動電圧pVT(転送電極T111の電圧Vt)、駆動電圧pVD(ノードCの電圧Vd)、および、駆動信号pSELを供給する。図1(a)のリセットトランジスタ117のゲートに駆動信号pRESが供給される。選択トランジスタ119のゲートに駆動信号pSELが供給される。これらの駆動信号によって、リセットトランジスタ117、および、選択トランジスタ119が制御される。1つの行に含まれる複数の画素100は共通の駆動信号線に接続される。駆動信号線は、上述の駆動信号pRES、駆動信号pSELなどを伝達する配線である。なお、図2では、異なる行に供給される駆動信号を区別するために、(n)、(n+1)などの行を表す符号を付している。他の図面でも同様である。図2においては、遮光層105の図示は省略されている。

本実施例では、第1の容量Cm116の第2の端子(ノードC)に供給される電圧Vdは、行ごとに独立して制御される。そのため、行駆動回路201が電圧供給部203から電圧Vdの供給される行を選択する。なお、異なる行に供給される電圧Vdを区別するために、(n)、(n+1)などの行を表す符号を付している。本実施例では、グローバル電子シャッタ動作を行う場合を説明する。この場合駆動電圧pVP、駆動電圧pVT、駆動電圧pVDは、全行で一括駆動される。しかしローリングシャッタ動作を行うこともできる。その場合は、各行ごとに制御される。以上に説明した構成により、本実施例では、複数の画素100を行ごとに駆動することができる。

それぞれの出力線120は、対応する列回路204に接続される。図1に示された列アンプ301は、列回路204に含まれる。列駆動回路202は、列回路204を列ごとに駆動する。具体的には、列駆動回路202は、駆動信号CSELを複数の列回路204に供給している。なお、異なる列に供給される駆動信号を区別するために、(m)、(m+1)などの列を表す符号を付している。他の図面でも同様である。このような構成により、行ごとに並列に読み出された信号を、順次、出力部に出力することができる。

列回路204について詳細に説明する。図3は、m列目およびm+1列目の列回路204の等価回路を示している。他の列の列回路204の図示は省略されている。

出力線120の信号は、列アンプ301によって増幅される。列アンプ301の出力ノードは、S/Hスイッチ302を介して容量CTSに接続される。また、列アンプ301の出力ノードは、S/Hスイッチ303を介して容量CTNに接続される。S/Hスイッチ302およびS/Hスイッチ303は、それぞれ、駆動信号pTSおよび駆動信号pTNによって制御される。このような構成により、画素100からのリセットノイズを含むノイズ信号Nと、光信号Sとを保持することができる。したがって、本実施例の撮像装置は相関二重サンプリングを行うことが可能である。つまりリセットノイズを除去した信号読み出しをすることができる。

容量CTSは、水平転送スイッチ304を介して水平出力線306に接続される。容量CTNは、水平転送スイッチ305を介して水平出力線307に接続される。水平転送スイッチ304および305は、列駆動回路からの駆動信号CSELによって制御される。

水平出力線306と水平出力線307とはいずれも出力アンプ122に接続される。出力アンプ122は、水平出力線306の信号と水平出力線307の信号との差分信号を増幅して出力する。増幅された信号は、アナログデジタル変換部205に入力され、アナログ信号からデジタル信号へ変換され、それから、撮像装置の外部へ出力される。

なお、列回路204はアナログデジタル変換回路であってもよい。この場合、アナログ−デジタル変換回路は、メモリやカウンタなどのデジタル信号を保持する保持部を有する。保持部には、ノイズ信号Nおよび光信号Sがそれぞれデジタル信号に変換されて保持される。

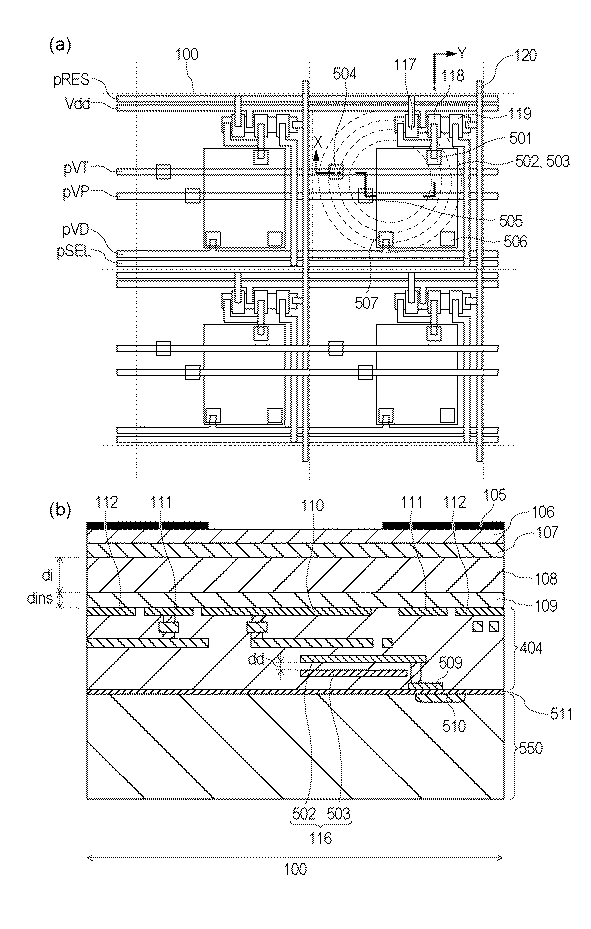

次に、本実施例の撮像装置の平面構造、および、断面構造について説明する。図4(a)は、撮像装置の平面構造を模式的に示している。図1と同じ部分には、同じ符号を付してある。図4(a)は2行2列の画素100を示している。図4(a)は、画素回路の配された基板の表面と平行な面における電極P110、転送電極T111、および、電極M112の配置を模式的に示している。

図4(b)は、撮像装置の断面構造を模式的に示している。図4(b)に示された断面は、図4(a)における一点破線A−Bに沿った断面に対応する。図1と同じ部分には、同じ符号を付してある。図4(b)は、マイクロレンズ401、平坦化層402、カラーフィルタ403、半導体層108と基板との間に配される層間膜404が示されている。半導体層108には、受光領域101、電荷転送領域102、および、電荷保持領域103が示されている。なお、層間膜404には電極と画素回路とを接続する不図示の導電部材が配されている。

図4(b)が示す通り、電極P110、転送電極T111、および、電極M112は、それらの重心が一致するように、配される。このような構成によれば、マイクロレンズ401が光電変換部(受光領域101および電極P110)に効率的に入射光をフォーカスすることができる。光電変換部の電界分布と光入射分布とが揃うため、光電変換によって発生した電荷が効率的に受光領域101に収集される。

図4(a)の示す平面において、転送電極T111は、電極P110を囲うように配されている。このような配置により、受光領域101に蓄積された電荷を、素早く電荷保持領域103に転送することができる。結果として、撮像装置の駆動を高速化することができる。また、転送電極T111に印加されるバイアス電圧によりポテンシャル障壁を形成することができる。これにより、生成された電荷を効率よく受光領域101に収集することができ、また、収集された電荷が電荷保持領域103や隣接する画素にもれることを抑制できる。電荷転送中には、速やかにかつ完全に電荷転送できるようになっている。

図4(c)は遮光層105の平面構造を模式的に示す。点線は電極P110、転送電極T111、電極M112の形状を示す。

次に、基板に配された画素回路の平面構造、および、断面構造について説明する。図5(a)は、基板に配された画素回路の平面視における配置を模式的に示している。つまり、図5(a)は、画素回路を基板の表面と平行な面に投影したときの配置を示している。図5(b)は、基板550、ならびに、基板550の上に積層された層間膜404および半導体層108の断面構造を模式的に示している。図5(b)に示された断面は、図5(a)における一点破線X−Yに沿った断面に対応する。なお、図1と同じ機能を有する部分には同じ符号を付してある。ただし、トランジスタについては対応するゲート電極に符号が付されている。また、駆動信号線を構成する導電部材には、当該駆動信号線に供給される駆動信号と同じ符号が付されている。例えば、pRESの符号が付された導電部材は、駆動信号pRESを供給するための駆動信号線を構成する。

図5(a)は、2行2列の行列状に配された4つの画素100を示している。右上の画素にのみ点線で、図4(a)の電極P110、転送電極T111、電極M112に相当する部分を示してある。その他の画素では省略してある。図5(a)には、第1の容量Cm116の第1の端子を構成する電極502および第2の端子を構成する電極503が示されている。電極502と電極503とは平面視において重なるように配置されている。

図5(a)に示されるように、第1の容量Cm116の第1の端子を構成する電極502と増幅トランジスタ118とがコンタクト501を介して電気的に接続される。第1の容量Cm116の第1の端子を構成する電極502と電極M112とは、コンタクト506を介して電気的に接続される。容量CM116の第2の端子を構成する電極503と駆動信号線pVDとは、コンタクト507を介して接続される。また、コンタクト504は、転送電極T111と駆動信号線pVTを接続する。コンタクト505は電極P110と駆動信号線pVPを接続する。

図5(a)および図5(b)が示すように、第1の容量Cm116の電極503は、駆動信号線pVDに接続される。駆動信号線pVDは、電源VD115からの電圧Vdを伝達する。本実施例では、駆動信号線pVDが行ごとに配される。つまり、ある行の駆動信号線pVDと、他の行の駆動信号線pVDとは電気的に絶縁される。このような構成により、行ごとに独立して第1の容量Cm116の第2の端子(ノードC)の電圧Vdを制御することができる。

図5(b)が示すように、撮像装置は基板550を含む。基板550には、画素トランジスタのソース領域およびドレイン領域が配される。画素トランジスタとは、画素回路に含まれるトランジスタであり、例えば、リセットトランジスタ117、増幅トランジスタ118、および、選択トランジスタ119である。基板550の上に、画素トランジスタのゲート電極、および、配線を構成する導電部材を含む層間膜404が配される。層間膜404の上に、絶縁層109、および、半導体層108が配される。

上部電極S106は、所定の量の光を透過させる導電部材で構成される。例えば、ITO(Indium Tin Oxide)などのインジウム、および/または、スズを含む化合物や、ZnOなどの化合物が、上部電極S106の材料として用いられる。このような構成によれば、多くの光を受光領域101に入射させることができる。そのため、感度を向上させることができる。他の例として、所定の量の光が透過する程度の薄さを有するポリシリコンや金属を、上部電極S106として用いてもよい。金属は抵抗が低いため、金属を上部電極S106の材料に用いた実施例は、低消費電力化あるいは駆動の高速化に有利である。なお、上部電極S106の光の透過率は、ゼロでなければ、特に限定されない。

遮光層105は、光の透過率が低い材料が用いられる。好適には、上部電極S106に対する光の透過率よりも低い透過率を有する材行が用いられる。遮光層105には、例えば、金属、有機樹脂などの材料が用いられる。遮光層105に金属が用いられる場合、遮光層105と上部電極S106とが電気的に接続される。このような構成により、上部電極S106の抵抗を実効的に下げることができるため、動作を高速化することができる。なお、本実施例では遮光層105は、上部電極S106の上に配されている。本実施例の変形例では、遮光層105は上部電極S106と電荷保持領域103との間に配される。

半導体層108は、真性のアモルファスシリコン(以下、a−Si)、低濃度のP型のa−Si、低濃度のN型のa−Siなどで形成される。あるいは、半導体層108は、化合物半導体で形成されてもよい。例えば、BN、GaAs、GaP、AlSb、GaAlAsPなどのIII−V族化合物半導体、CdSe、ZnS、HdTeなどのII−VI族化合物半導体、PbS、PbTe、CuOなどのIV−VI族化合物半導体が挙げられる。あるいは、半導体層108は、有機材料で形成されてもよい。例えば、フラーレン、クマリン6(C6)、ローダミン6G(R6G)、亜鉛フタロシアニン(ZnPc)、キナクリドン、フタロシアニン系化合物、ナフタロシアニン系化合物などを用いることができる。さらに、上述の化合物半導体で構成された量子ドット膜を半導体層108に用いることができる。半導体層108の不純物濃度が低いか、あるいは、半導体層108は真性であるとよい。このような構成によれば、半導体層108に空乏層を十分に広げることができるため、高感度化、ノイズ低減などの効果を得ることができる。

ブロッキング層107は、上部電極S106から半導体層108へ信号電荷と同じ導電型の電荷が注入されることを阻止する。上部電極S106をITOとした場合、半導体層108を形成する半導体との組み合わせによっては、上部電極S106をブロッキング層107として兼用することできる。つまり上部電極S106から半導体層108に信号電荷と同じ導電型の電荷が注入されないような、ポテンシャル障壁が形成されればよい。

ブロッキング層107には、半導体層108に用いられる半導体と同じ種類であって、半導体層108に用いられる半導体よりも不純物濃度の高いN型あるいはP型の半導体を用いることができる。例えば、半導体層108にa−Siが用いられる場合、ブロッキング層107に不純物濃度の高いN型のa−Si、あるいは、不純物濃度の高いP型のa−Siが用いられる。不純物濃度の違いによりフェルミ準位の位置が異なるため、電子およびホールのうち一方に対してのみ、ポテンシャルバリアを形成することができる。ブロッキング層107の導電型は、信号電荷と反対の導電型の電荷が多数キャリアとなる導電型である。

もしくは、半導体層108とは異なる材料でブロッキング層107を構成することができる。このような構成によれば、ヘテロ接合が形成される。材料の違いによりバンドギャップが異なるため、電子およびホールのうち一方に対してのみ、ポテンシャルバリアを形成することができる。

半導体層108と、電極P110、転送電極T111、および、電極M112のそれぞれとの間には、絶縁層109が配される。絶縁層109には、絶縁性の材料が用いられる。例えば絶縁層109の材料として、酸化シリコン、アモルファス酸化シリコン(以下、a−SiO)、窒化シリコン、アモルファス窒化シリコン(a−SiN)などの無機材料、あるいは、有機材料が用いられる。絶縁層109の厚さは、トンネル効果により電荷が透過しない程度の厚さとするとよい。このような構成にすることで、リーク電流を低減できるため、ノイズを低減することができる。具体的には、絶縁層109の厚さは50nm以上とするとよい。

ブロッキング層107、半導体層108、および、絶縁層109にa−Si、a−SiO、a−SiNを用いる場合は、水素化処理を行い、水素でダングリングボンドを終端してもよい。このような構成により、ノイズを低減することができる。

電極P110、転送電極T111、および、電極M112は、それぞれ、金属などの導電部材で構成される。電極P110、転送電極T111、および、電極M112には、配線を構成する導電部材、あるいは、外部との接続用のパッド電極を構成する導電部材と同じ材料が用いられる。このような構成によれば、電極P110、転送電極T111、電極M112、配線、および、パッド電極の一部または全部を同時に形成することができる。したがって、製造プロセスを簡略化することができる。

図6を用いて本実施例の動作について説明する。図6(a)〜(c)は、半導体層108における信号電荷(ホール)の動作を模式的に示している。図6(d)〜(f)は、半導体層108と絶縁層109との界面におけるポテンシャルを模式的に示す。図6(d)〜(f)、および、図7のそれぞれにおいて、縦軸はホールに対するポテンシャルを表している。縦軸の上に行くほど、ホールに対するポテンシャルが低い。したがって、縦軸の上に行くほど、電圧は低くなる。上部電極S106、および、電極P110、電極M112については、自由電子のエネルギー準位が示されている。ブロッキング層107、および、半導体層108については、伝導帯のエネルギー準位と価電子帯のエネルギー準位との間のバンドギャップが示されている。なお、半導体層108と絶縁層109との界面における半導体層のポテンシャルを、便宜的に、半導体層108の表面ポテンシャル、あるいは、単に表面ポテンシャルと呼ぶ。

図6(a)は、光電変換部101での光電変換によって生成したホールが受光領域101に蓄積された状態を示す。図6(d)は、図6(a)に対応する受光領域101、電荷転送領域102、電荷保持領域103におけるホールに対するポテンシャルの模式図を示す。白抜きの丸はホールを表す。この場合電極P110の電圧Vp、転送電極T111の電圧Vt、電極M112の電圧Vmは、Vp=Vm<Vtの関係を満たしている。この関係により、受光領域101と電荷保持領域103の間にはポテンシャル障壁が形成され、電気的に分離されている。つまり転送電極T111は、受光領域101と電荷保持領域103の分離を行う分離電極として働いている。好適にはVs=Vtとすることで、電気的な分離性能が向上する。

図6(b)は、受光領域101に蓄積されたホールを、電荷保持領域103に電荷転送している状態を示す。図6(e)は、図6(b)に対応する受光領域101、電荷転送領域102、電荷保持領域103におけるホールに対するポテンシャルの模式図を示す。この場合電極P110の電圧Vp、転送電極T111の電圧Vt、電極M112の電圧Vmは、Vp=Vt>Vmの関係またはVp>Vt>Vmの関係を満たしている。この関係により、受光領域101から電荷保持領域103の間にはポテンシャルのスロープが形成される。そのため、受光領域101に蓄積されたホールは、半導体層108と絶縁層109界面に沿って、電荷保持領域103へ転送される。

図6(c)は、電荷保持領域103に保持した信号電荷を半導体基板上の回路に読み出す動作を示す。図6(f)は、図6(c)に対応する受光領域101、電荷転送領域102、電荷保持領域103におけるホールに対するポテンシャルの模式図を示す。電極M112の電圧Vmを変化させることにより、電荷保持領域103の電荷の量に応じた電圧変化が電極M112に接続された増幅トランジスタ118に生じる。

本実施例において、受光領域101から電荷転送領域102を介して電荷保持領域103まで、半導体層108が、基板の表面に平行な方向に沿って連続している。したがって、受光領域101に蓄積された電荷を複数の画素において同時に転送し、信号が読み出されるまで電荷保持領域103で電荷保持することにより、グローバル電子シャッタ動作を実現できる。

次に、図7を用いて、電荷保持領域103に保持された電荷に基づく信号の読み出し動作について説明する。図7は、基板の表面に垂直な方向に沿った半導体層108のエネルギーバンドを模式的に示す。図7の左側には、受光領域101におけるエネルギーバンドが示されている。図7の右側には電荷保持領域103におけるエネルギーバンドが示されている。受光領域101については、上部電極S106、ブロッキング層107、半導体層108、絶縁層109、および、電極P110のエネルギーバンドが示されている。電荷保持領域103については、上部電極S106、ブロッキング層107、半導体層108、絶縁層109、電極M112のエネルギーバンドが示されている。

受光領域101の動作としては、以下のステップp1〜p3が繰り返し行われる。ステップp1は電荷転送、ステップp2は入射光の光電変換、および、信号電荷の蓄積である。以下各ステップについて説明する。

ステップp1において、図6で説明した通りに、受光領域101に蓄積された信号電荷を、電荷転送領域102を介して、電荷保持領域103に転送する。受光領域101は、ホールが蓄積された状態からホールがなくなった状態に変化する。一方で、電荷保持領域103はホールが存在しない状態からホールが保持された状態に変化する。

ステップp2では光電変換を行う。受光領域101においては、入射した光によって生じた電子ホール対のうちホールが信号電荷として蓄積される。電子は上部電極S106に排出される。その結果、入射した光の量に応じた量のホールが、受光領域101と絶縁層109との界面に蓄積される。

以降受光領域101では、ステップp1からステップp3が繰り返される。動画撮影の場合、この繰り返しが1フレームの動作に対応する。この動作は全画素同じタイミングで繰り返すことができるので、グローバル電子シャッタ動作となる。一括電荷転送後、受光領域101は、電荷保持領域103から電気的に切り離され、独立に制御することができる。

電荷保持領域103の動作としては、以下のステップm1〜m5が繰り返し行われる。ステップm1は増幅トランジスタ118の入力ノードのリセットである。ステップm2はノイズ信号Nの読み出し(N読み)である。ステップm3は電荷の転送である。ステップm4は電荷保持領域103からの信号電荷の排出である。ステップ5は光信号Sの読み出し(S読み)である。以下、それぞれのステップについて説明する。

ステップm1において、リセットトランジスタ117をオンにする。電極M112を含むノード、つまり、図1(a)のノードBの電圧がリセット電圧Vresにリセットされる。リセット電圧Vresは、例えば、3Vである。

その後、ステップm2において、リセットトランジスタ117をオフする。これにより、ノードBが電気的にフローティングになる。このときリセットトランジスタ117によるリセットノイズ(ノイズkTC)が発生しうる。選択トランジスタ119がオンし、そして、増幅トランジスタ118がリセットノイズを含むノイズ信号N(Vres+kTC)を画素100から出力する(N読み)。ノイズ信号Nは、列回路204の容量CTNに保持される。

その後、ステップm3において、受光領域101から電荷保持領域103へ信号電荷が転送される。受光領域101のステップp1と電荷保持部103のステップm3とは同時に行われる動作である。なお、この時点では、電源VD115が図1(a)のノードCに第1の電圧Vd1を供給している。

次に、ステップm4において、電源VD115が図1(a)のノードCに第2の電圧Vd2を供給する。電極M112(ノードB)の電圧は、ノードCの電圧の変化と同じ方向に向かって変化する。信号電荷としてホールを用いているため、このときの電極M112の電圧Vm2が上部電極S106の電圧Vs(=6V)よりも高くなるように、第1の電圧Vd1および第2の電圧Vd2が設定される。本実施例において、第1の電圧Vd1は2Vであり、第2の電圧Vd2は8Vである。

電極M112の電圧の変化量dVBは、電極M112に接続された第1の容量Cm116の容量値C1と、電荷保持領域103が有する第2の容量123の容量値C2との比に応じて決まる。ノードCの電圧の変化量dVdに対して、電極M112の電圧の変化量dVBは、dVB=dVd×C1/(C1+C2)と表される。なお、電極M112を含むノードBは他の容量成分を含みうる。しかし、他の容量成分は第1の容量Cm116の容量値C1にくらべて十分に小さい。そのため、ノードBの容量値は、第1の容量Cm116の容量値C1と等しいとみなしてよい。

本実施例では、電極M112の電圧の変化量dVBが、上部電極S106の電圧Vsとリセット電圧Vresの差(Vs−Vres)よりも十分に大きい。そのため、電極M112のポテンシャルは、上部電極S106のポテンシャルよりも低くなり、半導体層108のポテンシャルの傾きが反転する。これにより、黒丸で示された電子が上部電極S106から半導体層108へ注入される。また、信号電荷として半導体層108と絶縁層109の海面に保持されたホールの一部または全部が、ブロッキング層107の方へ移動する。移動したホールは、ブロッキング層107の多数キャリアと再結合して消滅する。その結果、半導体層108のホールが半導体層108から排出される。半導体層108の全体が空乏化する場合には、信号電荷として保持されたホールの全部が排出される。

次に、ノードCに第1の電圧Vd1が供給される。これにより、半導体層108のポテンシャルの傾きが再び反転する。そのため、半導体層108に注入されていた電子は、半導体層108から排出される。一方、ブロッキング層107が、上部電極S106から半導体層108へのホールの注入を阻止する。したがって、半導体層108の表面ポテンシャルは、保持されていたホールの量に応じて変化する。表面ポテンシャルの変化に対応して、電極M112の電圧は、リセットされた状態から、消滅したホールの量に応じた電圧Vsigだけ変化する。つまり、信号電荷として保持されたホールの量に応じた電圧VsigがノードBに現れる。保持されたホールの量に応じた電圧Vsigを、光信号成分と呼ぶ。

そして、ステップ5において、選択トランジスタ119がオンする。これにより、増幅トランジスタ118が光信号S(Vsig+Vres+kTC)を画素100から出力する。光信号Sは、列回路204の容量CTSに保持される。ステップm2で読み出されたノイズ信号N(Vres+kTC)と、ステップm5で読み出された光信号S(Vph+Vres+kTC)との差分が、保持された信号電荷に応じた電圧Vsigに基づく信号(光信号成分)である。

信号電荷が電子の場合、第2の電圧Vd2は第1の電圧Vd1より低い電圧である。また、リセット電圧Vresは上部電極S106の電圧Vsより低く設定される。

本実施例では、半導体層108のポテンシャルの傾きが反転することで、保持されたホールの排出を行っている。半導体層108のポテンシャルの傾きを反転させることができないと、排出されない電荷が生じるため、ノイズが生じる可能性がある。ここで、電極M112(ノードB)の電圧の変化量dVBが、上部電極S106の電圧Vsとリセット電圧Vresの差(Vs−Vres)に比べて大きいほど、ポテンシャル勾配を反転させやすい。つまり、電極M112の電圧の変化量dVBが、上部電極S106の電圧Vsとリセット電圧Vresの差(Vs−Vres)に比べて大きいほど、ノイズを低減することができる。

上述のとおり、ノードCの電圧の変化量dVdとノードBの電圧の変化量dVBとの間には、dVB=dVd×C1/(C1+C2)という関係がある。つまり、ノードBの容量値C1が大きいほど、ノードBの電圧の変化量dVBが大きくなる。

本実施例では、電極M112に第1の容量Cm116が接続されている。そのため、ノードBの容量値C1を大きくすることができる。このような構成によれば、第ノードBの電圧の変化量dVBを大きくすることができる。結果として、半導体層108を空乏化しやすくなるため、排出されない電荷を低減できる。このように、本実施例によれば、ノイズを低減することができる。

ノードBに第1の容量CM116が接続されていない構成を説明する。この場合、ノードBの容量は、半導体領域のPN接合による容量成分や配線との寄生容量成分を含みうる。しかし、これらの容量成分は、電荷保持領域103の有する第2の容量123の容量値C2に比べて無視できるほど小さい。したがって、C1/(C1+C2)がほとんどゼロになる。そのため、ノードCの電圧Vdを変化させても、ノードBの電圧がほとんど変化しない。そうすると、ポテンシャルの傾きが反転させられず、結果として信号電荷として保持されたホールの一部を排出できない可能性が生じる。これに対して、本実施例では排出されない信号電荷の量を低減できるので、ノイズを低減することができる。

続いて、第1の容量Cm116の容量値C1と、電荷保持領域103に含まれる第2の容量123の容量値C2と、各部に供給される電圧との関係について説明する。

本実施例においては、電荷保持領域103は、ブロッキング層107、半導体層108、絶縁層109を含んでいる。ブロッキング層107は、半導体層108、および、絶縁層109に比べて導電率が高い。そのため、電荷保持領域103に含まれる第2の容量123の容量値C2は、半導体層108による容量成分Ciと絶縁層109による容量成分Cinsの合成容量となる。具体的に、第2の容量123の容量値C2は、次の式(1)で表される。

C2=Ci×Cins/(Ci+Cins) ・・・(1)

平面視における電極P110の面積Ss、半導体層108の厚さdi、絶縁層109の厚さdins、半導体層108の比誘電率Ei、絶縁層109の比誘電率Eins、および、真空の誘電率E0を用いて、容量成分Ciおよび容量成分Cinsは、それぞれ、次の式(2)および式(3)で表される。

Ci=E0×Ei×Ss/di ・・・(2)

Cins=E0×Eins×Ss/dins ・・・(3)

電極P110のフリンジ電界はほとんど無視できるので、容量の計算に用いられる面積として、平面視における電極P110の面積Ssだけを考慮すればよい。平面視における電極P110の面積Ssは、例えば、図4における電極P110の面積である。また、図5において、半導体層108の厚さdi、絶縁層109の厚さdinsが示されている。

第1の容量Cm116の容量値C1は、平面視における上部電極211または下部電極213の面積Sd、上部電極211と下部電極213との距離dd、および、上部電極211および下部電極213の間の絶縁層の誘電率Edを用いて、次の式(4)で表される。

C1=E0×Ed×Sd/dd ・・・(4)

本実施例においては、ノードCの電圧Vdを、第1の電圧Vd1と第2の電圧Vd2とに制御することで、信号電荷の蓄積と、半導体層108の空乏化による信号電荷の排出を行っている。第1の容量Cm116の容量値C1と第2の容量123の容量値C2が以下に説明する関係を満たすと、上述の信号電荷の排出の際に、半導体層108に残る電荷を低減することができる。最初に、信号電荷がホールの実施例を説明する。

以下、簡単のために、第1の容量Cm116の容量値C1が、第2の容量123の容量値C2のk倍であるとする。つまり、容量値C1と容量値C2が次の式(5)の関係を有する。

C1=k×C2 ・・・(5)

前述のとおり、ノードCの電圧の変化量dVdと、電極M112(ノードB)の電圧の変化量dVBとは、次の式(19)で表される関係を有する。

dVB=dVd×C1/(C1+C2) ・・・(6)

式(5)と式(6)から、次の式(7)が得られる。

dVB=dVd×k/(1+k) ・・・(7)

ここで、信号電荷としてホールを蓄積するためには、上部電極S106(ノードA)に供給される電圧Vsとリセット電圧Vresが以下の式(8)の関係を満たすとよい。

Vs>Vres ・・・(8)

信号電荷のホールを転送するためには、上部電極S106(ノードA)の電圧Vs、リセット電圧Vres、および、電極M112の電圧の変化量dVBが、次の式(10)の関係を満たすとよい。

Vs<Vres+dVB ・・・(9)

式(8)の関係が満たされると、ホールが絶縁層109に向かってドリフトするためのポテンシャルの傾きを半導体層108に形成することができる。式(9)の関係が満たされると、半導体層108のポテンシャルの傾きを逆転させることが容易になる。

式(7)と式(9)から、式(10)が得られる。

Vs−Vres<dVd×k/(1+k) ・・・(10)

ここで、信号電荷がホールの実施例では、第2の電圧Vd2が第1の電圧Vd1よりも高い。つまり、ノードCの電圧の変化量dVd=Vd2−Vd1は、正の値である。したがって、式(10)の両辺をdVdで除しても、不等号の向きは変わらない。

したがって、式(10)から、容量値C1と容量値C2との容量比kに関して、次の式(11)で表される関係式が得られる。

この式(11)の関係が満たされると、排出されない電荷の量を低減することができる。したがって、ノイズを低減することができる。

具体的に、本実施例では第1の容量Cm116の容量値C1は4fFであり、第2の容量123の容量値C2は1fFである。つまり、k=4となっている。このような構成によれば、よりノイズを低減することができる。

本実施例では、平面視において、第1の容量Cm116の上部電極211および下部電極213のいずれかの面積Sdと、電極M112の面積Ssが、Sd>0.5×Ssの関係を満たす。このような構成によれば、上述の容量比の関係を容易に得ることができる。

また、kの値が大きいほど、ノイズ低減の効果は大きくなる。したがって、第1の容量Cm116の容量値C1が、第2の容量123の容量値C2と等しいか、あるいはそれより大きいと、ノイズ低減の効果をさらに高くすることができる。

ノードCの電圧の変化量dVdは、第1の電圧Vd1と第2の電圧Vd2とを用いて、dVd=Vd2−Vd1と表される。また、式(11)の左辺は、式(5)を用いてC1/(C1+C2)と書き換えることができる。したがって、式(11)は、式(12)のように変形される。

次に、信号電荷が電子の実施例を説明する。信号電荷が電子の場合、式(8)および式(9)の不等号の向きが変わる。したがって、次の式(10)の不等号の向きも変わる。すなわち、信号電荷が電子の場合には、次の式(13)が得られる。

Vs−Vres>dVd×k/(1+k) ・・・(13)

しかし、信号電荷が電子の実施例では、第2の電圧Vd2が第1の電圧Vd1よりも低い。つまり、ノードCの電圧の変化量dVd=Vd2−Vd1は、負の値である。したがって、式(13)の両辺をdVdで除すと、不等号の向きが変わる。その結果、信号電荷がホールの場合と同じように、式(11)、ならびに、式(12)が得られる。

ここで、式(12)の表す関係について説明する。リセット電圧Vresが電荷保持領域103の上部電極S106に供給される電圧Vsに近いほど、右辺の値は小さくなる。つまり、第1の容量Cm116の容量値C1が小さくても、半導体層108のポテンシャルの傾きを反転することができるようになる。リセット電圧Vresと上部電極S106に供給される電圧Vsとの差が小さいと、半導体層108に蓄積できる電荷の量が小さくなる。

一方で、リセット電圧Vresと電圧Vsとの差が大きいほど、右辺の値は大きくなる。つまり、第1の容量Cm116の容量値C1に大きい値が用いられる。このときには、リセット電圧Vresと第1の電圧Vs1との差が大きいので、半導体層108に蓄積できる電荷の量を増やすことができる。

以上に説明したとおり、第1の容量Cm116の容量値C1と、電荷保持領域103に含まれる第2の容量123の容量値C2との関係によって、ノイズを低減することができる。

なお、上で挙げた数値はあくまでも一例であり、これらの値に限定されるものではない。半導体層108と絶縁層109との間の界面に欠陥準位などが存在する可能性がある。このような場合には、公知の技術に基づいてフラットバンド電圧を考慮すればよい。

次に本実施例の撮像装置の制御に用いられる駆動信号について説明する。図8、図9は、本実施例の撮像装置に用いられる駆動信号のタイミングチャートを示している。図8には、1行分の信号の読み出し動作に対応した駆動信号が示されている。図9には、n行目とn+1行目の2行分の信号の読み出し動作に対応した駆動信号が示されている。

駆動信号pSELは選択トランジスタ119のゲートに供給される。駆動信号pRESはリセットトランジスタ117のゲートに供給される。駆動信号pVTは転送電極T111に供給される。駆動信号pTSはS/Hスイッチ302に供給される。駆動信号pTNはS/Hスイッチ303に供給される。駆動信号CSELは列駆動回路202に供給される。

駆動信号pSEL、駆動信号pRES、駆動信号pTN、駆動信号pTSがハイレベルの時に、対応するトランジスタまたはスイッチがオンする。駆動信号pSEL、駆動信号pRES、駆動信号pTN、駆動信号pTSがローレベルの時に、対応するトランジスタまたはスイッチがオフする。これらの駆動信号のハイレベルおよびローレベルは、トランジスタまたはスイッチの閾値電圧に応じて設定される。図8には、駆動信号pVDのタイミングチャートが示されている。駆動信号pVDは、初期電圧Vd0、第1の電圧Vd1、および、第2の電圧Vd2を含む。

本実施例の撮像装置は、いわゆるグローバル電子シャッタ動作を行う。まず図8を用いて詳細に説明する。t1からt2までの期間GSは一括電荷転送の期間である。t2からt10までの期間HBLNK(n)は水平ブランキング期間である。t10からt11までの期間HSCAN(n)は水平走査期間である。

時刻t1において、全画素の駆動信号pVTが6Vから3Vに変化する。同時に全画素の駆動信号pVDの電圧を初期電圧Vd0(=3V)から第1の電圧Vd1(=2V)に変化させる。これにより受光領域101の信号電荷を、全画素一括で、電荷保持領域103に転送する。時刻t2において、全画素の駆動信号pVTを3Vから6Vに変化させることで、電荷の転送を終了する。

時刻t3まで駆動信号pRES(n)はハイレベルに維持され、n行目の画素100のリセットトランジスタ117がオンされている。n行目の画素100のノードBの電圧は、リセット電圧Vresにリセットされている。その後、時刻t3において、駆動信号pRES(n)がローレベルになり、リセットトランジスタ117がオフする。

次に、駆動信号pTN(n)が、時刻t4においてハイレベルになり、時刻t5においてローレベルになる。これにより、リセットノイズ(図6のkTC)を含むノイズ信号Nが、列回路204の容量CTNに保持される。

時刻t6において、駆動信号pVD(n)が第1の電圧Vd1(=2V)から第2の電圧Vd2(=8V)に遷移する。続いて、時刻t7において、駆動信号pVD(n)が第2の電圧Vd2から第1の電圧Vd1に遷移する。時刻t6から時刻t7の動作によって、電荷保持領域103に保持されていた信号電荷の排出が行われ、ノードBには保持されていた信号電荷の量に応じた電圧Vsigが生じる。

駆動信号pTS(n)が、時刻t8においてハイレベルになり、時刻t9においてローレベルになる。これにより、電圧Vphとリセットノイズとを含む光信号Sが、列回路204の容量CTSに保持される。

続いて、時刻t10において、駆動信号pVD(n)が第1の電圧Vd1から第2の電圧Vd2に遷移する。これにより半導体層108に残留する電荷が全て排出され、受光領域101のリセット(膜リセット)が行われる。これにより前のフレームの残留電荷などが次のフレームの光信号Sに影響を与えることを防ぐことができる。

時刻t11において、駆動信号pPRES(n)がローレベルになり、かつ、駆動信号pVD(n)が第2の電圧Vd2から初期の電圧Vd0に遷移する。これにより、n行目の画素100のノードBの電圧が、再びリセット電圧Vresにリセットされる(FDリセット)。駆動信号pPRES(n)は次のフレームのt3までハイレベルに維持され、ノードBはリセット電圧Vresに固定される。この後、n行目の画素100は、次のフレームの信号電荷の蓄積を開始する。

時刻t11において、列回路204に読みだされたノイズ信号Nと光信号Sは、駆動信号CSELに基づいて、列ごとに出力アンプ122に出力される。出力アンプ122は光信号Sとノイズ信号Nの差分を増幅して、アナログ−デジタル変換部205に出力する。

以降、図9に示すようにn+1行目の画素100からの信号の読み出しが行われる。この動作は時刻t1から時刻t11と同様なので、説明を省略する。

以上に説明した通り、本実施例においては、半導体層108の連続する部分に受光領域101および電荷保持領域103が配される。このような構成によれば、ノイズを低減することができる。