JP6755911B2 - 半導体素子パッケージ - Google Patents

半導体素子パッケージ Download PDFInfo

- Publication number

- JP6755911B2 JP6755911B2 JP2018165079A JP2018165079A JP6755911B2 JP 6755911 B2 JP6755911 B2 JP 6755911B2 JP 2018165079 A JP2018165079 A JP 2018165079A JP 2018165079 A JP2018165079 A JP 2018165079A JP 6755911 B2 JP6755911 B2 JP 6755911B2

- Authority

- JP

- Japan

- Prior art keywords

- metal body

- groove

- insulating member

- cavity

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 108

- 229910052751 metal Inorganic materials 0.000 claims description 116

- 239000002184 metal Substances 0.000 claims description 116

- 239000000463 material Substances 0.000 claims description 35

- 229920005989 resin Polymers 0.000 claims description 33

- 239000011347 resin Substances 0.000 claims description 33

- 229910052782 aluminium Inorganic materials 0.000 claims description 18

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 16

- 239000010410 layer Substances 0.000 description 38

- 239000000758 substrate Substances 0.000 description 19

- 239000000853 adhesive Substances 0.000 description 16

- 230000001070 adhesive effect Effects 0.000 description 16

- 239000000203 mixture Substances 0.000 description 13

- 239000002019 doping agent Substances 0.000 description 11

- 238000000034 method Methods 0.000 description 11

- 230000000994 depressogenic effect Effects 0.000 description 10

- 238000005520 cutting process Methods 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 9

- 230000003287 optical effect Effects 0.000 description 9

- 229920001721 polyimide Polymers 0.000 description 8

- 230000007423 decrease Effects 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 229920002050 silicone resin Polymers 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 229920000106 Liquid crystal polymer Polymers 0.000 description 4

- 239000004977 Liquid-crystal polymers (LCPs) Substances 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 4

- 239000004734 Polyphenylene sulfide Substances 0.000 description 4

- 239000004954 Polyphthalamide Substances 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 239000003822 epoxy resin Substances 0.000 description 4

- 238000000605 extraction Methods 0.000 description 4

- 239000010931 gold Substances 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 229920000647 polyepoxide Polymers 0.000 description 4

- 239000009719 polyimide resin Substances 0.000 description 4

- 229920000069 polyphenylene sulfide Polymers 0.000 description 4

- 229920006375 polyphtalamide Polymers 0.000 description 4

- 239000011342 resin composition Substances 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 4

- 229910052737 gold Inorganic materials 0.000 description 3

- 230000001590 oxidative effect Effects 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 230000001954 sterilising effect Effects 0.000 description 3

- 229910052725 zinc Inorganic materials 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- 229910002704 AlGaN Inorganic materials 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 229920000122 acrylonitrile butadiene styrene Polymers 0.000 description 2

- 239000012790 adhesive layer Substances 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 238000005401 electroluminescence Methods 0.000 description 2

- 230000007613 environmental effect Effects 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 229910052738 indium Inorganic materials 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 229920005668 polycarbonate resin Polymers 0.000 description 2

- 239000004431 polycarbonate resin Substances 0.000 description 2

- 229920001296 polysiloxane Polymers 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 229910052711 selenium Inorganic materials 0.000 description 2

- 239000011669 selenium Substances 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 230000003595 spectral effect Effects 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 238000004659 sterilization and disinfection Methods 0.000 description 2

- 238000004381 surface treatment Methods 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- WUPHOULIZUERAE-UHFFFAOYSA-N 3-(oxolan-2-yl)propanoic acid Chemical compound OC(=O)CCC1CCCO1 WUPHOULIZUERAE-UHFFFAOYSA-N 0.000 description 1

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 229910000980 Aluminium gallium arsenide Inorganic materials 0.000 description 1

- 239000007977 PBT buffer Substances 0.000 description 1

- ISWSIDIOOBJBQZ-UHFFFAOYSA-N Phenol Chemical compound OC1=CC=CC=C1 ISWSIDIOOBJBQZ-UHFFFAOYSA-N 0.000 description 1

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 230000000844 anti-bacterial effect Effects 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- 230000003796 beauty Effects 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- AQCDIIAORKRFCD-UHFFFAOYSA-N cadmium selenide Chemical compound [Cd]=[Se] AQCDIIAORKRFCD-UHFFFAOYSA-N 0.000 description 1

- 229910052980 cadmium sulfide Inorganic materials 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000008094 contradictory effect Effects 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000005496 eutectics Effects 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000005555 metalworking Methods 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 239000012811 non-conductive material Substances 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 229920001707 polybutylene terephthalate Polymers 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000002096 quantum dot Substances 0.000 description 1

- 230000003014 reinforcing effect Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 229910052712 strontium Inorganic materials 0.000 description 1

- 229910052714 tellurium Inorganic materials 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/52—Encapsulations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/64—Heat extraction or cooling elements

- H01L33/647—Heat extraction or cooling elements the elements conducting electric current to or from the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/62—Arrangements for conducting electric current to or from the semiconductor body, e.g. lead-frames, wire-bonds or solder balls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/64—Heat extraction or cooling elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0008—Processes

- H01L2933/0033—Processes relating to semiconductor body packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/483—Containers

- H01L33/486—Containers adapted for surface mounting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/58—Optical field-shaping elements

- H01L33/60—Reflective elements

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Led Device Packages (AREA)

- Light Receiving Elements (AREA)

- Control And Other Processes For Unpacking Of Materials (AREA)

- Lead Frames For Integrated Circuits (AREA)

Description

Claims (6)

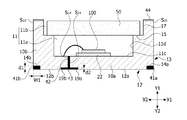

- 底面および側壁を含むキャビティを含む金属胴体と、

前記キャビティ内に配置される発光素子と、

前記金属胴体の底面に配置され、第1貫通ホールおよび第2貫通ホールを含む樹脂部と、

前記金属胴体上に配置される透光部材と、を含み、

前記金属胴体は、第1金属胴体と、第2金属胴体と、前記第1金属胴体と前記第2金属胴体との間に配置される絶縁部材と、を含み、

前記第1金属胴体の一部、前記第2金属胴体の一部、および、前記絶縁部材の一部は、前記キャビティの底面に位置し、

前記発光素子は、前記第1金属胴体の一部および前記第2金属胴体の一部と電気的に連結され、

前記第1金属胴体および前記第2金属胴体それぞれは、前記金属胴体の底面から突出した第1突出部および第2突出部をそれぞれ含み、

前記金属胴体は、前記第1突出部および前記第2突出部と前記絶縁部材との間の第1領域と、前記第1突出部および前記第2突出部と前記キャビティの底面とが垂直に重なる第2領域と、前記キャビティの外側に配置されて前記金属胴体の最上部面と重なる第3領域と、を含み、

前記第1領域の厚さは前記第2領域の厚さより薄く、

前記第2領域の厚さは前記第3領域の厚さより薄く、

前記第3領域は、前記キャビティから最も遠い領域の厚さが、前記キャビティから最も近い領域の厚さより薄く、

前記第1突出部および前記第2突出部は、前記第1貫通ホールおよび前記第2貫通ホール内にそれぞれ配置され、

前記第1突出部は前記第2突出部より大きく、

前記発光素子は紫外線光を出射し、前記第1突出部および前記第2突出部はアルミニウムを含み、

前記金属胴体は、前記第1金属胴体および前記第2金属胴体の底面に設置されている第1溝と、前記第1突出部と前記第2突出部との間に設置されている第2溝と、を含み、

前記第1溝は前記金属胴体の周辺に沿って閉ループ形状に形成されて前記第1金属胴体および前記第2金属胴体の底面が露出し、

前記第2溝は両終端が前記第1溝と連結され、

前記第1溝および前記第2溝には前記樹脂部が配置され、

前記第2溝の水平方向の幅は前記絶縁部材の水平方向の幅より大きく、

前記第1溝および前記第2溝に配置された樹脂部の材質は前記絶縁部材の材質と異なる、発光素子パッケージ。 - 前記第1突出部と前記第2突出部の面積比は1:0.2〜1:0.6である、請求項1に記載の半導体素子パッケージ。

- 前記第1突出部と前記第2突出部との間の間隔は前記絶縁部材の幅より大きい、請求項1に記載の半導体素子パッケージ。

- 前記第2溝の水平方向の幅は前記第1溝に配置された樹脂部の水平方向の幅より大きい、請求項1に記載の発光素子パッケージ。

- 前記第1溝に配置された樹脂部の高さは前記第2溝に配置された樹脂部の高さより高い、請求項4に記載の発光素子パッケージ。

- 前記キャビティ内の前記発光素子は100nm〜280nmの範囲にピーク波長を含む光を放射するように構成される、請求項1に記載の発光素子パッケージ。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2017-0113439 | 2017-09-05 | ||

| KR20170113439 | 2017-09-05 | ||

| KR1020180101576A KR102641336B1 (ko) | 2017-09-05 | 2018-08-28 | 반도체 소자 패키지 |

| KR10-2018-0101576 | 2018-08-28 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019047123A JP2019047123A (ja) | 2019-03-22 |

| JP2019047123A5 JP2019047123A5 (ja) | 2019-06-13 |

| JP6755911B2 true JP6755911B2 (ja) | 2020-09-16 |

Family

ID=65761758

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018165079A Active JP6755911B2 (ja) | 2017-09-05 | 2018-09-04 | 半導体素子パッケージ |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US11335843B2 (ja) |

| JP (1) | JP6755911B2 (ja) |

| KR (1) | KR102641336B1 (ja) |

| CN (1) | CN109427946B (ja) |

| TW (1) | TWI802587B (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102650690B1 (ko) * | 2018-10-23 | 2024-03-25 | 주식회사 루멘스 | Uv led 패키지 |

| WO2021014904A1 (ja) * | 2019-07-25 | 2021-01-28 | 株式会社大真空 | 発光装置のリッド材、リッド材の製造方法および発光装置 |

| JP7370274B2 (ja) * | 2020-02-18 | 2023-10-27 | 日機装株式会社 | 半導体パッケージ及び半導体発光装置 |

| JP7450466B2 (ja) * | 2020-06-22 | 2024-03-15 | スタンレー電気株式会社 | 発光装置及び発光装置の製造方法 |

Family Cites Families (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4003866B2 (ja) * | 2001-12-04 | 2007-11-07 | シチズン電子株式会社 | 表面実装型発光ダイオード及びその製造方法 |

| JP2003304000A (ja) | 2002-04-08 | 2003-10-24 | Citizen Electronics Co Ltd | 発光ダイオード用パッケージの製造方法 |

| KR100593943B1 (ko) | 2005-04-30 | 2006-06-30 | 삼성전기주식회사 | 발광 다이오드 패키지의 제조 방법 |

| US8044418B2 (en) * | 2006-07-13 | 2011-10-25 | Cree, Inc. | Leadframe-based packages for solid state light emitting devices |

| JP4205135B2 (ja) | 2007-03-13 | 2009-01-07 | シャープ株式会社 | 半導体発光装置、半導体発光装置用多連リードフレーム |

| JP5326705B2 (ja) | 2009-03-17 | 2013-10-30 | 日亜化学工業株式会社 | 発光装置 |

| JP5367668B2 (ja) | 2009-11-17 | 2013-12-11 | スタンレー電気株式会社 | 発光装置およびその製造方法 |

| KR101157530B1 (ko) | 2009-12-16 | 2012-06-22 | 인탑스엘이디 주식회사 | 발광다이오드 패키지 및 그 제조방법 |

| JP5383611B2 (ja) | 2010-01-29 | 2014-01-08 | 株式会社東芝 | Ledパッケージ |

| TW201250964A (en) * | 2011-01-27 | 2012-12-16 | Dainippon Printing Co Ltd | Resin-attached lead frame, method for manufacturing same, and lead frame |

| KR101852388B1 (ko) | 2011-04-28 | 2018-04-26 | 엘지이노텍 주식회사 | 발광 소자 패키지 |

| CN103078040B (zh) | 2011-08-22 | 2016-12-21 | Lg伊诺特有限公司 | 发光器件封装件和光装置 |

| KR101853067B1 (ko) * | 2011-08-26 | 2018-04-27 | 엘지이노텍 주식회사 | 발광 소자 패키지 |

| JP6015231B2 (ja) | 2011-08-26 | 2016-10-26 | 大日本印刷株式会社 | Led素子搭載用基板及びその製造方法、並びにled素子搭載用基板を用いた半導体装置 |

| US9263658B2 (en) * | 2012-03-05 | 2016-02-16 | Seoul Viosys Co., Ltd. | Light-emitting device and method of manufacturing the same |

| KR101400271B1 (ko) | 2012-08-03 | 2014-05-28 | (주)포인트엔지니어링 | 광디바이스 제조 방법 및 이에 의해 제조된 광디바이스 |

| KR101373710B1 (ko) | 2012-12-12 | 2014-03-13 | (주)포인트엔지니어링 | 엘이디 금속기판 패키지 및 그 제조방법 |

| CN104103734B (zh) * | 2013-04-02 | 2017-03-01 | 展晶科技(深圳)有限公司 | 发光二极管封装结构 |

| KR20150001268A (ko) | 2013-06-27 | 2015-01-06 | 엘지이노텍 주식회사 | 발광 소자 패키지 |

| US9583689B2 (en) * | 2013-07-12 | 2017-02-28 | Lite-On Opto Technology (Changzhou) Co., Ltd. | LED package |

| KR101541035B1 (ko) | 2013-08-16 | 2015-08-03 | (주)포인트엔지니어링 | 절단에 따른 버를 방지하는 칩원판 및 이를 제조하는 방법 |

| DE102014102810A1 (de) | 2014-03-04 | 2015-09-10 | Osram Opto Semiconductors Gmbh | Herstellung optoelektronischer Bauelemente |

| DE102014103034A1 (de) | 2014-03-07 | 2015-09-10 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement und Verfahren zu seiner Herstellung |

| SG11201607935WA (en) | 2014-03-25 | 2016-10-28 | 3M Innovative Properties Co | Flexible circuits with coplanar conductive features and methods of making same |

| JP6185415B2 (ja) | 2014-03-27 | 2017-08-23 | 株式会社東芝 | 半導体発光装置 |

| EP3975272A1 (en) * | 2014-05-29 | 2022-03-30 | Suzhou Lekin Semiconductor Co., Ltd. | Light emitting device package |

| CN104037316B (zh) | 2014-06-19 | 2017-06-20 | 鸿利智汇集团股份有限公司 | 一种led无机封装支架及其封装方法 |

| EP3179525B1 (en) | 2014-08-05 | 2018-10-24 | Citizen Electronics Co., Ltd | Semiconductor device and method for producing same |

| KR20160038568A (ko) * | 2014-09-30 | 2016-04-07 | (주)포인트엔지니어링 | 복수의 곡면 캐비티를 포함하는 칩 기판 |

| KR101668353B1 (ko) * | 2014-11-03 | 2016-10-21 | (주)포인트엔지니어링 | 칩 기판 및 칩 패키지 모듈 |

| JP6765804B2 (ja) * | 2014-11-28 | 2020-10-07 | エルジー イノテック カンパニー リミテッド | 発光素子パッケージ |

| US10211378B2 (en) * | 2016-01-29 | 2019-02-19 | Nichia Corporation | Light emitting device and method for manufacturing same |

| US9893250B1 (en) * | 2016-12-16 | 2018-02-13 | Nichia Corporation | Light emitting device having silicone resin-based sealing member |

-

2018

- 2018-08-28 KR KR1020180101576A patent/KR102641336B1/ko active IP Right Grant

- 2018-08-31 US US16/119,469 patent/US11335843B2/en active Active

- 2018-09-04 TW TW107131008A patent/TWI802587B/zh active

- 2018-09-04 JP JP2018165079A patent/JP6755911B2/ja active Active

- 2018-09-05 CN CN201811034004.6A patent/CN109427946B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20190074422A1 (en) | 2019-03-07 |

| JP2019047123A (ja) | 2019-03-22 |

| KR20190026581A (ko) | 2019-03-13 |

| US11335843B2 (en) | 2022-05-17 |

| TWI802587B (zh) | 2023-05-21 |

| TW201921728A (zh) | 2019-06-01 |

| CN109427946A (zh) | 2019-03-05 |

| KR102641336B1 (ko) | 2024-02-28 |

| CN109427946B (zh) | 2022-05-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP3483944B1 (en) | Light emitting device package and lighting apparatus comprising same | |

| JP6755911B2 (ja) | 半導体素子パッケージ | |

| KR20190006889A (ko) | 발광소자 패키지 | |

| US11355674B2 (en) | Semiconductor device package | |

| EP3451396B1 (en) | Semiconductor device package | |

| US11527681B2 (en) | Semiconductor device package | |

| KR102472710B1 (ko) | 반도체 소자 패키지 | |

| KR102537080B1 (ko) | 반도체 소자 패키지 | |

| KR102509075B1 (ko) | 반도체 소자 패키지 | |

| KR102509089B1 (ko) | 반도체 소자 패키지 | |

| KR102531150B1 (ko) | 광학렌즈 및 이를 포함하는 반도체 소자 패키지 | |

| KR102518578B1 (ko) | 반도체 소자 패키지 및 이를 포함하는 발광모듈 | |

| KR102432034B1 (ko) | 반도체 소자 패키지 | |

| KR102689078B1 (ko) | 발광소자 패키지 | |

| US11715817B2 (en) | Light-emitting element package and light-emitting element module including same | |

| KR102644793B1 (ko) | 발광소자 패키지 | |

| KR102401827B1 (ko) | 발광소자 패키지 및 이를 포함하는 조명장치 | |

| US20200357967A1 (en) | Semiconductor device package and light emitting device comprising same | |

| KR20200077180A (ko) | 발광 소자 패키지 | |

| KR20190094721A (ko) | 반도체 소자 패키지 및 이를 포함하는 발광장치 | |

| KR20190094719A (ko) | 반도체 소자 패키지 및 이를 포함하는 발광장치 | |

| KR20190094723A (ko) | 반도체 소자 패키지 및 이를 포함하는 발광장치 | |

| KR20190094720A (ko) | 반도체 소자 패키지 및 이를 포함하는 발광장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190510 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190510 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20190510 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20190821 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190827 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190828 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20191125 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200124 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200324 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200623 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200811 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200826 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6755911 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |