JP6661009B2 - オプトエレクトロニクス半導体部品およびオプトエレクトロニクス半導体部品の製造方法 - Google Patents

オプトエレクトロニクス半導体部品およびオプトエレクトロニクス半導体部品の製造方法 Download PDFInfo

- Publication number

- JP6661009B2 JP6661009B2 JP2018521031A JP2018521031A JP6661009B2 JP 6661009 B2 JP6661009 B2 JP 6661009B2 JP 2018521031 A JP2018521031 A JP 2018521031A JP 2018521031 A JP2018521031 A JP 2018521031A JP 6661009 B2 JP6661009 B2 JP 6661009B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- semiconductor component

- contact

- recess

- metal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 155

- 230000005693 optoelectronics Effects 0.000 title claims description 67

- 238000004519 manufacturing process Methods 0.000 title claims description 46

- 229910052751 metal Inorganic materials 0.000 claims description 162

- 239000002184 metal Substances 0.000 claims description 159

- 238000002347 injection Methods 0.000 claims description 74

- 239000007924 injection Substances 0.000 claims description 74

- 238000000034 method Methods 0.000 claims description 58

- 239000000463 material Substances 0.000 claims description 31

- 230000008569 process Effects 0.000 claims description 22

- 239000000126 substance Substances 0.000 claims description 8

- 238000000151 deposition Methods 0.000 claims description 6

- 239000000203 mixture Substances 0.000 claims description 5

- 238000002310 reflectometry Methods 0.000 claims description 5

- 230000000149 penetrating effect Effects 0.000 claims 1

- 238000009751 slip forming Methods 0.000 claims 1

- 239000010410 layer Substances 0.000 description 317

- 238000002161 passivation Methods 0.000 description 18

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 16

- 239000002800 charge carrier Substances 0.000 description 13

- 229910002601 GaN Inorganic materials 0.000 description 11

- 239000000758 substrate Substances 0.000 description 10

- 238000005530 etching Methods 0.000 description 8

- 230000005855 radiation Effects 0.000 description 8

- 239000011787 zinc oxide Substances 0.000 description 8

- 229910052782 aluminium Inorganic materials 0.000 description 7

- 238000003486 chemical etching Methods 0.000 description 6

- 229910004298 SiO 2 Inorganic materials 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 4

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000001459 lithography Methods 0.000 description 3

- -1 nitride compound Chemical class 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 238000003631 wet chemical etching Methods 0.000 description 3

- 230000008901 benefit Effects 0.000 description 2

- 230000005670 electromagnetic radiation Effects 0.000 description 2

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 230000007480 spreading Effects 0.000 description 2

- 238000003892 spreading Methods 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 238000010292 electrical insulation Methods 0.000 description 1

- 238000005538 encapsulation Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 230000013011 mating Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000001393 microlithography Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 239000000615 nonconductor Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 239000010948 rhodium Substances 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

- H10H20/011—Manufacture or treatment of bodies, e.g. forming semiconductor layers

- H10H20/013—Manufacture or treatment of bodies, e.g. forming semiconductor layers having light-emitting regions comprising only Group III-V materials

- H10H20/0137—Manufacture or treatment of bodies, e.g. forming semiconductor layers having light-emitting regions comprising only Group III-V materials the light-emitting regions comprising nitride materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/831—Electrodes characterised by their shape

- H10H20/8312—Electrodes characterised by their shape extending at least partially through the bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/832—Electrodes characterised by their material

- H10H20/833—Transparent materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/832—Electrodes characterised by their material

- H10H20/835—Reflective materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H29/00—Integrated devices, or assemblies of multiple devices, comprising at least one light-emitting semiconductor element covered by group H10H20/00

- H10H29/10—Integrated devices comprising at least one light-emitting semiconductor component covered by group H10H20/00

- H10H29/14—Integrated devices comprising at least one light-emitting semiconductor component covered by group H10H20/00 comprising multiple light-emitting semiconductor components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

- H10H20/032—Manufacture or treatment of electrodes

Landscapes

- Led Devices (AREA)

Description

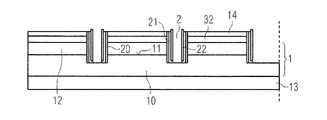

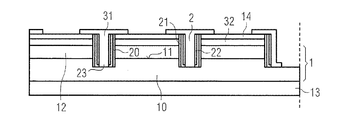

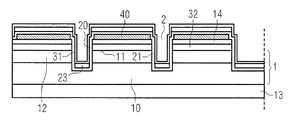

2 凹部

4 像点

5 キャリア

6 放射面

10 第1の層

11 活性層

12 第2の層

13 基板

14 第1のパッシベーション層

15 第2のパッシベーション層

20 第1の透明中間層

21 第1の金属ミラー層

22 第2の絶縁層

23 金属注入要素

31 第1のコンタクト要素

32 第2のコンタクト要素

40 フォトマスク

50 スイッチ

100 オプトエレクトロニクス半導体部品

Claims (20)

- 特定の順序で上下に配置された、第1の主面と、第1の層(10)と、活性層(11)と、第2の層(12)と、第2の主面とを含む半導体積層体(1)と、

前記第2の主面に配置され、前記半導体積層体(1)において前記第2の主面から前記第2の層(12)および前記活性層(11)を完全に貫通して延在して前記第1の層(10)に開口している凹部(2)を充填している第1のコンタクト要素(31)と、

前記第2の主面に平行で、かつ、横方向に互いに離間して前記第2の主面に設けられ、前記第2の主面の平面視において、前記凹部(2)に隣接して側方に配置されている複数の第2のコンタクト要素(32)と、

を備えるオプトエレクトロニクス半導体部品(100)であって、

前記第1のコンタクト要素(31)は、第1の透明中間層(20)と、第1の金属ミラー層(21)と、金属注入要素(23)とを含み、

前記第1の透明中間層(20)は、前記活性層(11)を横切って延びる前記凹部(2)の側壁に配置され、前記半導体積層体(1)に直接接触し、

前記第1の金属ミラー層(21)は、前記側壁の領域において前記第1の透明中間層(20)に直接設けられ、

前記金属注入要素(23)は、前記第1の層(10)に直接隣接する前記凹部(2)の底面に配置され、前記金属注入要素(23)と前記底面との間に更なる金属要素は配置されておらず、

前記第1の層(10)の領域において、前記第1の層(10)と前記第1の金属ミラー層(21)との間に電気的接触が生成され、

前記第1の透明中間層(20)は、動作中に、前記第2の層(12)と前記第1のコンタクト要素(31)との間に直接電流が流れることを防止し、

前記第2のコンタクト要素(32)の輪郭は、動作中に前記第1の主面を見たときに明るくなる前記半導体部品(100)の像点(4)の形状、大きさおよび位置を規定し、

前記金属注入要素(23)および前記第1の金属ミラー層(21)は、異なる材料組成を有し、

前記第2のコンタクト要素(32)はそれぞれ、像点(4)に個別に割り当てられる、

オプトエレクトロニクス半導体部品(100)。 - 前記凹部(2)の前記側壁は、前記第1の金属ミラー層(21)によって少なくとも80%以上覆われており、

前記活性層(11)によって出射される平均波長における前記第1の金属ミラー層(21)の反射率は、少なくとも80%であり、

前記活性層(11)によって出射される平均波長における前記金属注入要素(23)の反射率は、多くとも50%である、

請求項1に記載のオプトエレクトロニクス半導体部品(100)。 - 前記金属注入要素(23)は、前記底面の領域において前記第1の層(10)に直接隣接している、または、

前記底面の領域において、前記金属注入要素(23)と前記第1の層(10)との間に透明層が配置され、前記透明層は、前記金属注入要素(23)および前記第1の層(10)と直接接続されており、前記活性層(11)によって出射される平均波長において少なくとも80%の透明度を有する、

請求項1または2に記載のオプトエレクトロニクス半導体部品(100)。 - 前記第1の透明中間層(20)は、第1の絶縁層(20)であり、前記側壁の領域において前記第1の金属ミラー層(21)と前記半導体積層体(1)との間に直接電流が流れることを防止する、

請求項1から3の何れか1項に記載のオプトエレクトロニクス半導体部品(100)。 - 前記第1の透明中間層(20)は、コンタクト層(20)であり、

前記コンタクト層(20)は、前記第1の層(10)の領域において、前記第1の層(10)と前記第1の金属ミラー層(21)との間に電気的接触を生成し、

前記コンタクト層(20)は、前記第2の層(12)の領域において、前記第1の金属ミラー層(21)と前記第2の層(12)との間で電気絶縁的に作用し、

前記コンタクト層(20)は、前記底面と前記金属注入要素(23)との間に追加的に配置されている、

請求項1から4の何れか1項に記載のオプトエレクトロニクス半導体部品(100)。 - 前記第2のコンタクト要素(32)が連続的に形成され、

前記活性層(11)は、前記活性層(11)上に前記第2のコンタクト要素(32)を投影させた領域に連続的に形成されている、

請求項1から5の何れか1項に記載のオプトエレクトロニクス半導体部品(100)。 - 前記第2のコンタクト要素(32)は、前記像点(4)が互いに独立して明るくなるように、動作中に互いに独立して制御され、

前記凹部(2)は、2つの隣接する第2のコンタクト要素(32)の間の領域に配置される、

請求項1から6の何れか1項に記載のオプトエレクトロニクス半導体部品(100)。 - 少なくとも1つの像点(4)に、それぞれの像点(4)に重複して接触する複数の第1のコンタクト要素(31)が割り当てられる、

請求項1から7の何れか1項に記載のオプトエレクトロニクス半導体部品(100)。 - 前記第1のコンタクト要素(31)の少なくとも1つは、複数の隣接する像点(4)に隣接して側方に配置され、前記複数の隣接する像点(4)と接触するために同時に形成される、

請求項1から8の何れか1項に記載のオプトエレクトロニクス半導体部品(100)。 - 前記像点(4)は、格子網の目に配置され、

少なくとも1つの第1のコンタクト要素(31)の少なくとも1つの凹部(2)は、前記格子網の少なくとも1つの交点に配置される、

請求項7に記載のオプトエレクトロニクス半導体部品(100)。 - 前記凹部(2)は、溝(2)として形成され、

前記溝(2)および前記金属注入要素(23)はそれぞれ、前記第2の主面の平面視において、前記第2のコンタクト要素(32)を完全に囲む連続軌道を形成する、

請求項1から10の何れか1項に記載のオプトエレクトロニクス半導体部品(100)。 - 前記溝(2)は、個々の前記第2のコンタクト要素(32)の周りに接続され、前記第2のコンタクト要素(32)の周りに格子を形成し、

連続的な前記溝(2)には、動作中に複数の像点(4)に同時に接触する単一の連続的な第1のコンタクト要素(31)が形成される、

請求項7または11に記載のオプトエレクトロニクス半導体部品(100)。 - 前記金属注入要素(23)と前記第1の金属ミラー層(21)との間において、第2の絶縁層(22)が前記凹部(2)の前記側壁の領域に配置される、

請求項12に記載のオプトエレクトロニクス半導体部品(100)。 - 前記金属注入要素(23)は、前記凹部(2)の前記底面に層として設けられ、

前記第1の金属ミラー層は、反射性充填材料として前記凹部(2)に導入され、前記金属注入要素(23)と前記第2の主面との間の領域を完全にまたは少なくとも部分的に充填する、

請求項1から13の何れか1項に記載のオプトエレクトロニクス半導体部品(100)。 - A)第1の主面と、前記第1の主面上の第1の層(10)と、前記第1の層(10)上の活性層(11)と、前記活性層(11)上の第2の層(12)と、前記第2の層(12)上の第2の主面とを有する半導体積層体(1)を設ける工程と、

B)前記第2の主面において、前記活性層の主延在方向に平行である側方に互いに離間して配置されるように、複数の第2のコンタクト要素(32)を設ける工程と、

C)前記第2の層(12)および前記活性層(11)を完全に貫通して前記第1の層(10)に開口し、前記第2の主面の平面視において、前記第2のコンタクト要素(32)に隣接して側方に配置される凹部(2)を、前記第2の主面から前記半導体積層体(1)の中に穴または溝の形態で導入する工程と、

D)第1の透明中間層(20)が前記半導体積層体(1)に直接隣接するように、前記活性層(11)に対して側方に延びる前記凹部(2)の底面および側壁の全領域に前記第1の透明中間層(20)を設け、続いて、自己整合エッチングバックプロセスによって前記底面から前記第1の透明中間層(20)が除去される工程と、

E)前記側壁の領域において、第1の金属ミラー層(21)を前記第1の透明中間層(20)に直接設ける工程と、

F)前記第1の層(10)に直接隣接する前記凹部(2)の前記底面に金属注入要素(23)を設ける工程と、

を含み、

前記金属注入要素(23)と前記底面との間に更なる金属要素は配置されておらず、

前記金属注入要素(23)および前記第1の金属ミラー層(21)は、異なる材料組成を有する、

オプトエレクトロニクス半導体部品(100)の製造方法。 - 工程D)において、

乾式化学エッチバックプロセスによって前記底面から前記第1の透明中間層(20)が除去され、

前記第1の透明中間層(20)の前記エッチバックプロセスは、リソグラフィマスクを使用せずに実行される、

請求項15に記載のオプトエレクトロニクス半導体部品(100)の製造方法。 - 工程D)において、

前記第1の層(10)の領域において、前記第1の層(10)と前記第1の金属ミラー層(21)との間に電気的接触が生成される、

請求項15または16に記載のオプトエレクトロニクス半導体部品(100)の製造方法。 - 工程E)において、

前記第1の金属ミラー層(21)は、前記凹部(2)の前記底面および前記側壁の全領域に設けられ、

続いて、湿式化学または乾式化学エッチバックプロセスによって前記底面から前記第1の金属ミラー層(21)が除去され、

前記第1の金属ミラー層(21)の前記エッチバックプロセスは、自己整合的であり、リソグラフィマスクを使用せずに実行される、

請求項15から17の何れか1項に記載のオプトエレクトロニクス半導体部品(100)の製造方法。 - 前記第1の金属ミラー層(21)を設けた後、かつ、前記第1の金属ミラー層(21)の前記エッチバックプロセス前に、

第2の絶縁層(22)が、前記凹部(2)の前記底面および前記側壁の領域において、前記第1の金属ミラー層(21)の全領域に設けられ、

続いて、乾式化学エッチバックプロセスによって、前記底面の領域において前記第1の金属ミラー層(21)から前記第2の絶縁層(22)が除去され、

前記第2の絶縁層(22)の前記エッチバックプロセスは、自己整合的であり、リソグラフィマスクを使用せずに実行される、

請求項18に記載のオプトエレクトロニクス半導体部品(100)の製造方法。 - 工程F)は、工程E)の前に実行され、

工程F)において、前記金属注入要素(23)は、異方性堆積法によって前記凹部(2)の前記底面上に層として形成され、

工程E)において、前記凹部(2)は、前記第1の金属ミラー層(21)を形成する反射性材料で充填される、

請求項15から17の何れか1項に記載のオプトエレクトロニクス半導体部品(100)の製造方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102015119353.1 | 2015-11-10 | ||

| DE102015119353.1A DE102015119353B4 (de) | 2015-11-10 | 2015-11-10 | Optoelektronisches Halbleiterbauteil und Verfahren zur Herstellung eines optoelektronischen Halbleiterbauteils |

| PCT/EP2016/077149 WO2017081085A1 (de) | 2015-11-10 | 2016-11-09 | Optoelektronisches halbleiterbauteil und verfahren zur herstellung eines optoelektronischen halbleiterbauteils |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018533220A JP2018533220A (ja) | 2018-11-08 |

| JP6661009B2 true JP6661009B2 (ja) | 2020-03-11 |

Family

ID=57249827

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018521031A Active JP6661009B2 (ja) | 2015-11-10 | 2016-11-09 | オプトエレクトロニクス半導体部品およびオプトエレクトロニクス半導体部品の製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10374121B2 (ja) |

| JP (1) | JP6661009B2 (ja) |

| CN (1) | CN108292696B (ja) |

| DE (1) | DE102015119353B4 (ja) |

| WO (1) | WO2017081085A1 (ja) |

Families Citing this family (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102017117414A1 (de) * | 2017-08-01 | 2019-02-07 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Bauelements und optoelektronisches Bauelement |

| FR3073669B1 (fr) * | 2017-11-10 | 2021-11-05 | Commissariat Energie Atomique | Procede de fabrication d'un dispositif optoelectronique comprenant une pluralite de diodes |

| US11749790B2 (en) * | 2017-12-20 | 2023-09-05 | Lumileds Llc | Segmented LED with embedded transistors |

| FR3076170B1 (fr) * | 2017-12-22 | 2020-05-15 | Commissariat A L'energie Atomique Et Aux Energies Alternatives | Procede de report de structures electroluminescentes |

| DE102019101544A1 (de) | 2018-01-24 | 2019-07-25 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement und Verfahren |

| DE102018106970A1 (de) | 2018-03-23 | 2019-09-26 | Osram Opto Semiconductors Gmbh | Optoelektronisches Halbleiterbauelement und Verfahren zur Herstellung eines optoelektronischen Halbleiterbauelements |

| US10615305B1 (en) * | 2018-04-20 | 2020-04-07 | Facebook Technologies, Llc | Self-alignment of micro light emitting diode using planarization |

| JP7105612B2 (ja) * | 2018-05-21 | 2022-07-25 | シャープ株式会社 | 画像表示素子およびその形成方法 |

| DE102018122492A1 (de) * | 2018-09-14 | 2020-03-19 | Osram Opto Semiconductors Gmbh | Optoelektronisches halbleiterbauelement mit einer ersten und zweiten metallschicht sowie verfahren zur herstellung des optoelektronischen halbleiterbauelements |

| FR3087580B1 (fr) * | 2018-10-23 | 2020-12-18 | Aledia | Procede de realisation d’un dispositif optoelectronique comprenant des diodes electroluminescentes homogenes en dimensions |

| JPWO2020100303A1 (ja) * | 2018-11-16 | 2021-10-07 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| WO2020100299A1 (ja) * | 2018-11-16 | 2020-05-22 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| US20210358998A1 (en) * | 2018-11-16 | 2021-11-18 | Sakai Display Products Corporation | Micro led device and production method therefor |

| US20220013511A1 (en) * | 2018-11-16 | 2022-01-13 | Sakai Display Products Corporation | Micro led device and method for manufacturing same |

| WO2020100300A1 (ja) * | 2018-11-16 | 2020-05-22 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| WO2020100290A1 (ja) * | 2018-11-16 | 2020-05-22 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| JPWO2020100292A1 (ja) * | 2018-11-16 | 2021-09-24 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| WO2020100294A1 (ja) * | 2018-11-16 | 2020-05-22 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| US20210408341A1 (en) * | 2018-11-16 | 2021-12-30 | Sakai Display Products Corporation | Micro led device and production method therefor |

| JPWO2020100296A1 (ja) * | 2018-11-16 | 2021-09-09 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| JPWO2020100295A1 (ja) * | 2018-11-16 | 2021-10-07 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| WO2020100301A1 (ja) * | 2018-11-16 | 2020-05-22 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| CN112956038A (zh) * | 2018-11-16 | 2021-06-11 | 堺显示器制品株式会社 | 微型led装置及其制造方法 |

| WO2020100298A1 (ja) * | 2018-11-16 | 2020-05-22 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| JPWO2020115851A1 (ja) * | 2018-12-06 | 2021-10-14 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| JPWO2020121449A1 (ja) * | 2018-12-12 | 2021-10-21 | 堺ディスプレイプロダクト株式会社 | マイクロledデバイスおよびその製造方法 |

| DE102018132651A1 (de) * | 2018-12-18 | 2020-06-18 | Osram Opto Semiconductors Gmbh | Optoelektronisches halbleiterbauteil |

| US20220013577A1 (en) * | 2018-12-27 | 2022-01-13 | Sakai Display Products Corporation | Micro-led device and manufacturing method thereof |

| US20220093579A1 (en) * | 2019-01-28 | 2022-03-24 | Sakai Display Products Corporation | Micro led device and method for manufacturing same |

| DE102019106419A1 (de) * | 2019-03-13 | 2020-09-17 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Optoelektronischer halbleiterchip und verfahren zum herstellen eines optoelektronischen halbleiterchips |

| DE102019106546A1 (de) * | 2019-03-14 | 2020-09-17 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Verfahren zur herstellung von optoelektronischen halbleiterbauteilen und optoelektronisches halbleiterbauteil |

| JPWO2020194387A1 (ja) * | 2019-03-22 | 2020-10-01 | ||

| CN113614935A (zh) * | 2019-03-22 | 2021-11-05 | 堺显示器制品株式会社 | 微型led紫外辐射源及其制造方法 |

| DE102019121678B4 (de) * | 2019-08-12 | 2025-02-20 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Bauelement mit verbesserter wärmeabfuhr und verfahren zur herstellung eines bauelements |

| FR3103634B1 (fr) * | 2019-11-21 | 2021-12-03 | Commissariat Energie Atomique | Procede de formation d’une electrode commune d’une pluralite de dispositifs optoelectroniques |

| US11569415B2 (en) * | 2020-03-11 | 2023-01-31 | Lumileds Llc | Light emitting diode devices with defined hard mask opening |

| US11942507B2 (en) * | 2020-03-11 | 2024-03-26 | Lumileds Llc | Light emitting diode devices |

| US11848402B2 (en) * | 2020-03-11 | 2023-12-19 | Lumileds Llc | Light emitting diode devices with multilayer composite film including current spreading layer |

| US20210288222A1 (en) * | 2020-03-11 | 2021-09-16 | Lumileds Llc | Light Emitting Diode Devices With Common Electrode |

| US11735695B2 (en) * | 2020-03-11 | 2023-08-22 | Lumileds Llc | Light emitting diode devices with current spreading layer |

| WO2023058308A1 (ja) * | 2021-10-05 | 2023-04-13 | 株式会社ジャパンディスプレイ | 発光装置および発光装置形成基板 |

| US11935987B2 (en) * | 2021-11-03 | 2024-03-19 | Lumileds Llc | Light emitting diode arrays with a light-emitting pixel area |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102005053274A1 (de) * | 2005-09-30 | 2007-04-12 | Osram Opto Semiconductors Gmbh | Verfahren zum Herstellen einer Mehrzahl von Halbleiterchips und Halbleiterbauelement |

| US8575633B2 (en) * | 2008-12-08 | 2013-11-05 | Cree, Inc. | Light emitting diode with improved light extraction |

| US8368100B2 (en) * | 2007-11-14 | 2013-02-05 | Cree, Inc. | Semiconductor light emitting diodes having reflective structures and methods of fabricating same |

| DE102008011848A1 (de) * | 2008-02-29 | 2009-09-03 | Osram Opto Semiconductors Gmbh | Optoelektronischer Halbleiterkörper und Verfahren zur Herstellung eines solchen |

| CN102576783A (zh) * | 2009-07-30 | 2012-07-11 | 3M创新有限公司 | 像素化led |

| KR101630152B1 (ko) * | 2010-02-24 | 2016-06-14 | 엘지디스플레이 주식회사 | 하이브리드 발광다이오드 칩과 이를 포함하는 발광다이오드 소자 및 이의 제조방법 |

| TWI470832B (zh) | 2010-03-08 | 2015-01-21 | Lg伊諾特股份有限公司 | 發光裝置 |

| KR101154320B1 (ko) * | 2010-12-20 | 2012-06-13 | 엘지이노텍 주식회사 | 발광소자, 발광소자 패키지 및 이를 포함하는 조명 장치 |

| TWI435477B (zh) * | 2010-12-29 | 2014-04-21 | Lextar Electronics Corp | 高亮度發光二極體 |

| DE102011056888A1 (de) | 2011-12-22 | 2013-06-27 | Osram Opto Semiconductors Gmbh | Anzeigevorrichtung und Verfahren zur Herstellung einer Anzeigevorrichtung |

| US8816383B2 (en) * | 2012-07-06 | 2014-08-26 | Invensas Corporation | High performance light emitting diode with vias |

| DE102012107921A1 (de) | 2012-08-28 | 2014-03-06 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Halbleiterchips |

| DE102012110836A1 (de) * | 2012-11-12 | 2014-02-27 | Osram Opto Semiconductors Gmbh | Optoelektronischer Halbleiterchip und Verfahren zur Herstellung von optoelektronischen Halbleiterchips |

| DE102012112302A1 (de) | 2012-12-14 | 2014-06-18 | Osram Opto Semiconductors Gmbh | Anzeigevorrichtung und Verfahren zur Herstellung einer Anzeigevorrichtung |

| WO2014105403A1 (en) * | 2012-12-31 | 2014-07-03 | Invensas Corporation | High performance light emitting diode |

| DE102013102667A1 (de) | 2013-03-15 | 2014-10-02 | Osram Opto Semiconductors Gmbh | Anzeigevorrichtung |

| FR3007580B1 (fr) * | 2013-06-25 | 2016-10-21 | Commissariat Energie Atomique | Dispositif optoelectronique a reflectivite amelioree |

| DE102013112881A1 (de) | 2013-11-21 | 2015-05-21 | Osram Opto Semiconductors Gmbh | Optoelektronischer Halbleiterchip |

| DE102014101896A1 (de) | 2014-02-14 | 2015-08-20 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Halbleiterbauteils sowie optoelektronisches Halbleiterbauteil |

| JP2015177087A (ja) | 2014-03-17 | 2015-10-05 | スタンレー電気株式会社 | 半導体発光装置とその製造方法 |

| DE102014112750A1 (de) | 2014-09-04 | 2016-03-10 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Halbleiterbauteils und optoelektronisches Halbleiterbauteil |

| CN104952995B (zh) * | 2015-05-05 | 2017-08-25 | 湘能华磊光电股份有限公司 | 一种iii族半导体发光器件的倒装结构 |

| DE102015108532A1 (de) | 2015-05-29 | 2016-12-01 | Osram Opto Semiconductors Gmbh | Anzeigevorrichtung mit einer Mehrzahl getrennt voneinander betreibbarer Bildpunkte |

| DE102015116865B4 (de) | 2015-10-05 | 2025-07-10 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Verfahren zur Herstellung eines Halbleiterchips und Halbleiterchip |

-

2015

- 2015-11-10 DE DE102015119353.1A patent/DE102015119353B4/de active Active

-

2016

- 2016-11-09 WO PCT/EP2016/077149 patent/WO2017081085A1/de not_active Ceased

- 2016-11-09 JP JP2018521031A patent/JP6661009B2/ja active Active

- 2016-11-09 CN CN201680065573.XA patent/CN108292696B/zh active Active

- 2016-11-09 US US15/774,960 patent/US10374121B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20180331251A1 (en) | 2018-11-15 |

| WO2017081085A1 (de) | 2017-05-18 |

| US10374121B2 (en) | 2019-08-06 |

| DE102015119353B4 (de) | 2024-01-25 |

| CN108292696B (zh) | 2021-03-05 |

| JP2018533220A (ja) | 2018-11-08 |

| DE102015119353A1 (de) | 2017-05-11 |

| CN108292696A (zh) | 2018-07-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6661009B2 (ja) | オプトエレクトロニクス半導体部品およびオプトエレクトロニクス半導体部品の製造方法 | |

| US10516083B2 (en) | Light emitting diode module for surface mount technology and method of manufacturing the same | |

| US10978618B2 (en) | Semiconductor light emitting device | |

| JP5362704B2 (ja) | オプトエレクトロニクス半導体ボディおよびその製造方法 | |

| TWI472062B (zh) | 半導體發光裝置及其製造方法 | |

| US10734439B2 (en) | Method for producing an optoelectronic device comprising a plurality of gallium nitride diodes | |

| US9343644B2 (en) | Light emitting diode module for surface mount technology and method of manufacturing the same | |

| US7994519B2 (en) | Semiconductor chip and method for producing a semiconductor chip | |

| US7649193B2 (en) | Semiconductor body and semiconductor chip comprising a semiconductor body | |

| KR102453674B1 (ko) | 표시 장치 및 이러한 장치를 제조하기 위한 방법 | |

| KR20120018080A (ko) | 발광 다이오드 구조체 및 그 제조 방법 | |

| KR20140121608A (ko) | 발광 다이오드의 반사전극, 이를 포함하는 발광 다이오드 칩, 및 이들의 제조방법들 | |

| TW201312792A (zh) | 發光二極體結構及其製造方法 | |

| US11239392B2 (en) | Optoelectronic semiconductor chip, high-voltage semiconductor chip and method for producing an optoelectronic semiconductor chip | |

| KR20130044909A (ko) | 발광소자 및 그 제조방법 | |

| KR20170084148A (ko) | 상부 접점 아래에 트렌치를 갖는 발광 디바이스 | |

| KR20110135103A (ko) | 반도체 발광 소자 및 그 제조 방법 | |

| US12284845B2 (en) | Semiconductor light emitting device having reflective electrode on multilayer insulating structure | |

| KR102234117B1 (ko) | 발광소자 및 조명시스템 | |

| KR101364773B1 (ko) | 개별 전류 경로의 단위셀들을 갖춘 발광다이오드 및 그제조방법 | |

| KR20170099207A (ko) | 발광 소자 및 이의 제조 방법 | |

| KR20150037215A (ko) | 넓은 지향각을 갖는 발광 소자 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180521 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180521 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190425 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190604 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20190719 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20190724 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190814 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200121 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200210 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6661009 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |