JP6643975B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP6643975B2 JP6643975B2 JP2016256337A JP2016256337A JP6643975B2 JP 6643975 B2 JP6643975 B2 JP 6643975B2 JP 2016256337 A JP2016256337 A JP 2016256337A JP 2016256337 A JP2016256337 A JP 2016256337A JP 6643975 B2 JP6643975 B2 JP 6643975B2

- Authority

- JP

- Japan

- Prior art keywords

- pressure

- metal layer

- sintered metal

- bonding

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/4501—Shape

- H01L2224/45012—Cross-sectional shape

- H01L2224/45014—Ribbon connectors, e.g. rectangular cross-section

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49175—Parallel arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

Landscapes

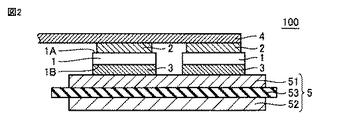

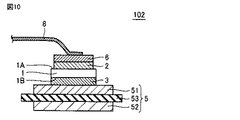

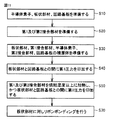

- Die Bonding (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016256337A JP6643975B2 (ja) | 2016-12-28 | 2016-12-28 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016256337A JP6643975B2 (ja) | 2016-12-28 | 2016-12-28 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018110149A JP2018110149A (ja) | 2018-07-12 |

| JP2018110149A5 JP2018110149A5 (enExample) | 2018-12-27 |

| JP6643975B2 true JP6643975B2 (ja) | 2020-02-12 |

Family

ID=62844633

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016256337A Active JP6643975B2 (ja) | 2016-12-28 | 2016-12-28 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6643975B2 (enExample) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113169083B (zh) * | 2019-06-20 | 2024-12-31 | 富士电机株式会社 | 半导体装置以及半导体装置的制造方法 |

| JP7484097B2 (ja) * | 2019-07-18 | 2024-05-16 | 株式会社レゾナック | 半導体装置 |

| JP7247053B2 (ja) * | 2019-08-02 | 2023-03-28 | 株式会社東芝 | 半導体装置 |

| JP7404208B2 (ja) * | 2020-09-24 | 2023-12-25 | 株式会社東芝 | 半導体装置 |

| CN116529876A (zh) * | 2020-11-27 | 2023-08-01 | 罗姆股份有限公司 | 半导体装置 |

| EP4503104A4 (en) | 2022-03-30 | 2025-07-02 | Mitsui Mining & Smelting Co Ltd | METHOD FOR PRODUCING BOUND BODY AND METHOD FOR BONDING BODIES TO BE BOUND |

| JP2025077454A (ja) * | 2023-11-06 | 2025-05-19 | ミネベアパワーデバイス株式会社 | 半導体装置 |

| WO2026003997A1 (ja) * | 2024-06-26 | 2026-01-02 | 三菱電機株式会社 | 半導体装置の製造方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5542567B2 (ja) * | 2010-07-27 | 2014-07-09 | 三菱電機株式会社 | 半導体装置 |

| JP2014029897A (ja) * | 2012-07-31 | 2014-02-13 | Hitachi Ltd | 導電性接合体およびそれを用いた半導体装置 |

| JP6147176B2 (ja) * | 2013-12-02 | 2017-06-14 | 三菱電機株式会社 | 半導体素子の基板への接合方法 |

-

2016

- 2016-12-28 JP JP2016256337A patent/JP6643975B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018110149A (ja) | 2018-07-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6643975B2 (ja) | 半導体装置の製造方法 | |

| JP6171622B2 (ja) | パワーモジュール用基板、パワーモジュール及びパワーモジュール用基板を製造する方法 | |

| US12057375B2 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| JP3846699B2 (ja) | 半導体パワーモジュールおよびその製造方法 | |

| JP5193452B2 (ja) | パワー半導体素子とハウジングとを備えた装置の製造方法 | |

| JP6143687B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| CN103635997A (zh) | 用于制造结构化的烧结连接层的方法以及具有结构化的烧结连接层的半导体器件 | |

| JP6366766B2 (ja) | 半導体装置 | |

| JP6881304B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| WO2016125419A1 (ja) | 半導体装置 | |

| CN109216234B (zh) | 用于处理半导体衬底的设备和方法 | |

| CN105531818A (zh) | 半导体装置的制造方法以及半导体装置 | |

| CN114078790B (zh) | 功率半导体模块装置及其制造方法 | |

| JP5954374B2 (ja) | 絶縁基板、その製造方法、半導体モジュールおよび半導体装置 | |

| CN117594465A (zh) | 半导体模块的制造方法 | |

| JP7351134B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| US9768036B2 (en) | Power semiconductor substrates with metal contact layer and method of manufacture thereof | |

| JP2001267475A (ja) | 半導体装置の実装構造およびその実装方法 | |

| JP6019790B2 (ja) | 接合方法及び接合部材 | |

| JP2014053406A (ja) | 半導体装置およびその製造方法 | |

| JP2014143342A (ja) | 半導体モジュール及びその製造方法 | |

| JP5630375B2 (ja) | 絶縁基板、その製造方法、半導体モジュールおよび半導体装置 | |

| TWI733011B (zh) | 電子零件安裝模組之製造方法 | |

| JP2006013420A (ja) | 電子部品収納用パッケージおよび電子装置 | |

| JP2021015964A (ja) | 半導体パッケージ、電子装置、および半導体パッケージの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181107 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20181107 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190802 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190806 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191003 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20191210 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200107 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6643975 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |