JP6469427B2 - 表示装置 - Google Patents

表示装置 Download PDFInfo

- Publication number

- JP6469427B2 JP6469427B2 JP2014245419A JP2014245419A JP6469427B2 JP 6469427 B2 JP6469427 B2 JP 6469427B2 JP 2014245419 A JP2014245419 A JP 2014245419A JP 2014245419 A JP2014245419 A JP 2014245419A JP 6469427 B2 JP6469427 B2 JP 6469427B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- wirings

- display device

- layer

- wiring layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000758 substrate Substances 0.000 claims description 82

- 239000007769 metal material Substances 0.000 claims description 5

- 229910010272 inorganic material Inorganic materials 0.000 claims 1

- 239000011147 inorganic material Substances 0.000 claims 1

- 239000010410 layer Substances 0.000 description 248

- 239000010408 film Substances 0.000 description 88

- 238000000926 separation method Methods 0.000 description 40

- 239000004973 liquid crystal related substance Substances 0.000 description 35

- 230000004048 modification Effects 0.000 description 22

- 238000012986 modification Methods 0.000 description 22

- 101000894525 Homo sapiens Transforming growth factor-beta-induced protein ig-h3 Proteins 0.000 description 20

- 102100021398 Transforming growth factor-beta-induced protein ig-h3 Human genes 0.000 description 20

- 208000028485 lattice corneal dystrophy type I Diseases 0.000 description 20

- 230000005684 electric field Effects 0.000 description 15

- 238000000034 method Methods 0.000 description 13

- 239000000463 material Substances 0.000 description 11

- 239000011347 resin Substances 0.000 description 11

- 229920005989 resin Polymers 0.000 description 11

- 230000002093 peripheral effect Effects 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 8

- 239000002184 metal Substances 0.000 description 8

- 239000003566 sealing material Substances 0.000 description 8

- 239000004065 semiconductor Substances 0.000 description 8

- 239000002356 single layer Substances 0.000 description 5

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 238000005401 electroluminescence Methods 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 239000011521 glass Substances 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 101000685663 Homo sapiens Sodium/nucleoside cotransporter 1 Proteins 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 102100023116 Sodium/nucleoside cotransporter 1 Human genes 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 150000002894 organic compounds Chemical class 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 239000000565 sealant Substances 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- OFIYHXOOOISSDN-UHFFFAOYSA-N tellanylidenegallium Chemical compound [Te]=[Ga] OFIYHXOOOISSDN-UHFFFAOYSA-N 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13452—Conductors connecting driver circuitry and terminals of panels

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/133345—Insulating layers

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Liquid Crystal (AREA)

Description

前記第1面は、前記表示機能層を駆動するための複数の表示素子が配列された表示素子部と、前記表示素子部に供給される信号が入力される入力部と、前記表示素子部と前記入力部とを電気的に接続する引出配線部と、を有し、

前記引出配線部は、絶縁膜を介して積層された複数の配線層を有し、

前記複数の配線層には、第1の配線幅の複数の第1配線が形成された第1配線層と、前記第1の配線幅よりも狭い第2の配線幅の複数の第2配線が形成された第2配線層と、が含まれ、

前記複数の第2配線の数は、前記複数の第1配線の数よりも多い。

前記基板の前記第1辺と前記表示素子部との間には、前記第1辺側から前記入力部、および前記引出配線部が順に設けられ、

前記第1方向における前記入力部の長さは、前記第1方向における前記表示素子部の長さよりも短くても良い。

前記引出配線部は、

前記表示素子部と前記入力部との間において、前記複数の第1配線および前記複数の第2配線を含む複数の引出配線が前記第2方向に沿って延びる第1部分と、

前記第1部分と前記入力部との間において、前記複数の引出配線が前記第2方向および前記第1方向と交差する第3方向に沿って延びる第2部分と、

前記第2部分と前記入力部との間において、前記複数の引出配線が前記第2方向に沿って延びる第3部分と、

を有し、

平面視において、前記複数の第1配線と、前記複数の第2配線とは互いに重ならなくても良い。

前記複数の第1配線は、第1離間距離で配列され、

前記複数の第2配線は、前記第1離間距離よりも小さい第2離間距離で配列されていても良い。

前記ゲート電極は、前記第1配線層と同層に形成されていても良い。

前記複数の第2配線の数は、前記複数の第3配線の数よりも多くても良い。

前記第2配線層と前記第3配線層との間には、前記第1絶縁膜よりも厚い第2絶縁膜が設けられ、

平面視において、前記複数の第1配線と前記複数の第2配線とは互いに重ならず、かつ、前記複数の第3配線は、前記複数の第1配線および前記複数の第2配線のうちの一部と重なっていても良い。

前記引出配線部は、

前記表示素子部と前記入力部との間において、前記複数の第1配線、前記複数の第2配線、および前記複数の第3配線を含む複数の引出配線が前記第2方向に沿って延びる第1部分と、

前記第1部分と前記入力部との間において、前記複数の引出配線が前記第2方向および前記第1方向と交差する第3方向に沿って延びる第2部分と、

前記第2部分と前記入力部との間において、前記複数の引出配線が前記第2方向に沿って延びる第3部分と、

を有し、

前記第1配線層と前記第2配線層との間には、無機絶縁膜である第1絶縁膜が設けられ、

前記第2配線層と前記第3配線層との間には、有機絶縁膜である第2絶縁膜が設けられ、

前記引出配線部の前記第3部分には、前記第2絶縁膜を厚さ方向に貫通するように前記第1方向に沿って延びる開口部が設けらていても良い。

前記回路部は、前記表示機能層が形成された表示領域と重なる位置に複数の表示素子が配列された表示素子部と、前記表示素子部に前記表示機能層を駆動する信号を伝送する入力部と、前記表示素子部と前記入力部とを電気的に接続する引出配線部と、を有し、

前記引出配線部は、積層された複数の配線層を有し、

前記複数の配線層には、第1離間距離で複数の第1配線が形成された第1配線層と、前記第1離間距離よりも小さい第2離間距離で複数の第2配線が形成された第2配線層と、が含まれ、

前記複数の第2配線の数は、前記複数の第1配線の数よりも多い。

まず、表示装置の基本構成について説明する。図1は、本実施の形態の表示装置の一例を示す平面図、図2は図1のA−A線に沿った断面図である。また、図3は、図2のB部の拡大断面図である。また、図4は、図2のC部の拡大断面図である。

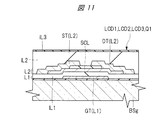

次に、図1に示す引出配線部LDの詳細について説明する。図5は、図1に示す引出配線部のレイアウトを模式的に示す拡大平面図である。また、図6は、図1に示す引出配線部において、複数の配線を二層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。また、図7は、図6に対応する検討例であって、複数の配線を単層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。また、図8は、図6に対応する別の検討例であって、複数の配線を二層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。また、図9は、図8のA−A線に沿った拡大断面図である。また、図10は、図6のA−A線に沿った拡大断面図である。また、図11は、図1に示す表示素子部に設けられた表示素子の構造例を示す拡大断面図である。

次に、上記した実施の形態に対する変形例について、代表的な変形例を例示的に説明する。

図6および図10では、複数の配線層のそれぞれに配線を形成する実施態様の例として、複数の配線WLを二層の配線層で引き回した場合の構造例を取り上げて説明した。本変形例1では、複数の配線WLを三層の配線層で引き回した場合の構造例を説明する。図13は、図6に対する変形例であって、複数の配線を三層の配線層で引き回した場合のレイアウト例を示す拡大平面図である。また、図14は、図13のA−A線に沿った拡大断面図である。なお、図13では、異なる層に形成された配線WL1、配線WL2、および配線WL3の区別をし易くするために、第一層目に形成された配線WL1を実線で示し、第二層目に形成された配線WL2を点線で示し、第三層目に形成された配線WL3を一点鎖線で示している。

次に、上記した図6に示す表示装置LCD1、図7に示す表示装置LCD2、図8に示す表示装置LCD3、および図13に示す表示装置LCD4では、各配線層に形成された配線WLが互いに重ならない実施態様について説明した。しかし、配線密度を向上させる点に着目すれば、異なる配線層に形成された配線WLの一部が厚さ方向に重なっている方が配線密度を向上させることができる。一方、異なる配線層に形成された配線WLの一部が厚さ方向に重なっている場合、各信号線が互いに干渉しノイズが生じたり、配線間の寄生容量によって信号が影響を受けたり、絶縁膜の欠陥により配線間が短絡したりする懸念が考えられる。そこで、本変形例2では、異なる配線層に形成された配線WLの一部が厚さ方向に重なっており、かつ重なった部分のノイズの影響を低減する技術について説明する。

また、上記変形例1で説明した表示装置LCD4や上記変形例2で説明した表示装置LCD5のように、絶縁膜IL2上に、配線WL3を形成する場合、配線WL3が形成されている領域には、絶縁膜IL2が形成されている必要がある。

BM 遮光膜

BS、FS 基板

BSb、FSb 背面

BSf、FSf 前面

BSg、FSg 基材

BSs1、BSs2、BSs3、BSs4 辺

CC 回路部

CE 共通電極

CF カラーフィルタ

CFr、CFg、CFb カラーフィルタ画素

CHP 半導体チップ

CNT1 制御回路

DP 表示部

DPQ 表示素子部

DR1 駆動回路

DT ドレイン電極

FL 額縁部

GT ゲート電極

IL1、IL2、IL3 絶縁膜

IPC 入力部

L1、L2、L3 配線層

LCD1、LCD2、LCD3、LCD4、LCD5 表示装置

LCL 液晶層

LD 引出配線部

LD1、LD2、LD3 部分

LS 光源

OC1、OC2 樹脂層

OP1 開口部

PE 画素電極

PL1、PL2 偏光板

PS 部材

Q1 トランジスタ

S1、S2、S3、S4 離間距離

SCL 半導体層

SL シール部

SLp シール材(封着材)

SLT スリット

ST ソース電極

VW 観者

W1、W2、W3 配線幅

WL、WL1、WL2、WL3 配線

Claims (12)

- 第1面を備える基板、を有し、

前記第1面は、複数の画素を備える表示領域と、前記複数の画素に供給される信号が入力される入力部と、前記表示領域と前記入力部とを電気的に接続する引出配線部と、を有し、

前記基板は、第1方向に沿って延びる第1辺、前記第1辺の反対側に位置する第2辺、前記第1方向に直交する第2方向に沿って延びる第3辺、および前記第3辺の反対側に位置する第4辺を備え、

前記引出配線部と前記入力部は、前記基板の前記第1辺と前記表示領域との間に設けられ、

前記引出配線部は、複数の第1配線を有する第1配線層と、前記第1配線層の前記第1面と反対側に形成された複数の第2配線を有する第2配線層と、前記第1配線層と前記第2配線層間に形成された第1絶縁層と、前記第2配線層の前記第1面と反対側に形成された第2絶縁層と、を有し、

前記引出配線部において、

前記第1配線層と前記第2配線層は、前記表示領域側において前記第2方向に沿って延在する第1部分と、前記入力部側において前記第2方向に沿って延在する第3部分と、前記第1部分と前記第3部分を接続し、前記第2方向に対して斜めに延在する第2部分と、を有し、

前記第3部分において、前記第1絶縁層に開口部が形成され、前記開口部を介して前記第1配線層と前記第2配線層が電気的に接続される、表示装置。 - 請求項1に記載の表示装置であって、

前記第1絶縁層は、無機材料からなり、前記第2絶縁層は、有機絶縁層からなる、表示装置。 - 請求項1に記載の表示装置であって、

平面視において、前記複数の第1配線と、前記複数の第2配線とは交互に配置され、かつ互いに重ならない、表示装置。 - 請求項3に記載の表示装置であって、

前記開口部の上には、有機絶縁層からなる前記第2絶縁層が形成される、表示装置。 - 請求項3に記載の表示装置であって、

平面視において、前記複数の第1配線のそれぞれの線幅は、前記複数の第2配線のそれぞれの線幅よりも広い、表示装置。 - 請求項1に記載の表示装置であって、

前記表示領域の前記複数の画素のそれぞれは、ゲート電極を有するトランジスタを有し、

前記第1配線層は、前記ゲート電極と同層に形成されている、表示装置。 - 請求項1に記載の表示装置であって、

前記複数の第1配線と前記複数の第2配線とは、互いに異なる種類の金属材料により形成されている、表示装置。 - 請求項1に記載の表示装置であって、

前記引出配線部は、複数の第3配線を有する第3配線層をさらに有し、

前記第2配線層と前記第3配線層間には、前記第2絶縁層が形成されている、表示装置。 - 請求項8に記載の表示装置であって、

平面視において、前記複数の第3配線は、前記複数の第1配線および前記複数の第2配線のうちの一部と重なっている、表示装置。 - 請求項8に記載の表示装置であって、

平面視において、前記複数の第3配線は、前記複数の第2配線とは互いに重ならず、かつ、前記複数の第1配線と重なっている、表示装置。 - 請求項8に記載の表示装置であって、

前記引出配線部は、

前記第2絶縁層に開口部が形成され、前記開口部を介して前記第2配線層と前記第3配線層が電気的に接続される、表示装置。 - 請求項1に記載の表示装置であって、

隣り合う第1配線間に、複数本の第2配線が配置される、表示装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014245419A JP6469427B2 (ja) | 2014-12-03 | 2014-12-03 | 表示装置 |

| US14/954,024 US9740066B2 (en) | 2014-12-03 | 2015-11-30 | Display device |

| CN201520983679.0U CN205210483U (zh) | 2014-12-03 | 2015-12-02 | 显示装置 |

| US15/660,482 US10558096B2 (en) | 2014-12-03 | 2017-07-26 | Display device |

| US16/701,999 US10895789B2 (en) | 2014-12-03 | 2019-12-03 | Display device |

| US17/121,259 US11402704B2 (en) | 2014-12-03 | 2020-12-14 | Display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014245419A JP6469427B2 (ja) | 2014-12-03 | 2014-12-03 | 表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019005511A Division JP6707156B2 (ja) | 2019-01-16 | 2019-01-16 | 表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016109791A JP2016109791A (ja) | 2016-06-20 |

| JP2016109791A5 JP2016109791A5 (ja) | 2017-11-02 |

| JP6469427B2 true JP6469427B2 (ja) | 2019-02-13 |

Family

ID=55848191

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014245419A Active JP6469427B2 (ja) | 2014-12-03 | 2014-12-03 | 表示装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (4) | US9740066B2 (ja) |

| JP (1) | JP6469427B2 (ja) |

| CN (1) | CN205210483U (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2018072669A (ja) * | 2016-11-01 | 2018-05-10 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN106681067B (zh) * | 2016-12-20 | 2019-01-22 | 深圳市华星光电技术有限公司 | 显示装置 |

| JP6777558B2 (ja) * | 2017-01-20 | 2020-10-28 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP2018189723A (ja) * | 2017-04-28 | 2018-11-29 | 株式会社ジャパンディスプレイ | 液晶表示装置 |

| WO2019220774A1 (ja) * | 2018-05-14 | 2019-11-21 | 株式会社巴川製紙所 | ヘッドマウントディスプレイ |

| KR20200039862A (ko) * | 2018-10-05 | 2020-04-17 | 삼성디스플레이 주식회사 | 표시장치 |

| JP7237665B2 (ja) * | 2019-03-11 | 2023-03-13 | 株式会社ジャパンディスプレイ | 表示装置 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002223051A (ja) * | 2001-01-25 | 2002-08-09 | Hitachi Ltd | 回路基板とその製造方法ならびにそれを用いた電子装置 |

| JP2002258315A (ja) * | 2001-03-01 | 2002-09-11 | Display Technologies Inc | アレイ基板、及びこれを用いる液晶表示装置 |

| JP2006054111A (ja) | 2004-08-12 | 2006-02-23 | Sony Corp | 表示装置 |

| JP2006071861A (ja) * | 2004-09-01 | 2006-03-16 | Seiko Epson Corp | 電気光学装置及び電子機器 |

| JP2006209089A (ja) * | 2004-12-27 | 2006-08-10 | Toshiba Matsushita Display Technology Co Ltd | 表示装置 |

| KR100814820B1 (ko) * | 2006-08-31 | 2008-03-20 | 삼성에스디아이 주식회사 | 유기 발광 표시장치 |

| JP4869892B2 (ja) * | 2006-12-06 | 2012-02-08 | 株式会社 日立ディスプレイズ | 液晶表示装置 |

| JP4657233B2 (ja) * | 2007-03-12 | 2011-03-23 | 株式会社 日立ディスプレイズ | 表示装置 |

| JP2010113051A (ja) * | 2008-11-05 | 2010-05-20 | Fuji Electric Holdings Co Ltd | 有機el用パッシブマトリックス型表示装置 |

| JP5492516B2 (ja) * | 2009-10-01 | 2014-05-14 | 株式会社ジャパンディスプレイ | 液晶表示装置 |

| JP2011100011A (ja) * | 2009-11-06 | 2011-05-19 | Mitsubishi Electric Corp | 表示装置 |

| US20120257135A1 (en) * | 2011-04-08 | 2012-10-11 | Shenzhen China Star Optoelectronics Technology Co. Ltd. | Fan-out design, method of forming fan-out design, and lcd adopting the fan-out design |

| TWI516851B (zh) * | 2011-05-05 | 2016-01-11 | 友達光電股份有限公司 | 液晶顯示面板的引線結構以及具有此引線結構的液晶顯示面板 |

| CN103718231B (zh) | 2011-08-09 | 2018-09-14 | 夏普株式会社 | 显示装置 |

| WO2014024783A1 (ja) * | 2012-08-09 | 2014-02-13 | シャープ株式会社 | 表示装置 |

| US9659973B2 (en) * | 2014-03-14 | 2017-05-23 | Innolux Corporation | Display device |

| JP6590505B2 (ja) * | 2015-04-06 | 2019-10-16 | 三菱電機株式会社 | 液晶表示装置 |

-

2014

- 2014-12-03 JP JP2014245419A patent/JP6469427B2/ja active Active

-

2015

- 2015-11-30 US US14/954,024 patent/US9740066B2/en active Active

- 2015-12-02 CN CN201520983679.0U patent/CN205210483U/zh active Active

-

2017

- 2017-07-26 US US15/660,482 patent/US10558096B2/en active Active

-

2019

- 2019-12-03 US US16/701,999 patent/US10895789B2/en active Active

-

2020

- 2020-12-14 US US17/121,259 patent/US11402704B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016109791A (ja) | 2016-06-20 |

| US11402704B2 (en) | 2022-08-02 |

| CN205210483U (zh) | 2016-05-04 |

| US10558096B2 (en) | 2020-02-11 |

| US20200103686A1 (en) | 2020-04-02 |

| US9740066B2 (en) | 2017-08-22 |

| US20210103169A1 (en) | 2021-04-08 |

| US20170322439A1 (en) | 2017-11-09 |

| US10895789B2 (en) | 2021-01-19 |

| US20160161815A1 (en) | 2016-06-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6469427B2 (ja) | 表示装置 | |

| US10297621B2 (en) | Transistor substrate and display device | |

| US11686985B2 (en) | Display apparatus | |

| US11774807B2 (en) | Display device | |

| JP2018112692A (ja) | 表示装置 | |

| JP2017191276A (ja) | 液晶表示装置 | |

| US9995978B2 (en) | Display device | |

| JP2016126041A (ja) | 表示装置 | |

| JP7132032B2 (ja) | 表示装置 | |

| JP2023015123A (ja) | 半導体装置 | |

| JP6707156B2 (ja) | 表示装置 | |

| JP6707418B2 (ja) | 表示装置、表示装置の製造方法、及び、カラーフィルタ基板 | |

| JP7227416B2 (ja) | 表示装置 | |

| JP2016071148A (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170922 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170922 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180726 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180807 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181004 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20181218 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190116 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6469427 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |