JP6311357B2 - 防止装置 - Google Patents

防止装置 Download PDFInfo

- Publication number

- JP6311357B2 JP6311357B2 JP2014043038A JP2014043038A JP6311357B2 JP 6311357 B2 JP6311357 B2 JP 6311357B2 JP 2014043038 A JP2014043038 A JP 2014043038A JP 2014043038 A JP2014043038 A JP 2014043038A JP 6311357 B2 JP6311357 B2 JP 6311357B2

- Authority

- JP

- Japan

- Prior art keywords

- resistor

- switch

- potential

- current

- value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H3/00—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection

- H02H3/006—Calibration or setting of parameters

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H3/00—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection

- H02H3/08—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection responsive to excess current

- H02H3/10—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection responsive to excess current additionally responsive to some other abnormal electrical conditions

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H1/00—Details of emergency protective circuit arrangements

- H02H1/0007—Details of emergency protective circuit arrangements concerning the detecting means

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H3/00—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection

- H02H3/08—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection responsive to excess current

- H02H3/085—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection responsive to excess current making use of a thermal sensor, e.g. thermistor, heated by the excess current

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H3/00—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection

- H02H3/08—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection responsive to excess current

- H02H3/087—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection responsive to excess current for dc applications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/08—Modifications for protecting switching circuit against overcurrent or overvoltage

- H03K17/082—Modifications for protecting switching circuit against overcurrent or overvoltage by feedback from the output to the control circuit

- H03K17/0822—Modifications for protecting switching circuit against overcurrent or overvoltage by feedback from the output to the control circuit in field-effect transistor switches

Description

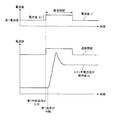

定電流回路では、バイポーラトランジスタのコレクタに抵抗の他端が接続され、このバイポーラトランジスタのコレクタ及びエミッタを介して流れる電流の第2の電流経路とは異なる第3の電流経路に第2の抵抗が設けられている。第2の抵抗の一端には所定の電圧が印加され、第2の抵抗の他端には第3の抵抗が接続されている。第3の抵抗の他端における電位の調整、及び、第3の抵抗の他端の開放のいずかを行うことによって、バイポーラトランジスタの電位を調整する。定電流回路が有するバイポーラトランジスタのベースの電位を調整することによって、定電流回路が流す電流の値を変更する。

本発明に係る防止装置は、一端が前記スイッチの他端に接続してある第4の抵抗と、該第4の抵抗の一端側から他端側に向けて一定の電流を流す第2の定電流回路と、該第2の定電流回路が流す電流の値を変更する第2の変更手段と、前記スイッチの一端、及び、前記第4の抵抗の他端における電位を比較する第2の比較部とを備え、前記比較部が行った比較の結果が、前記スイッチの他端における電位が前記抵抗の他端における電位よりも低いことを示す場合、又は、前記第2の比較部が行った比較の結果が、前記スイッチの一端における電位が前記第4の抵抗の他端における電位よりも低いことを示す場合に前記スイッチをオフにするように構成してあることを特徴とする。

本発明にあっては、スイッチの他端に第4の抵抗の一端が接続してあり、第2の定電流回路は、第4の抵抗の一端側から他端側に向けて一定の電流を流す。スイッチの一端、及び、第4の抵抗の他端における電位を比較する。スイッチ及び抵抗夫々の他端における電位を比較した結果が、スイッチの他端における電位が抵抗の他端における電位よりも低いことを示す場合、又は、スイッチの一端、及び、第4の抵抗の他端における電位を比較した結果が、前記スイッチの一端における電位が前記第4の抵抗の他端における電位よりも低いことを示す場合に前記スイッチをオフにする。第2の定電流回路が流す電流の値も変更する。

スイッチがオンである場合において、スイッチの他端における電位は電源の出力電圧からスイッチの両端間の電圧を引いた値であり、抵抗の他端における電位は、電源の出力電圧から、抵抗の両端間の電圧を引いた値である。定電流回路によって一定の電流が抵抗に流れているため、抵抗の両端間の電圧は一定である。そして、所定値以上の電流が電流経路に流れて、スイッチの両端間の電圧が所定電圧以上となった場合、スイッチの他端における電位が抵抗の他端における電位よりも低くなる。このとき、スイッチがオフにされるので、電流経路に過電流が流れることが防止される。

また、定電流回路が流す電流の値を変更する。これにより、抵抗の両端間の電圧を変更することが可能となるため、スイッチの他端における電位と比較する閾値電位を変更することができる。従って、例えば、スイッチの他端に誘導性負荷が接続されている場合、負荷が作動する直後から所定期間の間だけ、閾値電位を低い電位に変更することが可能である。また、スイッチ周辺の温度に応じて閾値電位を変更することも可能であり、装置ごとに閾値電位を変更することも可能である。閾値電位を適切に設定することによって、電流経路に過電流が流れることが確実に防止される。

具体的には、定電流回路が有する第2のバイポーラトランジスタのコレクタ及びエミッタ間を流れる電流の値を変更することによって、バイポーラトランジスタのベースの電位を調整する。これにより、定電流回路が流す電流の値が変更される。

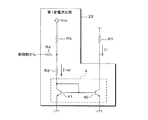

(実施の形態1)

図1は実施の形態1における電源システムの要部構成を示すブロック図である。この電源システム1は、車両に好適に搭載され、防止装置10、第1蓄電器11、第1負荷12、スタータ13、発電機14、第2負荷15及び第2蓄電器16を備える。防止装置10の一端は、第1蓄電器11の正極と、第1負荷12及びスタータ13夫々の一端とに接続されている。防止装置10の他端は、発電機14及び第2負荷15夫々の一端と、第2蓄電器16の正極とに接続されている。第1蓄電器11及び第2蓄電器16夫々の負極と、第1負荷12、スタータ13、発電機14及び第2負荷15夫々の他端とは接地されている。

第2蓄電器16は、電気二重層キャパシタ又はリチウムイオン電池等であり、発電機14から供給された電力を蓄える。第2蓄電器16は、更に、防止装置10を介して、第1蓄電器11から給電され、第1蓄電器11から供給された電力を蓄える。第2蓄電器16は、蓄えた電力を、防止装置10を介して第1蓄電器11及び第1負荷12に供給すると共に、第2負荷15に供給する。

スタータ13は、図示しないエンジンを始動させるためのモータであり、第1蓄電器11が蓄えた電力を用いて作動する。

第1負荷12及び第2負荷15夫々は特許請求の範囲における負荷として機能する。

FET21,22は防止装置10の両端間に流れる電流の電流経路に設けられている。

具体的には、制御部23は、抵抗R4の他端にバイポーラトランジスタ41のエミッタの電位を基準とした電圧Vccを印加するか、又は、抵抗R4の一端を接地することによって、抵抗R4の他端における電位を調整する。

なお、抵抗R4の他端における電位を、電圧Vccが印加されている抵抗R5の他端における電位と接地電位とに加えて、これら以外の電位に調整してもよい。この場合、電流値Irefをより細かく調整することも可能である。

制御部23は、スイッチ電流値が一定の電流値以上である場合にFET21,22をオフにし、防止装置10の両端間に過電流が流れることを防止する。

また、制御部23は、ステップS2でスイッチ温度の高/低に応じて第1電流値を小/大に設定し、電流値I1を、第1電流値、又は、第1電流値に電流値ΔIを加算した電流値に変更する。言い換えると、制御部23は、スイッチ温度の高/低に応じて電流値I1を小/大に変更する。

電流がFET21のドレインからFET22のドレインへ流れている場合、FET22のドレインにおける電位は、(Vb1−rs×Is)であり、抵抗R1の他端、即ち、抵抗R1の第1定電流回路25側の一端における電位は(Vb1−r1×I1)である。

このため、電流がFET22のドレインからFET21のドレインへ流れている場合、第1コンパレータ26は常に出力端子からハイレベルの電圧を出力し、制御部23はステップS7で通電を遮断すべきではないと判定する。

このため、電流がFET21のドレインからFET22のドレインへ流れている場合、第2コンパレータ29は常に出力端子からハイレベルの電圧を出力し、第2防止処理では、制御部23は通電を遮断すべきではないと判定する。

なお、設定時間は、第1作動信号が制御部23に入力されてから、突入電流が発生してスイッチ電流値の絶対値Isが安定するまでの時間よりも長い時間であることが好ましい。

図8は実施の形態2における第1定電流回路25の回路図である。実施の形態2は、実施の形態1と比較して第1定電流回路25及び第2定電流回路28の回路構成が異なる。

以下では、実施の形態2について、実施の形態1と異なる点を説明する。後述する構成を除く他の構成については、実施の形態1と同様であるため、同様の符号を付してその説明を省略する。

抵抗R4の他端の状態が固定されている場合においては、図4を用いて説明したように、抵抗R6の他端に電圧Vccが印加されている場合における電流値Irefが最も大きい。そして、抵抗R6の他端を開放している場合における電流値Irefが次に大きく、抵抗R6の他端を接地している場合における電流値Irefが最も小さい。

また、抵抗R4,R6夫々の他端における電位を、電圧Vccが印加されている抵抗R5の他端における電位と接地電位とに加えて、これら以外の電位に調整してもよい。この場合、電流値Irefを更に細かく調整することができる。

実施の形態2における制御部23は実施の形態1と同様に第1及び第2防止処理を行い、電流値I1,I2を変更する構成のみが実施の形態1と異なるので、実施の形態2における防止装置10は、実施の形態1と同様の効果を奏する。

図9は実施の形態3における第1定電流回路25の回路図である。実施の形態3は、実施の形態1と比較して第1定電流回路25及び第2定電流回路28の回路構成が異なる。

以下では、実施の形態3について、実施の形態1と異なる点を説明する。後述する構成を除く他の構成については、実施の形態1と同様であるため、同様の符号を付してその説明を省略する。

なお、抵抗R3の一端はバイポーラトランジスタ41のコレクタ及びベースに接続されている。

Iref=(Vda−Vbe)/r3・・・(1)

ここで、r3は抵抗R3の抵抗値であり、Vbeはバイポーラトランジスタ41のベース及びエミッタ間の電圧である。(1)式に示すように、電流値Irefは、電圧Vdaの高/低に応じて大/小となる。

以上のように構成された第1定電流回路25では、制御部25は簡単な構成で電流値I1を変更することができる。

12 第1負荷

15 第2負荷

21,22 FET

23 制御部

24 温度検出部

25 第1定電流回路

26 第1コンパレータ

28 第2定電流回路

29 第2コンパレータ

40,41 バイポーラトランジスタ

R1,R2 抵抗

Claims (6)

- 電流経路に設けられたスイッチを備え、該スイッチをオフにすることによって前記電流経路に過電流が流れることを防止する防止装置において、

一端が前記スイッチの一端に接続してある抵抗と、

該抵抗の一端側から他端側に向けて一定の電流を流す定電流回路と、

該定電流回路が流す電流の値を変更する変更手段と、

前記スイッチ及び抵抗夫々の他端における電位を比較する比較部と

を備え、

該比較部が行った比較の結果が、前記スイッチの他端における電位が前記抵抗の他端における電位よりも低いことを示す場合に前記スイッチをオフにし、

前記定電流回路は、

コレクタが前記抵抗の他端に接続されているバイポーラトランジスタと、

該バイポーラトランジスタのコレクタ及びエミッタを介して流れる電流の第2の電流経路とは異なる第3の電流経路に設けられ、一端に所定の電圧が印加され、他端が前記バイポーラトランジスタのベースに接続される第2の抵抗と、

該第2の抵抗の他端に一端が接続される第3の抵抗と

を有し、

前記変更手段は、該第3の抵抗の他端における電位の調整、及び、該第3の抵抗の他端の開放のいずれかを行うことによって、前記バイポーラトランジスタのベースの電位を調整し、該ベースの電位を調整することによって、前記電流の値を変更するように構成してあること

を特徴とする防止装置。 - 一端が前記スイッチの他端に接続してある第4の抵抗と、

該第4の抵抗の一端側から他端側に向けて一定の電流を流す第2の定電流回路と、

該第2の定電流回路が流す電流の値を変更する第2の変更手段と、

前記スイッチの一端、及び、前記第4の抵抗の他端における電位を比較する第2の比較部と

を備え、

前記比較部が行った比較の結果が、前記スイッチの他端における電位が前記抵抗の他端における電位よりも低いことを示す場合、又は、前記第2の比較部が行った比較の結果が、前記スイッチの一端における電位が前記第4の抵抗の他端における電位よりも低いことを示す場合に前記スイッチをオフにするように構成してあること

を特徴とする請求項1に記載の防止装置。 - 前記スイッチ周辺の温度を検出する温度検出部を更に備え、

前記変更手段は、前記温度検出部が検出した温度の高/低に応じて、前記定電流回路が流す電流の値を小/大に変更するように構成してあること

を特徴とする請求項1又は請求項2に記載の防止装置。 - 前記スイッチの他端に負荷が接続してあり、

該負荷が作動するか否かを判定する判定手段を備え、

前記変更手段は、該判定手段によって前記負荷が作動すると判定された場合、前記定電流回路が流す電流の値を上昇させるように構成してあること

を特徴とする請求項1から請求項3のいずれか1つに記載の防止装置。 - 前記変更手段は、前記判定手段によって前記負荷が作動すると判定されてから所定時間が経過した場合に、前記定電流回路が流す電流の値を、上昇させる前の電流値に戻すように構成してあること

を特徴とする請求項4に記載の防止装置。 - 電流経路に設けられたスイッチを備え、該スイッチをオフにすることによって前記電流経路に過電流が流れることを防止する防止装置において、

一端が前記スイッチの一端に接続してある抵抗と、

該抵抗の一端側から他端側に向けて一定の電流を流す定電流回路と、

該定電流回路が流す電流の値を変更する変更手段と、

前記スイッチ及び抵抗夫々の他端における電位を比較する比較部と

を備え、

該比較部が行った比較の結果が、前記スイッチの他端における電位が前記抵抗の他端における電位よりも低いことを示す場合に前記スイッチをオフにし、

前記定電流回路は、

コレクタが前記抵抗の他端に接続されているバイポーラトランジスタと、

ベース及びコレクタが前記バイポーラトランジスタのベースに接続されている第2のバイポーラトランジスタと

を有し、

前記バイポーラトランジスタ及び第2のバイポーラトランジスタのエミッタの電位は略同じであり、

前記変更手段は、前記第2のバイポーラトランジスタのコレクタ及びエミッタ間を流れる電流の値を変更することによって、前記バイポーラトランジスタのベースの電位を調整し、該ベースの電位を調整することによって、前記電流の値を変更するように構成してあること

を特徴とする防止装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014043038A JP6311357B2 (ja) | 2014-03-05 | 2014-03-05 | 防止装置 |

| US15/123,751 US10135234B2 (en) | 2014-03-05 | 2015-02-20 | Preventive apparatus |

| EP15758498.8A EP3116129B1 (en) | 2014-03-05 | 2015-02-20 | Preventive apparatus |

| PCT/JP2015/054736 WO2015133294A1 (ja) | 2014-03-05 | 2015-02-20 | 防止装置 |

| CN201580011624.6A CN106063129B (zh) | 2014-03-05 | 2015-02-20 | 防止装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014043038A JP6311357B2 (ja) | 2014-03-05 | 2014-03-05 | 防止装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015170918A JP2015170918A (ja) | 2015-09-28 |

| JP2015170918A5 JP2015170918A5 (ja) | 2017-10-12 |

| JP6311357B2 true JP6311357B2 (ja) | 2018-04-18 |

Family

ID=54055104

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014043038A Active JP6311357B2 (ja) | 2014-03-05 | 2014-03-05 | 防止装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10135234B2 (ja) |

| EP (1) | EP3116129B1 (ja) |

| JP (1) | JP6311357B2 (ja) |

| CN (1) | CN106063129B (ja) |

| WO (1) | WO2015133294A1 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017069716A (ja) * | 2015-09-29 | 2017-04-06 | 株式会社オートネットワーク技術研究所 | 半導体装置及び制御装置 |

| JP6610446B2 (ja) | 2016-06-21 | 2019-11-27 | 株式会社オートネットワーク技術研究所 | 給電制御装置 |

| JP6426783B2 (ja) * | 2017-03-14 | 2018-11-21 | ファナック株式会社 | パワー素子の異常検知機能を備えたモータ駆動装置 |

| JP6907984B2 (ja) * | 2018-03-23 | 2021-07-21 | 株式会社オートネットワーク技術研究所 | 制御装置、制御方法及びコンピュータプログラム |

| US11495836B2 (en) * | 2019-11-11 | 2022-11-08 | Samsung Sdi Co., Ltd. | Control unit for a battery system |

| JP7472577B2 (ja) * | 2020-03-23 | 2024-04-23 | 株式会社オートネットワーク技術研究所 | 電流制御装置、スイッチ制御装置、電流制御方法及びコンピュータプログラム |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03101129U (ja) * | 1990-01-30 | 1991-10-22 | ||

| US5864458A (en) * | 1995-09-14 | 1999-01-26 | Raychem Corporation | Overcurrent protection circuits comprising combinations of PTC devices and switches |

| JP3403309B2 (ja) * | 1997-01-31 | 2003-05-06 | 株式会社ケンウッド | 充電装置 |

| JP3589392B2 (ja) | 1999-02-26 | 2004-11-17 | 矢崎総業株式会社 | 過電流検出回路及び過電流検出・保護回路 |

| JP2001161025A (ja) * | 1999-11-30 | 2001-06-12 | Ando Electric Co Ltd | 電流制限装置 |

| JP2002017036A (ja) * | 2000-06-29 | 2002-01-18 | Nissan Motor Co Ltd | 過電流検知回路 |

| JP3914004B2 (ja) * | 2001-05-25 | 2007-05-16 | 矢崎総業株式会社 | 半導体素子の過電流検出・保護装置 |

| JP2003101129A (ja) | 2001-07-18 | 2003-04-04 | Tdk Corp | レーザダイオード駆動回路および駆動方法、並びにそれを用いた光ヘッド |

| US6917503B2 (en) * | 2003-10-29 | 2005-07-12 | Texas Instruments Incorporated | Programmable current limiting using a shunt resistor |

| JP4643419B2 (ja) * | 2005-11-08 | 2011-03-02 | 矢崎総業株式会社 | 自己診断機能を備えた負荷駆動装置 |

| JP4808047B2 (ja) * | 2006-03-03 | 2011-11-02 | 新日本無線株式会社 | 電流源回路 |

| US7839097B2 (en) * | 2007-02-03 | 2010-11-23 | Kinetic Technologies | System and method for wide-range high-accuracy-low-dropout current regulation |

| JP5171402B2 (ja) * | 2008-06-04 | 2013-03-27 | 矢崎総業株式会社 | 負荷回路の過電流保護装置 |

| TWI515987B (zh) | 2011-07-22 | 2016-01-01 | 鴻海精密工業股份有限公司 | 過壓過流保護電路 |

| JP5989375B2 (ja) | 2012-03-28 | 2016-09-07 | ラピスセミコンダクタ株式会社 | 半導体装置及び電池監視システム |

-

2014

- 2014-03-05 JP JP2014043038A patent/JP6311357B2/ja active Active

-

2015

- 2015-02-20 EP EP15758498.8A patent/EP3116129B1/en active Active

- 2015-02-20 WO PCT/JP2015/054736 patent/WO2015133294A1/ja active Application Filing

- 2015-02-20 US US15/123,751 patent/US10135234B2/en active Active

- 2015-02-20 CN CN201580011624.6A patent/CN106063129B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| EP3116129A1 (en) | 2017-01-11 |

| EP3116129B1 (en) | 2022-06-08 |

| EP3116129A4 (en) | 2017-03-15 |

| US20170018918A1 (en) | 2017-01-19 |

| CN106063129A (zh) | 2016-10-26 |

| CN106063129B (zh) | 2019-03-22 |

| JP2015170918A (ja) | 2015-09-28 |

| WO2015133294A1 (ja) | 2015-09-11 |

| US10135234B2 (en) | 2018-11-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6311357B2 (ja) | 防止装置 | |

| CN110061477B (zh) | 电源保护装置、电源装置、开关故障诊断方法及记录介质 | |

| US9825555B2 (en) | Semiconductor control device, switching device, inverter, and control system | |

| EP3922503B1 (en) | Load access detection method, switch circuit and battery management system | |

| JP6381023B2 (ja) | 突入電流制限回路 | |

| WO2017110878A1 (ja) | 給電制御装置 | |

| JP2015100240A (ja) | 保護装置及び変圧システム | |

| JP2017188983A (ja) | 電源供給装置 | |

| JP5796586B2 (ja) | 回路制御装置 | |

| US11004626B2 (en) | Power supply control device, power supply control method, and computer program | |

| JP2017229154A (ja) | バッテリ装置 | |

| KR101602434B1 (ko) | 충전시 발생하는 셀 밸런싱 스위치의 오진단 방지 장치 및 오진단 방지 방법 | |

| JP6624339B2 (ja) | 電源装置 | |

| US20190165561A1 (en) | Power supply control apparatus, power supply control method, and computer program | |

| JP2009118607A (ja) | バッテリ充電器 | |

| EP3048713A1 (en) | Power supply apparatus | |

| US10615682B2 (en) | Electrically driven vehicle inverter device | |

| WO2023073754A1 (ja) | 電源遮断装置、モータ駆動装置、および電動パワーステアリング装置 | |

| WO2018147102A1 (ja) | スイッチ制御装置 | |

| US10547194B2 (en) | Power supply control apparatus | |

| US9682650B2 (en) | Direction indicator system and direction indicator device for a vehicle | |

| JP2020092551A (ja) | 車両の電源装置 | |

| JP2021029091A (ja) | スイッチング素子の過電流検出装置 | |

| JP2017131040A (ja) | 保護装置及び電源システム | |

| JP2016201189A (ja) | 電子制御装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160727 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170904 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20170904 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20170907 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171003 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171124 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180220 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180305 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6311357 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |