JP6907984B2 - 制御装置、制御方法及びコンピュータプログラム - Google Patents

制御装置、制御方法及びコンピュータプログラム Download PDFInfo

- Publication number

- JP6907984B2 JP6907984B2 JP2018056897A JP2018056897A JP6907984B2 JP 6907984 B2 JP6907984 B2 JP 6907984B2 JP 2018056897 A JP2018056897 A JP 2018056897A JP 2018056897 A JP2018056897 A JP 2018056897A JP 6907984 B2 JP6907984 B2 JP 6907984B2

- Authority

- JP

- Japan

- Prior art keywords

- switch

- resistor

- voltage value

- voltage

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 66

- 238000004590 computer program Methods 0.000 title claims description 17

- 238000001514 detection method Methods 0.000 claims description 118

- 238000006243 chemical reaction Methods 0.000 description 30

- 239000004065 semiconductor Substances 0.000 description 14

- 238000010586 diagram Methods 0.000 description 12

- 230000006870 function Effects 0.000 description 6

- 230000007423 decrease Effects 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 3

- 230000002159 abnormal effect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 238000004891 communication Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/08—Modifications for protecting switching circuit against overcurrent or overvoltage

- H03K17/082—Modifications for protecting switching circuit against overcurrent or overvoltage by feedback from the output to the control circuit

- H03K17/0822—Modifications for protecting switching circuit against overcurrent or overvoltage by feedback from the output to the control circuit in field-effect transistor switches

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/08—Modifications for protecting switching circuit against overcurrent or overvoltage

- H03K17/081—Modifications for protecting switching circuit against overcurrent or overvoltage without feedback from the output circuit to the control circuit

- H03K17/08116—Modifications for protecting switching circuit against overcurrent or overvoltage without feedback from the output circuit to the control circuit in composite switches

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H3/00—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection

- H02H3/08—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection responsive to excess current

- H02H3/087—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection responsive to excess current for dc applications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02J—CIRCUIT ARRANGEMENTS OR SYSTEMS FOR SUPPLYING OR DISTRIBUTING ELECTRIC POWER; SYSTEMS FOR STORING ELECTRIC ENERGY

- H02J7/00—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries

- H02J7/0013—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries acting upon several batteries simultaneously or sequentially

- H02J7/0024—Parallel/serial switching of connection of batteries to charge or load circuit

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02J—CIRCUIT ARRANGEMENTS OR SYSTEMS FOR SUPPLYING OR DISTRIBUTING ELECTRIC POWER; SYSTEMS FOR STORING ELECTRIC ENERGY

- H02J7/00—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries

- H02J7/0029—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries with safety or protection devices or circuits

- H02J7/0031—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries with safety or protection devices or circuits using battery or load disconnect circuits

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02J—CIRCUIT ARRANGEMENTS OR SYSTEMS FOR SUPPLYING OR DISTRIBUTING ELECTRIC POWER; SYSTEMS FOR STORING ELECTRIC ENERGY

- H02J7/00—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries

- H02J7/0063—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries with circuits adapted for supplying loads from the battery

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/002—Switching arrangements with several input- or output terminals

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/12—Modifications for increasing the maximum permissible switched current

- H03K17/122—Modifications for increasing the maximum permissible switched current in field-effect transistor switches

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Electronic Switches (AREA)

- Emergency Protection Circuit Devices (AREA)

- Charge And Discharge Circuits For Batteries Or The Like (AREA)

- Control Of Electric Motors In General (AREA)

Description

最初に本発明の実施態様を列挙して説明する。以下に記載する実施形態の少なくとも一部を任意に組み合わせてもよい。

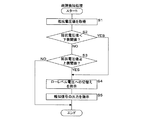

第1スイッチ又は第2スイッチがオフで固定された場合、電圧出力部が出力した電圧値が大きく変動する。これにより、第1スイッチ、第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生が検知される。

本発明の実施形態に係る電源システムの具体例を、以下に図面を参照しつつ説明する。なお、本発明はこれらの例示に限定されるものではなく、特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

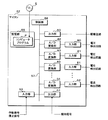

図1は、実施形態1における電源システム1の要部構成を示すブロック図である。電源システム1は、車両に好適に搭載されており、制御装置10、バッテリ11及び負荷12を備える。制御装置10は、バッテリ11の正極と、負荷12の一端とに接続されている。バッテリ11の負極と、負荷12の他端とは接地されている。

以上のように、制御装置10は、バッテリ11及び負荷12の電気的な接続と、この電気的な接続の遮断とを行うことによって、バッテリ11から負荷12への給電を制御する。

V62=V31・r62/r60・・・(1)

従って、抵抗電圧値V62は、第1抵抗31の両端間の電圧値V31に比例する。第1抵抗31の両端間の電圧値V31が上昇した場合、抵抗電圧値V62は上昇する。

V31=rs・It・・・(2)

It=V62・r60/(rs・r62)・・・(3)

入力部53には、作動信号及び停止信号が入力される。入力部53は、作動信号又は停止信号が入力された場合、入力された信号を制御部56に通知する。

抵抗電圧値V62は、(1)式に示すように、第1抵抗31の両端間の電圧値V31に比例する。

更に、電流検出回路21は、第1抵抗31の第1スイッチ30側の一端から電流を引き込む回路に限定されず、第1抵抗31の両端間の電圧値に応じた電圧値を出力する回路であってもよい。

図5は、実施形態2における電源システム1の要部構成を示すブロック図である。

以下では、実施形態2について、実施形態1と異なる点を説明する。後述する構成を除く他の構成については、実施形態1と共通しているため、実施形態1と共通する構成部には実施形態1と同一の参照符号を付してその説明を省略する。

図9は、実施形態3における電源システム1の要部構成を示すブロック図である。

以下では、実施形態3について、実施形態2と異なる点を説明する。後述する構成を除く他の構成については、実施形態2と共通しているため、実施形態2と共通する構成部には実施形態2と同一の参照符号を付してその説明を省略する。

N個の第2抵抗41夫々の抵抗値は、他の第2抵抗41の抵抗値中の少なくとも1つと異なっていてもよい。

実施形態3における制御装置10は、実施形態2における制御装置10が奏する効果を同様に奏する。

また、電流検出回路21が出力した抵抗電圧値に基づいて算出した電流値を用いる処理は、保護処理に限定されず、例えば、電流値からバッテリ11及び負荷12間に接続される電線温度を算出する処理であってもよい。

10 制御装置

11 バッテリ

12 負荷

20 駆動回路

21 電流検出回路(電圧出力回路)

22 マイコン

30 第1スイッチ

31 第1抵抗

40 第2スイッチ

41 第2抵抗

50,51 出力部

52,53 入力部

54 A/D変換部

55 記憶部

56 制御部(指示部、検知部)

57 内部バス

60,61 回路抵抗

62 回路抵抗(電流抵抗)

63 差動増幅器

64 FET(電流出力部)

70 電圧検出回路

71 電圧検出回路(第2の電圧検出回路)

80,81 入力部

82,83 A/D変換部

A 第1直列回路

B 第2直列回路

E 記憶媒体

P コンピュータプログラム

Claims (6)

- 直列に接続された第1スイッチ及び第1抵抗を有する第1直列回路と、

直列に接続された第2スイッチ及び第2抵抗を有し、前記第1直列回路に並列に接続される第2直列回路と、

前記第1スイッチ及び第2スイッチのオンへの切替えを指示する指示部と、

前記第1抵抗の両端間の電圧値に比例する電圧値を出力する電圧出力回路と、

前記第1スイッチ、第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知する検知部と

を備え、

前記電圧出力回路が出力する電圧値は、前記第1抵抗の両端間の電圧値が上昇した場合に上昇し、

前記検知部は、

前記指示部が前記第1スイッチ及び第2スイッチのオンへの切替えを指示している場合にて、前記電圧出力回路が出力した電圧値が第1閾値未満であるとき、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知し、

前記指示部が前記第1スイッチ及び第2スイッチのオンへの切替えを指示している場合にて、前記電圧出力回路が出力した電圧値が第2閾値以上であるとき、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知し、

前記第1閾値は前記第2閾値未満である

制御装置。 - 前記第1スイッチ及び第1抵抗間の接続ノードの電圧値を検出する電圧検出回路を備え、

前記検知部は、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知した場合に、前記電圧検出回路が検出した電圧値に基づいて、前記第1スイッチでの故障の発生を検知する

請求項1に記載の制御装置。 - 前記第2スイッチ及び第2抵抗間の接続ノードの電圧値を検出する第2の電圧検出回路を備え、

前記検知部は、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知した場合に、前記第2の電圧検出回路が検出した電圧値に基づいて、前記第2スイッチでの故障の発生を検知する

請求項1又は請求項2に記載の制御装置。 - 電流は、前記第1スイッチ及び第1抵抗の順に流れ、

前記電圧出力回路は、

前記第1スイッチ及び第1抵抗間の接続ノードから電流を引き込み、引き込んだ電流を出力する電流出力部と、

前記電流出力部が出力した電流が流れる電流抵抗と

を有し、

前記電圧出力回路は、前記電流抵抗の両端間の電圧値を出力する

請求項1から請求項3のいずれか1つに記載の制御装置。 - 第1抵抗に直列に接続される第1スイッチ、及び、第2抵抗に直列に接続される第2スイッチのオンへの切替えを指示するステップと、

前記第1抵抗の両端間の電圧値に比例する電圧値を取得するステップと、

前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第1閾値未満であるとき、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップと、

前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第2閾値以上であるとき、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップと

を含み、

前記第1スイッチ及び第1抵抗を有する第1直列回路は、前記第2スイッチ及び第2抵抗を有する第2直列回路に並列に接続され、

取得する電圧値は、前記第1抵抗の両端間の電圧値が上昇した場合に上昇し、

前記第1閾値は前記第2閾値未満である

制御方法。 - コンピュータに、

第1抵抗に直列に接続される第1スイッチ、及び、第2抵抗に直列に接続される第2スイッチのオンへの切替えを指示するステップと、

前記第1抵抗の両端間の電圧値に比例する電圧値を取得するステップと、

前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第1閾値未満であるとき、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップと、

前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第2閾値以上であるとき、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップと

を実行させるために用いられ、

前記第1スイッチ及び第1抵抗を有する第1直列回路は、前記第2スイッチ及び第2抵抗を有する第2直列回路に並列に接続され、

取得する電圧値は、前記第1抵抗の両端間の電圧値が上昇した場合に上昇し、

前記第1閾値は前記第2閾値未満である

コンピュータプログラム。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018056897A JP6907984B2 (ja) | 2018-03-23 | 2018-03-23 | 制御装置、制御方法及びコンピュータプログラム |

| PCT/JP2019/008780 WO2019181495A1 (ja) | 2018-03-23 | 2019-03-06 | 制御装置、制御方法及びコンピュータプログラム |

| US17/040,885 US11996829B2 (en) | 2018-03-23 | 2019-03-06 | Control device, control method, and computer program |

| CN201980017278.0A CN111819750B (zh) | 2018-03-23 | 2019-03-06 | 控制装置、控制方法及计算机可读取的存储介质 |

| JP2021109477A JP7028355B2 (ja) | 2018-03-23 | 2021-06-30 | 制御装置、制御方法及びコンピュータプログラム |

| US18/636,441 US20240259009A1 (en) | 2018-03-23 | 2024-04-16 | Control device, control method, and computer program |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018056897A JP6907984B2 (ja) | 2018-03-23 | 2018-03-23 | 制御装置、制御方法及びコンピュータプログラム |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021109477A Division JP7028355B2 (ja) | 2018-03-23 | 2021-06-30 | 制御装置、制御方法及びコンピュータプログラム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019169873A JP2019169873A (ja) | 2019-10-03 |

| JP2019169873A5 JP2019169873A5 (ja) | 2020-08-27 |

| JP6907984B2 true JP6907984B2 (ja) | 2021-07-21 |

Family

ID=67987046

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018056897A Active JP6907984B2 (ja) | 2018-03-23 | 2018-03-23 | 制御装置、制御方法及びコンピュータプログラム |

| JP2021109477A Active JP7028355B2 (ja) | 2018-03-23 | 2021-06-30 | 制御装置、制御方法及びコンピュータプログラム |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021109477A Active JP7028355B2 (ja) | 2018-03-23 | 2021-06-30 | 制御装置、制御方法及びコンピュータプログラム |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US11996829B2 (ja) |

| JP (2) | JP6907984B2 (ja) |

| CN (1) | CN111819750B (ja) |

| WO (1) | WO2019181495A1 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7391720B2 (ja) * | 2020-03-05 | 2023-12-05 | 株式会社東芝 | 半導体集積回路装置および電流検出回路 |

| CN113891521B (zh) * | 2021-11-05 | 2023-09-19 | 深圳市角度控光智能照明技术有限公司 | 一种pwm斩波调光冗余电路及其斩波调光方法 |

| JP2023152493A (ja) * | 2022-04-04 | 2023-10-17 | 株式会社オートネットワーク技術研究所 | 給電制御装置、給電制御方法及びコンピュータプログラム |

| CN115389979B (zh) * | 2022-10-28 | 2023-01-13 | 海的电子科技(苏州)有限公司 | 信号传输线的检测电路和检测方法、控制器、存储介质 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4967433B2 (ja) * | 2006-04-19 | 2012-07-04 | 横河電機株式会社 | スイッチ故障検出回路 |

| EP1936777B1 (en) | 2006-12-18 | 2017-11-01 | Nissan Motor Ltd. | Abnormality Diagnostic Device |

| JP5076812B2 (ja) * | 2006-12-18 | 2012-11-21 | 日産自動車株式会社 | 異常診断装置 |

| JP5050715B2 (ja) * | 2007-08-01 | 2012-10-17 | 株式会社デンソー | 発光ダイオード駆動回路 |

| US8598899B2 (en) * | 2011-01-25 | 2013-12-03 | Hamilton Sundstrand Corporation | Built-in test for an overvoltage protection circuit |

| CN202488098U (zh) * | 2011-12-27 | 2012-10-10 | 北京中纺锐力机电有限公司 | 一种制动相短路检测判断保护装置 |

| JP5929840B2 (ja) * | 2013-06-06 | 2016-06-08 | 株式会社オートネットワーク技術研究所 | 電力供給制御装置 |

| CN103683239A (zh) * | 2013-12-16 | 2014-03-26 | 杭州电子科技大学 | 一种浪涌保护电路 |

| JP6311357B2 (ja) * | 2014-03-05 | 2018-04-18 | 株式会社オートネットワーク技術研究所 | 防止装置 |

| US9429598B2 (en) * | 2014-06-30 | 2016-08-30 | Infineon Technologies Ag | Current measurement and control of a semiconductor element based on the current measurement in a power semiconductor arrangement |

| CN106877277B (zh) * | 2015-12-14 | 2019-07-23 | 北京宝沃汽车有限公司 | 一种继电器控制电路、车辆控制电路及车辆 |

-

2018

- 2018-03-23 JP JP2018056897A patent/JP6907984B2/ja active Active

-

2019

- 2019-03-06 CN CN201980017278.0A patent/CN111819750B/zh active Active

- 2019-03-06 US US17/040,885 patent/US11996829B2/en active Active

- 2019-03-06 WO PCT/JP2019/008780 patent/WO2019181495A1/ja active Application Filing

-

2021

- 2021-06-30 JP JP2021109477A patent/JP7028355B2/ja active Active

-

2024

- 2024-04-16 US US18/636,441 patent/US20240259009A1/en active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| JP2019169873A (ja) | 2019-10-03 |

| JP7028355B2 (ja) | 2022-03-02 |

| JP2021170785A (ja) | 2021-10-28 |

| CN111819750A (zh) | 2020-10-23 |

| US20210006241A1 (en) | 2021-01-07 |

| US20240259009A1 (en) | 2024-08-01 |

| WO2019181495A1 (ja) | 2019-09-26 |

| US11996829B2 (en) | 2024-05-28 |

| CN111819750B (zh) | 2022-08-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7028355B2 (ja) | 制御装置、制御方法及びコンピュータプログラム | |

| JP4121511B2 (ja) | 電源装置 | |

| JP4473927B2 (ja) | 短絡保護装置 | |

| JP5343986B2 (ja) | 電子装置 | |

| US20160181794A1 (en) | Inrush Current Limiting Circuit | |

| JP5770979B2 (ja) | バッテリー状態監視回路およびバッテリー装置 | |

| US20180143250A1 (en) | Vehicle including multiple analog switch monitoring system with simultaneous switch-state detection | |

| KR100657860B1 (ko) | 증폭기 및 증폭기의 과전류 검출 방법 | |

| JP6904229B2 (ja) | 給電制御装置及び給電制御方法 | |

| WO2018147103A1 (ja) | スイッチ制御装置、スイッチ切替え方法及びコンピュータプログラム | |

| CN111342443A (zh) | 一种多路电源同步供电的方法、系统、设备及介质 | |

| JP2021191011A (ja) | 電池監視装置 | |

| JP5638428B2 (ja) | アンテナ接続状態検出回路 | |

| JP2013126361A (ja) | 車載用電子制御装置 | |

| JP5343675B2 (ja) | 半導体駆動装置 | |

| JP2021180573A (ja) | 給電制御装置、溶断方法及びコンピュータプログラム | |

| JP7568018B2 (ja) | 駆動装置 | |

| WO2021131698A1 (ja) | 給電制御装置 | |

| JP3599084B2 (ja) | 電源装置 | |

| JP2014017672A (ja) | 負荷駆動回路 | |

| JP7533149B2 (ja) | 給電制御装置 | |

| WO2021210319A1 (ja) | 給電制御装置、検査方法及びコンピュータプログラム | |

| JP2013165631A (ja) | スイッチ回路及びパック電池 | |

| JP2019068639A (ja) | 放電装置 | |

| KR102416199B1 (ko) | 전계 효과 트랜지스터 보호 장치 및 이를 이용한 과전류 방지 시스템 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200618 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200714 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20201110 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201201 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210601 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210614 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6907984 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |