JP6206212B2 - タイミング信号発生回路 - Google Patents

タイミング信号発生回路 Download PDFInfo

- Publication number

- JP6206212B2 JP6206212B2 JP2014010352A JP2014010352A JP6206212B2 JP 6206212 B2 JP6206212 B2 JP 6206212B2 JP 2014010352 A JP2014010352 A JP 2014010352A JP 2014010352 A JP2014010352 A JP 2014010352A JP 6206212 B2 JP6206212 B2 JP 6206212B2

- Authority

- JP

- Japan

- Prior art keywords

- phase

- signal

- circuit

- control voltage

- degree

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 title claims description 62

- 238000001514 detection method Methods 0.000 claims description 98

- 230000015572 biosynthetic process Effects 0.000 claims description 33

- 238000003786 synthesis reaction Methods 0.000 claims description 33

- 230000002194 synthesizing effect Effects 0.000 claims description 8

- 239000003990 capacitor Substances 0.000 claims description 6

- 230000004044 response Effects 0.000 claims description 6

- 238000007599 discharging Methods 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 31

- 238000004088 simulation Methods 0.000 description 9

- 239000002131 composite material Substances 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- 230000010363 phase shift Effects 0.000 description 5

- 238000013139 quantization Methods 0.000 description 5

- 238000000034 method Methods 0.000 description 4

- 238000011084 recovery Methods 0.000 description 4

- 230000008859 change Effects 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000010365 information processing Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 210000000056 organ Anatomy 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 230000008054 signal transmission Effects 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

- H03L7/0814—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used the phase shifting device being digitally controlled

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/0807—Details of the phase-locked loop concerning mainly a recovery circuit for the reference signal

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/16—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/033—Speed or phase control by the received code signals, the signals containing no special synchronisation information using the transitions of the received signal to control the phase of the synchronising-signal-generating means, e.g. using a phase-locked loop

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/033—Speed or phase control by the received code signals, the signals containing no special synchronisation information using the transitions of the received signal to control the phase of the synchronising-signal-generating means, e.g. using a phase-locked loop

- H04L7/0331—Speed or phase control by the received code signals, the signals containing no special synchronisation information using the transitions of the received signal to control the phase of the synchronising-signal-generating means, e.g. using a phase-locked loop with a digital phase-locked loop [PLL] processing binary samples, e.g. add/subtract logic for correction of receiver clock

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/089—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses

- H03L7/0891—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses the up-down pulses controlling source and sink current generators, e.g. a charge pump

- H03L7/0895—Details of the current generators

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/093—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using special filtering or amplification characteristics in the loop

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0016—Arrangements for synchronising receiver with transmitter correction of synchronization errors

- H04L7/002—Arrangements for synchronising receiver with transmitter correction of synchronization errors correction by interpolation

- H04L7/0025—Arrangements for synchronising receiver with transmitter correction of synchronization errors correction by interpolation interpolation of clock signal

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

- Pulse Circuits (AREA)

Description

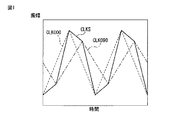

図1は、位相補間による位相シフトクロックの生成を説明する図である。

sin(ωt−θ)=sin(ωt)cosθ−cos(ωt)sinθ

≒CLK0×a−CLK90×(1−a)

ここで、aは位相シフト量に応じて決定される値である。

図1は、90°位相シフトした2つの三角波を合成することにより、中間の位相にシフトした信号の生成を説明する図である。

図2のタイミング信号発生回路は、位相比較回路11と、位相差ディジタルコード変換回路12と、ループフィルタ(Loop Filter)13と、位相制御ディジタルコード発生回路14と、位相合成回路(クロック発生回路)15と、を有する。位相比較回路11は、入力データ信号Dataと再生クロックclockとの位相差を検出し、位相差に応じてクロックタイミングの増加信号Upまたは減少信号Downを出力する。位相差ディジタルコード変換回路12は、UpおよびDown信号に対応する位相差ディジタルコードを出力する。ループフィルタ13は、ディジタル処理により位相差ディジタルコードの高周波成分を除去する。位相制御ディジタルコード発生回路14は、高周波成分が除去された位相差ディジタルコードに基づいて位相制御ディジタルコードを発生し、コードに対応したアナログ信号の位相制御信号(電流)I0、I90、I180、I270を発生する。位相合成回路15は、4相の位相クロックΦ0、Φ90、Φ180、Φ270を、各位相クロックの重み付けを表す位相制御信号に応じて合成する。位相合成回路15は、例えば、4相の位相クロックΦ0、Φ90、Φ180、Φ270が入力される4つの電流源による合計電流量を算出する回路で実現され、4つの電流源の電流量(バイアス量)を位相制御信号I0、I90、I180、I270に応じて変化させる。

図3に示すように、位相差ディジタルコードは、0から360度の位相を表し、位相制御ディジタルコードは、各位相に隣接する位相クロック(Φ0、Φ90、Φ180、Φ270)の合成における重み付けを示す。

第1実施形態のタイミング信号発生回路は、位相比較回路21と、チャージポンプ22と、反転スイッチ23と、ループフィルタ(Loop filter)24と、0,180度検出回路25と、90,270度検出回路26と、を有する。第1実施形態のタイミング信号発生回路は、さらに、0,90,180,270度検出回路27と、2相差動信号生成回路28と、合成位相選択回路29と、位相合成回路30と、を有する。第1実施形態は、ループフィルタ24が、単相の制御電圧信号Vcntl orgを発生する場合の例である。

合成位相選択回路29および位相合成回路30の回路およびその動作については後述する。

図5から図7を参照して、第1実施形態における制御に使用する信号についてまず説明する。

図8は、制御電圧信号生成部のうちのチャージポンプ22、反転スイッチ23およびループフィルタ24を含む回路構成を示す図である。

入力データ信号Dataに対して再生クロックclockの位相遅れている時には、Up信号が、進んでいる時には、Down信号が、位相比較回路21から入力する。位相比較回路21については広く知られているので、説明は省略する。

以下、第1実施形態のタイミング信号発生回路について、位相を変化させ続けた場合の動作シミュレーションを行った結果を説明する。

第2実施形態のタイミング信号発生回路は、位相比較回路21と、チャージポンプ22と、反転スイッチ23と、ループフィルタ(Loop filter)24と、0,180度検出回路25と、90,270度検出回路26と、を有する。第1実施形態のタイミング信号発生回路は、さらに、0,90,180,270度検出回路27と、2相差動信号生成回路28と、合成位相選択回路29と、位相合成回路30と、を有する。

22 チャージポンプ

23 反転スイッチ

24 ループフィルタ(Loop filter)

25 0,180度検出回路

26 90,270度検出回路

27 0,90,180,270度検出回路

28 2相差動信号生成回路

29 合成位相選択回路

30 位相合成回路

Claims (9)

- 入力信号とクロックとの位相差を検出する位相比較回路と、

検出した前記位相差に応じて、所定角度ごとに反転して高レベルと低レベル間で変化する2相差動の制御電圧信号を生成する制御電圧信号生成部と、

前記制御電圧信号を反転するタイミングを検出し、前記制御電圧信号の象限情報および反転タイミング信号を出力するタイミング検出回路と、

前記制御電圧信号および前記象限情報に基づいて、複数の位相クロックから、前記所定角度ごとに位相補間に用いる2相の位相クロックを選択し、位相補間における前記2相の位相クロックを合成するための位相制御信号を出力する合成位相選択回路と、

前記複数の位相クロックから選択した前記2相の位相クロックを、前記位相制御信号にしたがって合成することにより前記クロックを発生する位相合成回路と、を有するタイミング信号発生回路。 - 前記複数の位相クロックは、90度ずつずれた4相の位相クロックであり、前記制御電圧信号は、前記4相の位相クロックの90度ごとの象限に対応して反転する請求項1に記載のタイミング信号発生回路。

- 前記タイミング検出回路は、

前記制御電圧信号が前記高レベルまたは前記低レベルで反転するタイミングを検出し、0,180度検出信号および90,270度制御信号を出力する0,180度検出回路と、

前記制御電圧信号が前記高レベルまたは前記低レベルで反転するタイミングを検出し、90,270度検出信号および0,180度制御信号を出力する90,270度検出回路と、を有する請求項2に記載のタイミング信号発生回路。 - 前記0,180度検出回路は、前記制御電圧信号を高側閾値または低側閾値と比較し、前記制御電圧信号が前記高側閾値または前記低側閾値を超えると前記0,180度検出信号を出力する高側比較回路と、前記0,180度検出信号に応じて前記90,270度制御信号を生成する90,270度制御信号生成回路と、を有し、

前記90,270度検出回路は、前記制御電圧信号を前記高側閾値または前記低側閾値と比較し、前記制御電圧信号が前記高側閾値または前記低側閾値を超えると前記90,270度検出信号を出力する低側比較回路と、前記90,270度検出信号に応じて前記0,180度制御信号を生成する0,180度制御信号生成回路と、を有する請求項3に記載のタイミング信号発生回路。 - 前記0,180度検出回路は、前記制御電圧信号と、前記制御電圧信号の逆相信号にオフセット電圧を与えた逆相オフセット制御電圧信号を比較し、前記制御電圧信号が前記逆相オフセット制御電圧信号を超えると前記0,180度検出信号を出力する高側比較回路と、前記0,180度検出信号に応じて前記90,270度制御信号を生成する90,270度制御信号生成回路と、を有し、

前記90,270度検出回路は、前記制御電圧信号の逆相信号と、前記制御電圧信号にオフセット電圧を与えたオフセット制御電圧信号を比較し、前記制御電圧信号の逆相信号が前記オフセット制御電圧信号を超えると前記90,270度検出信号を出力する低側比較回路と、前記90,270度検出信号に応じて前記0,180度制御信号を生成する0,180度制御信号生成回路と、を有する請求項2に記載のタイミング信号発生回路。 - 前記タイミング検出回路は、

前記制御電圧信号の反転切り替え信号を生成する0,90,180,270度検出回路を有する請求項2に記載のタイミング信号発生回路。 - 前記制御電圧信号生成部は、

検出した前記位相差に応じて、充電信号および放電信号を出力するチャージポンプ回路と、

前記反転タイミング信号に応じて前記充電信号および前記放電信号の通過状態を切り替える反転スイッチと、

前記反転スイッチを通過する前記充電信号および前記放電信号により充電および放電が行われる容量を含むループフィルタと、を有する請求項1から6のいずれか1項に記載のタイミング信号発生回路。 - 前記合成位相選択回路は、選択した2相の位相クロック以外の位相クロックの重みがゼロである位相制御信号を出力し、

前記位相合成回路は、前記複数の位相クロックがそれぞれ入力される複数の電流源を有し、前記複数の電流源の電流を合成することにより前記クロックを合成し、前記位相制御信号にしたがって選択した前記2相の位相クロックが入力される電流源に前記位相制御信号にしたがった電流を流し、選択した前記2相の位相クロック以外の位相クロックが入力される電流源の電流をオフする請求項1から7のいずれか1項に記載のタイミング信号発生回路。 - 前記位相合成回路は、選択した前記2相の位相クロック以外の位相クロックが入力される電流源の電流をオフする時に、電流オフする限界付近になるように前記電流源をバイアスする請求項8に記載のタイミング信号発生回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014010352A JP6206212B2 (ja) | 2014-01-23 | 2014-01-23 | タイミング信号発生回路 |

| US14/570,256 US9160521B2 (en) | 2014-01-23 | 2014-12-15 | Timing signal generation circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014010352A JP6206212B2 (ja) | 2014-01-23 | 2014-01-23 | タイミング信号発生回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015139135A JP2015139135A (ja) | 2015-07-30 |

| JP6206212B2 true JP6206212B2 (ja) | 2017-10-04 |

Family

ID=53545764

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014010352A Expired - Fee Related JP6206212B2 (ja) | 2014-01-23 | 2014-01-23 | タイミング信号発生回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9160521B2 (ja) |

| JP (1) | JP6206212B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6361433B2 (ja) * | 2014-10-02 | 2018-07-25 | 富士通株式会社 | 周波数検出回路及び受信回路 |

| JP6479449B2 (ja) * | 2014-12-12 | 2019-03-06 | ラピスセミコンダクタ株式会社 | クロックデータリカバリ回路、位相同期回路及び半導体装置 |

| JP6839354B2 (ja) * | 2017-02-03 | 2021-03-10 | 富士通株式会社 | Cdr回路及び受信回路 |

| KR102649761B1 (ko) * | 2019-05-27 | 2024-03-20 | 삼성전자주식회사 | 클럭 위상 및 전압 오프셋 보정 방법 및 이를 수행하는 데이터 복원 회로 |

| TWI693796B (zh) * | 2019-11-08 | 2020-05-11 | 群聯電子股份有限公司 | 訊號產生電路、記憶體儲存裝置及訊號產生方法 |

| TWI831630B (zh) * | 2023-03-06 | 2024-02-01 | 瑞昱半導體股份有限公司 | 轉相控制器與轉相控制方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3039464B2 (ja) * | 1997-07-31 | 2000-05-08 | 日本電気株式会社 | クロック発生回路 |

| TW483255B (en) | 1999-11-26 | 2002-04-11 | Fujitsu Ltd | Phase-combining circuit and timing signal generator circuit for carrying out a high-speed signal transmission |

| JP4049511B2 (ja) | 1999-11-26 | 2008-02-20 | 富士通株式会社 | 位相合成回路およびタイミング信号発生回路 |

| JP3880302B2 (ja) | 2000-10-12 | 2007-02-14 | 富士通株式会社 | 位相合成回路およびタイミング信号発生回路 |

| US6586977B2 (en) * | 2000-09-22 | 2003-07-01 | Agere Systems Inc. | Four quadrant analog mixer-based delay-locked loop for clock and data recovery |

| JP3450293B2 (ja) * | 2000-11-29 | 2003-09-22 | Necエレクトロニクス株式会社 | クロック制御回路及びクロック制御方法 |

| US7515656B2 (en) | 2002-04-15 | 2009-04-07 | Fujitsu Limited | Clock recovery circuit and data receiving circuit |

| JP3942475B2 (ja) | 2002-04-15 | 2007-07-11 | 富士通株式会社 | クロック復元回路およびデータ受信回路 |

| JP3730607B2 (ja) | 2002-08-29 | 2006-01-05 | 株式会社東芝 | 差動データドライバー回路 |

| US7319345B2 (en) * | 2004-05-18 | 2008-01-15 | Rambus Inc. | Wide-range multi-phase clock generator |

| KR100630343B1 (ko) * | 2004-07-14 | 2006-09-29 | 삼성전자주식회사 | 아날로그 위상 보간 기술을 이용한 클록 데이터 복원 회로및 그 동작 방법 |

| US8085893B2 (en) * | 2005-09-13 | 2011-12-27 | Rambus, Inc. | Low jitter clock recovery circuit |

-

2014

- 2014-01-23 JP JP2014010352A patent/JP6206212B2/ja not_active Expired - Fee Related

- 2014-12-15 US US14/570,256 patent/US9160521B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20150207618A1 (en) | 2015-07-23 |

| JP2015139135A (ja) | 2015-07-30 |

| US9160521B2 (en) | 2015-10-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6206212B2 (ja) | タイミング信号発生回路 | |

| US7587012B2 (en) | Dual loop clock recovery circuit | |

| US9673972B2 (en) | Phase interpolator | |

| US9520883B2 (en) | Frequency detection circuit and reception circuit | |

| US7443219B2 (en) | Phase interpolation apparatus, systems, and methods | |

| JP4749168B2 (ja) | クロックアンドデータリカバリ回路 | |

| CN107846217B (zh) | 自我校正电路 | |

| JP2002190724A (ja) | クロックアンドデータリカバリ回路とそのクロック制御方法 | |

| CN106610688B (zh) | 用于旋转行波振荡器中相位线性度和内插的装置和方法 | |

| JP6337479B2 (ja) | 位相補間クロック発生回路 | |

| JP5273252B2 (ja) | 位相インタポレータ及び半導体回路装置 | |

| JP5900171B2 (ja) | デューティ比補正回路、ダブルエッジ装置及びデューティ比補正方法 | |

| JP2016220038A (ja) | 発振回路、電圧制御発振器、シリアルデータレシーバ | |

| JP5494323B2 (ja) | 受信回路 | |

| JP4825710B2 (ja) | 多相クロック生成回路およびシリアルデータ受信回路 | |

| JPWO2012131920A1 (ja) | 位相補正回路及び位相補正方法 | |

| US8983013B2 (en) | Signal processing circuit and signal processing method | |

| US9780797B2 (en) | CMOS interpolator for a serializer/deserializer communication application | |

| US11711200B2 (en) | Multiphase clock generators with digital calibration | |

| JP2008294492A (ja) | 多相クロック生成回路 | |

| WO2018217786A1 (en) | Multi-stage sampler with increased gain | |

| US11675386B2 (en) | System and method for recovering a clock signal | |

| CN114884504A (zh) | 时钟校正方法、时钟数据恢复电路、芯片、接收端和终端 | |

| JP2014116680A (ja) | クロック位相調整回路および受信回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161004 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170720 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170808 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170821 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6206212 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |