JP6204539B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6204539B2 JP6204539B2 JP2016135864A JP2016135864A JP6204539B2 JP 6204539 B2 JP6204539 B2 JP 6204539B2 JP 2016135864 A JP2016135864 A JP 2016135864A JP 2016135864 A JP2016135864 A JP 2016135864A JP 6204539 B2 JP6204539 B2 JP 6204539B2

- Authority

- JP

- Japan

- Prior art keywords

- photosensor

- data

- transistor

- pixel

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 100

- 238000006243 chemical reaction Methods 0.000 claims description 49

- 230000015654 memory Effects 0.000 claims description 46

- 230000006870 function Effects 0.000 claims description 45

- 230000035945 sensitivity Effects 0.000 claims description 39

- 238000001514 detection method Methods 0.000 claims description 32

- 230000001419 dependent effect Effects 0.000 claims description 3

- 238000003384 imaging method Methods 0.000 description 97

- 239000010408 film Substances 0.000 description 49

- 239000004973 liquid crystal related substance Substances 0.000 description 44

- 239000000758 substrate Substances 0.000 description 39

- 239000003990 capacitor Substances 0.000 description 30

- 238000003860 storage Methods 0.000 description 28

- 238000000034 method Methods 0.000 description 24

- 238000009792 diffusion process Methods 0.000 description 13

- 238000012545 processing Methods 0.000 description 11

- 238000004519 manufacturing process Methods 0.000 description 7

- 125000006850 spacer group Chemical group 0.000 description 7

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 238000009825 accumulation Methods 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 229910021417 amorphous silicon Inorganic materials 0.000 description 4

- 239000000470 constituent Substances 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 239000012535 impurity Substances 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 3

- 230000001186 cumulative effect Effects 0.000 description 3

- 230000009975 flexible effect Effects 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 230000014759 maintenance of location Effects 0.000 description 3

- 239000003550 marker Substances 0.000 description 3

- 239000000049 pigment Substances 0.000 description 3

- 239000009719 polyimide resin Substances 0.000 description 3

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 3

- 230000003936 working memory Effects 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 238000012905 input function Methods 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- 238000005457 optimization Methods 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- 238000003079 width control Methods 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 244000228957 Ferula foetida Species 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- 206010034972 Photosensitivity reaction Diseases 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 239000006229 carbon black Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 208000037265 diseases, disorders, signs and symptoms Diseases 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 210000000887 face Anatomy 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 210000000554 iris Anatomy 0.000 description 1

- 238000012886 linear function Methods 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000036211 photosensitivity Effects 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920002451 polyvinyl alcohol Polymers 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 238000005086 pumping Methods 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 210000003462 vein Anatomy 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/1461—Pixel-elements with integrated switching, control, storage or amplification elements characterised by the photosensitive area

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/1613—Constructional details or arrangements for portable computers

- G06F1/1633—Constructional details or arrangements of portable computers not specific to the type of enclosures covered by groups G06F1/1615 - G06F1/1626

- G06F1/1637—Details related to the display arrangement, including those related to the mounting of the display in the housing

- G06F1/1643—Details related to the display arrangement, including those related to the mounting of the display in the housing the display being associated to a digitizer, e.g. laptops that can be used as penpads

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/0412—Digitisers structurally integrated in a display

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/0416—Control or interface arrangements specially adapted for digitisers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/0416—Control or interface arrangements specially adapted for digitisers

- G06F3/04166—Details of scanning methods, e.g. sampling time, grouping of sub areas or time sharing with display driving

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/042—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by opto-electronic means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/14612—Pixel-elements with integrated switching, control, storage or amplification elements involving a transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

- H01L27/14645—Colour imagers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/14692—Thin film technologies, e.g. amorphous, poly, micro- or nanocrystalline silicon

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/70—Circuitry for compensating brightness variation in the scene

- H04N23/73—Circuitry for compensating brightness variation in the scene by influencing the exposure time

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/51—Control of the gain

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

Description

装置とその駆動方法に関する。

また、近年では、表示装置に撮像機能を持たせることで、入力機能を持たせたタッチパネ

ルが注目されている。タッチパネルは、パネルを直接指などで触れて操作できる表示装置

であり、タッチスクリーンなどとも呼ばれている。

ることで、表示領域が入力領域を兼ねることができる。一例として、特許文献1に画像取

り込み機能を備えた半導体装置が開示されている。

が強すぎる又は弱すぎる場合に、入射光が半導体装置の撮像の精度に影響を及ぼすという

問題がある。撮像の精度が低下すると、検出位置の誤認識や、取り込み画像(撮像データ

)が不鮮明になるなどの撮像不良が起きやすい。特に、外部からの光(外光)の影響を受

けることにより、上記のような問題が生じやすい。

の一とする。または、使用環境による撮像不良を防ぐ半導体装置の駆動方法を提供するこ

とを目的の一とする。

置を提供することを目的の一とする。または、入射光の強度によらず、高精度な撮像デー

タを取得することができる半導体装置の駆動方法を提供することを目的の一とする。

第2のフォトセンサと、第2のフォトセンサで取得された外光強度に応じて、第1のフォ

トセンサの駆動条件を設定するコントローラと、を有し、コントローラで設定された駆動

条件に応じて、第1のフォトセンサの感度を変更した上で撮像を行う半導体装置である。

これにより、半導体装置は、入射光の強度に応じて感度を最適化した第1のフォトセンサ

を用いて、撮像を行うことができる。

動電圧を設定することができる。

第2のフォトセンサと、第2のフォトセンサで取得された外光強度に応じて、第1のフォ

トセンサの駆動条件を設定するコントローラと、を有し、コントローラは、第1のレジス

タ、変換テーブル、CPU、第1のメモリ、タイミングコントローラ、及び電源回路を含

み、タイミングコントローラは、第2のレジスタを含み、電源回路は、第3のレジスタを

含み、第1のレジスタには、第2のフォトセンサで取得された外光強度のデータが格納さ

れ、変換テーブルには、外光強度に応じて第1のフォトセンサの駆動条件を規定するデー

タが格納され、CPUは、第1のメモリに格納されたプログラムの命令に従い、第1のレ

ジスタに格納されたデータ及び変換テーブルに格納されたデータを用いて、第2のレジス

タ及び第3のレジスタにそれぞれ格納するデータを生成し、タイミングコントローラは、

第2のレジスタに格納されたデータを用いて、第1のフォトセンサの駆動タイミング信号

を生成し、電源回路は、第3のレジスタに格納されたデータを用いて、第1のフォトセン

サの駆動電圧を生成し、コントローラで設定された駆動タイミング信号及び駆動電圧に応

じて、第1のフォトセンサの感度を変更した後に撮像を行う半導体装置である。

第2のフォトセンサと、第2のフォトセンサで取得された外光強度に応じて、第1のフォ

トセンサの駆動条件を設定するコントローラと、を有し、コントローラは、第1のレジス

タ、変換テーブル、CPU、第1のメモリ、第2のメモリ、タイミングコントローラ、及

び電源回路を含み、タイミングコントローラは、第2のレジスタを含み、電源回路は、第

3のレジスタを含み、第1のレジスタには、第2のフォトセンサで取得された外光強度の

データが格納され、変換テーブルには、外光強度に応じて第1のフォトセンサの駆動条件

を規定するデータが格納され、CPUは、第1のメモリに格納されたプログラムの命令に

従い、第1のレジスタに格納されたデータ及び変換テーブルに格納されたデータを用いて

、第2のメモリを用いてプログラムを実行して、第2のレジスタ及び第3のレジスタにそ

れぞれ格納するデータを生成し、タイミングコントローラは、第2のレジスタに格納され

たデータを用いて、第1のフォトセンサの駆動タイミング信号を生成し、電源回路は、第

3のレジスタに格納されたデータを用いて、第1のフォトセンサの駆動電圧を生成し、コ

ントローラで設定された駆動タイミング信号及び駆動電圧に応じて、第1のフォトセンサ

の感度を変更した後に撮像を行う半導体装置である。

を含み、第3のレジスタに格納されたデータを、D/A変換回路で電圧出力に変換し、増

幅回路で増幅することにより、第1のフォトセンサの駆動電圧として生成することができ

る。

とすることができる。

。また、ローレベルのときの電位を単に「L」又は「ロー」ともいう。

限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり

、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」また

は複数の「配線」が一体となって形成されている場合なども含む。

化する場合などには、「ソース」や「ドレイン」の機能は入れ替わることがある。このた

め、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることが

できるものとする。

の」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するも

の」は、接続対象に対して電気信号の授受を可能とするものであれば、特に制限を受けな

い。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジ

スタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を

有する素子などが含まれる。

けにくくすることができ、入射光の強度によらず、高精度な撮像データを取得することが

可能となる。

は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することな

くその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従っ

て、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、実施の

形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符

号を付す場合があり、繰り返しの説明は省略する。

本実施の形態に係る半導体装置は撮像機能を備えており、画素に設けられたフォトセン

サと、画素の周辺に設けられたフォトセンサと、コントローラと、を少なくとも有する。

コントローラは、画素の周辺に設けられたフォトセンサで取得された外光強度に応じて、

画素に設けられたフォトセンサの駆動条件を設定する。本形態に係る半導体装置は、コン

トローラで設定された駆動条件に応じて、画素に設けられたフォトセンサの感度を変更し

た上で撮像を行うことができる。

ンサ」とし、画素の周辺(画素外)に設けられたフォトセンサを「第2のフォトセンサ」

ともいう。

得する。コントローラは、第2のフォトセンサで取得された外光強度に応じて、第1のフ

ォトセンサの駆動条件を変更する。第1のフォトセンサは、前記コントローラで設定され

た駆動条件に応じて感度を変更する。

することで、感度を変更することができる。蓄積期間、又は読み出し期間などの駆動条件

の変更は、スタートパルス間隔の変更、クロック周波数の変更、又はパルス幅制御信号の

変更など駆動用のタイミング信号(駆動用タイミング信号)を制御することにより行うこ

とができる。

影響を抑え、高精度な撮像データを取得することが可能となる。

強度から、画素に設けられたフォトセンサ(第1のフォトセンサ1000)の感度を変更

するために、図1に示すコントローラ1100の構成を用いることができる。図1におい

て、コントローラ1100は、CPU1110、プログラムメモリ1120、外光強度デ

ータ用レジスタ1130、変換テーブル1140、作業用メモリ1150、タイミングコ

ントローラ1160、及び電源回路1170から構成される。タイミングコントローラ1

160は、制御データ用レジスタ1162を有する。電源回路1170は、制御データ用

レジスタ1172、D/A変換回路1174、及び増幅回路1176を有する。

いるが、名称は機能の表現に限定されず、序数詞が付された名称とすることができる。本

形態では、「プログラムメモリ」を「第1のメモリ」、「作業用メモリ」を「第2のメモ

リ」、「変換テーブル」を「第3のメモリ」とすることができる。また、「外光強度デー

タ用レジスタ」を「第1のレジスタ」、タイミングコントローラが有する「制御データ用

レジスタ」を「第2のレジスタ」、電源回路が有する「制御データ用レジスタ」を「第3

のレジスタ」とすることができる。

外光強度データ用レジスタ1130に格納されたデータ及び変換テーブル1140に格納

されたデータを用いて、タイミングコントローラ1160の制御データ用レジスタ116

2に格納するデータ及び電源回路1170の制御データ用レジスタ1172に格納するデ

ータを生成する。なお、作業用メモリ1150は、プログラムの命令を実行するために必

要なメモリ空間として用いることができる。

1120、外光強度データ用レジスタ1130、変換テーブル1140、制御データ用レ

ジスタ1162、制御データ用レジスタ1172、及び作業用メモリ1150は、ソフト

ウェア上はCPU1110と同一のアドレス空間に存在する構成とすることができる。す

なわち、プログラムメモリ1120、外光強度データ用レジスタ1130、変換テーブル

1140、制御データ用レジスタ1162、制御データ用レジスタ1172、及び作業用

メモリ1150は、ソフトウェア上は、特定の番地に割り振られたデータ領域とみなすこ

とができる。したがって、CPU1110が、プログラムメモリ1120、外光強度デー

タ用レジスタ1130、変換テーブル1140、制御データ用レジスタ1162、制御デ

ータ用レジスタ1172、又は作業用メモリ1150に、データの読み出しを行うとは、

ソフトウェア上は、特定の番地へのデータ読み出しを意味する。CPU1110が、プロ

グラムメモリ1120、外光強度データ用レジスタ1130、変換テーブル1140、制

御データ用レジスタ1162、制御データ用レジスタ1172、又は作業用メモリ115

0に、データの格納を行うとは、ソフトウェア上は、特定の番地へのデータの格納を意味

する。

リ1120は、プログラムアドレス空間に存在し、外光強度データ用レジスタ1130、

変換テーブル1140、制御データ用レジスタ1162、制御データ用レジスタ1172

、及び作業用メモリ1150は、プログラムアドレス空間とは異なるデータアドレス空間

に存在する構成とすることができる。プログラムアドレス空間とデータアドレス空間とを

ソフトウェア上で区別することで、両アドレス空間へのアクセスが効率的に行え、CPU

1110の処理能力を高め易くなる。

レス空間上の特定の番地に割り振られたデータ領域とみなすことができる。また、外光強

度データ用レジスタ1130、変換テーブル1140、制御データ用レジスタ1162、

制御データ用レジスタ1172、及び作業用メモリ1150は、ソフトウェア上は、デー

タアドレス空間上の特定の番地に割り振られたデータ領域とみなすことができる。

とは、ソフトウェア上は、プログラムアドレス空間の特定の番地からのデータ読み出しを

意味する。また、外光強度データ用レジスタ1130、変換テーブル1140、制御デー

タ用レジスタ1162、制御データ用レジスタ1172、又は作業用メモリ1150に、

データの読み出しを行うとは、ソフトウェア上は、データアドレス空間の特定の番地への

データ読み出しを意味する。外光強度データ用レジスタ1130、変換テーブル1140

、制御データ用レジスタ1162、制御データ用レジスタ1172、又は作業用メモリ1

150に、データの格納を行うとは、ソフトウェア上は、データアドレス空間の特定の番

地へのデータ格納を意味する。

度のデータを格納する。例えば、外光強度データ用レジスタ1130は、第2のフォトセ

ンサ1200で取得した外光強度を示すデジタルデータを格納する。

規定するデータを格納している。

タに従って、第1のフォトセンサ1000の駆動タイミング信号を生成する。制御データ

用レジスタ1162には、第2のフォトセンサ1200で取得した外光強度に対応してC

PU1110で生成されたデータが格納されている。したがって、タイミングコントロー

ラ1160は、第2のフォトセンサ1200で取得した外光強度に応じた第1のフォトセ

ンサ1000の駆動タイミング信号を生成することとなる。

間)若しくは周期、スタート信号のタイミング、パルス幅(ハイの期間)若しくは周期、

又はパルス幅制御信号のタイミング、パルス幅(ハイの期間)若しくは周期を変更するこ

とで行うことができる。

1のフォトセンサ1000の駆動電圧を生成する。制御データ用レジスタ1172には、

第2のフォトセンサ1200で取得した外光強度に対応してCPU1110で生成された

データが格納されている。したがって、電源回路1170は、第2のフォトセンサ120

0で取得した外光強度に応じた第1のフォトセンサ1000の駆動電圧を生成することと

なる。

ータを、アナログ値である電圧出力に変換する。D/A変換回路1174には、抵抗方式

、又は容量方式などの公知の回路を用いることができる。また、増幅回路1176は、D

/A変換回路1174から出力された電圧出力の電力を増幅する。増幅された電圧出力は

、第1のフォトセンサ1000の駆動電圧となる。駆動電圧には、第1のフォトセンサ1

000の基準電位、第1のフォトセンサ1000を駆動するための駆動回路への駆動電圧

などが含まれる。

ォトセンサ1000の感度を変更した上で、撮像を行う。このようにすることで、最適化

されたフォトセンサ(第1のフォトセンサ1000)を用いた撮像を行うことができ、高

精度な撮像データの取得が可能となる。

のフォトセンサ1000)の感度を実現し得る駆動条件をあらかじめ取得しておき、当該

駆動条件を定義するデータを変換テーブル1140に格納しておくことが望ましい。変換

テーブル1140へのデータの格納は、CPU1110で行うことができる。

レジスタ1130に格納されたデータに対応して制御データ用レジスタ1162に格納す

るデータ及び制御データ用レジスタ1172に格納するデータを直接格納する形式がある

。また、第2の形式として、外光強度データ用レジスタ1130に格納されたデータを独

立変数とし、制御データ用レジスタ1162に格納するデータ及び制御データ用レジスタ

1172に格納するデータを従属変数とする関数を定義するパラメータ・データを格納す

る形式がある。

40をメモリで構成する。外光強度データ用レジスタ1130に格納されているデータX

でメモリ(変換テーブル1140)のアドレスを指定する。当該アドレスに該当するデー

タ領域に、制御データ用レジスタ1162及び制御データ用レジスタ1172に格納すべ

きデータYを格納しておけばよい。なお、上記アドレスは、外光強度データ用レジスタ1

130に格納されているデータXを下位ビット、アドレス空間上で制御データ用レジスタ

1162及び制御データ用レジスタ1172に割り振られているアドレスZを上位ビット

、として形成することができる。なお、データ「X」、データ「Y」は、説明のため便宜

的に「X」、「Y」を付記して区別したものである。

から制御データ用レジスタ1162及び制御データ用レジスタ1172に格納するデータ

の生成が、ソフトウェア上で、CPU1110が変換テーブル1140からデータの読み

出しを1回行うだけで実現できる。そのため、CPU1110の負荷が少なく、容易に行

える。

40をメモリで構成する。外光強度データ用レジスタ1130に格納されたデータを独立

変数X、制御データ用レジスタ1162及び制御データ用レジスタ1172に格納するデ

ータを従属変数Yとし、この関係がY(X)=A・X+Bで表せる時、パラメータ・デー

タ(A,B)を上記メモリ(変換テーブル1140)に格納しておく。CPU1110は

、外光強度データ用レジスタ1130に格納されたデータXを読み出し、A・X+Bの演

算を行い、演算結果を制御データ用レジスタ1162及び制御データ用レジスタ1172

に格納するデータYとし、制御データ用レジスタ1162及び制御データ用レジスタ11

72それぞれに格納する。なお、ここでは一例として、XとYの関係を一次関数で表した

が、より複雑な関数形で表すことも可能である。

から、制御データ用レジスタ1162及び制御データ用レジスタ1172に格納するデー

タの生成を、より細かい精度で行うことができる。特に、広範の外光強度に対して、精度

良くフォトセンサ(第1のフォトセンサ1000)の駆動条件を定義する場合、第2の形

式は、第1の形式よりも変換テーブル1140に用いるメモリの容量が少なくて済む。

記メモリは、フラッシュメモリなどの不揮発性記憶装置で構成することが望ましい。不揮

発性記憶装置で構成することで、例えば、半導体装置の出荷時に一度メモリにデータを格

納しておけば、利用者が半導体装置の電源を切る度に、再度メモリにデータを格納しなく

てもいいという効果を得ることができる。

発性記憶装置とフラッシュメモリなどの不揮発性記憶装置とで構成し、半導体装置の起動

時にフラッシュメモリに格納したデータをSRAMまたはDRAMに格納し、半導体装置

の動作時はSRAMまたはDRAMからデータの読み出しを行う構成としてもよい。

ンサ1200により外光強度を取得し、コントローラ1100が第2のフォトセンサ12

00により取得された外光強度に応じて画素に設けられた第1のフォトセンサ1000の

駆動条件を変更し、コントローラ1100から与えられる駆動条件により第1のフォトセ

ンサ1000の感度を変更した上で撮像を行う。外光強度に応じて画素に設けられたフォ

トセンサの駆動条件を調整することにより、画素に設けられたフォトセンサの感度を最適

化した上で、撮像を行うことができる。したがって、室内や屋外など、使用環境等による

入射光の強度の強弱によらず、撮像の際における入射光の強度の影響を抑えることができ

、高精度な撮像データを取得することができる。

合わせることができる。

本形態では、実施の形態1と異なるコントローラの構成について説明する。なお、図1

と同じ構成については同じ符号を付し、詳細な説明は省略する。

いて、コントローラ2100は、専用処理回路2110、外光強度データ用レジスタ11

30、タイミングコントローラ1160、及び電源回路1170から構成される。専用処

理回路2110は、変換テーブル2112を有する。タイミングコントローラ1160は

、制御データ用レジスタ1162を有する。電源回路1170は、制御データ用レジスタ

1172、D/A変換回路1174、及び増幅回路1176を有する。

20、変換テーブル1140、及び作業用メモリ1150の代わりに、変換テーブル21

12を含む専用処理回路2110を有する点にある。

いるが、図1及びその説明と同様に名称は機能の表現に限定されず、序数詞が付された名

称とすることができる。本形態では、「外光強度データ用レジスタ」を「第1のレジスタ

」、タイミングコントローラが有する「制御データ用レジスタ」を「第2のレジスタ」、

電源回路が有する「制御データ用レジスタ」を「第3のレジスタ」とすることができる。

変換テーブル2112に格納されたデータを用いて、タイミングコントローラ1160の

制御データ用レジスタ1162に格納するデータ及び電源回路1170の制御データ用レ

ジスタ1172に格納するデータを生成するための専用回路である。

規定するデータを格納している。変換テーブル2112としては、上記実施の形態1で示

した変換テーブル1140を適用することができる。データの格納形式などについても、

上記実施の形態1に準じる。

タ1162に格納された制御データに従って、第1のフォトセンサ1000の駆動タイミ

ング信号を生成する。また、電源回路1170が、制御データ用レジスタ1172に格納

されたデータに従って、第1のフォトセンサ1000の駆動電圧を生成する。

ォトセンサ1000の感度を変更した上で、撮像を行う。このようにすることで、最適化

されたフォトセンサ(第1のフォトセンサ1000)を用いた撮像を行うことができ、高

精度な撮像データを取得できる。

サ1200により外光強度を取得し、コントローラ2100が第2のフォトセンサ120

0により取得された外光強度に応じて画素に設けられた第1のフォトセンサ1000の駆

動条件を変更し、コントローラ2100から与えられる駆動条件により第1のフォトセン

サ1000の感度を変更した上で撮像を行う。外光強度に応じて画素に設けられたフォト

センサの駆動条件を調整することにより、画素に設けられたフォトセンサの感度を最適化

した上で、撮像を行うことができる。したがって、撮像の際における外光強度の影響を抑

えることができ、高精度な撮像データを取得できる。

合わせることができる。

本形態では、上記実施の形態1又は2で示すコントローラを備えた半導体装置について

説明する。ここでは、半導体装置として、固体撮像素子(イメージセンサともいわれる)

の例について、図3〜図7を用いて説明する。

301、制御回路部331、コントローラ311、及びセンサ部371を有する。

又は上記実施の形態2で示したコントローラ2100の構成を適用する。画素部301は

、少なくとも上記実施の形態1又は2の第1のフォトセンサ1000を備える。センサ部

371は、少なくとも上記実施の形態1又は2の第2のフォトセンサ1200を備える。

する。各々の画素333は、第1のフォトセンサ335(上記実施の形態1又は2の第1

のフォトセンサ1000に相当する)を有する。第1のフォトセンサ335は、画素部3

01に接触又は接近した被検出物を検出し撮像することができる。

トランジスタとを有する。受光することで電気信号を発する機能を有する素子としては、

具体的にフォトダイオードが挙げられる。

いるのか、又は外光が画素部301に入射されているか、を、判別することで、被検出物

を検出する。

側のフォトセンサ読み出し回路351と、走査線側のフォトセンサ駆動回路355を有す

る。走査線側のフォトセンサ駆動回路355は、特定の行に配置された画素が有する第1

のフォトセンサ335に対して、後述するリセット動作と選択動作とを行う機能を有する

。また、信号線側のフォトセンサ読み出し回路351は、選択された行の画素が有する第

1のフォトセンサ335の出力信号を取り出す機能を有する。なお、信号線側のフォトセ

ンサ読み出し回路351は、アナログ信号であるフォトセンサの出力を、OPアンプを用

いてアナログ信号のまま固体撮像素子外部に取り出す構成や、A/D変換回路を用いてデ

ジタル信号に変換してから固体撮像素子外部に取り出す構成が考え得る。

フォトセンサ1200に相当する)を備える。センサ部371は、第2のフォトセンサに

より外光強度のデータを取得する。また、センサ部371は、コントローラ311に外光

強度のデータを転送するため、出力処理回路等の各種処理回路を備えることが好ましい。

センサ部371としては、フォトICを適用することができる。

35と同様に、受光することで電気信号を発する機能を有する素子と、トランジスタとを

有する構成とすることができる。受光することで電気信号を発する機能を有する素子とし

ては、具体的にフォトダイオードが挙げられる。

素333は、フォトダイオード344、トランジスタ341及びトランジスタ342を含

む第1のフォトセンサ335を有する。また、各画素は、信号線側のフォトセンサ読み出

し回路351に接続された第1の配線336及び第2の配線337と、走査線側のフォト

センサ駆動回路355に接続された第3の配線338及び第4の配線339を有する。

スタ341のゲートに電気的に接続されている。ここでは、フォトダイオード344とト

ランジスタ341のゲートとを電気的に接続する配線をゲート信号線343としている。

トランジスタ341は、ソース又はドレインの一方が第1の配線336に、ソース又はド

レインの他方がトランジスタ342のソース又はドレインの一方に電気的に接続されてい

る。トランジスタ342は、ゲートが第4の配線339に、ソース又はドレインの他方が

第2の配線337に電気的に接続されている。

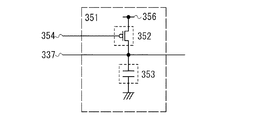

において、画素1列分のフォトセンサ読み出し回路351は、p型トランジスタ352、

及び保持容量353を有する。また、当該画素列の第2の配線337、第5の配線354

を有する。第5の配線354は、フォトセンサの動作に先立って、第2の配線337のプ

リチャージを行うための配線である。

5の動作に先立ち、第2の配線337の電位を基準電位に設定する。図5では、第5の配

線354の電位を”L”とすることで、第2の配線337を基準電位である高電位に設定

することができる。保持容量353は、第2の配線337の寄生容量が大きい場合には設

けなくてもよい。なお、基準電位は、低電位とする構成も可能である。この場合、p型ト

ランジスタ352の代わりにn型トランジスタを用い、第5の配線354の電位を”H”

とすることで、第2の配線337を基準電位である低電位に設定することができる。

のタイミングチャートを用いて説明する。図6の信号401は、図4における第3の配線

338の電位に相当する。図6の信号402は、図4における第4の配線339の電位に

相当する。図6の信号403は、図4におけるトランジスタ341のゲートが接続された

ゲート信号線343の電位に相当する。図6の信号404は、図4、図5における第2の

配線337の電位に相当する。また、図6の信号405は、図5における第5の配線35

4の電位に相当する。

作)と、フォトダイオード344が導通し、トランジスタ341のゲートが接続されたゲ

ート信号線343の電位(信号403)が”H”となる。また、第5の配線354の電位

(信号405)を”L”とすると、第2の配線337の電位(信号404)は”H”にプ

リチャージされる。

と、フォトダイオード344のオフ電流により、トランジスタ341のゲートが接続され

たゲート信号線343の電位(信号403)が低下し始める。フォトダイオード344は

、光が照射されるとオフ電流が増大するので、照射される光の量に応じてトランジスタ3

41のゲートが接続されたゲート信号線343の電位(信号403)は変化する。すなわ

ち、トランジスタ341のソースとドレイン間の電流が変化する。

と、トランジスタ342が導通し、第1の配線336と第2の配線337とが、トランジ

スタ341とトランジスタ342とを介して導通する。すると、第2の配線337の電位

(信号404)は、低下していく。なお、時刻C以前に、第5の配線354の電位(信号

405)の電位は”H”とし、第2の配線337のプリチャージを終了しておく。ここで

、第2の配線337の電位(信号404)が低下する速さは、トランジスタ341のソー

スとドレイン間の電流に依存する。すなわち、フォトダイオード344に照射されている

光の量に応じて変化する。

スタ342が遮断され、第2の配線337の電位(信号404)は、時刻D以後、一定値

となる。ここで、一定値となる値は、フォトダイオード344に照射されている光の量に

応じて変化する。したがって、第2の配線337の電位を取得することで、フォトダイオ

ード344に照射されている光の量を知ることができる。

積動作、及び選択動作を繰り返すことで実現される。固体撮像素子において、全画素にお

けるフォトセンサのリセット動作、累積動作、及び選択動作を実行することで、画素部3

01に接触又は接近した被検出物を撮像することができる。

、撮像データが不鮮明になる可能性がある。したがって、使用環境等による外光強度の影

響を受けて、撮像の精度が低下し、撮像データが不鮮明になる可能性がある。ここで、入

射光の強度が適正である場合、入射光の強度が強い場合、入射光の強度が弱い場合につい

て、被検出物の撮像データにおける輝度のヒストグラムを用いて説明する。

、横軸は輝度値である。輝度値は最小を0、最大を255とした。

る。実線1301は、被検出物の検出位置を示すピーク1302と検出位置以外を示すピ

ーク1303との2つのピークの輝度値が分離しているため、撮像データにおいて明暗の

区別が明確である。

11は、検出位置を示すピーク1302と検出位置以外を示すピーク1312との2つの

ピークの輝度値が接近している。2つのピークは、さらに接近するとピークが1つしか確

認できなくなり、撮像データにおいて明暗の区別が困難になる。そのため、被検出物を正

確に認識することが難しくなり、検出位置の判断も困難になる可能性がある。

21は、検出位置以外を示すピーク1322の1つしかピークが確認できないため、撮像

データにおいて明暗の区別が困難になる。そのため、被検出物を正確に認識することが難

しくなり、検出位置の判断も困難になる可能性がある。

2つのピークを確認することが難しくなり、撮像データの明暗の区別が難しくなってしま

う。そのため、被検出物を正確に認識することが難しくなり、検出位置の判断が困難にな

ってしまう。

ラムのように2つのピークの輝度値が分離して得られるようにするため、画素部301の

周辺(画素部301の外)に設けられたセンサ部371を用いて外光強度を取得し、外光

強度に応じてコントローラ311により第1のフォトセンサ335の感度を変更する。セ

ンサ部371を用いて外光強度を取得し、外光強度に応じてコントローラ311により第

1のフォトセンサ335の感度を変更することで最適化を行い、最適化された第1のフォ

トセンサ335を用いて撮像を行う。このようにすることで、使用環境等による外光強度

の強弱により受ける影響を最小限にしつつ、高精度な撮像データを取得することができる

固体撮像素子300を実現できる。

の配線338の電位(信号401)を変更して、フォトダイオード344に印加される電

圧、すなわちトランジスタ341のゲートに印加される電圧(信号403)を変更する、

(2)第1の配線336の電位と第6の配線356との電位差を変更して、トランジスタ

341のソースとドレインとの間に印加される電圧を変更する、(3)第1のフォトセン

サ335の累積動作に要する時間(累積時間:時刻Bから時刻Cまでの時間)を変更する

ことが挙げられる。また、これらの手法を組み合わせて感度を変更することも効果的であ

る。(1)〜(3)のような各配線の電位の変更やフォトセンサの累積動作に要する時間

の変更は、コントローラ311により行う。コントローラ311は、具体的には上記実施

の形態1又は実施の形態2に示すような構成を適用する。

を蓄積することができる量が増えるため第1のフォトセンサ335の感度が向上する。(

2)の手法では、トランジスタ341のソースとドレインとの間の電圧を大きくすること

で、電荷を蓄積することができる量が増えるため、第1のフォトセンサ335の感度が向

上する。そして(3)の手法では、累積時間を長くすることで電荷を蓄積する時間が長く

なるため、第1のフォトセンサ335の感度が向上する。(1)〜(3)の手法を用いる

ことで、入射光の強度が弱い使用環境においても、フォトセンサの感度を向上させ、撮像

の精度を高めることができる。また、入射光の強度が強い使用環境の場合は、逆の処理の

動作を行い第1のフォトセンサ335の感度を下げることで撮像の精度を高めることがで

きる。

触している場合だけでなく、非接触の場合にも検出を行うことができる。しかし、非接触

の被検出物は、画素部から被検出物が離れるに伴い被検出物の影が淡くなり明暗の区別が

困難になるため、接触している被検出物よりも検出が困難である。したがって、(1)〜

(3)の手法を用いて画素に設けられたフォトセンサの感度を向上させることで、非接触

の被検出物に対しても高精度な撮像データを取得することができる。

合わせることができる。

本形態では、上記実施の形態3と異なる半導体装置について説明する。ここでは、半導

体装置として表示装置の例を、図8、図9を用いて説明する。なお、図3の固体撮像素子

と同じ構成については同じ符号を付し、詳細な説明は省略する。

制御回路部331(以下、「第1の制御回路部331」ともいう)、第2の制御回路部5

63、コントローラ311、及びセンサ部371を有する。

又は上記実施の形態2で示したコントローラ2100の構成を適用する。画素部501は

、少なくとも上記実施の形態1又は2の第1のフォトセンサ1000を備える。センサ部

371は、少なくとも上記実施の形態1又は2の第2のフォトセンサ1200を備える。

する。各々の画素533は、第1のフォトセンサ335(上記実施の形態1又は2の第1

のフォトセンサ1000に相当する)及び表示素子537を有する。第1のフォトセンサ

335は、画素部501に接触又は接近した被検出物を検出し撮像することができる。

回路部563の有無にある。図3に示す構成の固体撮像素子は撮像の機能を有する。一方

、図8に示す構成の表示装置は、撮像の機能に加え、画像を表示する機能を有している。

そのため、図8に示す表示装置は、入力と表示の2つの機能を併せ持つことができる。こ

のような表示装置としては、タッチパネルなどが挙げられる。

、液晶層を有する。

電荷の排出を制御する機能を有する。保持容量は、液晶層に印加する電圧に相当する電荷

を保持する機能を有する。液晶層に電圧を印加することで偏光方向が変化することを利用

して、液晶層を透過する光の明暗(階調)を作ることで、画像を表示できる。液晶層を透

過する光には、光源(例えばバックライト)によって液晶表示装置の裏面から照射される

光を用いる。

に発光素子などの他の素子を有していてもよい。発光素子は、電流又は電圧によって輝度

が制御される素子であり、具体的には発光ダイオード、OLED(Organic Li

ght Emitting Diode)等が挙げられる。

トランジスタとを有する。受光することで電気信号を発する機能を有する素子としては、

具体的にフォトダイオードが挙げられる。

きているのか、又は外光が画素部501に入射されているか、を、判別することで、被検

出物を検出する。つまり、第1のフォトセンサ335は、外光を利用して被検出物を検出

することができる。また、第1のフォトセンサ335は、バックライトなどの光源から照

射され、被検出物により反射された反射光を利用して、被検出物を検出することができる

。さらに、第1のフォトセンサ335は、外光と反射光との両方を利用して、被検出物の

検出を行うこともできる。

回路部563は、ビデオデータ信号線などの信号線(「ソース信号線」ともいう。)を介

して表示素子537に信号を入力する表示素子駆動回路555と、走査線(「ゲート信号

線」ともいう。)を介して表示素子537に信号を入力する表示素子駆動回路551を有

する。例えば、表示素子駆動回路551は、特定の行に配置された画素が有する表示素子

を選択する機能を有する。また、表示素子駆動回路555は、選択された行の画素が有す

る表示素子に任意の電位を与える機能を有する。なお、表示素子駆動回路551により高

電位(「ハイレベル」の電位)を印加された表示素子では、トランジスタが導通状態とな

り、表示素子駆動回路555により与えられる電荷が供給される。

。

スタ541、保持容量542及び液晶素子543を有する表示素子537と、フォトダイ

オード344、トランジスタ341及びトランジスタ342を有する第1のフォトセンサ

335とを有する。

第7の配線562に、ソース又はドレインの他方が保持容量542の一方の電極及び液晶

素子543の一方の電極に電気的に接続されている。保持容量542の他方の電極は一定

の電位に保たれている。液晶素子543の他方の電極は一定の電位に保たれている。液晶

素子543は、一対の電極と、一対の電極の間に挟まれた液晶層と、を含む素子である。

2の電位を保持容量542と液晶素子543に印加する。保持容量542は、印加された

電位を保持する。液晶素子543は、印加された電位により、光の透過率を変更する。

スタ341のゲートに電気的に接続されている。トランジスタ341は、ソース又はドレ

インの一方が第1の配線336に、ソース又はドレインの他方がトランジスタ342のソ

ース又はドレインの一方に電気的に接続されている。トランジスタ342は、ゲートが第

4の配線339に、ソース又はドレインの他方が第2の配線337に電気的に接続されて

いる。

については、上記実施の形態3の説明に準じる。具体的には、フォトセンサ読み出し回路

351の構成として上述した図5の構成を適用することができる。また、第1のフォトセ

ンサ335の読み出し動作については、図6のタイミングチャートを用いた説明を適用す

ることができる。

射光の強度が強すぎる場合又は弱すぎる場合、撮像の精度が低下し、撮像データが不鮮明

になる可能性がある。

トグラムのように2つのピークの輝度値が分離して得られるようにするため、画素部50

1の周辺(画素部501の外部)に設けられたセンサ部371を用いて外光強度を取得し

、外光強度に応じてコントローラ311により第1のフォトセンサ335の感度を変更す

る。センサ部371を用いて外光強度を取得し、外光強度に応じてコントローラ311に

より第1のフォトセンサ335の感度を変更することで最適化を行い、最適化された第1

のフォトセンサ335を用いて撮像を行う。このようにすることで、使用環境等による外

光強度の強弱により受ける影響を最小限にしつつ、高精度な撮像データを取得することが

できる表示装置500を実現できる。

合わせることができる。

本形態では、フォトセンサに適用できる回路図の例について、図12〜図14を用いて

説明する。本形態に示すフォトセンサは、図4、図9に示す第1のフォトセンサ335に

代えて、適用することができる。

配線232をさらに有する構成としたものである。トランジスタ231は、ゲートが第8

の配線232に電気的に接続され、ソース又はドレインの一方がフォトダイオード344

の他方の電極に電気的に接続され、ソース又はドレインの他方がトランジスタ341のゲ

ートに電気的に接続される。トランジスタ231は、トランジスタ341のゲートに蓄積

された電荷を保持する機能を有している。

4をさらに有し、トランジスタ342及び第4の配線339を有さない構成としたもので

ある。保持容量233は、一方の電極がフォトダイオード344の他方の電極に電気的に

接続され、他方の電極が第9の配線234に電気的に接続される。また、トランジスタ3

41のソース又はドレインの一方が第2の配線337に電気的に接続される。

第10の配線242をさらに有する構成としたものである。トランジスタ241は、ゲー

トが第10の配線242に電気的に接続され、ソース又はドレインの一方がトランジスタ

231のソース又はドレインの他方及びトランジスタ341のゲートに電気的に接続され

、ソース又はドレインの他方が第1の配線336及びトランジスタ341のソース又はド

レインの一方に電気的に接続される。トランジスタ241は、トランジスタ341のゲー

トにリセット信号を供給する機能を有している。

ランジスタ342との接続関係が異なる構成を有している。トランジスタ341は、ゲー

トがトランジスタ231のソース又はドレインの他方及びトランジスタ241のソース又

はドレインの一方に電気的に接続され、ソース又はドレインの一方がトランジスタ342

のソース又はドレインの一方に電気的に接続され、ソース又はドレインの他方が第2の配

線337に電気的に接続される。トランジスタ342のソース又はドレインの他方は、第

1の配線336及びトランジスタ241のソース又はドレインの他方に電気的に接続され

る。

第4の配線339を有さない構成としたものである。トランジスタ341は、ソース又は

ドレインの他方が第2の配線337に電気的に接続される。

ランジスタ341との接続関係が異なる構成を有している。トランジスタ241は、ソー

ス又はドレインの他方が第11の配線244に電気的に接続される。トランジスタ341

は、ソース又はドレインの一方が第1の配線336に電気的に接続され、ソース又はドレ

インの他方が第2の配線337に電気的に接続される。

ランジスタ341との接続関係が異なる構成を有している。トランジスタ241は、ソー

ス又はドレインの他方がトランジスタ231のソース又はドレインの他方及びトランジス

タ341のゲートに電気的に接続され、ソース又はドレインの一方がトランジスタ341

のソース又はドレインの他方及び第2の配線337に電気的に接続される。

ができる。上記実施の形態1又は2で示したコントローラによって、外光強度に応じてフ

ォトセンサの駆動条件を変更することで、フォトセンサの感度を最適化した上での撮像が

可能となり、高精度な撮像データを取得することができる。

合わせることができる。

本形態では、上記実施の形態に示した表示装置の一例について、図10を用いて説明す

る。

面を有する基板1001上に、フォトダイオード1002、トランジスタ1003、保持

容量1004、及び液晶素子1005が設けられている。

の一部を示している。これらの構成は、実施の形態4で説明した画素533の構成(第1

のフォトセンサ335及び表示素子537)と同等である(図9参照)。

部のフォトセンサを構成する。また、トランジスタ1003、保持容量1004及び液晶

素子1005が表示素子を構成する。

るプロセスにおいて、トランジスタ1003とともに形成することが可能である。

02が有する半導体膜1006は、p型の導電型を付与する不純物元素を含む領域(p型

半導体層ともいう)と、真性半導体の特性を有する領域(i型半導体層ともいう)と、n

型の導電型を付与する不純物元素を含む領域(n型半導体層ともいう)とを有している。

in接合)である場合を例示しているが、フォトダイオード1002はpnダイオード(

pn接合)であってもよい。pinダイオードまたはpnダイオードは、p型の導電型を

付与する不純物元素と、n型を付与する不純物元素と、を、それぞれ半導体膜1006の

特定の領域に添加することで、形成することができる。

ドを適用することができる。この場合、p型半導体層、i型半導体層及びn型半導体層を

積層してpinダイオードとする、又はp型半導体層及びn型半導体層を順に積層してp

nダイオードとすることができる。

例えば、非晶質シリコン、微結晶シリコン、又は多結晶シリコンなどの半導体膜を用いて

形成したトランジスタを適用することができる。また、酸化物半導体を用いて形成したト

ランジスタを適用することができる。また、半導体膜上にゲート電極が配置されるトップ

ゲート型、半導体膜下にゲート電極が配置されるボトムゲート型のいずれの構造を適用し

てもよい。さらに、半導体膜上にソース電極及びドレイン電極が形成されるトップコンタ

クト型、半導体膜下にソース電極及びドレイン電極が形成されるボトムコンタクト型のい

ずれの構造を適用してもよい。

の構成においては、基板1001上に半導体膜を成膜し、該半導体膜をエッチングなどに

より所望の形状に加工(パターニング)することで、フォトダイオード1002の島状の

半導体膜と、トランジスタ1003の島状の半導体膜とを一緒に形成することができる。

そのため、通常のパネル作製プロセスに加え、別途フォトダイオード作製プロセスを追加

する必要がなく、作製コストを低減できる。

する。画素電極1007は、平坦化膜として機能する絶縁膜1032上に形成されている

。

容量1004と電気的に接続されている。また、対向電極1009は、基板(対向基板)

1013に形成されており、画素電極1007と対向電極1009との間に、液晶100

8が挟まれている。

スタについては図示していない。画素部に設けられたフォトセンサに用いられているトラ

ンジスタも、トランジスタ1003を作製するプロセスにおいて、トランジスタ1003

とともに基板1001上に形成することが可能である。

6を用いて制御することができる。図10では、フォトリソグラフィー法を利用して選択

的に形成された柱状のスペーサー1016を用いてセルギャップを制御している例を示す

。なお、図10におけるスペーサー1016の位置は一例であり、スペーサーの位置、個

数、及び密度などは、実施者が任意に決定することができる。また、柱状スペーサー10

16に代えて、画素電極1007と対向電極1009の間に球状のスペーサーを分散させ

ることで、セルギャップを制御することもできる。

れている。液晶1008は、ディスペンサ式(滴下式)又はディップ式(汲み上げ式)を

用いて形成することができる。

素を含むインジウム錫酸化物、有機インジウム、有機スズ、酸化亜鉛を含むインジウム亜

鉛酸化物(IZO;Indium Zinc Oxide)、酸化亜鉛、ガリウムを含む

酸化亜鉛、酸化スズ、酸化タングステンを含むインジウム酸化物、酸化タングステンを含

むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、又は酸化チタンを含むイ

ンジウム錫酸化物などを用いて形成することができる。

9にも上述した透光性を有する導電性材料を用いることができる。

1008の間には配向膜1012が、それぞれ設けられている。配向膜1011、配向膜

1012はポリイミド、ポリビニルアルコールなどの有機樹脂を用いて形成することがで

きる。配向膜1011、配向膜1012の表面には、ラビングなどの、液晶分子を一定方

向に配列させるための配向処理が施されている。ラビングは、配向膜に圧力をかけながら

、ナイロンなどの布を巻いたローラーを回転させて、上記配向膜の表面を一定方向に擦る

ことで、行うことができる。なお、配向処理を施すことなく、酸化珪素などの無機材料を

用いて配向特性を有する配向膜1011、配向膜1012を蒸着法により直接形成するこ

とも可能である。

ーフィルタ1014が、基板1013に形成されている。カラーフィルタ1014は、顔

料を分散させたアクリル系樹脂などの有機樹脂を基板1013上に塗布した後、所望の形

状に有機樹脂を加工して選択的に形成することができる。また、顔料を分散させたポリイ

ミド系樹脂を基板1013上に塗布した後、所望の形状にポリイミド系樹脂を加工して選

択的に形成することもできる。また、インクジェットなどの液滴吐出法を用いることで、

フォトリソグラフィー法を利用することなく、選択的にカラーフィルタ1014を形成す

ることもできる。

1002と重なる位置に形成されている。遮蔽膜1015を設けることで、基板1013

を透過して画素部内に入射したバックライトからの光が、直接フォトダイオード1002

に当たるのを防ぐことができる。さらに、画素間における液晶1008の配向の乱れに起

因するディスクリネーションが視認されるのを防ぐことができる。遮蔽膜1015には、

カーボンブラック、低次酸化チタンなどの黒色顔料を含む有機樹脂を用いることができる

。または、クロムを用いた膜で、遮蔽膜1015を形成することも可能である。

017を設ける。また、基板1013の対向電極1009が形成されている面とは反対の

面に、偏光板1018を設ける。

tical Alignment)型、OCB(optically compensa

ted Birefringence)型、又はIPS(In−Plane Switc

hing)型等を適用することができる。なお、本実施の形態では、画素電極1007と

対向電極1009の間に液晶1008が挟まれている構造の液晶素子1005を例に挙げ

て説明したが、本発明の一態様に係る表示装置はこの構成に限定されない。IPS型のよ

うに、一対の電極が、ともに基板1001側に形成されている液晶素子であってもよい。

量1004は、絶縁表面を有する基板上に薄膜の半導体膜を形成し、該半導体膜を用いて

形成する例を挙げているが、単結晶半導体基板、SOI基板などを用いて形成されていて

もよい。

出物1021が基板1001側に位置するものとする。この場合、矢印1025の方向に

照射される光は、被検出物1021によって遮られるため、フォトダイオード1002へ

の入射が遮られる。そのため、フォトダイオード1002は、被検出物の影を検出するこ

とになる。

05を通って基板1001側にある被検出物1021に照射され、被検出物1021によ

って反射された光がフォトダイオード1002に入射する。フォトダイオード1002は

、被検出物1021の反射光を検出することになる。

13側に位置する構成とする。この場合、遮蔽膜1015に開口を設けるなどして、フォ

トダイオード1002に基板1013側から光が入射するようにする。また、基板100

1側のフォトダイオード1002と重なる位置に遮蔽膜を設けるなどして、基板1001

側からフォトダイオード1002に光が入射されないようにする。被検出物がある場合、

基板1013側から照射される光は、被検出物によって遮られるため、フォトダイオード

1002への入射が遮られる。そのため、フォトダイオード1002は、被検出物の影を

検出することになる。

側にある場合、バックライトからの光は基板1001側から照射される。光は、液晶素子

1005を通って基板1013側にある被検出物に照射され、被検出物によって反射され

た光がフォトダイオード1002に入射する。フォトダイオード1002は、被検出物の

反射光を検出することになる。

では、絶縁表面を有する基板1001上に、フォトダイオード1052、トランジスタ1

053a、トランジスタ1053b、トランジスタ1053c、保持容量1054、及び

液晶素子1005が設けられている。

示素子の一部を示している。これらの構成は、実施の形態4で説明した画素533の構成

(第1のフォトセンサ335及び表示素子537)と同等である(図9参照)。

053bが画素部のフォトセンサを構成する。また、トランジスタ1053c、保持容量

1054及び液晶素子1005が表示素子を構成する。

ランジスタ1053cを有する例を示している。なお、上記実施の形態と同様、トランジ

スタの構造、構成材料などは、適宜選択することができ、図示した構造に限定されない。

いて形成したトランジスタを適用することが好ましい。酸化物半導体を用いたトランジス

タは、極めてオフ電流の低い特性を有するため、電荷保持機能を高めることができる。

フォトダイオード1052のカソードと電気的に接続されている。配線1030は、図9

に示すゲート信号線343に相当する。なお、配線1030は、絶縁膜1031上ではな

く、絶縁膜1033上に形成されていてもよい。

3bのソース電極又はドレイン電極の一方と電気的に接続されている。トランジスタ10

53aのソース電極又はドレイン電極の他方は配線(図9に示す第1の配線336に相当

)と電気的に接続されている。また、トランジスタ1053bのソース電極又はドレイン

電極の他方は配線(図9に示す第2の配線337に相当)と電気的に接続されている。

している。具体的には、フォトダイオード1052は、p型半導体層1041、i型半導

体層1042及びn型半導体層1043が順に積層されている。フォトダイオード105

2は、pin接合を積層型で形成している。

を用いたフォトダイオードが挙げられる。この場合、p型半導体層1041、及びn型半

導体層1043にも非晶質シリコンを用いることはできるが、電気伝導度が高い微結晶シ

リコンを用いることが好ましい。i型半導体層1042に非晶質シリコンを用いたフォト

ダイオードは、光感度が可視光線領域にあり、赤外線による誤動作を防ぐことができる。

が、フォトダイオード1052はpnダイオードであってもよい。フォトダイオード10

52がpnダイオードの場合は、p型半導体層及びn型半導体層として高品質の結晶シリ

コンを用いることが好ましい。また、本形態ではフォトダイオード1052が縦方向のダ

イオードである場合を例示しているが、図10のように横方向のダイオードを適用しても

よい。

5と電気的に接続される。フォトダイオード1052のカソードとなるn型半導体層10

43は、トランジスタ1053aのゲート電極と電気的に接続されている。なお、信号配

線1035は、図9に示す第3の配線338に相当する。

有する導電層が設けられていてもよい。また、n型半導体層1043の絶縁膜1033の

界面側には導電層が設けられていてもよい。例えば、配線1030が延在し、n型半導体

層1043を覆う様な形であってもよい。p型半導体層1041の光入射面側やn型半導

体層1043の絶縁膜1033の界面側に導電層を設けることで、p型半導体層1041

の抵抗又はn型半導体層1043の抵抗による電荷の損失を低減することができる。

タ1053cのソース電極またはドレイン電極の一方は画素電極1007と電気的に接続

され、ソース電極またはドレイン電極の他方は信号配線(図示せず)に接続されている。

ることが可能である。保持容量1054を構成する容量配線及び容量電極は、トランジス

タ1053a、1053b、1053cのゲート電極、又はソース電極及びドレイン電極

を作製する工程において形成される。誘電体膜となる絶縁膜は、ゲート絶縁膜を作製する

工程において形成される。保持容量1054は、液晶素子1005と並列にトランジスタ

1053cのソース電極またはドレイン電極の一方と接続されている。

が、平坦化膜として機能する絶縁膜1032上に形成されている。なお、画素電極100

7から上方の基板(対向基板)1013までの構成は、図10の説明に準じるため省略す

る。

表示装置を適用する。なお、図10、図11は上記実施の形態4に示した半導体装置の断

面に相当し、さらに画素部の周辺にセンサ部(フォトセンサ)と、コントローラと、を有

する。図10、図11に示す表示装置は、画素部の周辺に設けられたフォトセンサで外光

強度を取得し、コントローラが外光強度に応じて画素部に設けられたフォトセンサの駆動

条件を変更し、コントローラから与えられる駆動条件により画素部に設けられたフォトセ

ンサの感度を変更した上で撮像を行う。表示装置は、外光強度に応じて画素部に設けられ

たフォトセンサの駆動条件を変更することで最適化し、最適化したフォトセンサを用いて

撮像を行う。したがって、高精度な撮像データを取得することができる。

構成を適用することができる。

入力と表示の2つの機能を合わせ持つことができ、高機能な表示装置を提供することがで

きる。特に、高精度な撮像データを取得できるため、入力機能を高精度化することができ

る。

合わせることができる。

本形態では、上記実施の形態に示した画素に設けられたフォトセンサと、画素の周辺に

設けられたフォトセンサと、を有する半導体装置の応用例について説明する。

ついて説明する。図15は、表示装置の構造を示す斜視図の一例である。図15に示す表

示装置は、パネル1601と、第1の拡散板1602と、プリズムシート1603と、第

2の拡散板1604と、導光板1605と、反射板1606と、バックライト1608と

、回路基板1609とを有している。パネル1601は、一対の基板間に液晶素子、フォ

トダイオード、及び薄膜トランジスタなどを含む画素部が形成された構成を有する。バッ

クライト1608は、複数の光源1607を有する。

板1604と、導光板1605と、反射板1606とは、順に積層されている。光源16

07は導光板1605の端部に設けられている。導光板1605内部に拡散された光源1

607からの光は、第1の拡散板1602、プリズムシート1603及び第2の拡散板1

604によって、対向基板側から均一にパネル1601に照射される。

いているが、拡散板の数はこれに限定されず、単数であっても3以上であってもよい。ま

た、拡散板は、導光板1605とパネル1601との間に設けられていればよい。よって

、図15に示す構成の場合、プリズムシート1603よりもパネル1601に近い側にの

み拡散板が設けられていてもよいし、プリズムシート1603よりも導光板1605に近

い側にのみ拡散板が設けられていてもよい。

導光板1605からの光をパネル1601側に集光できる形状を有していればよい。

回路、パネル1601から出力される各種信号を処理する回路などが設けられている。そ

して図15では、回路基板1609とパネル1601とが、FPC1611(Flexi

ble Printed Circuit;フレキシブルプリントサーキット)を介して

接続されている。なお、上記回路基板1609に設けられた回路は、COG(Chip

On Glass)法を用いてパネル1601に接続されていてもよいし、上記回路の一

部がFPC1611にCOF(Chip On Film)法を用いて接続されていても

よい。

設けられ、制御系の回路と光源1607とがFPC1610を介して接続されている例を

示している。ただし、制御系の回路はパネル1601に設けられていてもよい。この場合

は、パネル1601と光源1607とをFPCなどにより接続させる。

例示しているが、これに限らず、パネル1601の直下に光源1607を配置する直下型

としてもよい。

イト1608からの光は、パネル1601を通過し、その一部が指1612において反射

し、再びパネル1601に入射する。各色に対応する光源1607を順に点灯させ、色ご

とに撮像を行うことで、被検出物である指1612のカラーの撮像データを得ることがで

きる。また撮像データから位置を認識することができ、表示画像の情報と組み合わせてタ

ッチパネルとして機能させることができる。

環境を問わず、高精度な撮像を行うことができる。また、さまざまな明るさの場所でも、

臨機応変に画素部のフォトセンサの感度を変更した上で撮像を行うため、利便性を高める

ことができる。

ライティングボード(黒板、ホワイトボードとも言われる)の一例を、図16に示す。例

えば、ライティングボード9600のパネル部9696に、上記実施の形態に示した半導

体装置を組み込むことができる。

。パネル部9696表面には、ガラス基板や透明な合成樹脂シートを用いることができる

。

撮像を行うことができる。そのため、ライティングボード9600をプリンター等と接続

しておくことで、パネル部9696に書き込まれた文字や図などを読み取って印刷するこ

とが可能である。もちろん、ライティングボード9600本体にプリンターを備えさせた

構成としてもよい。

み込めば、画像を表示するとともに、パネル部9696表面にマーカー等で書き込みを行

うことができる。さらに、パネル部9696に、画像を表示させた状態で文字や図を書き

込むことにより、撮像を行って読み取ったマーカーの軌跡と画像とを合成して映し出すこ

とも可能となる。パネル部9696の表示画像や書き込んだ文字などは、プリンター等に

より印刷することが可能である。

けられたフォトセンサの感度を最適化した上で撮像を行うことができるため、高精度な撮

像ができ、所望の印刷物を得ることができる。なお、室内が明るすぎる場合、又は室内で

なく屋外の場合でも、画素部に設けられたフォトセンサの感度を最適化した上での撮像が

できるため、高精度な撮像ができ、所望の印刷物を得ることができる。

説明する。

備えた画像再生装置(代表的にはDVD:Digital Versatile Dis

c等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置)が挙げられ

る。その他、携帯電話、携帯型ゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジ

タルスチルカメラなどのカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ

)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレ

イヤー等)、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ

払い機(ATM)、自動販売機などが挙げられる。これら電子機器の具体例を図17に示

す。

5003等を有する。表示部5002に、上記実施の形態に示した表示装置を組み込むこ

とができる。これにより、使用環境による外光強度に関係なく、最適化されたフォトセン

サの感度で撮像を行うことができ、高精度な撮像を行うことができる。したがって、高精

度な撮像機能という高機能なアプリケーションを搭載したディスプレイ5000を提供す

ることができる。なお、表示装置には、パーソナルコンピュータ用、TV放送受信用、広

告表示用などの全ての情報表示用のディスプレイが含まれる。

チ5103、操作キー5104、赤外線ポート5105等を有する。表示部5102に、

上記実施の形態に示した表示装置を組み込むことができる。これにより、使用環境による

外光強度に関係なく、最適化されたフォトセンサの感度で撮像を行うことができ、高精度

な撮像を行うことができる。したがって、高精度な撮像機能という高機能なアプリケーシ

ョンを搭載した携帯情報端末5100を提供することができる。特に、携帯情報端末51

00の場合は、さまざまな場所に持ち運ぶことが想定されているため、使用環境による外

光強度の影響によらず、高精度な撮像が可能であることは効果的である。

2、硬貨投入口5203、紙幣投入口5204、カード投入口5205、通帳投入口52

06等を有する。表示部5202に、上記実施の形態に示した表示装置を組み込むことが

できる。これにより、使用環境による外光強度に関係なく、最適化されたフォトセンサの

感度で撮像を行うことができ、高精度な撮像を行うことができる。さらに、現金自動預け

入れ払い機5200に適用するため、高精度な撮像を行えることで、指紋、顔、手形、掌

紋及び手の静脈の形状、虹彩等の、生体認証に用いられる生体情報の読み取り精度を高め

ることができる。したがって、生体認証における、本人であるにもかかわらず本人ではな

いと誤認識してしまう本人拒否率と、他人であるにもかかわらず本人と誤認識してしまう

他人受入率とを、低く抑えることができる。

5303、表示部5304、マイクロホン5305、スピーカー5306、操作キー53

07、スタイラス5308等を有する。表示部5304に、上記実施の形態に示した表示

装置を組み込むことができる。これにより、使用環境による外光強度に関係なく、最適化

されたフォトセンサの感度で撮像を行うことができ、高精度な撮像を行うことができる。

したがって、高精度な撮像機能という高機能なアプリケーションを搭載した携帯型ゲーム

機5300を提供することができる。携帯型ゲーム機5300も、携帯情報端末5100

と同様にさまざまな場所に持ち運ぶことが想定されているため、使用環境による外光強度

の影響によらず、高精度な撮像が可能であることは効果的である。なお、図17(D)に

示した携帯型ゲーム機は、2つの表示部5303と表示部5304とを有しているが、携

帯型ゲーム機が有する表示部の数は、これに限定されない。

232 第8の配線

233 保持容量

234 第9の配線

241 トランジスタ

242 第10の配線

244 第11の配線

300 固体撮像素子

301 画素部

311 コントローラ

331 第1の制御回路部

333 画素

335 第1のフォトセンサ

336 第1の配線

337 第2の配線

338 第3の配線

339 第4の配線

341 トランジスタ

342 トランジスタ

343 ゲート信号線

344 フォトダイオード

351 フォトセンサ読み出し回路

352 p型トランジスタ

353 保持容量

354 第5の配線

355 フォトセンサ駆動回路

356 第6の配線

371 センサ部

401 信号

402 信号

403 信号

404 信号

405 信号

500 表示装置

501 画素部

533 画素

537 表示素子

541 トランジスタ

542 保持容量

543 液晶素子

551 表示素子駆動回路

555 表示素子駆動回路

561 ゲート信号線

562 第7の配線

1000 第1のフォトセンサ

1001 基板

1002 フォトダイオード

1003 トランジスタ

1004 保持容量

1005 液晶素子

1006 半導体膜

1007 画素電極

1008 液晶

1009 対向電極

1010 導電膜

1011 配向膜

1012 配向膜

1013 基板

1014 カラーフィルタ

1015 遮蔽膜

1016 スペーサー

1017 偏光板

1018 偏光板

1021 被検出物

1025 矢印

1030 配線

1031 絶縁膜

1032 絶縁膜

1033 絶縁膜

1035 信号配線

1041 p型半導体層

1042 i型半導体層

1043 n型半導体層

1052 フォトダイオード

1053a トランジスタ

1053b トランジスタ

1053c トランジスタ

1054 保持容量

1100 コントローラ

1110 CPU

1120 プログラムメモリ

1130 外光強度データ用レジスタ

1140 変換テーブル

1150 作業用メモリ

1160 タイミングコントローラ

1162 制御データ用レジスタ

1170 電源回路

1172 制御データ用レジスタ

1174 D/A変換回路

1176 増幅回路

1200 第2のフォトセンサ

1301 実線

1302 ピーク

1303 ピーク

1311 破線

1312 ピーク

1321 破線

1322 ピーク

1601 パネル

1602 第1の拡散板

1603 プリズムシート

1604 第2の拡散板

1605 導光板

1606 反射板

1607 光源

1608 バックライト

1609 回路基板

1610 FPC

1611 FPC

1612 指

2100 コントローラ

2110 専用処理回路

2112 変換テーブル

5000 ディスプレイ

5001 筐体

5002 表示部

5003 支持台

5100 携帯情報端末

5101 筐体

5102 表示部

5103 スイッチ

5104 操作キー

5105 赤外線ポート

5200 現金自動預け入れ払い機

5201 筐体

5202 表示部

5203 硬貨投入口

5204 紙幣投入口

5205 カード投入口

5206 通帳投入口

5300 携帯型ゲーム機

5301 筐体

5302 筐体

5303 表示部

5304 表示部

5305 マイクロホン

5306 スピーカー

5307 操作キー

5308 スタイラス

9600 ライティングボード

9696 パネル部

Claims (3)

- 第1のフォトセンサと、

第2のフォトセンサと、

コントローラと、を有し、

前記第1のフォトセンサは、画素内に配置され、

前記第2のフォトセンサは、画素外に配置され、

前記コントローラは、

第1のメモリに格納された、プログラムの命令に従って、

第1のレジスタに格納された、前記第2のフォトセンサが取得した外光強度を示すデータと、

第2のメモリに格納された、前記第2のフォトセンサが取得した外光強度に基づいて、前記第1のフォトセンサが有するフォトダイオードの駆動条件を規定するデータと、を用いて、

第2のレジスタに格納するデータ及び第3のレジスタに格納するデータを生成する機能を有し、

前記コントローラを用い、輝度値に対する画素数のヒストグラムにおける、検出位置を示す第1のピークと、検出位置以外を示す第2のピークとが分離するように、前記第2のフォトセンサが取得した外光強度に基づいて、前記第1のフォトセンサが有するフォトダイオードに印加される電圧を変更して、前記第1のフォトセンサの感度を変更させることを特徴とする半導体装置。 - 第1のフォトセンサと、

第2のフォトセンサと、

コントローラと、を有し、

前記第1のフォトセンサは、画素内に配置され、

前記第2のフォトセンサは、画素外に配置され、

前記コントローラはプログラムメモリに格納された、プログラムの命令に従って、

外光強度データ用レジスタに格納された、前記第2のフォトセンサが取得した外光強度を示すデータと、

変換テーブルに格納された、前記第2のフォトセンサが取得した外光強度に基づいて、前記第1のフォトセンサが有するフォトダイオードの駆動条件を規定するデータと、を用いて、

第1の制御データ用レジスタに格納するデータ及び第2の制御データ用レジスタに格納するデータを生成する機能を有し、

前記コントローラを用い、輝度値に対する画素数のヒストグラムにおける、検出位置を示す第1のピークと、検出位置以外を示す第2のピークとが分離するように、前記第2のフォトセンサが取得した外光強度に基づいて、前記第1のフォトセンサが有するフォトダイオードに印加される電圧を変更して、前記第1のフォトセンサの感度を変更させることを特徴とする半導体装置。 - 請求項2において

前記外光強度データ用レジスタに格納されたデータを独立変数Xとし、

前記第1の制御データ用レジスタ及び前記第2の制御データ用レジスタに格納するデータを従属変数Yとし、

Y(X)=A・X+Bで表せるとき、

パラメータデータ(A、B)を前記変換テーブルに格納することを特徴とする半導体装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010054006 | 2010-03-11 | ||

| JP2010054006 | 2010-03-11 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015026341A Division JP5970095B2 (ja) | 2010-03-11 | 2015-02-13 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016208527A JP2016208527A (ja) | 2016-12-08 |

| JP6204539B2 true JP6204539B2 (ja) | 2017-09-27 |

Family

ID=44559632

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011049287A Expired - Fee Related JP5890608B2 (ja) | 2010-03-11 | 2011-03-07 | 半導体装置 |

| JP2015026341A Expired - Fee Related JP5970095B2 (ja) | 2010-03-11 | 2015-02-13 | 半導体装置 |

| JP2016135864A Active JP6204539B2 (ja) | 2010-03-11 | 2016-07-08 | 半導体装置 |

Family Applications Before (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011049287A Expired - Fee Related JP5890608B2 (ja) | 2010-03-11 | 2011-03-07 | 半導体装置 |

| JP2015026341A Expired - Fee Related JP5970095B2 (ja) | 2010-03-11 | 2015-02-13 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US8502902B2 (ja) |

| JP (3) | JP5890608B2 (ja) |

| KR (2) | KR101754382B1 (ja) |

| TW (1) | TWI513302B (ja) |

| WO (1) | WO2011111530A1 (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5848586B2 (ja) | 2010-11-12 | 2016-01-27 | 株式会社半導体エネルギー研究所 | 入出力装置 |

| JP5774974B2 (ja) | 2010-12-22 | 2015-09-09 | 株式会社半導体エネルギー研究所 | 半導体装置の駆動方法 |

| KR102021908B1 (ko) * | 2011-05-03 | 2019-09-18 | 삼성전자주식회사 | 광터치 스크린 장치 및 그 구동 방법 |

| KR101854187B1 (ko) * | 2011-07-28 | 2018-05-08 | 삼성전자주식회사 | 광센싱 장치 및 그 구동 방법, 광센싱 장치를 포함하는 광터치 스크린 장치 |

| JP5270790B1 (ja) * | 2012-05-30 | 2013-08-21 | 富士フイルム株式会社 | 放射線画像撮影装置、放射線画像撮影システム、放射線画像撮影装置の制御プログラム、及び放射線画像撮影装置の制御方法 |

| CN103855182A (zh) * | 2012-11-28 | 2014-06-11 | 瀚宇彩晶股份有限公司 | 有机发光二极管触控显示面板及其电磁式触控显示装置 |

| US10222911B2 (en) * | 2013-04-12 | 2019-03-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and driving method of the same |

| US9817520B2 (en) | 2013-05-20 | 2017-11-14 | Semiconductor Energy Laboratory Co., Ltd. | Imaging panel and imaging device |

| KR102085274B1 (ko) * | 2013-06-21 | 2020-03-06 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| CN104867964B (zh) * | 2015-05-18 | 2019-02-22 | 京东方科技集团股份有限公司 | 阵列基板、其制造方法以及有机发光二极管显示装置 |

| KR102453950B1 (ko) * | 2015-09-30 | 2022-10-17 | 엘지디스플레이 주식회사 | 표시장치와 그 구동 방법 |

| US20170170218A1 (en) * | 2015-12-09 | 2017-06-15 | Dpix, Llc | Top gate metal oxide thin film transistor switching device for imaging applications |

| CN106529463B (zh) * | 2016-10-28 | 2019-04-23 | 京东方科技集团股份有限公司 | 一种指纹识别显示面板、显示装置和指纹识别方法 |

| JP6892577B2 (ja) * | 2017-04-28 | 2021-06-23 | 天馬微電子有限公司 | イメージセンサ及びセンサ装置 |

| KR102430318B1 (ko) * | 2017-06-21 | 2022-08-10 | 삼성디스플레이 주식회사 | 표시 장치 및 그의 동작 방법 |

| US10777122B2 (en) * | 2017-12-27 | 2020-09-15 | Lg Display Co., Ltd. | Electroluminescence display device and driving method thereof |

| CN108304803B (zh) * | 2018-01-31 | 2021-04-23 | 京东方科技集团股份有限公司 | 光检测电路、光检测方法和显示装置 |

| KR102532091B1 (ko) * | 2018-11-16 | 2023-05-15 | 엘지디스플레이 주식회사 | 표시 장치 |

| TWI700621B (zh) | 2019-04-15 | 2020-08-01 | 友達光電股份有限公司 | 觸控面板 |

| US20220246893A1 (en) * | 2019-07-17 | 2022-08-04 | Semiconductor Energy Laboratory Co., Ltd. | Display Device |

Family Cites Families (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS634777A (ja) | 1986-06-24 | 1988-01-09 | Nippon Denso Co Ltd | 固体撮像装置 |

| JPH0612512B2 (ja) | 1989-03-16 | 1994-02-16 | ミナトエレクトロニクス株式会社 | 光学式タッチパネルの受光素子の感度調整方法 |

| JP2000150842A (ja) | 1998-11-05 | 2000-05-30 | Sharp Corp | 受光素子及びその製造方法 |

| JP4112184B2 (ja) | 2000-01-31 | 2008-07-02 | 株式会社半導体エネルギー研究所 | エリアセンサ及び表示装置 |

| US6747638B2 (en) | 2000-01-31 | 2004-06-08 | Semiconductor Energy Laboratory Co., Ltd. | Adhesion type area sensor and display device having adhesion type area sensor |

| JP2003296022A (ja) | 2002-04-01 | 2003-10-17 | Pioneer Electronic Corp | タッチパネル一体型表示装置 |

| JP4767013B2 (ja) | 2003-03-26 | 2011-09-07 | 株式会社半導体エネルギー研究所 | 光センサ |

| JP4257221B2 (ja) | 2003-03-31 | 2009-04-22 | 東芝松下ディスプレイテクノロジー株式会社 | 表示装置および情報端末装置 |

| JP4789515B2 (ja) | 2004-06-10 | 2011-10-12 | 三星電子株式会社 | 表示装置及びその駆動方法 |

| JP2006079589A (ja) | 2004-08-05 | 2006-03-23 | Sanyo Electric Co Ltd | タッチパネル |

| JP2006091462A (ja) * | 2004-09-24 | 2006-04-06 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| US7800594B2 (en) | 2005-02-03 | 2010-09-21 | Toshiba Matsushita Display Technology Co., Ltd. | Display device including function to input information from screen by light |

| JP2006243927A (ja) * | 2005-03-01 | 2006-09-14 | Toshiba Matsushita Display Technology Co Ltd | 表示装置 |

| US7492028B2 (en) | 2005-02-18 | 2009-02-17 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and manufacturing method of the same, and a semiconductor device |

| JP4338140B2 (ja) | 2005-05-12 | 2009-10-07 | 株式会社 日立ディスプレイズ | タッチパネル一体表示装置 |

| JP2007129564A (ja) | 2005-11-04 | 2007-05-24 | Olympus Imaging Corp | デジタルカメラ |

| US20070109239A1 (en) * | 2005-11-14 | 2007-05-17 | Den Boer Willem | Integrated light sensitive liquid crystal display |

| JP2008102418A (ja) | 2006-10-20 | 2008-05-01 | Toshiba Matsushita Display Technology Co Ltd | 表示装置 |

| US20070182723A1 (en) | 2006-01-31 | 2007-08-09 | Toshiba Matsushita Display Technology Co., Ltd. | Display device |

| JP2008053583A (ja) * | 2006-08-28 | 2008-03-06 | Nec Corp | 半導体受光素子及び半導体光集積素子 |

| JP5016896B2 (ja) * | 2006-11-06 | 2012-09-05 | 株式会社ジャパンディスプレイセントラル | 表示装置 |

| US7924273B2 (en) | 2006-11-06 | 2011-04-12 | Toshiba Matsushita Display Technology Co., Ltd. | Display apparatus with optical input function |

| JP2008181109A (ja) * | 2006-12-27 | 2008-08-07 | Semiconductor Energy Lab Co Ltd | 液晶表示装置及びそれを用いた電子機器 |

| JP4826512B2 (ja) | 2007-03-12 | 2011-11-30 | セイコーエプソン株式会社 | 表示装置及び電子機器 |

| WO2008123119A1 (en) | 2007-03-26 | 2008-10-16 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and electronic device provided with the photoelectric conversion device |

| CN101627350A (zh) | 2007-03-26 | 2010-01-13 | 夏普株式会社 | 定位设备和使用它的显示装置 |

| US20100134457A1 (en) | 2007-04-09 | 2010-06-03 | Hiromi Katoh | Display device |

| DE102007021036A1 (de) * | 2007-05-04 | 2008-11-06 | Carl Zeiss Ag | Anzeigevorrichtung und Anzeigeverfahren zur binokularen Darstellung eines mehrfarbigen Bildes |

| JP5125222B2 (ja) * | 2007-05-18 | 2013-01-23 | セイコーエプソン株式会社 | 液晶装置及び電子機器 |

| US20090051676A1 (en) | 2007-08-21 | 2009-02-26 | Gyu Hyeong Cho | Driving apparatus for display |

| JP5567770B2 (ja) | 2007-09-21 | 2014-08-06 | 株式会社ジャパンディスプレイ | 表示装置及び表示装置の製造方法 |

| JP5660755B2 (ja) * | 2007-11-02 | 2015-01-28 | 株式会社ジャパンディスプレイ | 表示装置および表示制御方法ならびに電子機器 |

| JP4978453B2 (ja) | 2007-12-14 | 2012-07-18 | セイコーエプソン株式会社 | センシング装置、表示装置および電子機器 |

| JP5014439B2 (ja) | 2007-12-20 | 2012-08-29 | シャープ株式会社 | 光センサ付き表示装置 |

| TWI360644B (en) * | 2008-02-19 | 2012-03-21 | Wintek Corp | Photo sensor for a display device |

| CN101911159A (zh) | 2008-03-03 | 2010-12-08 | 夏普株式会社 | 带光传感器的显示装置 |

| JP5311299B2 (ja) | 2008-06-03 | 2013-10-09 | 株式会社ジャパンディスプレイ | 液晶表示装置 |

| US8736587B2 (en) * | 2008-07-10 | 2014-05-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP5501583B2 (ja) * | 2008-08-08 | 2014-05-21 | 株式会社半導体エネルギー研究所 | 光電変換装置、及び当該光電変換装置を具備する電子機器 |

| JP4796104B2 (ja) * | 2008-08-29 | 2011-10-19 | シャープ株式会社 | 撮像装置、画像解析装置、外光強度算出方法、画像解析方法、撮像プログラム、画像解析プログラムおよび記録媒体 |

| KR20100038046A (ko) | 2008-10-02 | 2010-04-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 터치 패널 및 터치 패널의 구동방법 |

| US8154532B2 (en) * | 2008-10-15 | 2012-04-10 | Au Optronics Corporation | LCD display with photo sensor touch function |

| KR100975871B1 (ko) * | 2008-10-17 | 2010-08-13 | 삼성모바일디스플레이주식회사 | 광 센싱 회로, 이를 포함하는 터치 패널, 및 광 센싱 회로의 구동 방법 |

| CN102265594B (zh) * | 2008-12-22 | 2014-07-02 | 罗姆股份有限公司 | 图像修正处理电路、半导体装置、图像修正处理装置 |

| JP5313853B2 (ja) | 2008-12-24 | 2013-10-09 | 株式会社半導体エネルギー研究所 | センサを有する装置、及び表示装置 |

| CN102265244B (zh) | 2008-12-24 | 2015-08-26 | 株式会社半导体能源研究所 | 触摸面板及其驱动方法 |

| JP4699536B2 (ja) | 2009-03-06 | 2011-06-15 | シャープ株式会社 | 位置検出装置、制御方法、制御プログラムおよび記録媒体 |

| JP5740132B2 (ja) | 2009-10-26 | 2015-06-24 | 株式会社半導体エネルギー研究所 | 表示装置及び半導体装置 |

| TWI507934B (zh) | 2009-11-20 | 2015-11-11 | Semiconductor Energy Lab | 顯示裝置 |

| JP5866089B2 (ja) | 2009-11-20 | 2016-02-17 | 株式会社半導体エネルギー研究所 | 電子機器 |

| WO2011102501A1 (en) | 2010-02-19 | 2011-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Display device and method for driving display device |

-

2011

- 2011-02-17 KR KR1020177003173A patent/KR101754382B1/ko active IP Right Grant

- 2011-02-17 KR KR1020127026016A patent/KR101706291B1/ko active IP Right Grant

- 2011-02-17 WO PCT/JP2011/054058 patent/WO2011111530A1/en active Application Filing

- 2011-03-03 US US13/039,672 patent/US8502902B2/en active Active

- 2011-03-07 TW TW100107560A patent/TWI513302B/zh active

- 2011-03-07 JP JP2011049287A patent/JP5890608B2/ja not_active Expired - Fee Related

-

2013

- 2013-08-02 US US13/957,559 patent/US10031622B2/en active Active

-

2015

- 2015-02-13 JP JP2015026341A patent/JP5970095B2/ja not_active Expired - Fee Related

-

2016

- 2016-07-08 JP JP2016135864A patent/JP6204539B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US10031622B2 (en) | 2018-07-24 |

| WO2011111530A1 (en) | 2011-09-15 |

| KR20130028076A (ko) | 2013-03-18 |

| JP2015149071A (ja) | 2015-08-20 |

| KR20170016036A (ko) | 2017-02-10 |

| KR101706291B1 (ko) | 2017-02-14 |

| JP5970095B2 (ja) | 2016-08-17 |

| TW201206186A (en) | 2012-02-01 |

| US20110221945A1 (en) | 2011-09-15 |

| JP2016208527A (ja) | 2016-12-08 |

| US20130313412A1 (en) | 2013-11-28 |

| US8502902B2 (en) | 2013-08-06 |

| JP5890608B2 (ja) | 2016-03-22 |

| TWI513302B (zh) | 2015-12-11 |

| KR101754382B1 (ko) | 2017-07-05 |

| JP2011210248A (ja) | 2011-10-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6204539B2 (ja) | 半導体装置 | |

| JP5771262B2 (ja) | 表示装置 | |

| JP6117836B2 (ja) | 表示装置 | |

| JP5947363B2 (ja) | フォトセンサ | |

| JP5823709B2 (ja) | 表示装置の駆動方法 | |

| JP5745718B2 (ja) | 表示装置及び電子機器 | |

| JP5828928B2 (ja) | タッチパネル | |

| JP5679530B2 (ja) | 電子機器 | |

| JP5913517B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170417 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170509 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170609 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170808 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170831 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6204539 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |