JP6123414B2 - 半導体素子の製造方法、半導体素子の製造装置 - Google Patents

半導体素子の製造方法、半導体素子の製造装置 Download PDFInfo

- Publication number

- JP6123414B2 JP6123414B2 JP2013067014A JP2013067014A JP6123414B2 JP 6123414 B2 JP6123414 B2 JP 6123414B2 JP 2013067014 A JP2013067014 A JP 2013067014A JP 2013067014 A JP2013067014 A JP 2013067014A JP 6123414 B2 JP6123414 B2 JP 6123414B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- semiconductor

- amorphous

- chamber

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 148

- 238000004519 manufacturing process Methods 0.000 title claims description 104

- 238000005530 etching Methods 0.000 claims description 45

- 238000010438 heat treatment Methods 0.000 claims description 27

- 239000013078 crystal Substances 0.000 claims description 26

- 239000000758 substrate Substances 0.000 claims description 26

- 238000001312 dry etching Methods 0.000 claims description 25

- 230000015572 biosynthetic process Effects 0.000 claims description 23

- 230000000903 blocking effect Effects 0.000 claims description 11

- 230000007246 mechanism Effects 0.000 claims description 7

- NJPPVKZQTLUDBO-UHFFFAOYSA-N novaluron Chemical compound C1=C(Cl)C(OC(F)(F)C(OC(F)(F)F)F)=CC=C1NC(=O)NC(=O)C1=C(F)C=CC=C1F NJPPVKZQTLUDBO-UHFFFAOYSA-N 0.000 claims description 7

- 238000004891 communication Methods 0.000 claims description 3

- 229920002101 Chitin Polymers 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 117

- 239000010408 film Substances 0.000 description 103

- 238000000034 method Methods 0.000 description 53

- 230000008569 process Effects 0.000 description 46

- 238000012545 processing Methods 0.000 description 29

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 23

- 239000007789 gas Substances 0.000 description 19

- 230000003287 optical effect Effects 0.000 description 14

- 229910004298 SiO 2 Inorganic materials 0.000 description 13

- 229910000673 Indium arsenide Inorganic materials 0.000 description 10

- RPQDHPTXJYYUPQ-UHFFFAOYSA-N indium arsenide Chemical compound [In]#[As] RPQDHPTXJYYUPQ-UHFFFAOYSA-N 0.000 description 10

- 230000000694 effects Effects 0.000 description 9

- 239000003963 antioxidant agent Substances 0.000 description 6

- 230000003078 antioxidant effect Effects 0.000 description 6

- 238000005253 cladding Methods 0.000 description 6

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical group O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- 230000008570 general process Effects 0.000 description 5

- 239000003507 refrigerant Substances 0.000 description 5

- 238000003475 lamination Methods 0.000 description 4

- 239000002826 coolant Substances 0.000 description 3

- 238000011065 in-situ storage Methods 0.000 description 3

- 230000031700 light absorption Effects 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 238000012546 transfer Methods 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- 230000002411 adverse Effects 0.000 description 2

- 230000003064 anti-oxidating effect Effects 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 238000011109 contamination Methods 0.000 description 2

- 239000012792 core layer Substances 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 238000010301 surface-oxidation reaction Methods 0.000 description 2

- 229910000980 Aluminium gallium arsenide Inorganic materials 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- 229910005542 GaSb Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000008033 biological extinction Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000001276 controlling effect Effects 0.000 description 1

- 239000013039 cover film Substances 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 230000017525 heat dissipation Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000002401 inhibitory effect Effects 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 238000001953 recrystallisation Methods 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 230000007723 transport mechanism Effects 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Landscapes

- Light Receiving Elements (AREA)

- Optical Modulation, Optical Deflection, Nonlinear Optics, Optical Demodulation, Optical Logic Elements (AREA)

- Semiconductor Lasers (AREA)

Description

非晶質As膜を形成するためのAs供給部をチャンバ内に備えたドライエッチング装置を用いて、前記チャンバ内においてAlを含む半導体層が積層された半導体基板にエッチングを施して前記半導体層の少なくとも一部を露出させたメサ構造を形成し、前記メサ構造の形成の次に前記メサ構造の表面に非晶質As膜を形成するメサ構造形成工程と、

前記メサ構造形成工程の後に前記半導体基板を前記チャンバから搬出し、半導体結晶成長装置が備える他のチャンバに搬入する搬送工程と、

前記他のチャンバ内で、前記非晶質As膜を除去した後に前記メサ構造の両側を埋込層で埋め込む埋込工程と、

を備えることを特徴とする。

台座を備えたチャンバと、

前記チャンバ内に連通し、前記台座上の半導体基板にエッチングを行うためのエッチングガス供給部と、

前記チャンバ内に連通し、前記台座上の半導体基板に非晶質As膜を形成するように前記チャンバ内にAs分子を供給するAs供給部と、

前記チャンバに対する前記エッチングガス供給部および前記As供給部の連通と遮断とを選択的に切り替える開閉機構と、

を備えることを特徴とする。

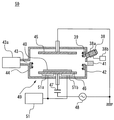

[実施の形態1にかかる装置の構成]

図1は、本発明の実施の形態1にかかる半導体素子の製造装置50の構成を示す図であり、製造装置50の内部構成を示した断面図である。製造装置50の主たる役割は、ドライエッチングを行うためのドライエッチング装置であり、製造装置50は一般的なドライエッチング装置の構成を備えている。さらに、製造装置50の特徴的な構成として、MBE装置で用いられるようなAs分子供給機構と、As分子供給によって懸念されるエッチング用途への悪影響を防ぐための機構が備えられている。

図2は、本発明の実施の形態1にかかる半導体素子の製造方法を説明するためのフローチャートである。図3乃至7は、本発明の実施の形態1にかかる半導体素子の製造方法により半導体素子が製造される過程を示す製造フロー図である。本実施の形態にかかる製造方法で製造されるのは、半導体発光素子である。

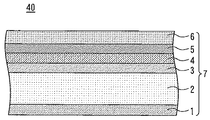

まず、図2に示すフローチャートでは、ステップS100にかかる第1積層工程が実施される。この工程では、先ず、MOCVD等の結晶成長装置(図示せず)を用いて、図3に示すように、p型InP基板1上に、半導体積層構造7を形成する。半導体積層構造7は、p型InPクラッド層2、p型Al(Ga)InAs下光閉込層3、AlGaInAs多重量子井戸活性層4、n型Al(Ga)InAs上光閉込層5、n型InPクラッド層6がこの順にp型InP基板1に積層されたものである。Alを含む半導体層は、p型Al(Ga)InAs下光閉込層3、AlGaInAs多重量子井戸活性層4、n型Al(Ga)InAs上光閉込層5である。

次に、ステップS101では、公知のフォトリソグラフィ技術、装置(図示せず)を用いて、半導体積層構造7上に選択的にシリコン酸化膜であるSiO2膜8を形成する。

次に、ステップS102は、エッチング工程によるメサ構造9の形成と、非晶質As膜10の形成工程とを、図1に示す製造装置50を用いて実施するものである。すなわち、まず、ステップS101で半導体積層構造7上にSiO2膜8を選択的に形成したもの(これが図1の半導体ウェハ40である)を、製造装置50の処理チャンバ49内に搬入する。

次に、ステップS104で搬送工程が実施される。非晶質As膜10を形成したメサ構造9を有する半導体ウェハ40を、製造装置50の処理チャンバ49から搬出する。そして、図示しない結晶成長装置(本実施の形態ではMOCVD装置とする)のチャンバ内に、半導体ウェハ40を搬入する。

次に、ステップS106の加熱工程および埋込層形成工程が実施される。具体的には、半導体ウェハ40を搬入したMOCVD装置(図示せず)内で、半導体ウェハ40を250℃以上に加熱することで、非晶質As膜を脱離させる。これは、MOCVD装置による結晶成長自体が通常は十分に高温環境でなされるものであるから、結晶成長を実施するための加熱に伴って、非晶質As膜10が脱離されることになる。

次に、図7に示すように、SiO2膜8を取り除いた後、n型InPコンタクト層15及びn型InGaAsコンタクト層16を形成する。これが第2積層工程である。その他の一般的な工程を経て本実施の形態に係る光半導体素子が製造される。これ以降の一般的な工程は各種公知技術を用いればよいため、説明を省略する。

メサ構造9を10℃以下の低温にした状態でAs分子を供給することで、メサ構造9の表面に非晶質As膜10を成膜することができる。非晶質As膜10は、メサ構造を大気に曝した際の表面酸化などの汚染を防ぐ働きをする。非晶質As膜10は、250℃以上に加熱することでメサ構造9から脱離させることができる。なお、上記のような半導体上の非晶質As膜の有用性・性質は、例えば非特許文献2に記載されている。

実施の形態1では、非晶質As膜10を酸化防止膜として用いることで、Alを含む半導体層(すなわち、p型Al(Ga)InAs下光閉込層3、AlGaInAs多重量子井戸活性層4、n型Al(Ga)InAs上光閉込層5)を被覆した。しかしながら、本発明はこれに限られるものではない。

非晶質As膜10に代えて、低温脱離が可能であって且つメサ構造9で露出したAl含有半導体層にAl酸化膜が形成されるのを防ぐことができる程度の酸化防止性能を有する酸化防止膜を用いても良い。

図8乃至11は、本発明の実施の形態2に係る光半導体素子の製造方法を説明するための製造フロー図である。実施の形態2にかかる製造方法は、実施の形態1とは異なり、半導体受光素子を製造する。

この工程は、図2のステップS100と対応する工程である。実施の形態2では、図8に示すように、n型InP基板17上に、半導体積層構造23を形成する。半導体積層構造23は、n型InPバッファ層18、n型AlGaInAs多重量子井戸アバランシェ倍増層19、p型InGaAs光吸収層20、p型InPキャップ層21、p型InGaAsコンタクト層22がこの順にn型InP基板17上に積層されたものである。n型多重量子井戸アバランシェ倍増層19が、Alを含む半導体層である。

次に、半導体積層構造23上にフォトリソグラフィなどによりパターニングしたSiO2膜24を形成する。この工程は、図2のステップS101と対応する工程である。

次に、半導体積層構造23にSiO2膜24を選択的に形成した半導体ウェハ240を、製造装置50の処理チャンバ49内に搬入する。図9に示すように、SiO2膜24をマスクとして用いて半導体積層構造23をドライエッチングしてメサ構造25を形成する。このとき、図1に示す製造装置50を用いてエッチングを行う。

次に、搬送工程が実施される。この工程は、図2のステップS104と対応する工程である。実施の形態2では、非晶質As膜26を形成したメサ構造25を有する半導体ウェハ240を、製造装置50の処理チャンバ49から搬出する。そして、図示しない結晶成長装置(本実施の形態ではMOCVD装置とする)のチャンバ内に、半導体ウェハ240を搬入する。

次に、加熱工程および埋込層形成工程が実施される。この工程は、図2のステップS106と対応する工程である。実施の形態2では、MOCVD装置内で250℃以上に加熱することで非晶質As膜26を脱離させ、図11に示すように、メサ構造25の両側を、高抵抗InP埋込層27で埋め込む。高抵抗InP埋込層27は、FeやRuなどをドープしたものである。このとき、非晶質As膜26を脱離させてから連続して埋め込みを行い、メサ構造25が大気に露出しないようにする。

高抵抗埋め込み層27の形成後は、その他の一般的な工程を経て本実施の形態に係る光半導体素子(半導体受光素子)が製造される。これ以降の一般的な工程は各種公知技術を用いればよく、新規な事項ではないため、説明を省略する。

図12乃至15は、本発明の実施の形態3に係る光半導体素子の製造方法を説明するための製造フロー図である。実施の形態3にかかる製造方法は、実施の形態1とは異なり、電界吸収型光変調器を製造する。

この工程は、図2のステップS100と対応する工程である。実施の形態3では、まず、図12に示すように、n型InP基板28上に、n型InPクラッド層29、AlGaInAs多重量子井戸コア層30、p型InPクラッド層31、p型InGaAsコンタクト層32を有する半導体積層構造33を形成する。AlGaInAs多重量子井戸コア層30が、Alを含む半導体層である。

次に、半導体積層構造33上にフォトリソグラフィなどによりパターニングしたSiO2膜34を形成する。この工程は、図2のステップS101と対応する工程である。

次に、図13に示すように、このSiO2膜34をマスクとして用いて半導体積層構造33をドライエッチングしてメサ構造35を形成する。このとき、図1に示す製造装置50を用いてエッチングを行う。

次に、搬送工程が実施される。この工程は、図2のステップS104と対応する工程である。実施の形態3では、非晶質As膜36を形成したメサ構造35を有する半導体ウェハ340を、製造装置50の処理チャンバ49から搬出する。そして、図示しない結晶成長装置(本実施の形態ではMOCVD装置とする)のチャンバ内に、半導体ウェハ340を搬入する。

次に、MOCVD装置内で250℃以上に加熱することで非晶質As膜36を脱離させ、図15に示すように、メサ構造の両側をFeやRuなどをドープした高抵抗InP埋込層37で埋め込む。このとき、非晶質As膜36を脱離させてから連続して埋め込みを行い、メサ構造35が大気に露出しないようにする。この工程は、図2のステップS106と対応する工程である。

以降、その他の一般的な工程を経て実施の形態3に係る光半導体素子(電界吸収型光変調器)が製造される。これ以降の一般的な工程は各種公知技術を用いればよく、新規な事項ではないため、説明を省略する。

Claims (7)

- 非晶質As膜を形成するためのAs供給部をチャンバ内に備えたドライエッチング装置を用いて、前記チャンバ内においてAlを含む半導体層が積層された半導体基板にエッチングを施して前記半導体層の少なくとも一部を露出させたメサ構造を形成し、前記メサ構造の形成の次に前記メサ構造の表面に非晶質As膜を形成するメサ構造形成工程と、

前記メサ構造形成工程の後に前記半導体基板を前記チャンバから搬出し、半導体結晶成長装置が備える他のチャンバに搬入する搬送工程と、

前記他のチャンバ内で、前記非晶質As膜を除去した後に前記メサ構造の両側を埋込層で埋め込む埋込工程と、

を備えることを特徴とする半導体素子の製造方法。 - 前記埋込工程が、前記他のチャンバ内で前記非晶質As膜を加熱することで前記メサ構造から前記非晶質As膜を脱離させることを特徴とする請求項1に記載の半導体素子の製造方法。

- 前記埋込工程は、前記他のチャンバで前記非晶質As膜を250℃以上の温度に加熱することで前記非晶質As膜を除去することを特徴とする請求項2に記載の半導体素子の製造方法。

- 前記メサ構造形成工程は、前記メサ構造の表面に前記非晶質As膜を10℃以下の温度で形成することを特徴とする請求項2または3に記載の半導体素子の製造方法。

- 台座を備えたチャンバと、

前記チャンバ内に連通し、前記台座上の半導体基板にエッチングを行うためのエッチングガス供給部と、

前記チャンバ内に連通し、前記台座上の半導体基板に非晶質As膜を形成するように前記チャンバ内にAs分子を供給するAs供給部と、

前記チャンバに対する前記エッチングガス供給部および前記As供給部の連通と遮断とを選択的に切り替える開閉機構と、

を備えることを特徴とする半導体素子の製造装置。 - 前記As供給部は、前記チャンバ内に連通したるつぼ及び前記るつぼを加熱するヒータを備えることを特徴とする請求項5に記載の半導体素子の製造装置。

- 前記チャンバ内を10℃以下に冷却する温度調整チラーを更に備えることを特徴とする請求項5または6に記載の半導体素子の製造装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013067014A JP6123414B2 (ja) | 2013-03-27 | 2013-03-27 | 半導体素子の製造方法、半導体素子の製造装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013067014A JP6123414B2 (ja) | 2013-03-27 | 2013-03-27 | 半導体素子の製造方法、半導体素子の製造装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014192369A JP2014192369A (ja) | 2014-10-06 |

| JP2014192369A5 JP2014192369A5 (ja) | 2016-02-18 |

| JP6123414B2 true JP6123414B2 (ja) | 2017-05-10 |

Family

ID=51838354

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013067014A Active JP6123414B2 (ja) | 2013-03-27 | 2013-03-27 | 半導体素子の製造方法、半導体素子の製造装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6123414B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN117461226A (zh) * | 2021-06-17 | 2024-01-26 | 三菱电机株式会社 | 光半导体元件及其制造方法 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06291032A (ja) * | 1993-04-06 | 1994-10-18 | Matsushita Electric Ind Co Ltd | 化合物半導体成長用基板 |

| JP3330218B2 (ja) * | 1994-03-25 | 2002-09-30 | 三菱電機株式会社 | 半導体装置の製造方法,及び半導体装置 |

| JP2858095B2 (ja) * | 1995-03-22 | 1999-02-17 | 光技術研究開発株式会社 | 化合物半導体の微細埋込構造の形成方法 |

| JPH09205254A (ja) * | 1996-01-26 | 1997-08-05 | Mitsubishi Electric Corp | 半導体装置の製造方法および半導体製造装置並びに半導体レーザの製造方法 |

| JPH09260289A (ja) * | 1996-03-19 | 1997-10-03 | Nippon Steel Corp | 化合物半導体単結晶の成長方法 |

| JP4864014B2 (ja) * | 2001-03-27 | 2012-01-25 | 株式会社リコー | 面発光型半導体レーザ素子の製造方法 |

-

2013

- 2013-03-27 JP JP2013067014A patent/JP6123414B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014192369A (ja) | 2014-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101436818B1 (ko) | 양자 웰 트랜지스터에 접촉부를 형성하는 기술 | |

| US8076740B2 (en) | Photo detector with a quantum dot layer | |

| CN108140581B (zh) | 隧道场效应晶体管 | |

| WO2016121408A1 (ja) | 電磁波検出器および電磁波検出器アレイ | |

| US20090001350A1 (en) | High hole mobility semiconductor device | |

| KR101922107B1 (ko) | 반도체소자 및 그 제조방법 | |

| US11193832B2 (en) | Infrared detector, imaging device including the same, and manufacturing method for infrared detector | |

| Narita et al. | Ultraviolet photodetectors using transparent gate AlGaN/GaN high electron mobility transistor on silicon substrate | |

| TW201501279A (zh) | 半導體元件及其製造方法 | |

| US20070045633A1 (en) | Semiconductor optical device having an improved current blocking layer and manufacturing method thereof | |

| US20210305449A1 (en) | Light source assembly, optical sensor assembly, and method of manufacturing a cell of the same | |

| JPH10125901A (ja) | 電界効果トランジスタ,及びその製造方法 | |

| JP2008053539A (ja) | 半導体光素子 | |

| JP6123414B2 (ja) | 半導体素子の製造方法、半導体素子の製造装置 | |

| JP2010016089A (ja) | 電界効果トランジスタ、その製造方法、及び半導体装置 | |

| US8441037B2 (en) | Semiconductor device having a thin film stacked structure | |

| US8891573B2 (en) | 6.1 angstrom III-V and II-VI semiconductor platform | |

| JP2016502278A (ja) | 温度安定性に優れる金属酸化物薄膜トランジスタ | |

| US7391798B2 (en) | Semiconductor laser device | |

| TW201327816A (zh) | 半導體裝置及其製造方法 | |

| JP2020009799A (ja) | トンネル電界効果トランジスタ | |

| JP2005251820A (ja) | ヘテロ接合型電界効果トランジスタ | |

| EP2590232A1 (en) | Photoreceptor element and method for producing same | |

| JP5483558B2 (ja) | 半導体薄膜の形成方法 | |

| JPH06164057A (ja) | 半導体レーザおよびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20151221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160915 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161004 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161104 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170307 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170320 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6123414 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |