JP6091273B2 - 半導体装置とその製造方法 - Google Patents

半導体装置とその製造方法 Download PDFInfo

- Publication number

- JP6091273B2 JP6091273B2 JP2013056803A JP2013056803A JP6091273B2 JP 6091273 B2 JP6091273 B2 JP 6091273B2 JP 2013056803 A JP2013056803 A JP 2013056803A JP 2013056803 A JP2013056803 A JP 2013056803A JP 6091273 B2 JP6091273 B2 JP 6091273B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor

- layer

- semiconductor layer

- substrate

- groove

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Optical Integrated Circuits (AREA)

- Light Receiving Elements (AREA)

Description

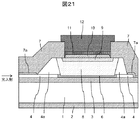

前記半導体基板上に形成され、第1の開口部を有する第1の絶縁膜と、

前記第1の開口部直下の前記半導体基板内に形成された第1の溝と、

前記第1の溝内の前記半導体基板上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1の半導体層と、

前記第1の溝内の前記第1の半導体層上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1導電型の第2の半導体層と、

前記第1の開口領域内の前記第2の半導体層上に形成され、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第1の半導体層及び前記第2の半導体層よりも大きい第1導電側の第3の半導体層と、

前記第1の開口領域内の前記第3の半導体層上に形成された金属層とを備え、

前記第1の溝の上部の開口領域は前記第1の開口部を取り囲むように形成され、前記第1の溝の上部では前記第1の絶縁膜からなる庇が形成され、前記第1の溝の側壁は前記半導体基板の(111)面を含み、前記第1の溝の底部は前記半導体基板の(100)面を含み、

前記第1の半導体層は、前記第1の溝底部を構成する前記半導体基板の(100)面と、前記第1の溝側壁を構成する半導体基板の(111)面と、前記第1の絶縁膜から成る庇の下部表面と、前記第2の半導体層とに接しており、

前記第2の半導体層は、前記第1の半導体層と、前記第1の絶縁膜から成る庇の下部表面と、前記第3の半導体層とに接しており、

前記第1の半導体層と前記第2の半導体層の界面は、前記第1の半導体層と前記第1の絶縁膜との界面よりも下部に位置し、

前記第3の半導体層と前記金属層の界面は、前記第1の絶縁膜の下部表面と前記第1の絶縁膜の上部表面の間に位置し、

前記第2の半導体層は前記半導体基板から空間的に分離していることを特徴とする半導体装置とする。

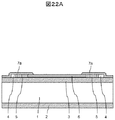

又、半導体基板上に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜に前記半導体基板が露出した第1の開口部を有する工程と、

前記第1の開口部直下の前記半導体基板内に第1の溝を形成する工程と、

前記第1の溝内の前記半導体基板上に、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1の半導体層を形成する工程と、

前記第1の溝内の前記第1の半導体層上に、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1導電型の第2の半導体層を形成する工程と、

前記第1の開口領域内の前記第2の半導体層上に、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第1の半導体層及び前記第2の半導体層よりも大きい第1導電側の第3の半導体層を形成する工程と、

前記第1の開口領域内の前記第3の半導体層上に金属層を形成する工程とを有し、

前記第1の溝を形成する工程は、前記第1の溝上部の開口領域が前記第1の開口部よりも広くなるよう、水平方向にも前記半導体基板のエッチングを施すことで前記第1の溝上部に前記第1の絶縁膜の庇を形成すると共に、前記第1の溝の底部が前記半導体基板の(100)面を有し、前記第1の溝の側壁が前記半導体基板の(111)面を有するように溝形成条件を調整する工程を含み、

前記第1の半導体層を形成する工程は、前記第1の半導体層が、前記第1の溝底部を構成する前記半導体基板の(100)面と、前記第1の溝側壁を構成する前記半導体基板の(111)面と、前記第1の絶縁膜から成る庇の下部表面とに接すると共に、前記第1の半導体層と前記第2の半導体層の界面が、前記第1の半導体層と前記第1の絶縁膜の界面よりも下部に位置するように前記第1の半導体層の形成条件を調整する工程を含み、

前記第2の半導体層を形成する工程は、前記第2の半導体層が前記第1の半導体層と、前記第1の絶縁膜の庇の下部表面とに接するように前記第2の半導体層の形成条件を調整する工程を含み、

前記第3の半導体層を形成する工程は、前記第3の半導体層と前記金属層の界面が前記第1の絶縁膜の下部表面と前記第1の絶縁膜の上部表面との間に位置するように前記第3の半導体層の形成条件を調整する工程を含むことを特徴とする半導体装置の製造方法とする。

SOI基板201上に、実施例1〜実施例4に示したいずれかのGe受光素子202と、Siからなる光変調器203が形成され、SOI基板のSi支持基板上には化合物半導体レーザ204が搭載されており、それぞれがSOI層からなる光導波路205で結合されている。上記光導波路205には光ファイバ206が結合しており、SOI基板201外部との光信号の送受信が可能な構造を成している。また、上記SOI基板201上には、LSIチップ208が搭載されている。上記LSIチップ208はGe受光素子202と光変調器203、更に化合物半導体レーザ204上の金属電極207と接続されており、化合物半導体レーザ204と光変調器203を駆動するドライバ回路、及びGe受光素子202の信号を受ける増幅回路等が組み込まれている。

本発明に関わる半導体装置は、半導体基板と、前記半導体基板上に形成され、第1の開口部を有する第1の絶縁膜と、前記第1の開口部直下の前記半導体基板内に形成された第1の溝と、前記第1の溝内の前記半導体基板上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1の半導体層と、前記第1の溝内の前記第1の半導体層上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1導電型の第2の半導体層と、前記第1の開口領域内の前記第2の半導体層上に形成され、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第1の半導体層及び前記第2の半導体層よりも大きい第1導電側の第3の半導体層と、前記第1の開口領域内の前記第3の半導体層上に形成された金属層から成り、前記第1の溝上部の開口領域は前記第1の開口部を取り囲むように形成され、前記第1の溝上部では前記第1の絶縁膜からなる庇が形成され、前記第1の溝は(111)面を含む前記半導体基板の側壁を有していて、前記第1の半導体層は、前記第1の溝底部に露出した前記半導体基板の(100)面と、(111)面を含む前記半導体基板の側壁と、前記第1の絶縁膜から成る庇の下部表面と、前記第2の半導体層と接しており、前記第2の半導体層は、前記第1の半導体層と前記第1の絶縁膜から成る庇の下部表面と、前記第3の半導体層と接しており、前記第1の半導体層と前記第2の半導体層の界面は、前記第1の半導体層と前記第1の絶縁膜の界面よりも下部に位置し、前記第3の半導体層と前記金属層の界面は前記第1の絶縁膜の下部表面と前記第1の絶縁膜の上部表面の間に位置し、前記第2の半導体層は前記半導体基板から空間的に分離していることを特徴とすると良い。

Claims (15)

- 半導体基板と、

前記半導体基板上に形成され、第1の開口部を有する第1の絶縁膜と、

前記第1の開口部直下の前記半導体基板内に形成された第1の溝と、

前記第1の溝内の前記半導体基板上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1の半導体層と、

前記第1の溝内の前記第1の半導体層上に形成され、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1導電型の第2の半導体層と、

前記第1の開口部内の前記第2の半導体層上に形成され、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第1の半導体層及び前記第2の半導体層よりも大きい第1導電側の第3の半導体層と、

前記第1の開口部内の前記第3の半導体層上に形成された金属層とを備え、

前記第1の溝の上部の開口領域は前記第1の開口部を取り囲むように形成され、前記第1の溝の上部では前記第1の絶縁膜からなる庇が形成され、前記第1の溝の側壁は前記半導体基板の(111)面を含み、前記第1の溝の底部は前記半導体基板の(100)面を含み、

前記第1の半導体層は、前記第1の溝底部を構成する前記半導体基板の(100)面と、前記第1の溝側壁を構成する半導体基板の(111)面と、前記第1の絶縁膜から成る庇の下部表面と、前記第2の半導体層とに接しており、

前記第2の半導体層は、前記第1の半導体層と、前記第1の絶縁膜から成る庇の下部表面と、前記第3の半導体層とに接しており、

前記第1の半導体層と前記第2の半導体層の界面は、前記第1の半導体層と前記第1の絶縁膜との界面よりも下部に位置し、

前記第3の半導体層と前記金属層の界面は、前記第1の絶縁膜の下部表面と前記第1の絶縁膜の上部表面の間に位置し、

前記第2の半導体層は前記半導体基板から空間的に分離していることを特徴とする半導体装置。 - 前記第1の絶縁膜から成る庇の水平方向の長さは、前記第1の溝の深さに対して10分の1倍以上且つ1倍以下であることを特徴とする請求項1に記載の半導体装置。

- 前記第2の半導体層と前記第3の半導体層中の不純物濃度は、深さ方向に対してほぼ一定であることを特徴とする請求項1または請求項2に記載の半導体装置。

- 前記第1の半導体層が受光機能を有することを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

- 前記半導体基板は、前記第1の溝底部の界面において第1導電型を示し、前記半導体装置がダイオードとしての機能を有することを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

- 前記半導体基板は、半導体支持基板と、前記半導体支持基板を覆うように形成された絶縁膜と、該絶縁膜上に位置し、導波路状にパターニングされた第1の光導波路とを備えることを特徴とする請求項1乃至5のいずれか一項に記載の半導体装置。

- 前記半導体基板は、前記第1の光導波路上に、前記第1の光導波路を覆い、前記第1の光導波路の一部表面が露出するような開口を有する絶縁膜と、前記開口内部の前記第1の光導波路上に前記半導体支持基板を構成する元素をその一部に含む第2の光導波路を有していることを特徴とする請求項6に記載の半導体装置。

- 前記第3の半導体層と前記金属層はオーミック接合界面を有することを特徴とする請求項1乃至7のいずれか一項に記載の半導体装置。

- 前記第3の半導体層と前記金属層はショットキー接合界面を有することを特徴とする請求項1乃至7のいずれか一項に記載の半導体装置。

- 前記半導体支持基板と前記第1の光導波路はシリコンで構成され、

前記第2の光導波路と前記第3の半導体層はシリコンまたはシリコン・ゲルマニウムで構成され、

前記第1の半導体層と前記第2の半導体層はゲルマニウムまたはシリコン・ゲルマニウムで構成され、

前記第1の半導体層と前記第2の半導体層のゲルマニウム組成が、共に前記第2の光導波路と前記第3の半導体層のいずれのゲルマニウム組成よりも大きいことを特徴とする請求項6に記載の半導体装置。 - 半導体基板上に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜に前記半導体基板が露出した第1の開口部を有する工程と、

前記第1の開口部直下の前記半導体基板内に第1の溝を形成する工程と、

前記第1の溝内の前記半導体基板上に、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1の半導体層を形成する工程と、

前記第1の溝内の前記第1の半導体層上に、前記半導体基板の主成分を成す元素とは異なる元素をその一部に含み、禁制帯幅が前記半導体基板よりも小さい第1導電型の第2の半導体層を形成する工程と、

前記第1の開口部内の前記第2の半導体層上に、前記半導体基板の主成分を成す元素と同一元素をその一部に含み、禁制帯幅が前記第1の半導体層及び前記第2の半導体層よりも大きい第1導電側の第3の半導体層を形成する工程と、

前記第1の開口部内の前記第3の半導体層上に金属層を形成する工程とを有し、

前記第1の溝を形成する工程は、前記第1の溝上部の開口領域が前記第1の開口部よりも広くなるよう、水平方向にも前記半導体基板のエッチングを施すことで前記第1の溝上部に前記第1の絶縁膜の庇を形成すると共に、前記第1の溝の底部が前記半導体基板の(100)面を有し、前記第1の溝の側壁が前記半導体基板の(111)面を有するように溝形成条件を調整する工程を含み、

前記第1の半導体層を形成する工程は、前記第1の半導体層が、前記第1の溝底部を構成する前記半導体基板の(100)面と、前記第1の溝側壁を構成する前記半導体基板の(111)面と、前記第1の絶縁膜から成る庇の下部表面とに接すると共に、前記第1の半導体層と前記第2の半導体層の界面が、前記第1の半導体層と前記第1の絶縁膜の界面よりも下部に位置するように前記第1の半導体層の形成条件を調整する工程を含み、

前記第2の半導体層を形成する工程は、前記第2の半導体層が前記第1の半導体層と、前記第1の絶縁膜の庇の下部表面とに接するように前記第2の半導体層の形成条件を調整する工程を含み、

前記第3の半導体層を形成する工程は、前記第3の半導体層と前記金属層の界面が前記第1の絶縁膜の下部表面と前記第1の絶縁膜の上部表面との間に位置するように前記第3の半導体層の形成条件を調整する工程を含むことを特徴とする半導体装置の製造方法。 - 前記庇の水平方向の長さは、前記第1の溝の深さに対して10分の1倍以上且つ1倍以下であることを特徴とする請求項11に記載の半導体装置の製造方法。

- 前記第2の半導体層と前記第3の半導体層の形成は、不純物を添加したエピタキシャル成長により行い、前記第2の半導体層と前記第3の半導体層中の不純物濃度を、深さ方向に対してほぼ一定とすることを特徴とする請求項11または請求項12に記載の半導体装置の製造方法。

- 前記半導体基板には、半導体支持基板と、前記半導体支持基板を覆う絶縁膜と、前記絶縁膜上に形成された単結晶半導体層を有する基板を用い、該絶縁膜上の半導体層を、導波路状にパターニングして第1の光導波路を形成することを特徴とする請求項11乃至13のいずれか一項に記載の半導体装置の製造方法。

- 前記半導体支持基板と前記第1の光導波路がシリコンから成る基板を用い、

前記第2の光導波路と前記第3の半導体層をシリコンまたはシリコン・ゲルマニウムとし、

前記第1の半導体層と前記第2の半導体層をゲルマニウムまたはシリコン・ゲルマニウムとし、

前記第1の半導体層と前記第2の半導体層のゲルマニウム組成が、共に前記第2の光導波路と前記第3の半導体層のいずれのゲルマニウム組成よりも大きくすることを特徴とする請求項14に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013056803A JP6091273B2 (ja) | 2013-03-19 | 2013-03-19 | 半導体装置とその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013056803A JP6091273B2 (ja) | 2013-03-19 | 2013-03-19 | 半導体装置とその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014183195A JP2014183195A (ja) | 2014-09-29 |

| JP2014183195A5 JP2014183195A5 (ja) | 2016-03-31 |

| JP6091273B2 true JP6091273B2 (ja) | 2017-03-08 |

Family

ID=51701617

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013056803A Active JP6091273B2 (ja) | 2013-03-19 | 2013-03-19 | 半導体装置とその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6091273B2 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6514904B2 (ja) * | 2015-02-05 | 2019-05-15 | 富士通株式会社 | 光半導体素子 |

| JP6184539B2 (ja) * | 2016-02-18 | 2017-08-23 | 沖電気工業株式会社 | 半導体受光素子、光電融合モジュール、半導体受光素子の製造方法 |

| JP2018049856A (ja) * | 2016-09-20 | 2018-03-29 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2019117855A (ja) | 2017-12-27 | 2019-07-18 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US11393939B2 (en) * | 2019-09-20 | 2022-07-19 | Taiwan Semiconductor Manufacturing Company Ltd. | Photo sensing device and method of fabricating the photo sensing device |

| US11404590B2 (en) * | 2019-09-20 | 2022-08-02 | Taiwan Semiconductor Manufacturing Company Ltd. | Photo sensing device and method of fabricating the photo sensing device |

| US11393940B2 (en) | 2019-09-20 | 2022-07-19 | Taiwan Semiconductor Manufacturing Co., Ltd. | Photodetector and method for forming the same |

| WO2021145077A1 (ja) * | 2020-01-15 | 2021-07-22 | 東京エレクトロン株式会社 | 成膜方法、成膜装置、および半導体装置の製造方法 |

| JP7468791B1 (ja) | 2022-12-01 | 2024-04-16 | 三菱電機株式会社 | 導波路型受光素子 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS51107768A (ja) * | 1975-02-17 | 1976-09-24 | Siemens Ag | Heimendonotakaishirikonkubominoseizohoho |

| JPS57180147A (en) * | 1981-04-30 | 1982-11-06 | Fujitsu Ltd | Semiconductor device |

| EP0227523A3 (en) * | 1985-12-19 | 1989-05-31 | SILICONIX Incorporated | Method for obtaining regions of dielectrically isolated single crystal silicon |

| JP2988353B2 (ja) * | 1995-03-13 | 1999-12-13 | 日本電気株式会社 | 光検出用の半導体装置及びその製造方法 |

| CN101836295A (zh) * | 2007-08-08 | 2010-09-15 | 新加坡科技研究局 | 半导体装置及其制备方法 |

-

2013

- 2013-03-19 JP JP2013056803A patent/JP6091273B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014183195A (ja) | 2014-09-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6091273B2 (ja) | 半導体装置とその製造方法 | |

| JP5917978B2 (ja) | 半導体装置及びその製造方法 | |

| US8294213B2 (en) | Semiconductor photodiode device and manufacturing method thereof | |

| US11393940B2 (en) | Photodetector and method for forming the same | |

| US20200158954A1 (en) | Integrated photonics including waveguiding material | |

| US9653639B2 (en) | Laser using locally strained germanium on silicon for opto-electronic applications | |

| JP6048578B2 (ja) | 半導体受光素子及びその製造方法 | |

| US5818322A (en) | Silicon photosensitive element | |

| JP2020161674A (ja) | 受光器 | |

| JP2015046429A (ja) | 受光素子およびその製造方法 | |

| EP4205184A1 (en) | Diode with light-sensitive intrinsic region | |

| CN107863399B (zh) | 基于LRC工艺的n-Ge-i-Ge-p-Si结构波导型光电探测器及其制备方法 | |

| JP2015088756A (ja) | 基板構造体とそれを含むcmos素子及びその製造方法 | |

| JP2014183194A (ja) | 半導体装置の製造方法 | |

| WO2015115396A1 (ja) | SiGeフォトダイオード | |

| US20200144443A1 (en) | Method for producing a photodiode and photodiode | |

| JP6696735B2 (ja) | Ge系光素子及びその製造方法 | |

| KR20140048463A (ko) | 반도체 레이저 및 그 제조방법 | |

| CN112186075A (zh) | 一种波导型光电探测器及制造方法 | |

| CN116666500B (zh) | 锗光电探测器及通过热失配应力提高其长波响应的方法 | |

| JP7275843B2 (ja) | 光半導体素子 | |

| JP2024117750A (ja) | ゲルマニウム半導体装置及びその製造方法 | |

| US20190296181A1 (en) | Aluminum gallium arsenide and indium gallium phosphide power converter on silicon | |

| CN114914789A (zh) | 一种基于3μm SOI的集成硅基激光器及其制备方法 | |

| CN111354829A (zh) | 光电集成电路及其制备方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20141027 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20141030 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160212 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160212 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160914 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160920 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161104 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170110 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170207 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6091273 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |