JP6007796B2 - 回路基板の製造方法 - Google Patents

回路基板の製造方法 Download PDFInfo

- Publication number

- JP6007796B2 JP6007796B2 JP2013001853A JP2013001853A JP6007796B2 JP 6007796 B2 JP6007796 B2 JP 6007796B2 JP 2013001853 A JP2013001853 A JP 2013001853A JP 2013001853 A JP2013001853 A JP 2013001853A JP 6007796 B2 JP6007796 B2 JP 6007796B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit board

- chip

- solder

- resist

- openings

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 14

- 229910000679 solder Inorganic materials 0.000 claims description 90

- 239000002245 particle Substances 0.000 claims description 27

- 238000000034 method Methods 0.000 claims description 23

- 230000004907 flux Effects 0.000 claims description 7

- 238000002844 melting Methods 0.000 claims description 4

- 230000008018 melting Effects 0.000 claims description 4

- 239000012299 nitrogen atmosphere Substances 0.000 claims description 4

- 230000002093 peripheral effect Effects 0.000 description 25

- 238000010586 diagram Methods 0.000 description 17

- 238000005516 engineering process Methods 0.000 description 14

- 239000000758 substrate Substances 0.000 description 7

- 238000012986 modification Methods 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000011161 development Methods 0.000 description 4

- 230000007547 defect Effects 0.000 description 2

- BDAGIHXWWSANSR-UHFFFAOYSA-N methanoic acid Natural products OC=O BDAGIHXWWSANSR-UHFFFAOYSA-N 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- OSWFIVFLDKOXQC-UHFFFAOYSA-N 4-(3-methoxyphenyl)aniline Chemical compound COC1=CC=CC(C=2C=CC(N)=CC=2)=C1 OSWFIVFLDKOXQC-UHFFFAOYSA-N 0.000 description 1

- RSWGJHLUYNHPMX-UHFFFAOYSA-N Abietic-Saeure Natural products C12CCC(C(C)C)=CC2=CCC2C1(C)CCCC2(C)C(O)=O RSWGJHLUYNHPMX-UHFFFAOYSA-N 0.000 description 1

- KHPCPRHQVVSZAH-HUOMCSJISA-N Rosin Natural products O(C/C=C/c1ccccc1)[C@H]1[C@H](O)[C@@H](O)[C@@H](O)[C@@H](CO)O1 KHPCPRHQVVSZAH-HUOMCSJISA-N 0.000 description 1

- 239000002313 adhesive film Substances 0.000 description 1

- 150000001412 amines Chemical class 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 239000006071 cream Substances 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 235000019253 formic acid Nutrition 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 239000000178 monomer Substances 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 238000007781 pre-processing Methods 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- KHPCPRHQVVSZAH-UHFFFAOYSA-N trans-cinnamyl beta-D-glucopyranoside Natural products OC1C(O)C(O)C(CO)OC1OCC=CC1=CC=CC=C1 KHPCPRHQVVSZAH-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/108—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern by semi-additive methods; masks therefor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/4853—Connection or disconnection of other leads to or from a metallisation, e.g. pins, wires, bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

- H01L23/49816—Spherical bumps on the substrate for external connection, e.g. ball grid arrays [BGA]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/3457—Solder materials or compositions; Methods of application thereof

- H05K3/3478—Applying solder preforms; Transferring prefabricated solder patterns

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/3457—Solder materials or compositions; Methods of application thereof

- H05K3/3485—Applying solder paste, slurry or powder

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/563—Encapsulation of active face of flip-chip device, e.g. underfilling or underencapsulation of flip-chip, encapsulation preform on chip or mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12042—LASER

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/111—Pads for surface mounting, e.g. lay-out

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/099—Coating over pads, e.g. solder resist partly over pads

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10954—Other details of electrical connections

- H05K2201/10977—Encapsulated connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/341—Surface mounted components

- H05K3/3431—Leadless components

- H05K3/3436—Leadless components having an array of bottom contacts, e.g. pad grid array or ball grid array components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/3452—Solder masks

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49155—Manufacturing circuit on or in base

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Geometry (AREA)

- Ceramic Engineering (AREA)

- Wire Bonding (AREA)

- Electric Connection Of Electric Components To Printed Circuits (AREA)

Description

1.本技術を適用した電子部品の実施の形態

2.回路基板の製造方法

3.変形例

まず、図1乃至図7を参照して、本技術を適用した電子部品の一実施の形態について説明する。

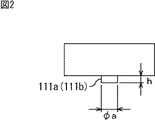

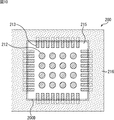

図1は、本技術を適用した電子部品を構成するチップ100の裏面を模式的に示す図である。なお、図を分かりやすくするために、図中、エリア端子111a及びペリフェラル端子111bの符号の図示を一部省略している。

図3は、本技術を適用した電子部品を構成し、チップ100が実装される回路基板200の構成例を示している。図3の上の図は、回路基板200を上から見た模式図であり、下の図は、回路基板200の断面の模式図である。なお、図を分かりやすくするために、図中、ランド212、パッド213、はんだバンプ214a、及び、はんだバンプ214bの符号の図示を一部省略している。

本技術を適用した電子部品300は、回路基板200上にチップ100を実装することにより製造される。

次に、図8乃至図12を参照して、回路基板200の製造方法について説明する。

まず、ベース基板211のランド212、パッド213、及び、絶縁膜215の表面が平坦になるように平坦化処理が行われる。これにより、ランド212、パッド213、及び、絶縁膜215の高さが均一になり、実装領域200Dの表面が平坦になる。

次に、回路基板200の実装面全体にレジスト401が塗布又はラミネートされる。これにより、実装領域200Dの表面がレジスト401により覆われる。なお、レジスト401は、例えば感光性樹脂により構成され、その厚さは、例えば30μmとされる。

次に、露光及び現像を行うことにより、レジスト401に開口401A及び開口401B(図11)が形成される。

次に、レジスト401の開口401A及び開口401Bに、それぞれ略同量の粉状のはんだ粒子が充填される。

次に、窒素雰囲気中においてリフローが行われる。これにより、回路基板200全体が加熱され、開口401A内及び開口401B内のはんだ粒子421が溶け、開口401A及び開口401B内において、略同じ形状のはんだバンプ214a及びはんだバンプ214bがそれぞれ形成される。

次に、レジスト401が全て除去される。レジスト401の除去には、例えば、アミン系剥離液が用いられる。これにより、実装領域200Dが全て露出する。また、はんだ粒子421から生じるフラックスの残渣等の洗浄が行われる。

以下、上述した本技術の実施の形態の変形例について説明する。

例えば、回路基板200の製造時に、水素や蟻酸等で満たされた還元雰囲気中でリフロー工程を行うようにしてもよい。これにより、はんだ粒子の表面をフラックスによりコーティングする必要がなくなる。

また、以上に示した回路基板200のパターン(ランド212及びパッド213)の形状は、その一例であり、この例に限定されるものではない。パターンの形状の種類も上述した2種類に限定されるものではなく、1種類、或いは、3種類以上の場合にも本技術を適用することができる。しかも、本技術によれば、回路基板上に露出しているパターンによらずに、略同一形状のはんだバンプを、所定の位置に高精度に形成することができる。

さらに、上述したチップ100の端子111、はんだバンプ214、レジスト401の開口401A,401B、及び、はんだ粒子421等の形状や寸法は、その一例であり、必要に応じて変更することが可能である。例えば、以上の説明では、チップ100の端子111の径を、はんだバンプ214の径と同じにする例を示したが、はんだバンプ214の径より大きくしたり、又は、小さくしたりすることが可能である。

所定のチップが実装される実装領域の表面が平坦化され、かつ、露出しており、

前記実装領域に形成されているパターン上の前記チップの各端子が接続される接続位置にそれぞれ略同じ形状のはんだバンプが形成されている

回路基板。

(2)

前記実装領域の表面を平坦化する第1の工程と、

前記実装領域をレジストで覆う第2の工程と、

前記パターン上の各前記接続位置に合わせて同じ形状の開口を前記レジストにそれぞれ形成する第3の工程と、

前記開口より径が小さいはんだ粒子を前記開口に充填する第4の工程と、

前記はんだ粒子を溶かし、前記開口内に前記はんだバンプを形成する第5の工程と、

前記レジストを除去する第6の工程と

を含む工程により製造される前記(1)に記載の回路基板。

(3)

前記実装領域の周囲を囲むように前記回路基板の実装面の周縁にソルダレジストが形成されている

前記(1)又は(2)に記載の回路基板。

(4)

所定のチップが実装される実装領域の表面を平坦化する第1の工程と、

前記実装領域をレジストで覆う第2の工程と、

前記実装領域に形成されているパターン上の前記チップの各端子が接続される接続位置に合わせて同じ形状の開口を前記レジストにそれぞれ形成する第3の工程と、

前記開口より径が小さいはんだ粒子を前記開口に充填する第4の工程と、

前記はんだ粒子を溶かし、前記開口内にはんだバンプを形成する第5の工程と、

前記レジストを除去する第6の工程と

を含む回路基板の製造方法。

(5)

前記はんだ粒子の表面がフラックスによりコーティングされており、

前記第5の工程を窒素雰囲気中で行う

前記(4)に記載の回路基板の製造方法。

(6)

チップと、

前記チップを実装する回路基板と

を備え、

前記回路基板は、

前記チップが実装される実装領域の表面が平坦化され、かつ、露出しており、

前記実装領域に形成されているパターン上の前記チップの各端子が接続される接続位置にそれぞれ略同じ形状のはんだバンプが形成されている

電子部品。

(7)

前記回路基板は、

前記実装領域の表面を平坦化する第1の工程と、

前記実装領域をレジストで覆う第2の工程と、

前記パターン上の各前記接続位置に合わせて同じ形状の開口を前記レジストにそれぞれ形成する第3の工程と、

前記開口より径が小さいはんだ粒子を前記開口に充填する第4の工程と、

前記はんだ粒子を溶かし、前記開口内に前記はんだバンプを形成する第5の工程と、

前記レジストを除去する第6の工程と

を含む工程により製造される

前記(6)に記載の電子部品。

Claims (2)

- 所定のチップが実装される実装領域のパターン及び絶縁膜の表面を平坦化する第1の工程と、

前記実装領域をレジストで覆う第2の工程と、

前記パターン上の前記チップの各端子が接続される接続位置に合わせて同じ形状の開口を前記レジストにそれぞれ形成する第3の工程と、

前記開口より径が小さいはんだ粒子を前記開口に充填する第4の工程と、

前記はんだ粒子を溶かし、前記開口内にはんだバンプを形成する第5の工程と、

前記レジストを除去し、前記パターン及び前記絶縁膜の表面が平坦化されている前記実装領域を露出する第6の工程と

を含む回路基板の製造方法。 - 前記はんだ粒子の表面がフラックスによりコーティングされており、

前記第5の工程を窒素雰囲気中で行う

請求項1に記載の回路基板の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013001853A JP6007796B2 (ja) | 2013-01-09 | 2013-01-09 | 回路基板の製造方法 |

| TW102143891A TWI633812B (zh) | 2013-01-09 | 2013-11-29 | 製造一電路基板之方法 |

| US14/133,074 US9918388B2 (en) | 2013-01-09 | 2013-12-18 | Circuit substrate, method of manufacturing circuit substrate, and electronic component |

| CN201410001411.2A CN103917040B (zh) | 2013-01-09 | 2014-01-02 | 电路基板、电路基板的制造方法和电子组件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013001853A JP6007796B2 (ja) | 2013-01-09 | 2013-01-09 | 回路基板の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014135354A JP2014135354A (ja) | 2014-07-24 |

| JP2014135354A5 JP2014135354A5 (ja) | 2015-03-19 |

| JP6007796B2 true JP6007796B2 (ja) | 2016-10-12 |

Family

ID=51042336

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013001853A Active JP6007796B2 (ja) | 2013-01-09 | 2013-01-09 | 回路基板の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9918388B2 (ja) |

| JP (1) | JP6007796B2 (ja) |

| CN (1) | CN103917040B (ja) |

| TW (1) | TWI633812B (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104733359A (zh) * | 2015-03-24 | 2015-06-24 | 王春 | 一种高效、节能金属图形线路速成的ept |

| US10014268B2 (en) * | 2016-03-01 | 2018-07-03 | Advanced Semiconductor Engineering, Inc. | Semiconductor chip, semiconductor device and manufacturing process for manufacturing the same |

| EP3433603B1 (en) | 2016-07-19 | 2020-01-29 | HP Indigo B.V. | Assessment of primer content on a print substrate |

| US10643863B2 (en) * | 2017-08-24 | 2020-05-05 | Advanced Semiconductor Engineering, Inc. | Semiconductor package and method of manufacturing the same |

| WO2020004510A1 (ja) * | 2018-06-26 | 2020-01-02 | 日立化成株式会社 | 異方性導電フィルム及びその製造方法並びに接続構造体の製造方法 |

| CN114420003B (zh) * | 2022-01-17 | 2024-01-02 | 深圳市思坦科技有限公司 | 集成式led结构及制备方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6440174A (en) * | 1987-08-04 | 1989-02-10 | Taruchin Kk | Soldering method |

| JP3362079B2 (ja) | 1993-05-12 | 2003-01-07 | 昭和電工株式会社 | はんだ粉末定着方法 |

| US5686318A (en) * | 1995-12-22 | 1997-11-11 | Micron Technology, Inc. | Method of forming a die-to-insert permanent connection |

| JP3819576B2 (ja) * | 1997-12-25 | 2006-09-13 | 沖電気工業株式会社 | 半導体装置及びその製造方法 |

| WO2000010369A1 (fr) * | 1998-08-10 | 2000-02-24 | Fujitsu Limited | Realisation de bossages de soudure, methode de montage d'un dispositif electronique et structure de montage pour ce dispositif |

| JP4087876B2 (ja) * | 1998-08-10 | 2008-05-21 | 富士通株式会社 | ハンダバンプの形成方法 |

| JP3420076B2 (ja) | 1998-08-31 | 2003-06-23 | 新光電気工業株式会社 | フリップチップ実装基板の製造方法及びフリップチップ実装基板及びフリップチップ実装構造 |

| KR100723454B1 (ko) * | 2004-08-21 | 2007-05-30 | 페어차일드코리아반도체 주식회사 | 높은 열 방출 능력을 구비한 전력용 모듈 패키지 및 그제조방법 |

| CN100473259C (zh) * | 2004-04-13 | 2009-03-25 | 纬创资通股份有限公司 | 电路板组装方法与结构及用以组装该结构的工装用具 |

| US7928591B2 (en) * | 2005-02-11 | 2011-04-19 | Wintec Industries, Inc. | Apparatus and method for predetermined component placement to a target platform |

| JP5104460B2 (ja) * | 2008-03-28 | 2012-12-19 | 富士通株式会社 | 突起電極を有する基板の製造方法 |

| JP5456545B2 (ja) * | 2009-04-28 | 2014-04-02 | 昭和電工株式会社 | 回路基板の製造方法 |

| JP5658442B2 (ja) * | 2009-06-02 | 2015-01-28 | 株式会社東芝 | 電子部品とその製造方法 |

-

2013

- 2013-01-09 JP JP2013001853A patent/JP6007796B2/ja active Active

- 2013-11-29 TW TW102143891A patent/TWI633812B/zh active

- 2013-12-18 US US14/133,074 patent/US9918388B2/en active Active

-

2014

- 2014-01-02 CN CN201410001411.2A patent/CN103917040B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20140191382A1 (en) | 2014-07-10 |

| US9918388B2 (en) | 2018-03-13 |

| JP2014135354A (ja) | 2014-07-24 |

| TW201429329A (zh) | 2014-07-16 |

| CN103917040A (zh) | 2014-07-09 |

| TWI633812B (zh) | 2018-08-21 |

| CN103917040B (zh) | 2017-09-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6007796B2 (ja) | 回路基板の製造方法 | |

| TWI496259B (zh) | 封裝裝置及其製造方法 | |

| JP5837339B2 (ja) | 半導体装置の製造方法及び半導体装置 | |

| KR101940237B1 (ko) | 미세 피치 pcb 기판에 솔더 범프 형성 방법 및 이를 이용한 반도체 소자의 플립 칩 본딩 방법 | |

| WO2016107062A1 (zh) | 一种在倒装芯片基板上小间距之间制备高凸点锡球的制备方法 | |

| JP6538596B2 (ja) | 電子部品の製造方法及び電子部品の製造装置 | |

| CN104659002A (zh) | 半导体封装件及其制造方法 | |

| JP2008252042A (ja) | 回路基板、および回路基板の形成方法 | |

| JP5320165B2 (ja) | 半導体装置 | |

| TW201417196A (zh) | 晶片封裝基板和結構及其製作方法 | |

| US9674952B1 (en) | Method of making copper pillar with solder cap | |

| JP2011171427A (ja) | 積層型半導体装置 | |

| TWI655727B (zh) | 封裝基板及包含該封裝基板的覆晶封裝電路 | |

| JP2018037520A (ja) | 半導体装置、電子装置、半導体装置の製造方法及び電子装置の製造方法 | |

| JP3942952B2 (ja) | リフロー半田付け方法 | |

| JP2010123676A (ja) | 半導体装置の製造方法、半導体装置 | |

| JP5062376B1 (ja) | 電子部品実装基板の製造方法 | |

| JP2009188026A (ja) | 電子部品 | |

| JP2008140868A (ja) | 多層配線基板および半導体装置 | |

| KR101037744B1 (ko) | 전도성 범프를 갖는 칩 및 그 제조방법과, 칩을 구비한 전자부품 및 그 제조방법 | |

| JP2007027701A (ja) | 配線基板 | |

| US8604356B1 (en) | Electronic assembly having increased standoff height | |

| TWI613741B (zh) | 銲點凸塊製造方法 | |

| JP5934057B2 (ja) | プリント回路基板 | |

| JP2006319030A (ja) | 回路基板とその製造方法、および半導体装置とその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150129 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150129 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20151106 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151112 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151211 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160621 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160722 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160816 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160829 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6007796 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |