JP5935287B2 - 撮像装置および撮像表示システム - Google Patents

撮像装置および撮像表示システム Download PDFInfo

- Publication number

- JP5935287B2 JP5935287B2 JP2011231768A JP2011231768A JP5935287B2 JP 5935287 B2 JP5935287 B2 JP 5935287B2 JP 2011231768 A JP2011231768 A JP 2011231768A JP 2011231768 A JP2011231768 A JP 2011231768A JP 5935287 B2 JP5935287 B2 JP 5935287B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- imaging

- reset

- potential

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/30—Transforming light or analogous information into electric information

- H04N5/32—Transforming X-rays

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/65—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to reset noise, e.g. KTC noise related to CMOS structures by techniques other than CDS

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/71—Charge-coupled device [CCD] sensors; Charge-transfer registers specially adapted for CCD sensors

- H04N25/75—Circuitry for providing, modifying or processing image signals from the pixel array

Description

1.実施の形態(2つのゲート電圧パルスにおいて、一方をオン電位、他方をオフ電位としてリセット駆動を行う撮像装置の例)

2.変形例1(一方の電圧パルスの切り換えタイミングを早めた例)

3.変形例2(一方の電圧パルスの振幅(オン電位値)を相対的に小さくした例)

4.変形例3(一方の電圧パルスの切り換えタイミングを早め、かつ振幅を相対的に小さくした例)

5.変形例4(1回目のリセット駆動の際に切り換えタイミングを早めた例)

6.変形例5(一方のゲート電極をLDD層にオーバーラップさせた例)

7.変形例6(パッシブ型の画素回路の他の例)

8.変形例7(パッシブ型の画素回路の他の例)

9.変形例8,9(アクティブ型の画素回路の例)

10.変形例10,11(放射線に基づいて撮像を行う撮像部の例)

12.適用例(撮像表示システムへの適用例)

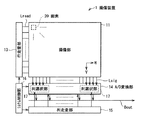

[撮像装置1の全体構成]

図1は、本開示の一実施の形態に係る撮像装置(撮像装置1)の全体のブロック構成を表すものである。撮像装置1は、入射光(撮像光)に基づいて被写体の情報を読み取る(被写体を撮像する)ものである。この撮像装置1は、撮像部11、行走査部13、A/D変換部14、列走査部15およびシステム制御部16を備えている。これらのうち、行走査部13、A/D変換部14、列走査部15およびシステム制御部16が、本開示における「駆動部」の一具体例に対応する。

撮像部11は、入射光(撮像光)に応じて電気信号を発生させるものである。この撮像部11では、画素(撮像画素,単位画素)20が、行列状(マトリクス状)に2次元配置されており、各画素20は、撮像光の光量に応じた電荷量の光電荷を発生して内部に蓄積する光電変換素子(後述の光電変換素子21)を有している。尚、図1中に示したように、以下、撮像部11内における水平方向(行方向)を「H」方向とし、垂直方向(列方向)を「V」方向として説明する。

行走査部13は、後述のシフトレジスタ回路や所定の論理回路等を含んで構成されており、撮像部11内の複数の画素20に対して行単位(水平ライン単位)での駆動(線順次走査)を行う画素駆動部(行走査回路)である。具体的には、後述する読み出し動作やリセット動作等の撮像動作を例えば線順次走査により行う。尚、この線順次走査は、読み出し制御線Lreadを介して前述した行走査信号を各画素20へ供給することによって行われるようになっている。

A/D変換部14は、複数(ここでは4つ)の信号線Lsigごとに1つ設けられた複数の列選択部17を有しており、信号線Lsigを介して入力した信号電圧(信号電荷)に基づいてA/D変換(アナログ/デジタル変換)を行うものである。これにより、デジタル信号からなる出力データDout(撮像信号)が生成され、外部へ出力されるようになっている。

列走査部15は、例えば図示しないシフトレジスタやアドレスデコーダ等を含んで構成されており、上記した列選択部17内の各スイッチSW2を走査しつつ順番に駆動するものである。このような列走査部15による選択走査によって、信号線Lsigの各々を介して読み出された各画素20の信号(上記した出力データDout)が、順番に外部へ出力されるようになっている。

システム制御部16は、行走査部13、A/D変換部14および列走査部15の動作を制御するものである。具体的には、システム制御部16は、前述した各種のタイミング信号(制御信号)を生成するタイミングジェネレータを有しており、このタイミングジェネレータにおいて生成される各種のタイミング信号を基に、行走査部13、A/D変換部14および列走査部15の駆動制御を行う。このシステム制御部16の制御に基づいて、行走査部13、A/D変換部14および列走査部15がそれぞれ撮像部11内の複数の画素20に対する撮像駆動(線順次撮像駆動)を行うことにより、撮像部11から出力データDoutが取得されるようになっている。

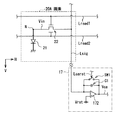

本実施の形態の撮像装置1では、撮像光Linが撮像部11へ入射すると、各画素20内の光電変換素子21では、この撮像光Linが信号電荷に変換(光電変換)される。このとき、蓄積ノードNでは、光電変換により発生した信号電荷の蓄積によって、ノード容量に応じた電圧変化が生じる。具体的には、蓄積ノード容量をCs、発生した信号電荷をqとすると、蓄積ノードNでは(q/Cs)の分だけ電圧が変化(ここでは低下)する。このような電圧変化に応じて、トランジスタ22のドレインには入力電圧Vin(信号電荷に対応した電圧)が印加される。このトランジスタ22へ供給される入力電圧Vin(蓄積ノードNに蓄積された信号電荷)は、読み出し制御線Lreadから供給される行走査信号に応じてトランジスタ22がオン状態になると、画素20から信号線Lsigへ読み出される。

図7(A),(B)は、露光期間および読み出し期間における画素20および列選択部17内のチャージアンプ回路の動作例を表したものである。尚、以下では説明の便宜上、トランジスタ22のオン・オフ状態を、スイッチを用いて図示している。

上述のように、読み出し/第1リセット期間Tr1では、読み出し動作に伴ってリセット動作がなされるが、この期間Tr1後であっても、それ以前に蓄積されていた信号電荷の一部が画素20内に(残留)する場合がある。信号電荷の一部が画素20内に残ると、次の読み出し動作時(次のフレーム期間での撮像時)においてその残留電荷に起因した残像が発生し、撮像画質が劣化してしまう。以下、図8〜図12を参照して、このような信号電荷の残存について、詳細に説明する。

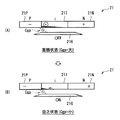

上記のような信号電荷の残存が発生する理由の一つとして、外光(特に、強外光)の影響を受けて画素20内の電荷が飽和してしまうことが考えられる。光電変換素子21では、ゲート電極21Gに印加されるゲート電圧により、真性半導体層21Iが、蓄積状態(飽和状態)、空乏状態、反転状態のいずれかの状態となる。ところが、薄膜フォトダイオードでは、その蓄積状態もしくは反転状態においてゲート電極21G側の界面に電荷が誘起された状態(図8(A))から、空乏状態(図8(B))に遷移するには、数百μsオーダーの時間が必要である。通常、PIN型のフォトダイオードは、空乏状態で光感度が最大となるため空乏状態で使用するが、例えば強外光が照射されてVnp<0Vの状態になると、蓄積状態に遷移する。尚、Vnpは、p型半導体層21P側から見たn型半導体層21Nの電位である。

そこで本実施の形態では、複数回(ここでは、上記読み出し/第1リセット期間Tr1におけるリセット動作を含む計2回)のリセット動作が行われる。また、読み出し駆動およびリセット駆動は、後述するように線順次でなされ、詳細には読み出し駆動および複数回のリセット駆動が単一の線順次駆動によってなされる。これにより、上記残留電荷を低減し、この残留電荷に起因して生じる残像を抑えるようにしている。以下、この複数回のリセット動作について詳細に説明する。

第2リセット期間Tr2では、具体的には、例えば図15(A)に示した第1の動作例のようにして、2回目のリセット動作が行われる。即ち、画素20内のトランジスタ22がオン状態になると共に、チャージアンプ回路におけるスイッチSW1もオン状態となっている。これにより、チャージアンプ172を用いたボルテージフォロワ回路が形成されている。このため、チャージアンプ172では、その帰還特性(フィードバック特性)により、負側の入力端子側(信号線Lsig側)の電圧が、正側の入力端子に印加されているリセット電圧Vrstに略等しくなる。このように第1の動作例では、チャージアンプ172における帰還特性を利用して、画素20内の蓄積ノードNの電位Vnがリセット電圧Vrstに変位する(2回目のリセット動作がなされる)。

上述のように、複数回のリセット動作がなされることにより、残留電荷を抑制して残像発生を低減することができるが、この残留電荷排出のためのリセット駆動に伴って、いわゆるチャージインジェクションと呼ばれる現象が生じる。即ち、蓄積ノードNでは、上述のように読み出し/第1リセット期間Tr1後に所定のリセット電圧Vrstとなるが、この後、トランジスタ22がオン状態からオフ状態に遷移する。この際、その電位差(オン電位とオフ電位との差)に応じて、蓄積ノードNの電位がリセット電圧Vrstから微小に変動する。ここでは、蓄積ノードNが光電変換素子21のカソード側に接続されていることから、図14(E)中の矢印X1で示したように、電位Vnがリセット電位Vrstから降下する。このチャージインジェクションの発生は、撮像データDoutにおいてノイズとなり画質劣化を招くことから、できるだけ低減されることが望ましい。また、このトランジスタ22のオフ動作の後、例えば図17に示したように、画素20内の寄生容量(トランジスタ22のゲート・ドレイン間に形成された寄生容量Cgd,ゲート・ソース間に形成された寄生容量Cgs)に蓄積された電荷は、電荷分配により例えばドレイン側からソース側へ流れる(図中のP2参照)。一方、光電変換素子21では暗電流(リーク電流;図中のP3参照)が発生する。このため、オフ動作後の電位Vnは、これらの寄生容量に起因する電荷移動と暗電流との大小関係に応じて更に変動する(電位Vn=Vrst−ΔV)。例えば、暗電流よりも寄生容量による影響が強ければ、電位Vnは上昇し(リセット電位Vrstに近づき)、逆に暗電流による影響がより強い場合には、電位Vnは降下する。

ここで、図18(A)〜(E)に、本実施の形態の比較例に係る撮像駆動動作を表すタイミング波形図を示す。比較例では、本実施の形態と同様の回路構成およびトランジスタを用いて撮像駆動動作がなされる。また、読み出し制御線Lread1,Lread2のそれぞれに対してオン電位Vonおよびオフ電位Voffが印加されるようになっている。但し、比較例では、2回目のリセット動作に際し、電位Vread1,Vread2において、同一のタイミング(t16)でオフ電位Voffからオン電位Vonへ切り替えられ、かつ同一のタイミング(t17)でオン電位Vonからオフ電位Voffへ切り替えられる。

図20(A)〜(E)は、変形例1に係る撮像動作を説明するためのタイミング波形図である。このように、例えば2回目のリセット駆動の際、電位Vread1,Vread2においてオン電位Vonからオフ電位Voffへの切り替えタイミングが異なっていてもよい。例えば、電位Vread2におけるオン電位Vonからオフ電位Voffへの切り替えタイミングが、電位Vread1における上記タイミングよりも相対的に早めてリセット駆動がなされるとよい。具体的には、タイミングt16において電位Vread1,Vread2のそれぞれがオフ電位Voffからオン電位Vonへ切り替えられた後、電位Vread2では、タイミングt17よりも前のタイミングt17aにおいて、オン電位Vonからオフ電位Voffに切り替えられる。この後、タイミングt17では電位Vread1においても、オン電位Vonからオフ電位Voffへの切り替えがなされる。

図22(A)〜(E)は、変形例2に係る撮像動作を説明するためのタイミング波形図である。本変形例では、上記変形例1と同様、2回目のリセット動作の際に、電位Vread1,Vread2としてオン電位(Von1,Von2)が印加される。但し、また、オン電位Von1,Von2からオフ電位Voffへの各切り替えタイミングは、同時となっている。つまり、本変形例では、2回目のリセット動作の際に電位Vread1,Vread2のそれぞれにおけるオン電位Von1,Von2の値が異なっており、例えば、オン電位Von1よりも、オン電位Von2を相対的に小さくして駆動がなされる。具体的には、電位Vread1では、タイミングt16においてオフ電位Voffからオン電位Von1へ切り替えられた後、タイミングt17においてオン電位Von1からオフ電位Voffへ切り替えられる。一方、電位Vread2では、タイミングt16においてオフ電位Voffからオン電位Von2へ切り替えられた後、タイミングt17においてオン電位Von2からオフ電位Voffへ切り替えられる。このような駆動を行うため、本変形例では、読み出し制御線Lread1,Lread2に対し計3値の電位(オン電位Von1,Von2およびオフ電位Voff)を印加可能となっている。

図24(A)〜(E)は、変形例3に係る撮像動作を説明するためのタイミング波形図である。本変形例では、2回目のリセット動作の際に、上記変形例1と同様、電位Vread2のオン電位Von2からオフ電位Voffへの切り替えタイミングを、電位Vread1よりも相対的に早めると共に、上記変形例2と同様、オン電位Von1よりもオン電位Von2を相対的に小さくして駆動がなされる。

図25(A)〜(E)は、変形例4に係る撮像動作を説明するためのタイミング波形図である。上記実施の形態等では、2回目のリセット動作の際に、オン電位Vonからオフ電位Voffへの切り替えタイミングやオン電位Vonの値を異なるようにして駆動がなされる場合について説明したが、このような駆動を1回目のリセット動作時に行ってもよい。例えば、1回目のリセット駆動の際、電位Vread1,Vread2においてオン電位Vonからオフ電位Voffへの切り替えタイミングが異なっていてもよい(電位Vread2のオン電位Vonからオフ電位Voffへの切り替えタイミングが、電位Vread1よりも相対的に早められてもよい)。具体的には、タイミングt13において電位Vread1,Vread2のそれぞれがオフ電位Voffからオン電位Vonへ切り替えられた後、電位Vread2では、タイミングt14よりも前のタイミングt14aにおいて、オン電位Vonからオフ電位Voffに切り替えられる。この後、タイミングt14では電位Vread1においても、オン電位Vonからオフ電位Voffへの切り替えがなされる。

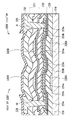

図27は、変形例5に係るトランジスタ(トランジスタ22A)の概略構成を表す断面図である。上記実施の形態では、上述のような読み出し駆動およびリセット駆動を2つのゲート電極を有するトランジスタ(図4に示したトランジスタ22)を用いて行う場合について説明したが、その2つのゲート電極のうち一方がLDD層にオーバーラップしていてもよい。具体的には、トランジスタ22Aは、上記実施の形態のトランジスタ22と同様、基板110上に、第1ゲート電極220A1、第1ゲート絶縁膜229、半導体層226(チャネル層226a,LDD層226b,N+層226c)が設けられている。また、半導体層226上には、第2ゲート絶縁膜230、第2ゲート電極220Bおよび第1層間絶縁膜231が積層されている。第1層間絶縁膜231上には、コンタクトホールH1を埋め込むようにソース・ドレイン電極228が形成され、その上に第2層間絶縁膜232が設けられている。

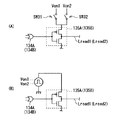

図28は、変形例6に係る画素(画素20A)の回路構成を、上記実施の形態で説明した列選択部17の回路構成例と共に表したものである。本変形例の画素20Aは、実施の形態の画素20と同様にいわゆるパッシブ型の回路構成となっており、1つの光電変換素子21と1つのトランジスタ22とを有している。また、この画素20AにはH方向に沿って延在する読み出し制御線Lread1,Lread2と、V方向に沿って延在する信号線Lsigとが接続されている。

図29は、変形例7に係る画素(画素20D)の回路構成を、上記実施の形態で説明した列選択部17の回路構成例と共に表したものである。本変形例の画素20Dは、実施の形態の画素20と同様にいわゆるパッシブ型の回路構成となっており、1つの光電変換素子21を有しており、H方向に沿って延在する読み出し制御線Lread1,Lread2と、V方向に沿って延在する信号線Lsigとに接続されている。

図31は、変形例8に係る画素(画素20B)の回路構成を、以下説明する列選択部17Bの回路構成例とともに表したものである。また、図32は、変形例9に係る画素(画素20C)の回路構成を、列選択部17Bの回路構成例とともに表したものである。これらの変形例8,9に係る画素20B,20Cはそれぞれ、これまで説明した画素20,20Aとは異なり、いわゆるアクティブ型の画素回路を有している。

図34(A),(B)はそれぞれ、変形例10,11に係る撮像部(撮像部11A,11B)の概略構成を模式的に表したものである。

続いて、上記実施の形態および各変形例(変形例1〜11)に係る撮像装置は、以下に説明するような撮像表示システムへ適用可能である。

(1)各々が光電変換素子と電界効果型のトランジスタとを含む複数の画素を有する撮像部と、前記トランジスタのオン動作およびオフ動作を切り替えることにより、前記画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備え、前記トランジスタが半導体層を間にして第1および第2のゲート電極を有し、前記駆動部は、前記トランジスタの前記第1のゲート電極に第1の電圧、前記第2のゲート電極に第2の電圧をそれぞれ印加することにより、前記オン動作および前記オフ動作を切り替え、かつ前記リセット駆動の際には、前記第1および第2の電圧のそれぞれにおいて、オン電圧およびオフ電圧間の切り替え時期およびオン電圧値のうちの一方または両方が互いに異なるように設定する撮像装置。

(2)前記駆動部は、前記第1の電圧をオン電圧、前記第2の電圧をオフ電圧に保持して前記リセット駆動を行う上記(1)に記載の撮像装置。

(3)前記駆動部は、前記第1の電圧よりも前記第2の電圧におけるオン電圧からオフ電圧への切り替え時期を相対的に早めて前記リセット駆動を行う上記(1)または(2)に記載の撮像装置。

(4)前記駆動部は、前記第1の電圧よりも前記第2の電圧における前記オン電圧値を相対的に小さく設定して前記リセット駆動を行う上記(1)〜(3)のいずれかに記載の撮像装置。

(5)前記駆動部は、前記第1の電圧よりも前記第2の電圧におけるオン電圧からオフ電圧への切り替え時期を相対的に早め、かつ前記第1の電圧よりも前記第2の電圧における前記オン電圧値を相対的に小さく設定して前記リセット駆動を行う上記(1)〜(4)のいずれかに記載の撮像装置。

(6)前記駆動部は、前記リセット駆動を1フレーム期間内で間欠的に複数回行い、前記1フレーム期間内の少なくとも最終回のリセット駆動の際に、前記第1および第2の電圧の前記切り替え時期および前記オン電圧値のうちの一方または両方が異なるように設定する上記(1)〜(5)のいずれかに記載の撮像装置。

(7)前記駆動部による前記読み出し駆動に伴って、前記画素内の信号電荷のリセット動作がなされる上記(1)〜(6)のいずれかに記載の撮像装置。

(8)前記トランジスタでは、前記第1および第2のゲート電極の各ゲート長が互いに異なっている上記(1)〜(7)のいずれかに記載の撮像装置。

(9)前記トランジスタは、それぞれが、前記半導体層と電気的に接続されると共に、ソースまたはドレインとして機能する一対のソース・ドレイン電極を有し、前記半導体層は、活性層と、前記活性層と前記一対のソース・ドレイン電極のそれぞれとの間に形成されたLDD(Lightly Doped Drain)層とを含み、前記第1および第2のゲート電極のうちの一方または両方のゲート電極が、一方のソース・ドレイン電極側に形成されたLDD層にオーバーラップして設けられている上記(8)に記載の撮像装置。

(10)前記第2のゲート電極が、一方のソース・ドレイン電極側に形成されたLDD層にオーバーラップして設けられている上記(9)に記載の撮像装置。

(11)前記光電変換素子が、PIN型のフォトダイオードまたはMIS型センサからなる上記(1)〜(10)のいずれかに記載の撮像装置。

(12)前記撮像部が、入射した放射線に基づいて電気信号を発生させるものである上記(1)〜(11)のいずれかに記載の撮像装置。

(13)前記撮像部は、前記光電変換素子上に、放射線を前記光電変換素子の感度域に変換する波長変換層を有する上記(12)に記載の撮像装置。

(14)前記撮像部は、入射した放射線を直接的に電気信号に変換する光電変換層を有する上記(12)に記載の撮像装置。

(15)前記放射線がX線である上記(12)〜(14)のいずれかに記載の撮像装置。

(16)前記トランジスタの前記半導体層は、アモルファスシリコン、多結晶シリコン、微結晶シリコンまたは酸化物半導体よりなる上記(1)〜(15)のいずれかに記載の撮像装置。

(17)撮像装置と、この撮像装置により得られた撮像信号に基づく画像表示を行う表示装置とを備え、前記撮像装置は、各々が光電変換素子と電界効果型のトランジスタとを含む複数の画素を有する撮像部と、前記トランジスタのオン動作およびオフ動作を切り替えることにより、前記画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備え、前記トランジスタが半導体層を間にして第1および第2のゲート電極を有し、前記駆動部は、前記トランジスタの前記第1のゲート電極に第1の電圧、前記第2のゲート電極に第2の電圧をそれぞれ印加することにより、前記オン動作および前記オフ動作を切り替え、かつ前記リセット駆動の際には、前記第1および第2の電圧のそれぞれにおいて、オン電圧およびオフ電圧間の切り替え時期およびオン電圧値のうちの一方または両方が互いに異なるように設定する撮像表示システム。

Claims (16)

- 各々が光電変換素子と電界効果型のトランジスタとを含む複数の画素を有する撮像部と、

前記トランジスタのオン動作およびオフ動作を切り替えることにより、前記画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備え、

前記トランジスタが半導体層を間にして第1および第2のゲート電極を有し、

前記駆動部は、

前記トランジスタの前記第1のゲート電極に第1の電圧、前記第2のゲート電極に第2の電圧をそれぞれ印加することにより、前記オン動作および前記オフ動作を切り替え、かつ

前記リセット駆動の際には、前記第1および第2の電圧のそれぞれにおいて、オン電圧からオフ電圧への切り替え時期が互いに異なるように設定する

撮像装置。 - 前記駆動部は、前記第1の電圧よりも前記第2の電圧におけるオン電圧からオフ電圧への切り替え時期を相対的に早めて前記リセット駆動を行う

請求項1に記載の撮像装置。 - 前記駆動部は、前記第1および第2の電圧において、オフ電圧からオン電圧への切り替えを同期して、前記リセット駆動を行う

請求項2に記載の撮像装置。 - 前記駆動部は、前記第1の電圧よりも前記第2の電圧における前記オン電圧値を相対的に小さく設定して前記リセット駆動を行う

請求項1ないし請求項3のいずれか1つに記載の撮像装置。 - 前記駆動部は、

前記リセット駆動を1フレーム期間内で間欠的に複数回行い、

前記1フレーム期間内の少なくとも最終回のリセット駆動の際に、前記切り替え時期が異なるように設定する

請求項1ないし請求項4のいずれか1つに記載の撮像装置。 - 前記駆動部による前記読み出し駆動に伴って、前記画素内の信号電荷のリセットがなされる

請求項1ないし請求項5のいずれか1つに記載の撮像装置。 - 前記トランジスタでは、前記第1および第2のゲート電極の各ゲート長が互いに異なっている

請求項1ないし請求項6のいずれか1つに記載の撮像装置。 - 前記トランジスタは、それぞれが、前記半導体層と電気的に接続されると共に、ソースまたはドレインとして機能する一対のソース・ドレイン電極を有し、

前記半導体層は、

活性層と、

前記活性層と前記一対のソース・ドレイン電極のそれぞれとの間に形成されたLDD(Lightly Doped Drain)層とを含み、

前記第1および第2のゲート電極のうちの一方または両方のゲート電極が、一方のソース・ドレイン電極側に形成されたLDD層にオーバーラップして設けられている

請求項7に記載の撮像装置。 - 前記第2のゲート電極が、一方のソース・ドレイン電極側に形成されたLDD層にオーバーラップして設けられている

請求項8に記載の撮像装置。 - 前記光電変換素子が、PIN型のフォトダイオードまたはMIS型センサからなる

請求項1ないし請求項9のいずれか1つに記載の撮像装置。 - 前記撮像部が、入射した放射線に基づいて電気信号を発生させるものである

請求項1ないし請求項9のいずれか1つに記載の撮像装置。 - 前記撮像部は、前記光電変換素子上に、放射線を前記光電変換素子の感度域に変換する波長変換層を有する

請求項10に記載の撮像装置。 - 前記撮像部は、入射した放射線を吸収して電気信号に変換する光電変換層を有する

請求項11に記載の撮像装置。 - 前記放射線がX線である

請求項11ないし請求項13のいずれか1つに記載の撮像装置。 - 前記トランジスタの前記半導体層は、アモルファスシリコン、多結晶シリコン、微結晶シリコンまたは酸化物半導体よりなる

請求項1ないし請求項14のいずれか1つに記載の撮像装置。 - 撮像装置と、この撮像装置により得られた撮像信号に基づく画像表示を行う表示装置とを備え、

前記撮像装置は、

各々が光電変換素子と電界効果型のトランジスタとを含む複数の画素を有する撮像部と、

前記トランジスタのオン動作およびオフ動作を切り替えることにより、前記画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備え、

前記トランジスタが半導体層を間にして第1および第2のゲート電極を有し、

前記駆動部は、

前記トランジスタの前記第1のゲート電極に第1の電圧、前記第2のゲート電極に第2の電圧をそれぞれ印加することにより、前記オン動作および前記オフ動作を切り替え、かつ

前記リセット駆動の際には、前記第1および第2の電圧のそれぞれにおいて、オン電圧からオフ電圧への切り替え時期が互いに異なるように設定する

撮像表示システム。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011231768A JP5935287B2 (ja) | 2011-10-21 | 2011-10-21 | 撮像装置および撮像表示システム |

| US13/650,799 US8928773B2 (en) | 2011-10-21 | 2012-10-12 | Image pickup unit and image pickup display system |

| CN201210394884.4A CN103067667B (zh) | 2011-10-21 | 2012-10-15 | 图像拍摄单元和图像拍摄显示系统 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011231768A JP5935287B2 (ja) | 2011-10-21 | 2011-10-21 | 撮像装置および撮像表示システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013090274A JP2013090274A (ja) | 2013-05-13 |

| JP2013090274A5 JP2013090274A5 (ja) | 2014-11-06 |

| JP5935287B2 true JP5935287B2 (ja) | 2016-06-15 |

Family

ID=48110108

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011231768A Expired - Fee Related JP5935287B2 (ja) | 2011-10-21 | 2011-10-21 | 撮像装置および撮像表示システム |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8928773B2 (ja) |

| JP (1) | JP5935287B2 (ja) |

| CN (1) | CN103067667B (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013084947A1 (ja) * | 2011-12-07 | 2013-06-13 | シャープ株式会社 | 光センサ回路の動作方法、および、当該光センサ回路を備えた表示装置の動作方法 |

| JP5895504B2 (ja) | 2011-12-15 | 2016-03-30 | ソニー株式会社 | 撮像パネルおよび撮像処理システム |

| JP6126470B2 (ja) * | 2013-06-12 | 2017-05-10 | ソニーセミコンダクタソリューションズ株式会社 | 放射線撮像装置および放射線撮像表示システム |

| JP6198485B2 (ja) * | 2013-06-28 | 2017-09-20 | キヤノン株式会社 | 光電変換装置、及び撮像システム |

| CN103686004B (zh) * | 2013-12-11 | 2017-02-08 | 格科微电子(上海)有限公司 | 列并行模数转换器、像素感光值输出方法及cmos图像传感器 |

| WO2015141777A1 (ja) * | 2014-03-20 | 2015-09-24 | シャープ株式会社 | 光検出装置 |

| TWI700823B (zh) * | 2014-06-27 | 2020-08-01 | 日商半導體能源研究所股份有限公司 | 攝像裝置及電子裝置 |

| JP6395482B2 (ja) * | 2014-07-11 | 2018-09-26 | キヤノン株式会社 | 光電変換装置、および、撮像システム |

| JP2016021445A (ja) | 2014-07-11 | 2016-02-04 | キヤノン株式会社 | 光電変換装置、および、撮像システム |

| JP6494207B2 (ja) * | 2014-07-31 | 2019-04-03 | キヤノン株式会社 | 光電変換装置、光電変換システム、光電変換装置の駆動方法 |

| JP6425448B2 (ja) | 2014-07-31 | 2018-11-21 | キヤノン株式会社 | 光電変換装置、および、撮像システム |

| US9685476B2 (en) * | 2015-04-03 | 2017-06-20 | Semiconductor Energy Laboratory Co., Ltd. | Imaging device and electronic device |

| CN107018338B (zh) | 2016-01-22 | 2021-01-29 | 松下知识产权经营株式会社 | 摄像装置 |

| EP3571531A4 (en) | 2017-01-23 | 2020-08-05 | Shenzhen Xpectvision Technology Co., Ltd. | X-RAY DETECTORS CAPABLE OF IDENTIFYING AND MANAGING LOAD SHARING |

| KR20220022019A (ko) * | 2020-08-14 | 2022-02-23 | 삼성디스플레이 주식회사 | 입력 감지 방법 및 이를 포함하는 입력 감지 장치 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0590586A (ja) * | 1991-09-30 | 1993-04-09 | Nec Corp | 薄膜トランジスタ |

| JP3885222B2 (ja) * | 1999-11-10 | 2007-02-21 | カシオ計算機株式会社 | フォトセンサシステムの駆動制御方法 |

| JP5016746B2 (ja) * | 2000-07-28 | 2012-09-05 | キヤノン株式会社 | 撮像装置及びその駆動方法 |

| JP4147094B2 (ja) * | 2002-11-22 | 2008-09-10 | キヤノン株式会社 | 放射線撮像装置及び放射線撮像システム |

| JP4266656B2 (ja) * | 2003-02-14 | 2009-05-20 | キヤノン株式会社 | 固体撮像装置及び放射線撮像装置 |

| JP4342191B2 (ja) * | 2003-02-14 | 2009-10-14 | シャープ株式会社 | 薄膜トランジスタを備えた装置及びその製造方法 |

| KR100890152B1 (ko) * | 2006-12-22 | 2009-03-20 | 매그나칩 반도체 유한회사 | Cmos 이미지 센서를 위한, 작은 크기, 높은 이득 및낮은 노이즈의 픽셀 |

| US7918420B2 (en) * | 2007-07-17 | 2011-04-05 | The Boeing Company | System and methods for simultaneous momentum dumping and orbit control |

| US8063964B2 (en) * | 2007-11-20 | 2011-11-22 | Altasens, Inc. | Dual sensitivity image sensor |

| JP4538528B2 (ja) * | 2008-12-26 | 2010-09-08 | 廣津 和子 | 固体撮像素子 |

| JP5721994B2 (ja) * | 2009-11-27 | 2015-05-20 | 株式会社ジャパンディスプレイ | 放射線撮像装置 |

-

2011

- 2011-10-21 JP JP2011231768A patent/JP5935287B2/ja not_active Expired - Fee Related

-

2012

- 2012-10-12 US US13/650,799 patent/US8928773B2/en not_active Expired - Fee Related

- 2012-10-15 CN CN201210394884.4A patent/CN103067667B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013090274A (ja) | 2013-05-13 |

| US20130100330A1 (en) | 2013-04-25 |

| CN103067667B (zh) | 2017-09-12 |

| US8928773B2 (en) | 2015-01-06 |

| CN103067667A (zh) | 2013-04-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5935287B2 (ja) | 撮像装置および撮像表示システム | |

| JP5874670B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935284B2 (ja) | 撮像装置および撮像表示システム | |

| JP5853486B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935286B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935285B2 (ja) | 撮像装置および撮像表示システム | |

| JP5999921B2 (ja) | 撮像装置および撮像表示システム | |

| JP6152729B2 (ja) | 撮像装置および撮像表示システム | |

| JP2013090274A5 (ja) | ||

| CN102820337A (zh) | 放射线摄像装置、放射线摄像显示系统和晶体管 | |

| US7566878B2 (en) | Radiation image detector | |

| JP5895650B2 (ja) | 撮像装置および撮像表示システム | |

| JP2013247270A (ja) | 撮像装置および撮像表示システム | |

| JP5935293B2 (ja) | 撮像装置および撮像表示システム | |

| JP2015023080A (ja) | 放射線撮像装置および放射線撮像表示システム | |

| JP6166128B2 (ja) | 放射線撮像装置および放射線撮像表示システム | |

| JP5884384B2 (ja) | 撮像装置および撮像表示システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140917 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140917 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150910 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151007 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151113 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160412 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160425 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5935287 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |