JP5935285B2 - 撮像装置および撮像表示システム - Google Patents

撮像装置および撮像表示システム Download PDFInfo

- Publication number

- JP5935285B2 JP5935285B2 JP2011229996A JP2011229996A JP5935285B2 JP 5935285 B2 JP5935285 B2 JP 5935285B2 JP 2011229996 A JP2011229996 A JP 2011229996A JP 2011229996 A JP2011229996 A JP 2011229996A JP 5935285 B2 JP5935285 B2 JP 5935285B2

- Authority

- JP

- Japan

- Prior art keywords

- reset

- imaging

- voltage

- period

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000003384 imaging method Methods 0.000 title claims description 185

- 238000006243 chemical reaction Methods 0.000 claims description 91

- 230000005855 radiation Effects 0.000 claims description 26

- 239000004065 semiconductor Substances 0.000 claims description 26

- 230000005669 field effect Effects 0.000 claims description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 5

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 4

- 229910021424 microcrystalline silicon Inorganic materials 0.000 claims description 3

- 230000035945 sensitivity Effects 0.000 claims description 3

- 230000004048 modification Effects 0.000 description 37

- 238000012986 modification Methods 0.000 description 37

- 238000010586 diagram Methods 0.000 description 33

- 238000002347 injection Methods 0.000 description 21

- 239000007924 injection Substances 0.000 description 21

- 238000009825 accumulation Methods 0.000 description 14

- 230000003071 parasitic effect Effects 0.000 description 9

- 230000007704 transition Effects 0.000 description 9

- 230000000052 comparative effect Effects 0.000 description 6

- 101150105133 RRAD gene Proteins 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 239000010408 film Substances 0.000 description 5

- 230000007423 decrease Effects 0.000 description 4

- 206010047571 Visual impairment Diseases 0.000 description 3

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 238000007599 discharging Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 229920006395 saturated elastomer Polymers 0.000 description 3

- 239000000758 substrate Substances 0.000 description 3

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 description 2

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 2

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 description 2

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 101100313728 Vitis vinifera VINST1 gene Proteins 0.000 description 2

- RPPBZEBXAAZZJH-UHFFFAOYSA-N cadmium telluride Chemical compound [Te]=[Cd] RPPBZEBXAAZZJH-UHFFFAOYSA-N 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 230000003111 delayed effect Effects 0.000 description 2

- 238000007689 inspection Methods 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 239000011669 selenium Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229910004261 CaF 2 Inorganic materials 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 206010034972 Photosensitivity reaction Diseases 0.000 description 1

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000005260 alpha ray Effects 0.000 description 1

- 230000005250 beta ray Effects 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 230000005251 gamma ray Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000036211 photosensitivity Effects 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000002601 radiography Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 229910052711 selenium Inorganic materials 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/30—Transforming light or analogous information into electric information

- H04N5/32—Transforming X-rays

-

- A—HUMAN NECESSITIES

- A61—MEDICAL OR VETERINARY SCIENCE; HYGIENE

- A61B—DIAGNOSIS; SURGERY; IDENTIFICATION

- A61B6/00—Apparatus or devices for radiation diagnosis; Apparatus or devices for radiation diagnosis combined with radiation therapy equipment

- A61B6/42—Arrangements for detecting radiation specially adapted for radiation diagnosis

- A61B6/4208—Arrangements for detecting radiation specially adapted for radiation diagnosis characterised by using a particular type of detector

- A61B6/4233—Arrangements for detecting radiation specially adapted for radiation diagnosis characterised by using a particular type of detector using matrix detectors

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/30—Circuitry of solid-state image sensors [SSIS]; Control thereof for transforming X-rays into image signals

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/57—Control of the dynamic range

- H04N25/58—Control of the dynamic range involving two or more exposures

- H04N25/581—Control of the dynamic range involving two or more exposures acquired simultaneously

- H04N25/583—Control of the dynamic range involving two or more exposures acquired simultaneously with different integration times

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/62—Detection or reduction of noise due to excess charges produced by the exposure, e.g. smear, blooming, ghost image, crosstalk or leakage between pixels

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/62—Detection or reduction of noise due to excess charges produced by the exposure, e.g. smear, blooming, ghost image, crosstalk or leakage between pixels

- H04N25/626—Reduction of noise due to residual charges remaining after image readout, e.g. to remove ghost images or afterimages

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/71—Charge-coupled device [CCD] sensors; Charge-transfer registers specially adapted for CCD sensors

- H04N25/75—Circuitry for providing, modifying or processing image signals from the pixel array

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/78—Readout circuits for addressed sensors, e.g. output amplifiers or A/D converters

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Health & Medical Sciences (AREA)

- Life Sciences & Earth Sciences (AREA)

- Medical Informatics (AREA)

- Physics & Mathematics (AREA)

- Pathology (AREA)

- Molecular Biology (AREA)

- Biophysics (AREA)

- Nuclear Medicine, Radiotherapy & Molecular Imaging (AREA)

- Optics & Photonics (AREA)

- Mathematical Physics (AREA)

- Radiology & Medical Imaging (AREA)

- Biomedical Technology (AREA)

- Heart & Thoracic Surgery (AREA)

- High Energy & Nuclear Physics (AREA)

- Surgery (AREA)

- Animal Behavior & Ethology (AREA)

- General Health & Medical Sciences (AREA)

- Public Health (AREA)

- Veterinary Medicine (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Measurement Of Radiation (AREA)

Description

1.実施の形態(1回目のリセット駆動時のゲート電圧よりも2回目のリセット駆動時のゲート電圧を低くして撮像動作を行う撮像装置の例)

2.変形例1(2回目のゲート電圧を段階的に低くした例)

3.変形例2(パッシブ型の画素回路の他の例)

4.変形例3(パッシブ型の画素回路の他の例)

5.変形例4,5(アクティブ型の画素回路の例)

6.変形例6,7(放射線に基づいて撮像を行う撮像部の例)

7.適用例(撮像表示システムへの適用例)

[撮像装置1の全体構成]

図1は、本開示の一実施の形態に係る撮像装置(撮像装置1)の全体のブロック構成を表すものである。撮像装置1は、入射光(撮像光)に基づいて被写体の情報を読み取る(被写体を撮像する)ものである。この撮像装置1は、撮像部11、行走査部13、A/D変換部14、列走査部15およびシステム制御部16を備えている。これらのうち、行走査部13、A/D変換部14、列走査部15およびシステム制御部16が、本開示における「駆動部」の一具体例に対応する。

撮像部11は、入射光(撮像光)に応じて電気信号を発生させるものである。この撮像部11では、画素(撮像画素,単位画素)20が、行列状(マトリクス状)に2次元配置されており、各画素20は、撮像光の光量に応じた電荷量の光電荷を発生して内部に蓄積する光電変換素子(後述の光電変換素子21)を有している。尚、図1中に示したように、以下、撮像部11内における水平方向(行方向)を「H」方向とし、垂直方向(列方向)を「V」方向として説明する。

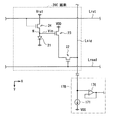

行走査部13は、後述のシフトレジスタ回路や所定の論理回路等を含んで構成されており、撮像部11内の複数の画素20に対して行単位(水平ライン単位)での駆動(線順次走査)を行う画素駆動部(行走査回路)である。具体的には、後述する読み出し動作やリセット動作等の撮像動作を例えば線順次走査により行う。尚、この線順次走査は、読み出し制御線Lreadを介して前述した行走査信号を各画素20へ供給することによって行われるようになっている。

A/D変換部14は、複数(ここでは4つ)の信号線Lsigごとに1つ設けられた複数の列選択部17を有しており、信号線Lsigを介して入力した信号電圧(信号電荷)に基づいてA/D変換(アナログ/デジタル変換)を行うものである。これにより、デジタル信号からなる出力データDout(撮像信号)が生成され、外部へ出力されるようになっている。

列走査部15は、例えば図示しないシフトレジスタやアドレスデコーダ等を含んで構成されており、上記した列選択部17内の各スイッチSW2を走査しつつ順番に駆動するものである。このような列走査部15による選択走査によって、信号線Lsigの各々を介して読み出された各画素20の信号(上記した出力データDout)が、順番に外部へ出力されるようになっている。

システム制御部16は、行走査部13、A/D変換部14および列走査部15の動作を制御するものである。具体的には、システム制御部16は、前述した各種のタイミング信号(制御信号)を生成するタイミングジェネレータを有しており、このタイミングジェネレータにおいて生成される各種のタイミング信号を基に、行走査部13、A/D変換部14および列走査部15の駆動制御を行う。このシステム制御部16の制御に基づいて、行走査部13、A/D変換部14および列走査部15がそれぞれ撮像部11内の複数の画素20に対する撮像駆動(線順次撮像駆動)を行うことにより、撮像部11から出力データDoutが取得されるようになっている。

本実施の形態の撮像装置1では、撮像光Linが撮像部11へ入射すると、各画素20内の光電変換素子21では、この撮像光Linが信号電荷に変換(光電変換)される。このとき、蓄積ノードNでは、光電変換により発生した信号電荷の蓄積によって、ノード容量に応じた電圧変化が生じる。具体的には、蓄積ノード容量をCs、発生した信号電荷をqとすると、蓄積ノードNでは(q/Cs)の分だけ電圧が変化(ここでは低下)する。このような電圧変化に応じて、トランジスタ22のドレインには入力電圧Vin(信号電荷に対応した電圧)が印加される。このトランジスタ22へ供給される入力電圧Vinは、読み出し制御線Lreadから供給される行走査信号に応じてトランジスタ22がオン状態になると、蓄積ノードNに蓄積された信号電荷が画素20から信号線Lsigへ読み出される。

図7(A),(B)は、露光期間および読み出し期間における画素20および列選択部17内のチャージアンプ回路の動作例を表したものである。尚、以下では説明の便宜上、トランジスタ22のオン・オフ状態を、スイッチを用いて図示している。

上述のように、読み出し/第1リセット期間Tr1では、読み出し動作に伴ってリセット動作がなされるが、この期間Tr1後であっても、それ以前に蓄積されていた信号電荷の一部が画素20内に残存(残留)する場合がある。信号電荷の一部が画素20内に残ると、次の読み出し動作時(次のフレーム期間での撮像時)においてその残留電荷に起因した残像が発生し、撮像画質が劣化してしまう。以下、図8〜図12を参照して、このような信号電荷の残存について、詳細に説明する。

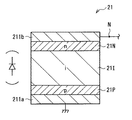

上記のような信号電荷の残存が発生する理由の一つとして、外光(特に、強外光)の影響を受けて画素20内の電荷が飽和してしまうことが考えられる。光電変換素子21では、ゲート電極21Gに印加されるゲート電圧により、真性半導体層21Iが、蓄積状態(飽和状態)、空乏状態、反転状態のいずれかの状態となる。ところが、薄膜フォトダイオードでは、その蓄積状態もしくは反転状態においてゲート電極21G側の界面に電荷が誘起された状態(図8(A))から、空乏状態(図8(B))に遷移するには、数百μsオーダーの時間が必要である。通常、PIN型のフォトダイオードは、空乏状態で光感度が最大となるため空乏状態で使用するが、例えば強外光が照射されてVnp<0Vの状態になると、蓄積状態に遷移する。尚、Vnpは、p型半導体層21P側から見たn型半導体層21Nの電位である。

そこで本実施の形態では、複数回(ここでは、上記読み出し/第1リセット期間Tr1におけるリセット動作を含む計2回)のリセット動作が行われる。また、読み出し駆動およびリセット駆動は、後述するように線順次でなされ、詳細には読み出し駆動および複数回のリセット駆動が単一の線順次駆動によってなされる。これにより、上記残留電荷を低減し、この残留電荷に起因して生じる残像を抑えるようにしている。具体的には、図13に示したように、1垂直期間(1フレーム期間)ΔTvにおいて、露光期間Tex後、期間Tr1において読み出し動作および1回目のリセット動作がなされた後、所定の時間間隔後の第2リセット期間Tr2において2回目のリセット動作(第2リセット動作)がなされる。また、これらのうち、期間Tr1,Tr2における読み出し動作およびリセット動作の各動作はそれぞれ線順次に行われる(システム制御部16の制御に基づいて、各画素20では、線順次読み出し駆動および線順次リセット駆動がなされる)。

図14〜図17に、線順次撮像駆動(線順次読み出し駆動および線順次リセット駆動)の際の各動作のタイミングの一例について示す。図14は、本実施の形態に係る線順次撮像駆動の一例を、タイミング波形図で表わしたものである。ここで、(A)〜(F)はそれぞれ、読み出し制御線Lread(1)〜Lread(3),Lread(n-2)〜Lread(n)の電位Vread(1)〜Vread(3),Vread(n-2)〜Vread(n)のタイミング波形を示している。また、図中に示したΔThは、1水平期間(1水平走査期間)を表している。図15〜図17ではそれぞれ、前述したアンプリセット制御線Lcarstの電位Vcarstを、前述した第1の動作例の場合(各図の(D))および第2の動作例の場合(各図の(E))の各々について示している。

第2リセット期間Tr2では、具体的には、例えば図19(A)に示した第1の動作例のようにして、2回目のリセット動作が行われる。即ち、画素20内のトランジスタ22がオン状態になると共に、チャージアンプ回路におけるスイッチSW1もオン状態となっている。これにより、チャージアンプ172を用いたボルテージフォロワ回路が形成されている。このため、チャージアンプ172では、その帰還特性(フィードバック特性)により、負側の入力端子側(信号線Lsig側)の電圧が、正側の入力端子に印加されているリセット電圧Vrstに略等しくなる。このように第1の動作例では、チャージアンプ172における帰還特性を利用して、画素20内の蓄積ノードNの電位Vnがリセット電圧Vrstに変位する(2回目のリセット動作がなされる)。

上述のように、複数回のリセット動作がなされることにより、残留電荷を抑制して残像発生を低減することができるが、この残留電荷排出のためのリセット駆動に伴って、いわゆるチャージインジェクションと呼ばれる新たな現象が生じる。即ち、画素20内の蓄積ノードNでは、上述のように読み出し/第1リセット期間Tr1後に所定のリセット電圧Vrstとなるが、この後、トランジスタ22がオン状態からオフ状態に遷移する。この際、例えば図21に示したように、画素20内の寄生容量(トランジスタ22のゲート・チャネル間に形成されたゲート容量Cgc(図示せず),ゲート・ドレイン間に形成された寄生容量Cgd)に蓄積された電荷に起因して、蓄積ノードNの電位がリセット電圧Vrstから微小に変動する(図中のP2参照)。ここでは、蓄積ノードNが光電変換素子21のカソード側に接続されていることから、電位Vnがリセット電位Vrstから所定の電位分、降下する(図18(D)中の矢印X1)。このようなチャージインジェクションの発生は、撮像データDoutにおいてノイズとなり画質劣化を招くことから、できるだけ低減されることが望ましい。

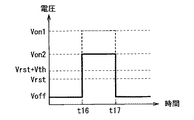

ここで、図22(A)〜(E)に、本実施の形態の比較例に係る撮像駆動動作を表すタイミング波形図を示す。比較例では、本実施の形態と同様の回路構成を用いて撮像駆動動作がなされる。また、読み出し制御線Lreadに対して2値(オン電位Von1およびオフ電位Voff)の電圧パルスが印加されるようになっている。この比較例では、1回目および2回目のいずれのリセット動作に際しても、電位Vreadにおいて、オン電位Von1が印加される。具体的には、タイミングt13〜t14およびタイミングt16〜t17の各期間において、同一のオン電位Vonが印加される。

図24は、変形例1に係る撮像動作を説明するためのタイミング波形図である。このように、例えば2回目のリセット駆動の際、段階的に電圧を切り替える(段階的に電圧が低くなる)ように設定してもよい。換言すると、第2リセット期間Tr2の一部の期間において、オン電位Von1よりも低いオン電位Von2が印加される。具体的には、上述した第2リセット期間Tr2において、タイミングt16に、電位Vreadをオフ電位Voffからオン電位Von1へ切り替え、続くタイミングt16aにおいて、オン電位Von1からこれよりも低いオン電位Von2へ切り替え、更に続くタイミングt16bに、そのオン電位Von2からオフ電位Voffへの切り替えを行う。尚、図24では、1回目のリセット動作の際の電圧波形に対応する部分を破線で示し、2回目のリセット動作の際の電圧波形に対応する部分を実線で示している。

図25は、変形例2に係る画素(画素20A)の回路構成を、上記実施の形態で説明した列選択部17の回路構成例と共に表したものである。本変形例の画素20Aは、実施の形態の画素20と同様にいわゆるパッシブ型の回路構成となっており、1つの光電変換素子21と1つのトランジスタ22とを有している。また、この画素20AにはH方向に沿って延在する読み出し制御線Lreadと、V方向に沿って延在する信号線Lsigとが接続されている。

図26は、変形例3に係る画素(画素20D)の回路構成を、上記実施の形態で説明した列選択部17の回路構成例と共に表したものである。本変形例の画素20Dは、実施の形態の画素20と同様にいわゆるパッシブ型の回路構成となっており、1つの光電変換素子21を有しており、H方向に沿って延在する読み出し制御線Lreadと、V方向に沿って延在する信号線Lsigとに接続されている。

図27は、変形例4に係る画素(画素20B)の回路構成を、以下説明する列選択部17Bの回路構成例とともに表したものである。また、図28は、変形例5に係る画素(画素20C)の回路構成を、列選択部17Bの回路構成例とともに表したものである。これらの変形例4,5に係る画素20B,20Cはそれぞれ、これまで説明した画素20,20Aとは異なり、いわゆるアクティブ型の画素回路を有している。

図30(A),(B)はそれぞれ、変形例6,7に係る撮像部(撮像部11A,11B)の概略構成を模式的に表したものである。

続いて、上記実施の形態および各変形例(変形例1〜7)に係る撮像装置は、以下に説明するような撮像表示システムへ適用可能である。

(1)各々が光電変換素子と電界効果型のトランジスタとを含む複数の画素を有する撮像部と、前記トランジスタを用いて前記画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備え、前記駆動部は、前記リセット駆動を1フレーム期間内で間欠的に複数回行い、前記トランジスタに対し、1フレーム期間内の少なくとも1回のリセット期間にわたってまたはその一部の期間において、他の回のリセット期間に印加される第1の電圧よりも低い第2の電圧を印加して前記トランジスタのオン動作を行う撮像装置。

(2)前記駆動部は、少なくとも最終回のリセット駆動の際に、前記トランジスタに対して前記第2の電圧を印加する上記(1)に記載の撮像装置。

(3)前記駆動部は、前記第2の電圧を時系列に沿って段階的に低くなるように設定する上記(1)または(2)に記載の撮像装置。

(4)前記第2の電圧の印加期間は前記第1の電圧の印加期間よりも短い上記(3)に記載の撮像装置。

(5)前記第2の電圧は、前記トランジスタの閾値電圧よりも大きい上記(1)〜(4)のいずれかに記載の撮像装置。

(6)前記駆動部は、前記読み出し駆動に伴って、1フレーム期間内の1回目のリセット駆動を前記第1の電圧を用いて行い、最終回のリセット駆動の際に前記第2の電圧を用いる上記(1)〜(5)のいずれかに記載の撮像装置。

(7)前記光電変換素子が、PIN型のフォトダイオードまたはMIS型センサからなる上記(1)〜(6)のいずれかに記載の撮像装置。

(8)前記撮像部が、入射した放射線に基づいて電気信号を発生させるものである上記(1)〜(7)のいずれかに記載の撮像装置。

(9)前記撮像部は、前記光電変換素子上に、放射線を前記光電変換素子の感度域に変換する波長変換層を有する上記(8)に記載の撮像装置。

(10)前記放射線がX線である上記(9)に記載の撮像装置。

(11)前記トランジスタの前記半導体層は、アモルファスシリコン、多結晶シリコン、微結晶シリコンまたは酸化物半導体よりなる上記(1)〜(10)のいずれかに記載の撮像装置。

(12)撮像装置と、この撮像装置により得られた撮像信号に基づく画像表示を行う表示装置とを備え、前記撮像装置は、各々が光電変換素子と電界効果型のトランジスタとを含む複数の画素を有する撮像部と、前記トランジスタを用いて前記画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備え、前記駆動部は、前記リセット駆動を1フレーム期間内で間欠的に複数回行い、前記トランジスタに対し、1フレーム期間内の少なくとも1回のリセット期間にわたってまたはその一部の期間において、他の回のリセット期間に印加される第1の電圧よりも低い第2の電圧を印加して前記トランジスタのオン動作を行う撮像表示システム。

Claims (12)

- 各々が光電変換素子と電界効果型のトランジスタとを含む複数の画素を有する撮像部と、

前記トランジスタを用いて前記画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備え、

前記駆動部は、

前記リセット駆動を1フレーム期間内で間欠的に複数回行い、

前記トランジスタに対し、1フレーム期間における複数回のリセット期間のうち第1のリセット期間には第1の電圧を印加すると共に、前記第1のリセット期間とは異なる第2のリセット期間には、前記第1の電圧よりも低い第2の電圧を含む2以上の電圧を段階的に切り替えて印加して前記トランジスタのオン動作を行う

撮像装置。 - 前記駆動部は、少なくとも最終回のリセット駆動の際に、前記トランジスタに対して前記第2の電圧を印加する

請求項1に記載の撮像装置。 - 前記第2の電圧の印加期間は前記第1の電圧の印加期間よりも短い

請求項1または2に記載の撮像装置。 - 前記第2のリセット期間において、前記第1の電圧を印加した後に前記第2の電圧を印加する

請求項1ないし請求項3のいずれか1つに記載の撮像装置。 - 前記第2の電圧は、前記トランジスタの閾値電圧よりも大きい

請求項1ないし請求項4のいずれか1つに記載の撮像装置。 - 前記駆動部は、

前記読み出し駆動に伴って、1フレーム期間内の1回目のリセット駆動を前記第1の電圧を用いて行い、

最終回のリセット駆動の際に前記第2の電圧を用いる

請求項1ないし請求項5のいずれか1つに記載の撮像装置。 - 前記光電変換素子が、PIN型のフォトダイオードまたはMIS型センサからなる

請求項1ないし請求項6のいずれか1つに記載の撮像装置。 - 前記撮像部が、入射した放射線に基づいて電気信号を発生させるものである

請求項1ないし請求項6のいずれか1つに記載の撮像装置。 - 前記撮像部は、前記光電変換素子上に、放射線を前記光電変換素子の感度域に変換する波長変換層を有する

請求項1ないし請求項7のいずれか1つに記載の撮像装置。 - 前記放射線がX線である

請求項8または請求項9に記載の撮像装置。 - 前記トランジスタの前記半導体層は、アモルファスシリコン、多結晶シリコン、微結晶シリコンまたは酸化物半導体よりなる

請求項1ないし請求項10のいずれか1つに記載の撮像装置。 - 撮像装置と、この撮像装置により得られた撮像信号に基づく画像表示を行う表示装置とを備え、

前記撮像装置は、

各々が光電変換素子と電界効果型のトランジスタとを含む複数の画素を有する撮像部と、

前記トランジスタを用いて前記画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備え、

前記駆動部は、

前記リセット駆動を1フレーム期間内で間欠的に複数回行い、

前記トランジスタに対し、1フレーム期間における複数回のリセット期間のうち第1のリセット期間には第1の電圧を印加すると共に、前記第1のリセット期間とは異なる第2のリセット期間には、前記第1の電圧よりも低い第2の電圧を含む2以上の電圧を段階的に切り替えて印加して前記トランジスタのオン動作を行う

撮像表示システム。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011229996A JP5935285B2 (ja) | 2011-10-19 | 2011-10-19 | 撮像装置および撮像表示システム |

| CN201210411303.3A CN103067668B (zh) | 2011-10-19 | 2012-10-12 | 图像拍摄单元和图像拍摄显示系统 |

| US13/650,328 US9019425B2 (en) | 2011-10-19 | 2012-10-12 | Image pickup unit and image pickup display system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011229996A JP5935285B2 (ja) | 2011-10-19 | 2011-10-19 | 撮像装置および撮像表示システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013090207A JP2013090207A (ja) | 2013-05-13 |

| JP2013090207A5 JP2013090207A5 (ja) | 2014-11-06 |

| JP5935285B2 true JP5935285B2 (ja) | 2016-06-15 |

Family

ID=48110109

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011229996A Expired - Fee Related JP5935285B2 (ja) | 2011-10-19 | 2011-10-19 | 撮像装置および撮像表示システム |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9019425B2 (ja) |

| JP (1) | JP5935285B2 (ja) |

| CN (1) | CN103067668B (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5935284B2 (ja) | 2011-10-18 | 2016-06-15 | ソニー株式会社 | 撮像装置および撮像表示システム |

| WO2013084947A1 (ja) * | 2011-12-07 | 2013-06-13 | シャープ株式会社 | 光センサ回路の動作方法、および、当該光センサ回路を備えた表示装置の動作方法 |

| JP5895504B2 (ja) | 2011-12-15 | 2016-03-30 | ソニー株式会社 | 撮像パネルおよび撮像処理システム |

| CN104301640B (zh) * | 2014-08-30 | 2017-10-03 | 中国科学院长春光学精密机械与物理研究所 | 一种nmos线阵图像传感器的高效时序驱动方法 |

| CN104219467B (zh) * | 2014-08-30 | 2018-09-14 | 中国科学院长春光学精密机械与物理研究所 | 一种nmos线阵图像传感器 |

| CN108777771B (zh) * | 2014-09-10 | 2020-12-25 | 原相科技股份有限公司 | 图像感测器及成像系统的运作方法 |

| CN105182396B (zh) * | 2015-06-29 | 2018-04-24 | 苏州瑞派宁科技有限公司 | 一种探测器信号读出的通道复用方法 |

| JP2018082295A (ja) | 2016-11-16 | 2018-05-24 | キヤノン株式会社 | 撮像装置及び撮像システム |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001135561A (ja) | 1999-11-05 | 2001-05-18 | Canon Inc | ステージ装置、露光装置およびデバイス製造方法 |

| JP5016746B2 (ja) * | 2000-07-28 | 2012-09-05 | キヤノン株式会社 | 撮像装置及びその駆動方法 |

| JP4132850B2 (ja) * | 2002-02-06 | 2008-08-13 | 富士通株式会社 | Cmosイメージセンサおよびその制御方法 |

| JP2006148328A (ja) * | 2004-11-17 | 2006-06-08 | Matsushita Electric Ind Co Ltd | 固体撮像装置 |

| JP2006217421A (ja) * | 2005-02-04 | 2006-08-17 | Matsushita Electric Ind Co Ltd | 固体撮像装置 |

| KR20070085867A (ko) * | 2004-12-07 | 2007-08-27 | 브라잇 이미징 리미티드 | 높은 명암도 편차를 갖는 장면의 화상 처리 방법 및 장치 |

| JP4607006B2 (ja) * | 2005-12-27 | 2011-01-05 | 京セラ株式会社 | 映像信号処理方法および映像信号処理装置 |

| KR100890152B1 (ko) * | 2006-12-22 | 2009-03-20 | 매그나칩 반도체 유한회사 | Cmos 이미지 센서를 위한, 작은 크기, 높은 이득 및낮은 노이즈의 픽셀 |

| EP2432015A1 (en) * | 2007-04-18 | 2012-03-21 | Invisage Technologies, Inc. | Materials, systems and methods for optoelectronic devices |

| KR100882119B1 (ko) * | 2007-07-24 | 2009-02-05 | 주식회사 하이닉스반도체 | 상 변화 메모리 장치의 구동 방법 |

| JP4725608B2 (ja) * | 2008-07-03 | 2011-07-13 | ソニー株式会社 | 比較器、比較器の校正方法、固体撮像素子、およびカメラシステム |

| IT1393759B1 (it) * | 2008-07-28 | 2012-05-08 | Stmicroelectronics Rousset | Dispositivo di programmazione di una cella di memoria pcm con scarica di capacita' e metodo per la programmazione di una cella di memoria pcm |

| DE102009053281B4 (de) * | 2009-11-13 | 2022-04-28 | Arnold & Richter Cine Technik Gmbh & Co. Betriebs Kg | Bildsensor |

| JP5721994B2 (ja) * | 2009-11-27 | 2015-05-20 | 株式会社ジャパンディスプレイ | 放射線撮像装置 |

| JP5935284B2 (ja) | 2011-10-18 | 2016-06-15 | ソニー株式会社 | 撮像装置および撮像表示システム |

| JP5935286B2 (ja) | 2011-10-19 | 2016-06-15 | ソニー株式会社 | 撮像装置および撮像表示システム |

-

2011

- 2011-10-19 JP JP2011229996A patent/JP5935285B2/ja not_active Expired - Fee Related

-

2012

- 2012-10-12 US US13/650,328 patent/US9019425B2/en not_active Expired - Fee Related

- 2012-10-12 CN CN201210411303.3A patent/CN103067668B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20130100302A1 (en) | 2013-04-25 |

| JP2013090207A (ja) | 2013-05-13 |

| CN103067668B (zh) | 2018-02-09 |

| US9019425B2 (en) | 2015-04-28 |

| CN103067668A (zh) | 2013-04-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5935286B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935285B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935287B2 (ja) | 撮像装置および撮像表示システム | |

| JP5853486B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935284B2 (ja) | 撮像装置および撮像表示システム | |

| JP5999921B2 (ja) | 撮像装置および撮像表示システム | |

| JP5874670B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935293B2 (ja) | 撮像装置および撮像表示システム | |

| US9197824B2 (en) | Image pickup unit, method of driving image pickup unit, and image pickup display system | |

| JP6062800B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935291B2 (ja) | 撮像装置および撮像表示システム | |

| JP2013205140A (ja) | 撮像装置および撮像表示システム | |

| JP5884384B2 (ja) | 撮像装置および撮像表示システム | |

| JP5817227B2 (ja) | 放射線撮像装置および放射線撮像表示システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140917 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140917 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150928 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151007 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151111 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160412 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160425 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5935285 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |