JP5935291B2 - 撮像装置および撮像表示システム - Google Patents

撮像装置および撮像表示システム Download PDFInfo

- Publication number

- JP5935291B2 JP5935291B2 JP2011240135A JP2011240135A JP5935291B2 JP 5935291 B2 JP5935291 B2 JP 5935291B2 JP 2011240135 A JP2011240135 A JP 2011240135A JP 2011240135 A JP2011240135 A JP 2011240135A JP 5935291 B2 JP5935291 B2 JP 5935291B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- period

- amplifier

- imaging

- reset operation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000003384 imaging method Methods 0.000 title claims description 196

- 238000006243 chemical reaction Methods 0.000 claims description 99

- 230000005855 radiation Effects 0.000 claims description 30

- 230000035945 sensitivity Effects 0.000 claims description 3

- 230000000368 destabilizing effect Effects 0.000 claims 2

- 230000004048 modification Effects 0.000 description 35

- 238000012986 modification Methods 0.000 description 35

- 238000010586 diagram Methods 0.000 description 29

- 230000000875 corresponding effect Effects 0.000 description 7

- 230000000694 effects Effects 0.000 description 7

- 238000000034 method Methods 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 6

- 101150105133 RRAD gene Proteins 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 3

- 230000001603 reducing effect Effects 0.000 description 3

- 239000000758 substrate Substances 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 206010047571 Visual impairment Diseases 0.000 description 2

- 238000009825 accumulation Methods 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 230000003321 amplification Effects 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 230000000052 comparative effect Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 238000005070 sampling Methods 0.000 description 2

- 239000011669 selenium Substances 0.000 description 2

- 229910004261 CaF 2 Inorganic materials 0.000 description 1

- 229910004613 CdTe Inorganic materials 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000005260 alpha ray Effects 0.000 description 1

- 230000005250 beta ray Effects 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 230000005251 gamma ray Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000002601 radiography Methods 0.000 description 1

- 229910052711 selenium Inorganic materials 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/30—Transforming light or analogous information into electric information

- H04N5/32—Transforming X-rays

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/65—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to reset noise, e.g. KTC noise related to CMOS structures by techniques other than CDS

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/71—Charge-coupled device [CCD] sensors; Charge-transfer registers specially adapted for CCD sensors

- H04N25/75—Circuitry for providing, modifying or processing image signals from the pixel array

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/78—Readout circuits for addressed sensors, e.g. output amplifiers or A/D converters

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Measurement Of Radiation (AREA)

Description

1.実施の形態(パッシブ型の画素回路の例1)

2.変形例

変形例1(パッシブ型の画素回路の例2)

変形例2,3(アクティブ型の画素回路の例)

変形例4(線順次撮像駆動の他の例)

変形例5,6(列選択部の他の構成例)

変形例7,8(放射線に基づいて撮像を行う撮像部の例)

3.適用例(撮像表示システムへの適用例)

4.その他の変形例

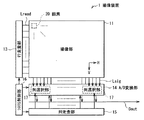

[撮像装置1の全体構成]

図1は、本開示の一実施の形態に係る撮像装置(撮像装置1)の全体のブロック構成を表すものである。撮像装置1は、撮像光に基づいて被写体の情報を読み取る(被写体を撮像する)ものである。この撮像装置1は、撮像部11、行走査部13、A/D変換部14、列走査部15およびシステム制御部16を備えている。これらのうち、行走査部13、A/D変換部14、列走査部15およびシステム制御部16が、本開示における「駆動部」の一具体例に対応する。

撮像部11は、入射した撮像光に応じて電気信号を発生させるもの(撮像領域)である。この撮像部11では、入射した撮像光の光量に応じた電荷量の光電荷を発生して内部に蓄積する光電変換部(後述する光電変換素子21)を有する画素(撮像画素,単位画素)20が、行列状(マトリクス状)に2次元配置されている。なお、図1中に示したように、以下、撮像部11内における水平方向(行方向)を「H」方向とし、垂直方向(列方向)を「V」方向として説明する。

図1に示した行走査部13は、例えば図示しないシフトレジスタ回路やアドレスデコーダ、論理回路等を含んで構成されており、撮像部11内の複数の画素20に対して行単位(水平ライン単位)での駆動(線順次走査)を行う画素駆動部(行走査回路)である。具体的には、後述する線順次読み出し駆動や線順次リセット駆動等の線順次撮像駆動の際に、そのような線順次走査を行う。なお、この線順次走査は、読み出し制御線Lreadを介して前述した行走査信号を各画素20へ供給することによって行われるようになっている。

A/D変換部14は、図1に示したように、複数(ここでは4つ)の信号線Lsigごとに1つ設けられた複数の列選択部17を有しており、信号線Lsigを介して入力した信号電圧(信号電荷)に基づいてA/D変換(アナログ/デジタル変換)を行うものである。これにより、デジタル信号からなる出力データDout(撮像信号)が生成され、外部へ出力されるようになっている。

列走査部15は、例えば図示しないシフトレジスタやアドレスデコーダ等を含んで構成されており、上記した列選択部17内の各スイッチSW2を走査しつつ順番に駆動するものである。このような列走査部15による選択走査によって、信号線Lsigの各々を介して読み出された各画素20の信号(上記した出力データDout)が、順番に外部へ出力されるようになっている。

(1.基本動作)

この撮像装置1では、図2に示したように、後述する露光期間Texにおいて撮像光Linが撮像部11へ入射すると、光電変換層111(図3に示した各画素20内の光電変換素子21)では、この撮像光Linが信号電荷に変換(光電変換)される。この光電変換によって発生した信号電荷により、蓄積ノードNでは蓄積ノード容量に応じた電圧変化が生じる。具体的には、蓄積ノード容量をCs、発生した信号電荷をqとすると、蓄積ノードNでは(q/Cs)の分だけ電圧が低下する。このような電圧変化に応じて、トランジスタ22のドレインには入力電圧Vin(信号電荷に対応した電圧)が印加される。このトランジスタ22へ供給される入力電圧Vinは、読み出し制御線Lreadから供給される行走査信号に応じてトランジスタ22がオン状態になると、その電荷が画素20から信号線Lsigへ読み出される(読み出し期間)。

ここで、図5(A),(B)を参照して、上記した露光期間Texおよび読み出し期間における画素20および列選択部17内のチャージアンプ回路の動作について、詳細に説明する。なお、以下では説明の便宜上、トランジスタ22のオン・オフ状態を、スイッチを用いて図示している。

ところで、上記のような1回目の画素リセット動作を行ったにも関わらず、この1回目の画素リセット動作前に蓄積された信号電荷の一部が、画素20内に残存してしまう場合がある。このように信号電荷の一部が画素20内に残ってしまうと、次の読み出し動作時(次のフレーム期間での撮像時)においてその残留電荷に起因した残像が発生し、撮像画質が低下してしまうという問題がある。

また、本実施の形態では、例えば以下の図9〜図16に示したようにして、線順次撮像駆動(線順次読み出し駆動および線順次リセット駆動)の際の、各リセット動作(画素リセット動作およびアンプリセット動作)のタイミングや期間が設定されている。

続いて、上記実施の形態の変形例(変形例1〜8)について説明する。なお、実施の形態における構成要素と同一のものには同一の符号を付し、適宜説明を省略する。

図17は、変形例1に係る画素(画素20A)の回路構成を、上記実施の形態で説明した列選択部17の回路構成例とともに表したものである。本変形例の画素20Aは、実施の形態の画素20と同様にいわゆるパッシブ型の回路構成となっており、1つの光電変換素子21と1つのトランジスタ22とを有している。また、この画素20Aには画素20と同様に、H方向に沿って延在する読み出し制御線Lreadと、V方向に沿って延在する信号線Lsigとが接続されている。

(回路構成)

図18は、変形例2に係る画素(画素20B)の回路構成を、以下説明する列選択部17Bの回路構成例とともに表したものである。また、図19は、変形例3に係る画素(画素20C)の回路構成を、列選択部17Bの回路構成例とともに表したものである。これらの変形例2,3に係る画素20B,20Cはそれぞれ、これまで説明した画素20,20Aとは異なり、いわゆるアクティブ型の回路構成となっている。

このようなアクティブ型の回路構成からなる画素20B,20Cを有する変形例2,3の撮像装置では、以下のようにして撮像動作(線順次撮像駆動)がなされる。

図21(A)〜(C)および図22(A)〜(C)はそれぞれ、変形例4に係る撮像駆動例をタイミング図で表わしたものである。

図23は、変形例5に係る列選択部(列選択部17C)の概略構成を回路図で表わしたものである。本変形例の列選択部17Cは、上記実施の形態の列選択部17において、チャージアンプ回路の構成が以下の点で異なっている。

図24は、変形例6に係る列選択部(列選択部17D)のブロック構成を表したものであり、図25は、この列選択部17Dにおける詳細な回路構成例を表したものである。

図26(A),(B)はそれぞれ、変形例7,8に係る撮像部(撮像部11A,11B)の概略構成を模式的に表したものである。

続いて、上記実施の形態および各変形例(変形例1〜8)に係る撮像装置の撮像表示システムへの適用例について説明する。

以上、実施の形態、変形例および適用例を挙げて本開示の技術を説明したが、本技術はこれらの実施の形態等に限定されず、種々の変形が可能である。

(1)

各々が光電変換素子を含む複数の画素を有する撮像部と、

アンプを含んで構成されると共に、前記光電変換素子により得られた電荷を前記アンプを用いて前記画素から信号として読み出す読み出し動作と、前記画素内の電荷をリセットするための画素リセット動作と、前記アンプの動作をリセットするためのアンプリセット動作とがそれぞれ行われるように、各画素を駆動する駆動部と

を備え、

前記駆動部は、前記画素リセット動作の終了タイミングおよび前記アンプリセット動作の終了タイミングのうちの少なくとも一方が、所定の電源電位不安定化期間内に含まれないように、各画素の駆動を行う

撮像装置。

(2)

前記駆動部は、前記画素リセット動作の終了タイミングが前記電源電位不安定化期間内に含まれないように、各画素の駆動を行う

上記(1)に記載の撮像装置。

(3)

前記駆動部は、前記画素リセット動作の終了タイミングおよび前記アンプリセット動作の終了タイミングの双方が前記電源電位不安定化期間内に含まれないように、各画素の駆動を行う

上記(2)に記載の撮像装置。

(4)

前記駆動部は、前記アンプリセット動作の終了タイミングが前記電源電位不安定化期間内に含まれないように、各画素の駆動を行う

上記(1)に記載の撮像装置。

(5)

前記画素リセット動作の期間と前記アンプリセット動作の期間との少なくとも一部が、互いにオーバーラップしている

上記(1)ないし(4)のいずれかに記載の撮像装置。

(6)

前記アンプリセット動作の期間内に、前記画素リセット動作の期間全体が含まれている

上記(5)に記載の撮像装置。

(7)

前記画素リセット動作の期間と前記アンプリセット動作の期間とが、互いに一致している

上記(5)に記載の撮像装置。

(8)

前記駆動部は、前記画素リセット動作の全期間または前記アンプリセット動作の全期間が前記電源電位不安定化期間内に含まれないように、各画素の駆動を行う

上記(1)ないし(7)のいずれかに記載の撮像装置。

(9)

前記駆動部は、

前記アンプを用いて読み出された信号の一部を選択するマルチプレクサ回路と、

前記マルチプレクサ回路により選択された信号に対してA/D変換を行うA/Dコンバータとを有し、

前記電源電位不安定化期間は、前記マルチプレクサ回路の動作期間および前記A/Dコンバータの動作期間のうちの少なくとも一方を含む

上記(1)ないし(8)のいずれかに記載の撮像装置。

(10)

前記駆動部は、前記画素リセット動作が所定の単位期間内で間欠的に複数回行われるように、各画素を駆動する

上記(1)ないし(9)のいずれかに記載の撮像装置。

(11)

前記画素リセット動作が、1水平期間を超える期間に亘って間欠的に複数回行われる

上記(10)に記載の撮像装置。

(12)

前記撮像部が、入射した放射線に応じて電気信号を発生させるものであり、放射線撮像装置として構成されている

上記(1)ないし(11)のいずれかに記載の撮像装置。

(13)

前記撮像部は、

前記光電変換素子を構成する光電変換層と、

前記放射線を前記光電変換層の感度域に波長変換する波長変換層と

を有する上記(12)に記載の撮像装置。

(14)

前記撮像部は、前記光電変換素子を構成すると共に前記放射線に応じて前記電気信号を直接発生させる光電変換層を有する

上記(12)に記載の撮像装置。

(15)

前記放射線がX線である

上記(12)ないし(14)のいずれかに記載の撮像装置。

(16)

撮像装置と、この撮像装置により得られた撮像信号に基づく画像表示を行う表示装置とを備え、

前記撮像装置は、

各々が光電変換素子を含む複数の画素を有する撮像部と、

アンプを含んで構成されると共に、前記光電変換素子により得られた電荷を前記アンプを用いて前記画素から信号として読み出す読み出し動作と、前記画素内の電荷をリセットするための画素リセット動作と、前記アンプの動作をリセットするためのアンプリセット動作とがそれぞれ行われるように、各画素を駆動する駆動部と

を備え、

前記駆動部は、前記画素リセット動作の終了タイミングおよび前記アンプリセット動作の終了タイミングのうちの少なくとも一方が、所定の電源電位不安定化期間内に含まれないように、各画素の駆動を行う

撮像表示システム。

Claims (12)

- 各々が光電変換素子を含む複数の画素を有する撮像部と、

アンプを含んで構成されると共に、前記光電変換素子により得られた電荷を前記アンプを用いて前記画素から信号として読み出す読み出し動作と、前記画素内の電荷をリセットするための1または複数回の画素リセット動作と、前記アンプの動作をリセットするためのアンプリセット動作とがそれぞれ行われるように、各画素を駆動する駆動部と

を備え、

前記駆動部は、

前記読み出し動作と、前記1または複数回の画素リセット動作のうちの1回目の画素リセット動作とが、並行して行われると共に、

前記読み出し動作および前記画素リセット動作の終了タイミングと、前記アンプリセット動作の終了タイミングとの双方が、所定の電源電位不安定化期間内に含まれず、かつ、

前記読み出し動作および前記画素リセット動作の全期間と、前記アンプリセット動作の全期間とが、前記電源電位不安定化期間内に含まれないように、各画素の駆動を行う

撮像装置。 - 前記画素リセット動作の期間と前記アンプリセット動作の期間との少なくとも一部が、互いにオーバーラップしている

請求項1に記載の撮像装置。 - 前記アンプリセット動作の期間内に、前記画素リセット動作の期間全体が含まれている

請求項2に記載の撮像装置。 - 前記画素リセット動作の期間と前記アンプリセット動作の期間とが、互いに一致している

請求項2に記載の撮像装置。 - 前記駆動部は、

前記アンプを用いて読み出された信号の一部を選択するマルチプレクサ回路と、

前記マルチプレクサ回路により選択された信号に対してA/D変換を行うA/Dコンバータとを有し、

前記電源電位不安定化期間は、前記マルチプレクサ回路の動作期間および前記A/Dコンバータの動作期間のうちの少なくとも一方を含む

請求項1ないし請求項4のいずれか1項に記載の撮像装置。 - 前記駆動部は、前記画素リセット動作が所定の単位期間内で間欠的に複数回行われるように、各画素を駆動する

請求項1ないし請求項5のいずれか1項に記載の撮像装置。 - 前記画素リセット動作が、1水平期間を超える期間に亘って間欠的に複数回行われる

請求項6に記載の撮像装置。 - 前記撮像部が、入射した放射線に応じて電気信号を発生させるものであり、放射線撮像装置として構成されている

請求項1ないし請求項7のいずれか1項に記載の撮像装置。 - 前記撮像部は、

前記光電変換素子を構成する光電変換層と、

前記放射線を前記光電変換層の感度域に波長変換する波長変換層と

を有する請求項8に記載の撮像装置。 - 前記撮像部は、前記光電変換素子を構成すると共に前記放射線に応じて前記電気信号を直接発生させる光電変換層を有する

請求項8に記載の撮像装置。 - 前記放射線がX線である

請求項8ないし請求項10のいずれか1項に記載の撮像装置。 - 撮像装置と、この撮像装置により得られた撮像信号に基づく画像表示を行う表示装置とを備え、

前記撮像装置は、

各々が光電変換素子を含む複数の画素を有する撮像部と、

アンプを含んで構成されると共に、前記光電変換素子により得られた電荷を前記アンプを用いて前記画素から信号として読み出す読み出し動作と、前記画素内の電荷をリセットするための1または複数回の画素リセット動作と、前記アンプの動作をリセットするためのアンプリセット動作とがそれぞれ行われるように、各画素を駆動する駆動部と

を備え、

前記駆動部は、

前記読み出し動作と、前記1または複数回の画素リセット動作のうちの1回目の画素リセット動作とが、並行して行われると共に、

前記読み出し動作および前記画素リセット動作の終了タイミングと、前記アンプリセット動作の終了タイミングとの双方が、所定の電源電位不安定化期間内に含まれず、かつ、

前記読み出し動作および前記画素リセット動作の全期間と、前記アンプリセット動作の全期間とが、前記電源電位不安定化期間内に含まれないように、各画素の駆動を行う

撮像表示システム。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011240135A JP5935291B2 (ja) | 2011-11-01 | 2011-11-01 | 撮像装置および撮像表示システム |

| CN201210414005.XA CN103124323B (zh) | 2011-11-01 | 2012-10-25 | 图像拍摄单元和图像拍摄显示系统 |

| US13/659,941 US8982255B2 (en) | 2011-11-01 | 2012-10-25 | Image pickup including photoelectric conversion |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011240135A JP5935291B2 (ja) | 2011-11-01 | 2011-11-01 | 撮像装置および撮像表示システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013098765A JP2013098765A (ja) | 2013-05-20 |

| JP2013098765A5 JP2013098765A5 (ja) | 2014-10-23 |

| JP5935291B2 true JP5935291B2 (ja) | 2016-06-15 |

Family

ID=48172042

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011240135A Expired - Fee Related JP5935291B2 (ja) | 2011-11-01 | 2011-11-01 | 撮像装置および撮像表示システム |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8982255B2 (ja) |

| JP (1) | JP5935291B2 (ja) |

| CN (1) | CN103124323B (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5935293B2 (ja) | 2011-11-02 | 2016-06-15 | ソニー株式会社 | 撮像装置および撮像表示システム |

| WO2013084947A1 (ja) * | 2011-12-07 | 2013-06-13 | シャープ株式会社 | 光センサ回路の動作方法、および、当該光センサ回路を備えた表示装置の動作方法 |

| JP5895504B2 (ja) | 2011-12-15 | 2016-03-30 | ソニー株式会社 | 撮像パネルおよび撮像処理システム |

| JP6238573B2 (ja) * | 2013-05-28 | 2017-11-29 | キヤノン株式会社 | 撮像装置の駆動方法、撮像装置、撮像システム |

| JP6351252B2 (ja) * | 2013-12-18 | 2018-07-04 | キヤノン株式会社 | 光電変換装置の駆動方法 |

| JP6501513B2 (ja) * | 2014-12-22 | 2019-04-17 | キヤノン株式会社 | 放射線画像撮影装置及びその制御方法 |

| JP6708474B2 (ja) | 2016-04-28 | 2020-06-10 | キヤノン株式会社 | 撮像装置及び放射線撮像システム |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5227900A (en) * | 1990-03-20 | 1993-07-13 | Canon Kabushiki Kaisha | Method of driving ferroelectric liquid crystal element |

| JP3911788B2 (ja) | 1997-03-10 | 2007-05-09 | ソニー株式会社 | 固体撮像素子およびその駆動方法 |

| EP1662773B1 (en) | 1997-08-15 | 2014-01-22 | Sony Corporation | Solid-state image sensor and method of driving same |

| JP3998134B2 (ja) * | 2002-09-13 | 2007-10-24 | シャープ株式会社 | Ad変換装置、多チャンネルad変換装置、x線センサーモジュールおよびそれらの制御方法 |

| JP5171431B2 (ja) | 2008-06-26 | 2013-03-27 | 株式会社ジャパンディスプレイウェスト | 光電変換装置、放射線撮像装置及び放射線検出装置 |

| WO2010010620A1 (ja) * | 2008-07-24 | 2010-01-28 | 株式会社島津製作所 | 光または放射線撮像装置 |

| JP2010253089A (ja) * | 2009-04-27 | 2010-11-11 | Konica Minolta Medical & Graphic Inc | 放射線画像生成装置及び放射線画像生成システム |

| JP5721994B2 (ja) * | 2009-11-27 | 2015-05-20 | 株式会社ジャパンディスプレイ | 放射線撮像装置 |

| US8189402B2 (en) * | 2010-06-16 | 2012-05-29 | Ememory Technology Inc. | Sensing circuit for memory cell supplied with low power |

| JP5935293B2 (ja) | 2011-11-02 | 2016-06-15 | ソニー株式会社 | 撮像装置および撮像表示システム |

-

2011

- 2011-11-01 JP JP2011240135A patent/JP5935291B2/ja not_active Expired - Fee Related

-

2012

- 2012-10-25 US US13/659,941 patent/US8982255B2/en not_active Expired - Fee Related

- 2012-10-25 CN CN201210414005.XA patent/CN103124323B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN103124323B (zh) | 2018-05-11 |

| JP2013098765A (ja) | 2013-05-20 |

| CN103124323A (zh) | 2013-05-29 |

| US20130107092A1 (en) | 2013-05-02 |

| US8982255B2 (en) | 2015-03-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5935291B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935286B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935293B2 (ja) | 撮像装置および撮像表示システム | |

| JP5935284B2 (ja) | 撮像装置および撮像表示システム | |

| JP5853486B2 (ja) | 撮像装置および撮像表示システム | |

| JP5999921B2 (ja) | 撮像装置および撮像表示システム | |

| JP5874670B2 (ja) | 撮像装置および撮像表示システム | |

| US9197824B2 (en) | Image pickup unit, method of driving image pickup unit, and image pickup display system | |

| JP5935285B2 (ja) | 撮像装置および撮像表示システム | |

| JP5895650B2 (ja) | 撮像装置および撮像表示システム | |

| JP5724623B2 (ja) | 信号伝達装置および撮像表示システム | |

| JP5884384B2 (ja) | 撮像装置および撮像表示システム | |

| JP5817227B2 (ja) | 放射線撮像装置および放射線撮像表示システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140909 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140909 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150928 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151007 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151109 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160412 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160425 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5935291 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |