JP5798442B2 - クロック分配回路及びクロック分配回路の形成方法 - Google Patents

クロック分配回路及びクロック分配回路の形成方法 Download PDFInfo

- Publication number

- JP5798442B2 JP5798442B2 JP2011232120A JP2011232120A JP5798442B2 JP 5798442 B2 JP5798442 B2 JP 5798442B2 JP 2011232120 A JP2011232120 A JP 2011232120A JP 2011232120 A JP2011232120 A JP 2011232120A JP 5798442 B2 JP5798442 B2 JP 5798442B2

- Authority

- JP

- Japan

- Prior art keywords

- clock signal

- feedback

- feedback clock

- circuit

- clock

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/06—Clock generators producing several clock signals

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/10—Distribution of clock signals, e.g. skew

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49579—Watch or clock making

Description

クロックツリーの分岐点を通じて分配されるクロック信号で動作する論理回路を有する半導体集積回路におけるクロック分配回路であって、

クロック信号が分配されるクロックツリーと、

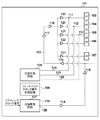

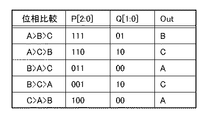

前記クロックツリーの異なる分岐点から出力される複数のフィードバッククロック信号を受信し、各フィードバッククロック信号の位相差を検知する位相比較回路と、

前記位相比較回路によって検知した位相差に基づいて、前記半導体集積回路内の信号遅延バラツキを補正するためのバラツキ補正済フィードバッククロック信号を生成するフィードバッククロック信号生成回路と、

前記フィードバッククロック信号生成回路によって生成された前記バラツキ補正済フィードバッククロック信号と基準クロック信号との位相差が小さくなるように前記クロック信号を出力する位相調整回路とを有し、

前記フィードバッククロック信号生成回路は、前記複数のフィードバッククロック信号の各フィードバッククロック信号と基準クロック信号との遅延差から、平均遅延値を算出し、その算出した平均遅延値に従って中心特性となるフィードバッククロック信号を前記バラツキ補正済フィードバッククロック信号として生成することを特徴とする。

以下に本発明に係るクロック分配回路、とりわけフィードバッククロック信号生成回路により複数のフィードバッククロック信号の位相差を検知し、中心特性に近いフィードバッククロック信号を選択する実施形態について説明する。ここで、この選択したフィードバッククロック信号は、半導体集積回路内の製造バラツキを補正したバラツキ補正済フィードバッククロック信号として生成することになる。

実施形態2では、フィードバッククロック信号生成回路によって複数のフィードバッククロック信号の位相差を検知し、中心特性となるフィードバッククロック信号(バラツキ補正済フィードバッククロック信号)を生成する場合の構成について説明する。実施形態1と異なる点は、位相比較回路108とフィードバッククロック信号生成回路109の内部構成である。

実施形態1あるいは実施形態2のクロック分配回路を形成する場合には、以下のような処理を実行することになる。

Claims (7)

- クロックツリーの分岐点を通じて分配されるクロック信号で動作する論理回路を有する半導体集積回路におけるクロック分配回路であって、

クロック信号が分配されるクロックツリーと、

前記クロックツリーの異なる分岐点から出力される複数のフィードバッククロック信号を受信し、各フィードバッククロック信号の位相差を検知する位相比較回路と、

前記位相比較回路によって検知した位相差に基づいて、前記半導体集積回路内の信号遅延バラツキを補正するためのバラツキ補正済フィードバッククロック信号を生成するフィードバッククロック信号生成回路と、

前記フィードバッククロック信号生成回路によって生成された前記バラツキ補正済フィードバッククロック信号と基準クロック信号との位相差が小さくなるように前記クロック信号を出力する位相調整回路とを有し、

前記フィードバッククロック信号生成回路は、前記複数のフィードバッククロック信号の各フィードバッククロック信号と基準クロック信号との遅延差から、平均遅延値を算出し、その算出した平均遅延値に従って中心特性となるフィードバッククロック信号を前記バラツキ補正済フィードバッククロック信号として生成する

ことを特徴とするクロック分配回路。 - 前記位相比較回路は、前記複数のフィードバッククロック信号の各フィードバッククロック信号の位相を比較して、位相差を検知する

ことを特徴とする請求項1に記載のクロック分配回路。 - 前記フィードバッククロック信号生成回路は、前記複数のフィードバッククロック信号の位相差に基づいて、該複数のフィードバッククロック信号の内、中心特性に近いフィードバッククロック信号を選択して前記バラツキ補正済フィードバッククロック信号として生成する

ことを特徴とする請求項1または2に記載のクロック分配回路。 - 前記位相比較回路は、前記複数のフィードバッククロック信号の各フィードバッククロック信号と基準クロック信号との遅延差を比較することで、各フィードバッククロック信号の位相差を検知する

ことを特徴とする請求項1に記載のクロック分配回路。 - 前記フィードバッククロック信号生成回路は、前記複数のフィードバッククロック信号の各フィードバッククロック信号と基準クロック信号との遅延差の内、前記平均遅延値と一定値以上の差がある遅延差がある場合、その遅延差を除く、残りの遅延差で平均遅延値を再算出して、その再算出した平均遅延値に従って中心特性となるフィードバッククロック信号を前記バラツキ補正済フィードバッククロック信号として生成する

ことを特徴とする請求項1に記載のクロック分配回路。 - 前記複数のフィードバッククロック信号のフィードバックパスの配線経路は、前記クロックツリーの起点から前記フィードバックパスの分岐点までのクロックの配線経路の近傍に配置される

ことを特徴とする請求項1乃至5のいずれか1項に記載のクロック分配回路。 - 請求項1に記載のクロック分配回路の形成方法であって、

前記複数のフィードバッククロック信号のフィードバックパスの配線経路を、前記クロックツリーの起点から前記フィードバックパスの分岐点までのクロックの配線経路の近傍に配置する工程と、

前記複数のフィードバッククロック信号のフィードバックパスを前記位相比較回路に接続する工程と、

前記位相比較回路と前記位相調整回路との間に前記フィードバッククロック信号生成回路を配置する工程と

を有することを特徴とするクロック分配回路の形成方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011232120A JP5798442B2 (ja) | 2011-10-21 | 2011-10-21 | クロック分配回路及びクロック分配回路の形成方法 |

| US13/603,755 US8736339B2 (en) | 2011-10-21 | 2012-09-05 | Clock distribution circuit and method of forming clock distribution circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011232120A JP5798442B2 (ja) | 2011-10-21 | 2011-10-21 | クロック分配回路及びクロック分配回路の形成方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013090290A JP2013090290A (ja) | 2013-05-13 |

| JP2013090290A5 JP2013090290A5 (ja) | 2014-11-27 |

| JP5798442B2 true JP5798442B2 (ja) | 2015-10-21 |

Family

ID=48135459

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011232120A Active JP5798442B2 (ja) | 2011-10-21 | 2011-10-21 | クロック分配回路及びクロック分配回路の形成方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8736339B2 (ja) |

| JP (1) | JP5798442B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9523736B2 (en) | 2014-06-19 | 2016-12-20 | Nuvoton Technology Corporation | Detection of fault injection attacks using high-fanout networks |

| US9397663B2 (en) | 2014-07-22 | 2016-07-19 | Winbond Electronics Corporation | Fault protection for high-fanout signal distribution circuitry |

| US9397666B2 (en) * | 2014-07-22 | 2016-07-19 | Winbond Electronics Corporation | Fault protection for clock tree circuitry |

| US10013581B2 (en) | 2014-10-07 | 2018-07-03 | Nuvoton Technology Corporation | Detection of fault injection attacks |

| US9471094B1 (en) * | 2014-12-30 | 2016-10-18 | Cadence Design Systems, Inc. | Method of aligning timing of a chip select signal with a cycle of a memory device |

| CN107300948A (zh) * | 2016-04-14 | 2017-10-27 | 飞思卡尔半导体公司 | 具有多位时钟门控单元的集成电路 |

| US10254782B2 (en) * | 2016-08-30 | 2019-04-09 | Micron Technology, Inc. | Apparatuses for reducing clock path power consumption in low power dynamic random access memory |

| US11366899B2 (en) | 2020-02-18 | 2022-06-21 | Nuvoton Technology Corporation | Digital fault injection detector |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5406590A (en) * | 1992-10-23 | 1995-04-11 | Compaq Computer Corporation | Method of and apparatus for correcting edge placement errors in multiplying phase locked loop circuits |

| JPH06273478A (ja) * | 1993-03-20 | 1994-09-30 | Hitachi Ltd | クロックスキュー補正回路、及び半導体集積回路 |

| JP3180780B2 (ja) | 1998-10-13 | 2001-06-25 | 日本電気株式会社 | デジタルdll回路 |

| US6608530B1 (en) * | 2001-12-14 | 2003-08-19 | Cypress Semiconductor Corp. | Enhanced ZDB feedback methodology utilizing binary weighted techniques |

| US6737902B2 (en) * | 2002-05-16 | 2004-05-18 | Sun Microsystems, Inc. | Method and a system to distribute clock signals in digital circuits |

| US7098714B2 (en) * | 2003-12-08 | 2006-08-29 | Micron Technology, Inc. | Centralizing the lock point of a synchronous circuit |

| KR100705502B1 (ko) * | 2005-12-10 | 2007-04-09 | 한국전자통신연구원 | 클록 편차를 제거하는 클록 발생 장치 및 클록 수신 장치 |

| JP2007336003A (ja) | 2006-06-12 | 2007-12-27 | Nec Electronics Corp | クロック分配回路、半導体集積回路、クロック分配回路の形成方法及びそのプログラム |

| JP2008010607A (ja) | 2006-06-29 | 2008-01-17 | Nec Computertechno Ltd | 半導体集積回路およびクロックスキュー低減方法 |

| JP2010273286A (ja) * | 2009-05-25 | 2010-12-02 | Renesas Electronics Corp | クロック分配回路およびクロック分配方法 |

-

2011

- 2011-10-21 JP JP2011232120A patent/JP5798442B2/ja active Active

-

2012

- 2012-09-05 US US13/603,755 patent/US8736339B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8736339B2 (en) | 2014-05-27 |

| US20130099844A1 (en) | 2013-04-25 |

| JP2013090290A (ja) | 2013-05-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5798442B2 (ja) | クロック分配回路及びクロック分配回路の形成方法 | |

| JP6242228B2 (ja) | クロック生成方法およびクロック生成回路 | |

| JP4919909B2 (ja) | 半導体装置 | |

| US9898035B2 (en) | Clock synchronization method | |

| US8766688B2 (en) | DLL circuit and delay-locked method using the same | |

| JP6783535B2 (ja) | クロック補正装置及びクロック補正方法 | |

| JP4079733B2 (ja) | 位相同期ループ回路 | |

| JP2005149313A (ja) | 半導体集積回路の設計方法および半導体集積回路 | |

| JP2006041129A (ja) | 半導体集積回路 | |

| JP2010233018A (ja) | クロック分配回路及びクロックスキュー調整方法 | |

| JP2010273132A (ja) | タイミング調整回路、タイミング調整方法及び補正値算出方法 | |

| JP2007228145A (ja) | 半導体集積回路 | |

| JP3652277B2 (ja) | 遅延同期回路用遅延調整回路 | |

| JP3869406B2 (ja) | クロック位相差検出回路、クロック分配回路、及び大規模集積回路 | |

| US8710892B2 (en) | Clock distribution circuit | |

| JP5580763B2 (ja) | 半導体集積回路 | |

| JP2005038159A (ja) | 半導体装置及びクロックスキュー調整方法 | |

| JP4611015B2 (ja) | 半導体集積回路装置 | |

| JP6111739B2 (ja) | クロックスキュー補正回路、その補正方法、及びクロック分配装置 | |

| JP3867653B2 (ja) | 半導体集積回路 | |

| JP2004199705A (ja) | 集積回路のためのクロック生成装置および生成方法 | |

| JP2009187110A (ja) | クロック分配回路の設計方法 | |

| JP2004266034A (ja) | 半導体集積回路、および半導体集積回路の設計方法 | |

| JP2007110762A (ja) | 半導体装置 | |

| JP2004302819A (ja) | 半導体集積回路のレイアウト設計方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141014 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20141014 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150528 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150601 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150702 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150724 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150821 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5798442 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |